WD83C593 Micro Channel Bus Interface Controller Device

39

# TABLE OF CONTENTS

| 1.0 | Description and Application .    |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-1  |

|-----|----------------------------------|-------|-----|-----|------|-----|------|------|-----|----|---|---|---|---|---|---|---|---|-------|

|     | 1.1 Features                     |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-1  |

|     | 1.2 Theory of Operation .        | •     | •   | •   | •    | •   | •    | •    | •   |    | • | • | • |   |   | • |   | • | 39-1  |

| 2.0 | POS Registers and Decoding       |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-2  |

|     | 2.1 Space Decodings              |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-2  |

|     | 2.1.1 POS[2] Register            |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-2  |

|     | 2.1.2 POS[3] Register .          |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-4  |

|     | 2.1.3 POS[4] Register .          |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-4  |

|     | 2.2 Other POS Functions - PC     |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-5  |

| 3.0 | Programming the EEPROM Re        | gist  | ers |     | •    |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-6  |

| App | endix A Pin Designations .       |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   | - | 39-7  |

|     | endix B Register Designations    |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   |       |

| App | endix C Electrical Characteristi | cs    |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-14 |

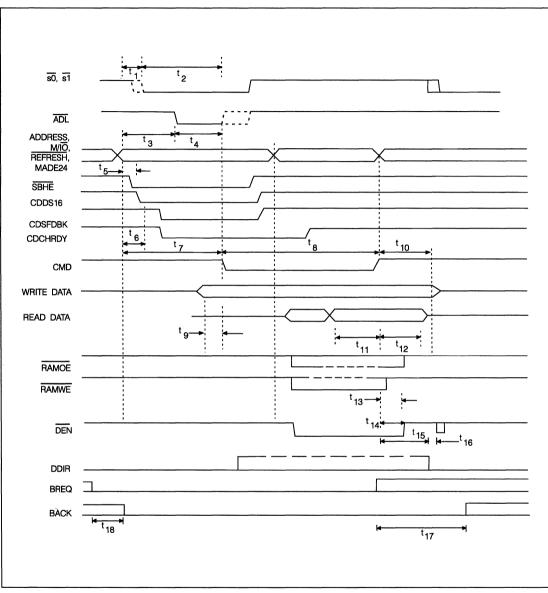

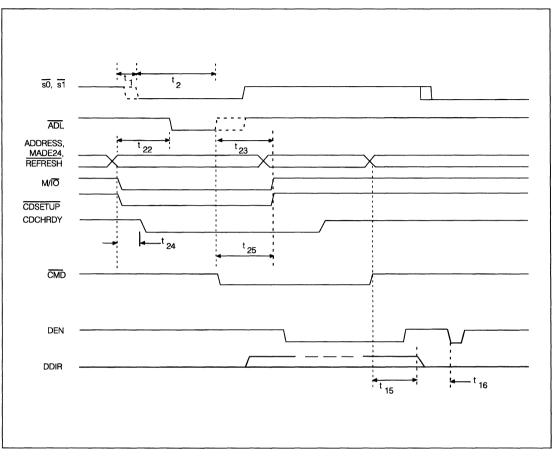

| App | endix D AC Operating Character   | erist | ics | and | iT t | mir | ng [ | Diag | gra | ms |   | • |   | • |   |   |   | • | 39-16 |

| FIG | URES                             |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   |       |

| 2-1 | General System Block Diagram     | n     |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-3  |

| 3-1 | Typical EEPROM Register Bit (    | Cell  |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-6  |

| A-1 | 84-PLCC Pinout                   |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   |       |

| D-1 | Host-Memory Read/Write Timi      | ng    |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-18 |

| D-2 | Set-up Timing                    | •     | •   | •   |      | •   |      | •    | ·   |    | • |   |   |   | • | • | • | • | 39-19 |

| -   |                                  |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   |       |

| IA  | BLES                             |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   |       |

| A-1 | Pin Descriptions                 |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-8  |

| B-1 | Internal Register I/O Map .      |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-12 |

| B-2 | Register Descriptions            |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-12 |

| C-1 | DC Parameters                    |       |     | •   |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-14 |

|     | Non-Operational Specifications   |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   |       |

|     | Operational Specifications .     |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   |       |

| D-1 | AC Operating Characteristics     |       |     |     |      |     |      |      |     |    |   |   |   |   |   |   |   |   | 39-16 |

\_\_\_\_ \_\_.

# **1.0 DESCRIPTION AND APPLICATION**

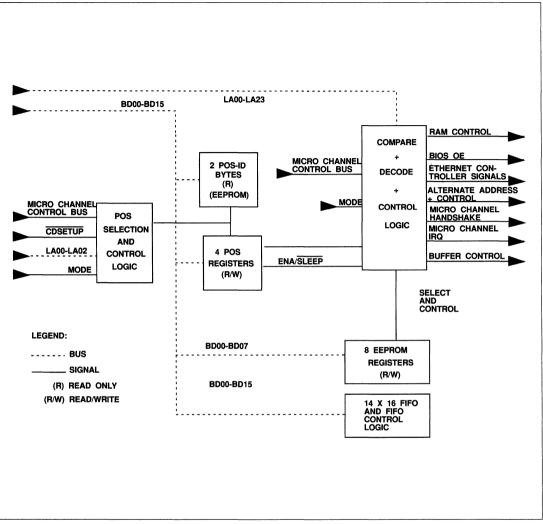

The WD83C593 is a Micro Channel bus interface controller designed for non-intelligent Ethernet or StarLAN boards. The device is used as an interface to the LAN controller, BIOS ROM, buffer RAM (which functions as shared memory), and the host Micro Channel bus.

## 1.1 FEATURES

- Direct interface between a non-intelligent Ethernet or StarLAN LAN controller and a Micro Channel bus

- Ten bytes of internal electrically erasable programmable read only memory (EEPROM)

- 84-pin ASIC, 2.0 micron CMOS technology

- Programmable BIOS ROM size (16, 32, or 64 Kbytes)

- Programmable RAM size (16 or 64 Kbytes)

- Single, 5V power supply

- Four Vcc, ground, and program-selectable IRQ pins

- Testable/programmable before and after assembly

## 1.2 THEORY OF OPERATION

The WD83C593 non-intelligent interface device connects the Micro Channel bus (as a non-DMA slave) to the LAN controller, BIOS ROM, and buffer RAM. The WD83C593 satisfies all necessary interface requirements, performs all decoding for local I/O and memory spaces, and generates the necessary chip select control and handshake signals. In order for the WD83C593 non-intelligent Micro Channel bus interface device to function properly, the mode select pin must be left open (internally pulled high).

This enables the WD83C593 to arbitrate between the host and WD83C690 LAN controller for the BD00-BD15 data bus. During local WD83C690 DMA bursts in and out of the buffer RAM, the device isolates the BD data bus from the Micro Channel via external buffering, and prevents the host from intervening until the process is complete. When a valid decode occurs, the device negates the CDCHRDY signal.

The remainder of the time, the device enables the external buffers so that the host can perform memory or I/O cycles (anywhere on the card). The host uses a 16-bit wide "move" string operation to transfer data to and from the buffer RAM. During this time, the WD83C593 generates the RAM control signals (tri-state during local RAM accesses).

# 2.0 POS REGISTERS AND DECODING

Designers of Micro Channel adapters are required by the Micro Channel architecture to use two readonly ID bytes and (up to) six read/write programmable option select (POS) registers. This arrangement accomplishes the following:

- · eliminates switches and jumpers

- permits the installation of multiple identical cards

- · allows the identification of any card by slot

- · resolves resource assignment conflicts

Designers are also required to provide an adapter description file (.ADF) that reports the contents of the ID bytes, the number of POS registers used on the card, their purpose and contents, and their "alternate contents."

The Micro Channel bus defines the architecture of the following bits:

POS[2] bit 0.....Card enable (address 102h)

POS[5] bit 7.....CH CK active indicator (105h)

POS[5] bit 6......CH CK status available indicator (105h)

The remaining POS registers are "free form" and can be used for space decoding, establishing arbitration levels, and so on. When the system is reset, each adapter must turn off the card enable bit, which in turn disables all outputs from the card, including the interrupt request lines.

The central configuration software checks all slots independently for ID bytes, and uses the ADF files provided to resolve conflicts and set up the POS registers. It is during this time <u>only</u> that the POS registers can be accessed, and they can be accessed only by the configuration software.

The CDSETUP line, together with the least significant three address lines, is used for decoding POS register accesses.

#### 2.1 Space Decodings

Three POS registers, POS[2], POS[3], and POS[4], are used to decode the card I/O space, shared RAM space, and BIOS ROM space, respectively. The mode select pin, as indicated previously, must be left open.

#### 2.1.1 POS[2] Register

| Bit    | Bit Assignment |

|--------|----------------|

| 7      | LA11           |

| 6      | LA10           |

| 6<br>5 | LA09           |

| 4      | LA08           |

| 3      | LA07           |

| 2      | LA06           |

| 1      | LA05           |

| 0      | CDEN           |

If a 29h is written in POS[2], the WD83C593 I/O space is placed in the range 280h - 029Fh. This is one of 128 possible 32-Kbyte ranges. For each of the primary and alternate choices, one or more interrupt levels are defined in the .ADF file.

#### Bit (7:1)

These bits are used to decode the I/O space for the application.

#### Bit 0

Card Enable.

Bit 0 wakes up low and, until it is set by the configuration routine, keeps the card in "sleep" mode.

FIGURE 2-1. GENERAL SYSTEM BLOCK DIAGRAM

## 2.1.2 POS[3] Register

| Bit | Bit Assignment |

|-----|----------------|

| 7   | LA19           |

| 6   | LA18           |

| 5   | LA17           |

| 4   | LA16           |

| 3   | LA15           |

| 2   | LA14           |

| 1   | PME            |

| 0   | CLAIM          |

If a C2h is written in POS[3], the shared RAM space is placed in the range 0C0000h - 0C3FFFh. This is one of 64 possible 16-Kbyte ranges. It is intended to place shared RAM in the general range, 0C0000h - 0DFFFFh.

#### Bit (7:2)

These bits are used to set the shared RAM space for the application.

#### Bit (1:0)

Memory Enable; Claim.

Bit 1 wakes up low and, until it is set by the configuration routine, keeps the RAM buffer disabled. Bit 0 is provided for use by the driver software (to identify availability when multiple cards are used in the same system).

## 2.1.3 POS[4] Register

| Bit | Bit Assignment |

|-----|----------------|

| 7   | LA19           |

| 6   | LA18           |

| 5   | LA17           |

| 4   | LA16           |

| 3   | LA15           |

| 2   | LA14           |

| 1   | BE1            |

| 0   | BE0            |

If a D0h is written in POS[4], the BIOS ROM space is placed in the range 0D0000h - 0D3FFFh. This is one of 64 possible 16-Kbyte ranges. It is intended to place the BIOS ROM in the general range, 0C0000h - 0DFFFFh.

### Bit (7:2)

These bits are used to set the BIOS ROM location for the application.

#### Bit (1:0)

BIOS Size/Enable.

Bits 1 and 0 are used to set the size of the BIOS ROM and, when necessary, to disable it as follows:

| BE1 | BE0 | FUNCTION          |

|-----|-----|-------------------|

| 0   | 0   | BIOS is 16 Kbytes |

| 0   | 1   | BIOS is 32 Kbytes |

| 1   | 0   | BIOS is Disabled  |

| 1   | 1   | BIOS is 64 Kbytes |

## 2.2 Other POS Functions ! POS[5] Register

POS[5] provides bits that increase memory size, divide the BSCK clock by "2" (for internal use), and enable /disable interrupts to the host.

| Bit | Bit Assignment |

|-----|----------------|

| 7   | СНСК           |

| 6   | СНСК           |

| 5   | N/A            |

| 4   | N/A            |

| 3   | MSE            |

| 2   | CDIV           |

| 1   | IEN1           |

| 0   | IENO           |

## Bit (7)

Active Indicator (Micro Channel defined).

## Bit (6)

Status Available Indicator (Micro Channel defined).

## Bit (5:4)

Not applicable.

## Bit 3

Memory Size Enable.

When set to "1", this bit increases the memory size from  $8 \times 16$  Kbytes to  $32 \times 16$  Kbytes.

## Bit 2

Clock Divider.

This bit, when reset, divides the BSCK clock by "2" for internal use. When the system is powered off, the bit is reset.

## Bit (1:0)

Interrupt Enable.

Together, these bits enable/disable the interrupts to the host, and determine the level of the interrupt as follows.

| IEN1 | IEN0 | FUNCTION                |

|------|------|-------------------------|

| 0    | 0    | Interrupt level is IRQ0 |

| 0    | 1    | Interrupt level is IRQ1 |

| 1    | 0    | Interrupt level is IRQ2 |

| 1    | 1    | Interrupt level is IRQ3 |

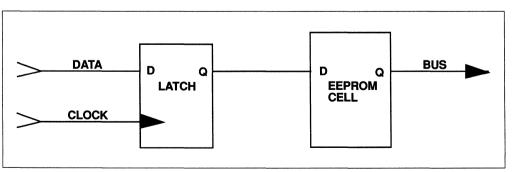

## 3.0 PROGRAMMING THE EEPROM REGISTERS

The WD83C593 contains ten, internal eight-bit registers implemented in EEPROM technology (see Table B-2). These registers contain random data when the device is shipped from the factory and must be programmed by you for your application. If they are not, the device will not function properly.

To initially program the EEPROM registers, you must write the data to be sorted to each register. Figure 3-1 illustrates a typical EEPROM register bit cell. Data is stored in the latch and its output is presented to the input of the EEPROM cell. Once the data is stored in the registers, you must write the following to the EEPROM control register: A5h (followed by) 00h. It is important that you write the numbers in the order given. This starts the programming process of all ten EEPROM registers with data stored in the latches. The program operation requires a maximum of 20 milliseconds to complete. During this time, it is important that you do not access any of the registers in the device. Refer to Appendix B for more information on the **EEPROM** registers.

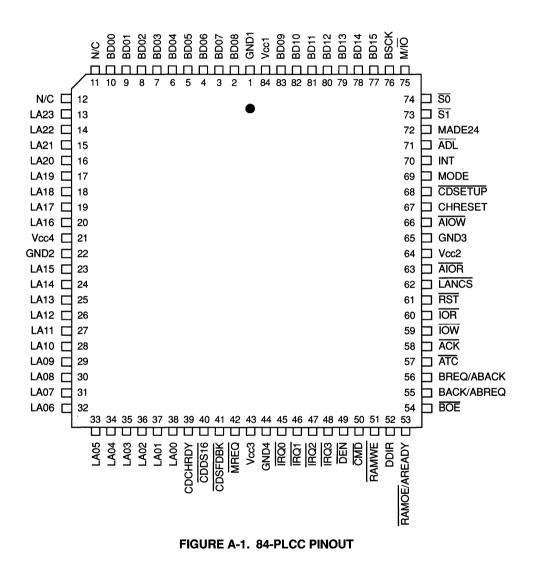

# **APPENDIX A -- PIN DESIGNATIONS**

Figure A-1 illustrates the 84-pin PLCC device. Table A-1 lists all pin designations.

| PIN<br>NO.     | PIN<br>NAME             | SIGNAL NAME/<br>DESCRIPTION                                                                                                                                                                                                                                                                                |

|----------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host N         | licro Channel Bus Signa | ls                                                                                                                                                                                                                                                                                                         |

| 2-10<br>77-83  | BD00-BDI5 (I/O)         | HOST MICRO CHANNEL DATA BUS: This bus needs to be externally buffered.                                                                                                                                                                                                                                     |

| 11             | REFRESH (I)             | REFRESH CYCLE: Input from host system. Indicates when a system memory refresh cycle is taking place.                                                                                                                                                                                                       |

| 15-20<br>23-38 | LA00-LA21 (I)           | HOST MICRO CHANNEL ADDRESS LINES: These are the 20 bits of the host Micro Channel address lines.                                                                                                                                                                                                           |

| 39             | CDCHRDY (O)             | CHANNEL READY: This output, normally active, is pulled inactive to allow additional time to complete a channel operation. The maximum time that this line can be held inactive is $3.5 \ \mu$ sec.                                                                                                         |

| 40             | CDDS16 (O)              | CARD DATA SIZE 16: This output is used to indicate to the host Micro Channel that the current data transfer is 16 bits wide. It is derived from a valid address decode.                                                                                                                                    |

| 41             | CDSFDBK (O)             | CARD SELECTED FEEDBACK: This output is asserted as<br>an acknowledgement when an I/O or memory device on the<br>LAN card is selected.                                                                                                                                                                      |

| 45-48          | IRQ0-3 (O)              | INTERRUPT REQUEST: These outputs tell the host micro-<br>processor that an interrupt has occurred and the LAN card<br>needs attention.                                                                                                                                                                     |

| 50             | CMD (I)                 | COMMAND: This input is used to define when data is valid on the data bus. The trailing edge of the signal indicates the end of the bus cycle.                                                                                                                                                              |

| 67             | CHRESET (I)             | CHANNEL RESET: This signal is generated by the host when the host Micro Channel is powered up.                                                                                                                                                                                                             |

| 68             | CDSETUP (I)             | CARD SETUP: This input is generated by the host logic to<br>individually select channel connectors during system<br>configuration and error recovery procedures. This input,<br>together with LAO-LA2, is used to access the POS<br>registers. The CDSFDBK output is not asserted during<br>configuration. |

## TABLE A-1. PIN DESCRIPTIONS

| PIN<br>NO. | PIN<br>NAME               | SIGNAL NAME/<br>DESCRIPTION                                                                                                                                                                                                               |  |  |  |  |

|------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Host N     | licro Channel Bus Signals | s, Cont.                                                                                                                                                                                                                                  |  |  |  |  |

| 71         | ADL (I)                   | ADDRESS DECODE LATCH: This input is used to<br>indicate that the Micro Channel addresses are to be<br>latched. The trailing edge is used.                                                                                                 |  |  |  |  |

| 72         | MADE24 (I)                | MEMORY ADDRESS ENABLE 24: This input, when active, indicates that an unextended address space equal to or less than 16M is present on the address bus.                                                                                    |  |  |  |  |

| 74, 73     | <u>50, 51</u> (I)         | STATUS BITS 0 AND 1: These inputs indicate the start of<br>a channel cycle and also define the type of channel cycle<br>as follows.                                                                                                       |  |  |  |  |

|            |                           | M/IO S0 S1 TYPE   0 0 0 Reserved A   0 0 1 I/O Write   0 1 0 I/O Read   0 1 1 Reserved B   1 0 0 Reserved C   1 0 1 Memory Write   1 1 0 Memory Read   1 1 1 Reserved D                                                                   |  |  |  |  |

| 75         | M/ <del>IO</del> (I)      | MEMORY/INPUT OUTPUT: This input distinguishes a memory cycle from an I/O cycle.                                                                                                                                                           |  |  |  |  |

| LAN C      | ontroller Signals         |                                                                                                                                                                                                                                           |  |  |  |  |

| 55         | BACK/ABREQ (O)            | LAN BUS ACKNOWLEDGE: This output is generated to<br>acknowledge a LAN BUS REQUEST.                                                                                                                                                        |  |  |  |  |

| 56         | BREQ/ABACK (I)            | LAN BUS REQUEST: This input is generated by the LAN controller to indicate that a DMA transfer is needed. It is automatically generated when the LAN controller's FIFO buffers need servicing.                                            |  |  |  |  |

| 58         | ACK (I)                   | LAN SLAVE I/O ACKNOWLEDGE: This input is asserted<br>by the LAN chip when it grants access to its internal<br>registers. The input is used to insert wait states until the<br>LAN is synchronized for a register read or write operation. |  |  |  |  |

| 59         | IOW (O)                   | LAN I/O WRITE: This output, together with LANCS, is used to write to the internal LAN registers.                                                                                                                                          |  |  |  |  |

## TABLE A-1. PIN DESCRIPTIONS (Continued)

| PIN<br>NO. | PIN<br>NAME              | SIGNAL NAME/<br>DESCRIPTION                                                                                                                                                                                                            |

|------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAN C      | ontroller Signals, Cont. |                                                                                                                                                                                                                                        |

| 60         | IOR (O)                  | LAN I/O READ: This output, together with LANCS, is used to read the internal LAN registers.                                                                                                                                            |

| 61         | RST (O)                  | LAN RESET: This output places the LAN in reset mode immediately. No packets are received or transmitted by the LAN until the STA bit in the LAN is set.                                                                                |

| 62         | LANCS (O)                | LAN CHIP SELECT: This output places the LAN device in slave mode for access to internal registers.                                                                                                                                     |

| 70         | INT (I)                  | LAN INTERRUPT: This input indicates that the LAN controller needs host attention (at the end of an operation, when an error occurs, etc.).                                                                                             |

| 76         | BSCK (I)                 | CLOCK: This input is the 40-MHz clock.                                                                                                                                                                                                 |

| 69         | MODE (I)                 | ALTERNATE MODE SELECT: This input must be left open<br>(internally pulled high). It signifies that the WD83C593 is<br>being used on a non-intelligent board, directly interfacing<br>the WD83C690 LAN controller to the buffer memory. |

| RAM S      | bignals                  |                                                                                                                                                                                                                                        |

| 51         | RAMWE (O)                | RAM WRITE ENABLE: This output is used to write host data into the buffer RAM.                                                                                                                                                          |

| 53         | RAMOE/AREADY (O)         | RAM OUTPUT ENABLE: This output is used to gate the buffer RAM onto the data bus, BD00-BD15.                                                                                                                                            |

| ROM S      | Signal                   |                                                                                                                                                                                                                                        |

| 54         | BOE (O)                  | BIOS ROM OUTPUT ENABLE: This output is the chip select for the BIOS ROM. It gates data onto BD0-BD7.                                                                                                                                   |

| Buffer     | Control Signals          | · · · ·                                                                                                                                                                                                                                |

| 42         | MREQ (O)                 | MEMORY REQUEST: This output is provided for use in a possible memory mapped scheme. This is an unlatched memory decode indicator.                                                                                                      |

| 49         | DEN (O)                  | DATA BUFFER ENABLE: This output is generated to enable or disable the external bidirectional data buffers.                                                                                                                             |

## TABLE A-1. PIN DESCRIPTIONS (Continued)

٠

.

.

| PIN<br>NO.      | PIN<br>NAME | SIGNAL NAME/<br>DESCRIPTION                                                                                                                                       |

|-----------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52              | DDIR (O)    | DATA DIRECTION: This output is generated to control the direction of the external bidirectional buffers between the host data bus and DB00-DB15 (local data bus). |

| Power           | <b>.</b>    |                                                                                                                                                                   |

| 21,43,<br>64,84 | Vcc         | +5V dc                                                                                                                                                            |

| 1,22,<br>44,65  | GND         | GROUND.                                                                                                                                                           |

| No Cor          | nection     |                                                                                                                                                                   |

| 11,12           | N/C         | Pins 11, 12 must be left open. They are used for factory testing.                                                                                                 |

TABLE A-1. PIN DESCRIPTIONS (Continued)

## **APPENDIX B -- REGISTER DESIGNATIONS**

This appendix provides information on the WD83C593's internal registers. Table B-1 sum-

marizes the I/O mapping, and the remainder of the appendix describes each register in detail.

| Туре       | Name                                                      |

|------------|-----------------------------------------------------------|

| R/W        | Memory Enable, Reset Register (MER)                       |

| W          | EEPROM Control Register (EEC)                             |

| R (EEPROM) | Reserved (PID0)                                           |

| R (EEPROM) | Reserved (PID1)                                           |

| R/W        | Internal Mask and Command Control Register (IMCCR)        |

| R/W        | General Purpose Register (GPR)                            |

| R (EEPROM) | LAN Address Registers (LAR)                               |

| R/W        | LAN Controller Registers (LAN)                            |

|            | W<br>R (EEPROM)<br>R (EEPROM)<br>R/W<br>R/W<br>R (EEPROM) |

#### TABLE B-1. INTERNAL REGISTER I/O MAP

| Name: MEMORY ENABLE, RESET (MER) |                                                                                                                                                                                                                                              |                             |                          |                              | <b>Offset:</b> 0x00        |               |                    |                                             |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------|------------------------------|----------------------------|---------------|--------------------|---------------------------------------------|

|                                  | AN contro                                                                                                                                                                                                                                    | ller, as well<br>Micro Char | as the otl<br>nel to sha | her register<br>are the on-t | s (except L<br>board buffe | AR, PID0,     | PID1 and F         | ter 1 μsec,<br>EX). Setting<br>cleared, RAM |

|                                  | bit7<br>REST                                                                                                                                                                                                                                 | bit6<br>MENB                | bit5<br>N/A              | bit4<br>N/A                  | bit3<br>N/A                | bit2<br>N/A   | bit1<br>N/A        | bit0<br>N/A                                 |

| Name: EE                         | PROM CO                                                                                                                                                                                                                                      | NTROL (EI                   | EC)                      |                              |                            | Of            | fset: 0x01         |                                             |

| EEPROM r                         | Description: Writing A5h first and then 00h to this register starts the program process for theEEPROM registers. See the EEPROM programming instructions for a detailed description on howthis register is used.bit7bit6bit5bit4bit2bit1bit0 |                             |                          |                              |                            |               |                    |                                             |

|                                  | 1                                                                                                                                                                                                                                            | 0                           | 1                        | 0                            | 0                          | 1             | 0                  | 1                                           |

| Name: R                          | ESERVED                                                                                                                                                                                                                                      | (PID0)                      |                          |                              |                            | Off           | iset: 0x02         | <u> </u>                                    |

| Descriptio<br>numbers.           | <b>n:</b> This wri                                                                                                                                                                                                                           | te-only regi                | ster is use              | ed only by r                 | nanufacturi                | ing to set th | ne Micro Ch        | annel POS ID                                |

| Name: R                          | ESERVED                                                                                                                                                                                                                                      | (PID1)                      |                          |                              |                            | Of            | i <b>set:</b> 0x03 |                                             |

| Descriptio<br>numbers.           | <b>n:</b> This wri                                                                                                                                                                                                                           | te-only regi                | ster is use              | ed only by r                 | nanufacturi                | ing to set th | ne Micro Ch        | annel POS ID                                |

## **TABLE B-2. REGISTER DESCRIPTIONS**

| Name: INT<br>REG          |             | MASK AND<br>(IMCCR) | COMMAN     | D CONTR     | OL          | Offset:     | 0x05             |                                       |

|---------------------------|-------------|---------------------|------------|-------------|-------------|-------------|------------------|---------------------------------------|

| Description               | n: Bit 2 is | s cleared wl        | nen the ho | st Micro Ch | annel is po | wered off o | r undergoe       | es a soft reset.                      |

|                           | bit7<br>-   | bit6<br>-           | bit5<br>-  | bit4<br>-   | bit3<br>-   | bit2<br>EIL | bit1<br>-        | bit0<br>-                             |

| Note:                     |             |                     |            |             |             |             |                  |                                       |

| bit2 (EIL)                |             |                     |            |             |             |             |                  | oller to the host<br>the interrupt.   |

| Name: GE                  | NERALF      | PURPOSE I           | REGISTEF   | (GPR)       |             | Off         | set: 0X07        |                                       |

| Description               | n: This is  | s an 8-bit wi       | de genera  | purpose re  | egister.    |             |                  | · · · · · · · · · · · · · · · · · · · |

| Name: LAN                 |             | ESS REGIS           | TERS (LA   | R)          |             | Off         | set: 0X08        | - 0X0F                                |

| Description               |             |                     |            |             |             | permanentl  | y stored in      | the                                   |

| Name: LAN                 |             | ROLLER RE           | GISTERS    | (LAN)       |             | Off         | <b>set:</b> 0X10 | - 0X1F                                |

| Description<br>decode and |             |                     |            |             |             | he LAN coi  | ntroller chip    | o. Only the                           |

|                           |             | TABLE               | B-2. REG   | ISTER DE    | SCRIPTION   | IS (Contin  | ued)             |                                       |

# **APPENDIX C - ELECTRICAL CHARACTERISTICS**

Table C-1 lists the dc electrical parameters for the WD83C593, Table C-2 lists the non-operational

specifications, and Table C-3 lists the operational specifications.

Ta =  $0^{\circ}$ C (32°F) to 70°C (158°F), Vcc = 5V % 10%

| SYMBOL          | CHARACTERISTIC                                                        | MIN | ТҮР | MAX  | UNITS | CONDITIONS                        |

|-----------------|-----------------------------------------------------------------------|-----|-----|------|-------|-----------------------------------|

| IDD             | V <sub>DD</sub> Supply Current                                        | -   | 8   | 10   | mA    | -                                 |

| V <sub>DD</sub> | Voltage Supply                                                        | 4.5 | 5   | 5.5  | V     | -                                 |

| VIH             | Input High Voltage                                                    | 2.0 | -   | -    | V     | -                                 |

| VIL             | Input Low Voltage                                                     | -   | -   | 0.8  | ۷     | -                                 |

| Voн             | Output High Voltage                                                   | 2.4 | -   | -    | V     | note 1                            |

| Vol             | Output Low Voltage                                                    | -   | -   | 0.5  | ۷     | note 2                            |

| ILH             | Input Source Current                                                  | -   | -   | 0.1  | μA    | V <sub>IN</sub> = V <sub>DD</sub> |

| ILL             | Input Sink Current                                                    | -   | -   | -1.0 | μA    | V <sub>IN</sub> = 0               |

| lozh            | Tri-state High Current                                                | -10 | -   | 10   | μA    | VIN = VDD                         |

| lozl            | Tri-state Low Current                                                 | -10 |     | 10   | μA    | V <sub>IN</sub> = 0               |

| Vol             | Output Low Voltage<br>(Pins IRQ0, IRQ1,<br>IRQ2, and IRQ3)            | -   | -   | 0.5  | V     | note 3                            |

| Vol             | Output Low Voltage<br>(All pins except IRQ0,<br>IRQ1, IRQ2, and IRQ3) | -   | -   | 0.4  | V     | note 4                            |

## TABLE C-1. DC PARAMETERS

## NOTES

1.  $I_{OH} = -24$  mA on IRQ0, IRQ1, IRQ2 and IRQ3.

$I_{OH}$  = -8 mA on all other outputs and I/O pins.

2.  $I_{OL} = 0.5V$  (and 24 mA) on IRQ0, IRQ1, IRQ2, and IRQ3.

$I_{OL}$  = 0.4V (and 8 mA) on all other outputs and I/O pins.

- 3.  $I_{OL} = 24$  mA on pins IRQ0, IRQ1, IRQ2, and IRQ3.

- 4.  $I_{OL} = 8$  mA on all other outputs and I/O pins.

| PARAMETER                                             | MIN  | ТҮР | МАХ                       | UNIT                  |

|-------------------------------------------------------|------|-----|---------------------------|-----------------------|

| Storage temperature                                   | -65  | -   | 150                       | Degrees<br>Centigrade |

| Voltage on any pin<br>with respect to V <sub>SS</sub> | -0.6 | -   | Vcc + 0.3<br>(except Vpp) | Volts                 |

| Voltage on $V_{CC}$ with respect to $V_{SS}$          | -    | -   | 7.0                       | Volts                 |

TABLE C-2. NON-OPERATIONAL SPECIFICATIONS

| PARAMETER                                                         | MIN  | ТҮР | MAX  | UNIT                  |

|-------------------------------------------------------------------|------|-----|------|-----------------------|

| Ambient temperature                                               | 0    | 25  | 70   | Degrees<br>Centigrade |

| Humidity                                                          | 20   | -   | 95   | Percent               |

| V <sub>CC</sub> supply voltage<br>with respect to V <sub>SS</sub> | 4.50 | 5.0 | 5.50 | Volts                 |

| Icc supply current<br>(full loading)                              | -    | -   | 100  | Milliamps             |

| Power dissipation                                                 | -    | -   | 500  | Milliwatts            |

**TABLE C-3. OPERATIONAL SPECIFICATIONS**

# **APPENDIX D - AC OPERATING CHARACTERISTICS**

This appendix provides information on the WD83C593's ac operating characteristics. Table

D-1 lists the ac operating characteristics. Figures D-1 and D-2 illustrate timing information.

| SYMBOL          | PARAMETER                                                 | MIN | MAX | UNITS |

|-----------------|-----------------------------------------------------------|-----|-----|-------|

| t1              | Status active low from<br>ADDRESS, M/IO, REFRESH<br>valid | 10  | -   | nsec  |

| t <sub>2</sub>  | CMD active low from status active low                     | 55  | -   | nsec  |

| t3              | ADL active low from<br>ADDRESS M/IO, REFRESH<br>valid     | 45  | -   | nsec  |

| t4              | ADL active low to CMD active low                          | 40  | -   | nsec  |

| t5              | CDDS16 active low from<br>ADDRESS, M/IO, REFRESH<br>valid | _   | 55  | nsec  |

| t <sub>6</sub>  | CDSFDBK and CDCHRDY<br>low from ADDRESS valid             | -   | 60  | nsec  |

| t7              | CMD active low from<br>ADDRESS valid                      | 85  | -   | nsec  |

| t <sub>8</sub>  | CMD pulse width                                           | 90  | -   | nsec  |

| t9              | Write data setup to CMD active low                        | 0   | -   | nsec  |

| t <sub>10</sub> | Write data hold time from<br>CMD high (at the PS/2 bus)   | 30  | -   | nsec  |

| t11             | Read data setup time to<br>CMD high (at the PS/2 bus)     | 60  | -   | nsec  |

| t <sub>12</sub> | Read data hold time from<br>CMD high (at the PS/2 bus)    | 5   | -   | nsec  |

## TABLE D-1. AC OPERATING CHARACTERISTICS

| SYMBOL                         | PARAMETER                                                                                             | MIN               | MAX                            | UNITS |

|--------------------------------|-------------------------------------------------------------------------------------------------------|-------------------|--------------------------------|-------|

| t13                            | CMD high to RAMOE or RAMWE high                                                                       | 0                 | -                              | nsec  |

| t <sub>14</sub><br>WRITE CYCLE | CMD high to DEN high (during WRITE)                                                                   | 15                | -                              | nsec  |

| t14<br>READ CYCLE              | CMD high to DEN high (during READ)                                                                    | -                 | 25                             | nsec  |

| t15                            | CMD high to DDIR low                                                                                  | 0                 | -                              | nsec  |

| t16                            | DDIR low to pulse*<br>(read cycles only)                                                              | 0                 | -                              | nsec  |

| t17                            | BREQ active high to BACK active high                                                                  | 1 clk cyc<br>time | -                              |       |

| t18                            | BREQ low to BACK low                                                                                  | 1 clk cyc<br>time | 3 clk cyc<br>time + 25<br>nsec |       |

| t19                            | LANCS active low to IOR or IOW active low                                                             | 0                 | -                              | nsec  |

| t20                            | $\overline{\text{ACK}}$ active low from $\overline{\text{IOR}}$ or $\overline{\text{IOW}}$ active low | 0                 | -                              | nsec  |

| t <sub>21</sub>                | ACK high from IOR or IOW high                                                                         | 0                 | -                              | nsec  |

| t22                            | CDSETUP active low to<br>ADL active low                                                               | 15                | -                              | nsec  |

| t23                            | CDSETUP hold from ADL high                                                                            | 25                | -                              | nsec  |

| t24                            | CDCHRDY inactive low from CDSETUP active low                                                          | -                 | 100                            | nsec  |

| t25                            | CDSETUP hold from CMD active low                                                                      | 30                | -                              | nsec  |

TABLE D-1. AC OPERATING CHARACTERISTICS (Continued)

\*The pulse occurs on the DEN line, when the DDIR signal goes low during read cycles.

FIGURE D-1. HOST-MEMORY READ/WRITE TIMING

FIGURE D-2. SET-UP TIMING