# Peak Reducing EMI Solution

#### **Features**

- Cypress PREMIS™ family offering

- . Generates an EMI optimized clocking signal at the out-

- Selectable input to output frequency

- Single 1.25% or 3.75% down or center spread output

- · Integrated loop filter components

- · Operates with a 3.3V or 5V supply

- Low power CMOS design

- Available in 8-pin SOIC (Small Outline Integrated Circuit)

### **Key Specifications**

| Supply Voltages:              |                                   |

|-------------------------------|-----------------------------------|

| Frequency Range:              | 28 MHz ≤ F <sub>in</sub> ≤ 75 MHz |

| Crystal Reference Range       | 28 MHz ≤ F <sub>in</sub> ≤ 40 MHz |

| Cycle to Cycle Jitter:        | 300 ps (max.)                     |

| Selectable Spread Percentage: | 1.25% or 3.75%                    |

| Output Duty Cycle:            | 40/60% (worst case)               |

| Output Rise and Fall Time:    | 5 ns (max.)                       |

**Table 1. Modulation Width Selection**

| SS% | W181I-01, 02, 03<br>Output                                   | W181I-51, 52, 53<br>Output                              |

|-----|--------------------------------------------------------------|---------------------------------------------------------|

| 0   | F <sub>in</sub> ≥ F <sub>out</sub> ≥ F <sub>in</sub> − 1.25% | $F_{in} + 0.625\% \ge F_{in} \ge -0.625\%$              |

| 1   | $F_{in} \ge F_{out} \ge F_{in} - 3.75\%$                     | F <sub>in</sub> + 1.875% ≥ F <sub>in</sub> ≥<br>-1.875% |

**Table 2. Frequency Range Selection**

|     |     |                           | W181I Option#          | !                         |

|-----|-----|---------------------------|------------------------|---------------------------|

| FS2 | FS1 | -01, 51<br>(MHz)          | -02, 52<br>(MHz)       | -03, 53<br>(MHz)          |

| 0   | 0   | $28 \le F_{IN} \le 36$    | $28 \le F_{IN} \le 36$ | N/A                       |

| 0   | 1   | $36 \le F_{IN} \le 48$    | $36 \le F_{IN} \le 48$ | N/A                       |

| 1   | 0   | 46 ≤ F <sub>IN</sub> ≤ 57 | N/A                    | 46 ≤ F <sub>IN</sub> ≤ 57 |

| 1   | 1   | 57 ≤ F <sub>IN</sub> ≤ 75 | N/A                    | 57 ≤ F <sub>IN</sub> ≤ 75 |

PREMIS is a trademark of Cypress Semiconductor Corporation.

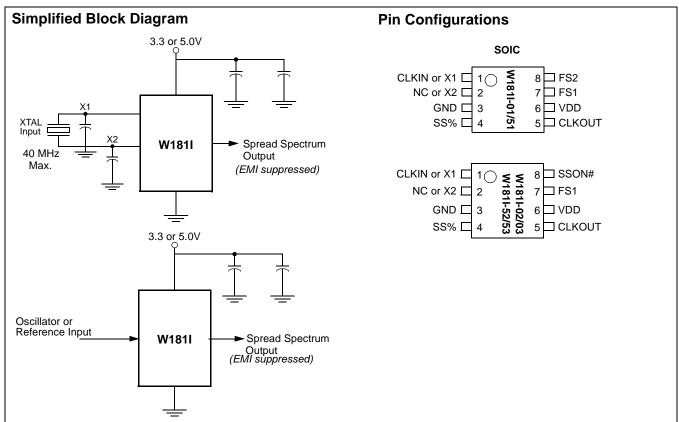

## **Pin Definitions**

| Pin Name    | Pin No.<br>(SOIC) | Pin<br>Type | Pin Description                                                                                                                                                                                                               |  |  |

|-------------|-------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CLKOUT      | 5                 | 0           | Output Modulated Frequency: Frequency modulated copy of the unmodulated input clock (SSON# asserted).                                                                                                                         |  |  |

| CLKIN or X1 | 1                 | I           | Crystal Connection or External Reference Frequency Input: This pin has dual functions. It may either be connected to an external crysta or to an external reference clock.                                                    |  |  |

| NC or X2    | 2                 | I           | Crystal Connection: If using an external reference, this pin must be left unconnected.                                                                                                                                        |  |  |

| SSON#       | 8(02/03/52/53     | I           | <b>Spread Spectrum Control (Active LOW):</b> Asserting this signal (active LOW) turns the internal modulation waveform on. This pin has an internal pull-down resistor.                                                       |  |  |

| FS1:2       | 7, 8 (01/51)      | I           | Frequency Selection Bit(s) 1 and 2: These pins select the frequency range of operation. Refer to Table 2. These pins have internal pull-up resistors.                                                                         |  |  |

| SS%         | 4                 | I           | Modulation Width Selection: When Spread Spectrum feature is turn on, this pin is used to select the amount of variation and peak EMI reduction that is desired on the output signal. This pin has an intern pull-up resistor. |  |  |

| VDD         | 6                 | Р           | Power Connection: Connected to 3.3V or 5V power supply.                                                                                                                                                                       |  |  |

| GND         | 3                 | G           | <b>Ground Connection:</b> Connect all ground pins to the common system ground plane.                                                                                                                                          |  |  |

#### Overview

The W181I products are one series of devices in the Cypress PREMIS family. The PREMIS family incorporates the latest advances in PLL spread spectrum frequency synthesizer techniques. By frequency modulating the output with a low-frequency carrier, peak EMI is greatly reduced. Use of this technology allows systems to pass increasingly difficult EMI testing without resorting to costly shielding or redesign.

In a system, not only is EMI reduced in the various clock lines, but also in all signals which are synchronized to the clock. Therefore, the benefits of using this technology increase with the number of address and data lines in the system. The Simplified Block Diagram on page 1 shows a simple implementation.

### **Functional Description**

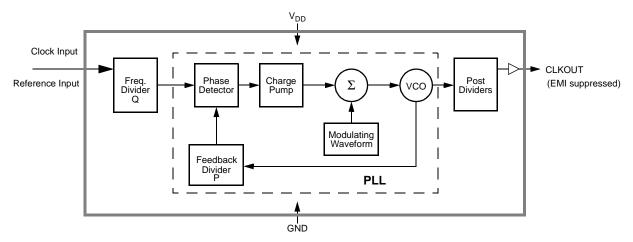

The W181I uses a Phase-Locked Loop (PLL) to frequency modulate an input clock. The result is an output clock whose frequency is slowly swept over a narrow band near the input signal. The basic circuit topology is shown in *Figure 1*. The input reference signal is divided by Q and fed to the phase detector. A signal from the VCO is divided by P and fed back to the phase detector also. The PLL will force the frequency of the VCO output signal to change until the divided output signal and the divided reference signal match at the phase detector input. The output frequency is then equal to the ratio of P/Q

times the reference frequency. (Note: For the W181I the output frequency is equal to the input frequency.) The unique feature of the Spread Spectrum Frequency Timing Generator is that a modulating waveform is superimposed at the input to the VCO. This causes the VCO output to be slowly swept across a predetermined frequency band.

Because the modulating frequency is typically 1000 times slower than the fundamental clock, the spread spectrum process has little impact on system performance.

#### **Frequency Selection With SSFTG**

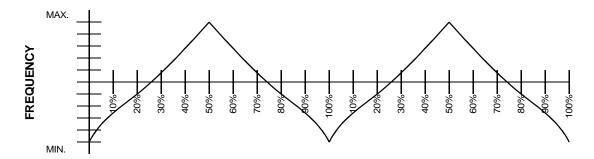

In Spread Spectrum Frequency Timing Generation, EMI reduction depends on the shape, modulation percentage, and frequency of the modulating waveform. While the shape and frequency of the modulating waveform are fixed for a given frequency, the modulation percentage may be varied.

Using frequency select bits (FS1:2 pins), the frequency range can be set. Spreading percentage is set to be 1.25% or 3.75% (see *Table 1*).

A larger spreading percentage improves EMI reduction. However, large spread percentages may either exceed system maximum frequency ratings or lower the average frequency to a point where performance is affected. For these reasons, spreading percentages between 0.5% and 2.5% are most common.

Figure 1. Functional Block Diagram

# **Spread Spectrum Frequency Timing Generation**

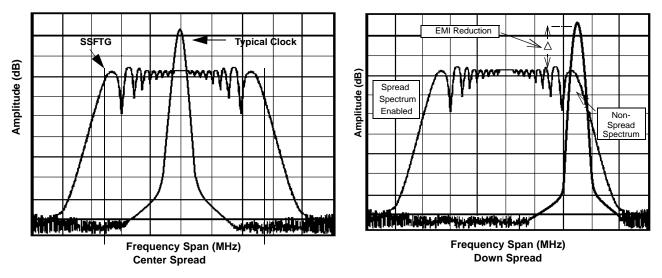

The device generates a clock that is frequency modulated in order to increase the bandwidth that it occupies. By increasing the bandwidth of the fundamental and its harmonics, the amplitudes of the radiated electromagnetic emissions are reduced. This effect is depicted in *Figure 2*.

As shown in *Figure 2*, a harmonic of a modulated clock has a much lower amplitude than that of an unmodulated signal. The reduction in amplitude is dependent on the harmonic number and the frequency deviation or spread. The equation for the reduction is:

$$dB = 6.5 + 9*log_{10}(P) + 9*log_{10}(F)$$

Where P is the percentage of deviation and F is the frequency in MHz where the reduction is measured.

The output clock is modulated with a waveform depicted in *Figure 3*. This waveform, as discussed in "Spread Spectrum Clock Generation for the Reduction of Radiated Emissions" by Bush, Fessler, and Hardin produces the maximum reduction in the amplitude of radiated electromagnetic emissions. *Figure 3* details the Cypress spreading pattern. Cypress does offer options with more spread and greater EMI reduction. Contact your local Sales representative for details on these devices.

Figure 2. Clock Harmonic with and without SSCG Modulation Frequency Domain Representation

Figure 3. Typical Modulation Profile

# Absolute Maximum Ratings[1]

Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.

| Parameter           | Description                            | Rating       | Unit |

|---------------------|----------------------------------------|--------------|------|

| $V_{DD}$ , $V_{IN}$ | Voltage on any pin with respect to GND | -0.5 to +7.0 | V    |

| T <sub>STG</sub>    | Storage Temperature                    | -65 to +150  | °C   |

| T <sub>A</sub>      | Operating Temperature                  | -40 to +85   | °C   |

| T <sub>B</sub>      | Ambient Temperature under Bias         | -55 to +125  | °C   |

| P <sub>D</sub>      | Power Dissipation                      | 0.5          | W    |

# DC Electrical Characteristics: -40°C < $T_A$ < +85°C, $V_{DD}$ = 3.3V $\pm 5\%$

| Parameter        | Description            | Test Condition                               | Min. | Тур. | Max. | Unit |

|------------------|------------------------|----------------------------------------------|------|------|------|------|

| I <sub>DD</sub>  | Supply Current         |                                              |      | 18   | 32   | mA   |

| t <sub>ON</sub>  | Power-Up Time          | First locked clock cycle after Power<br>Good |      |      | 5    | ms   |

| V <sub>IL</sub>  | Input Low Voltage      |                                              |      |      | 0.8  | V    |

| V <sub>IH</sub>  | Input High Voltage     |                                              | 2.4  |      |      | V    |

| V <sub>OL</sub>  | Output Low Voltage     |                                              |      |      | 0.4  | V    |

| V <sub>OH</sub>  | Output High Voltage    |                                              | 2.4  |      |      | V    |

| I <sub>IL</sub>  | Input Low Current      | Note [2]                                     |      |      | -100 | μΑ   |

| I <sub>IH</sub>  | Input High Current     | Note [2]                                     |      |      | 10   | μΑ   |

| I <sub>OL</sub>  | Output Low Current     | @ 0.4V, V <sub>DD</sub> = 3.3V               |      | 15   |      | mA   |

| I <sub>OH</sub>  | Output High Current    | @ 2.4V, V <sub>DD</sub> = 3.3V               |      | 15   |      | mA   |

| C <sub>I</sub>   | Input Capacitance      | All pins except CLKIN                        |      |      | 7    | pF   |

| C <sub>I</sub>   | Input Capacitance      | CLKIN pin only                               |      | 6    | 10   | pF   |

| R <sub>P</sub>   | Input Pull-Up Resistor |                                              |      | 500  |      | kΩ   |

| Z <sub>OUT</sub> | Clock Output Impedance |                                              |      | 25   |      | Ω    |

#### Note:

Single Power Supply: The voltage on any input or I/O pin cannot exceed the power pin during power-up.

Inputs FS1:2 have a pull-up resistor; Input SSON# has a pull-down resistor.

# DC Electrical Characteristics: $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}, \ \text{V}_{\text{DD}} = 5\text{V} \pm 10\%$

| Parameter        | Description            | Test Condition                               | Min.               | Тур. | Max.                | Unit |

|------------------|------------------------|----------------------------------------------|--------------------|------|---------------------|------|

| I <sub>DD</sub>  | Supply Current         |                                              |                    | 30   | 50                  | mA   |

| t <sub>ON</sub>  | Power-Up Time          | First locked clock cycle after<br>Power Good |                    |      | 5                   | ms   |

| V <sub>IL</sub>  | Input Low Voltage      |                                              |                    |      | 0.15V <sub>DD</sub> | V    |

| V <sub>IH</sub>  | Input High Voltage     |                                              | 0.7V <sub>DD</sub> |      |                     | V    |

| V <sub>OL</sub>  | Output Low Voltage     |                                              |                    |      | 0.4                 | V    |

| V <sub>OH</sub>  | Output High Voltage    |                                              | 2.4                |      |                     | V    |

| I <sub>IL</sub>  | Input Low Current      | Note [2]                                     |                    |      | -100                | μΑ   |

| I <sub>IH</sub>  | Input High Current     | Note [2]                                     |                    |      | 10                  | μΑ   |

| I <sub>OL</sub>  | Output Low Current     | @ 0.4V, V <sub>DD</sub> = 5V                 |                    | 24   |                     | mA   |

| I <sub>OH</sub>  | Output High Current    | @ 2.4V, V <sub>DD</sub> = 5V                 |                    | 24   |                     | mA   |

| C <sub>I</sub>   | Input Capacitance      | All pins except CLKIN                        |                    |      | 7                   | pF   |

| C <sub>I</sub>   | Input Capacitance      | CLKIN pin only                               |                    | 6    | 10                  | pF   |

| R <sub>P</sub>   | Input Pull-Up Resistor |                                              |                    | 500  |                     | kΩ   |

| Z <sub>OUT</sub> | Clock Output Impedance |                                              |                    | 25   |                     | Ω    |

# AC Electrical Characteristics: $T_A = -40 \, ^{\circ} C < T_A < +85 \, ^{\circ} C, \ V_{DD} = 3.3 V \pm 5 \% \ or \ 5 V \pm 10 \% \ or$

| Parameter         | Description            | Description Test Condition Mi                                                         |    | Тур. | Max. | Unit |

|-------------------|------------------------|---------------------------------------------------------------------------------------|----|------|------|------|

| f <sub>IN</sub>   | Input Frequency        | Input Clock                                                                           | 28 |      | 75   | MHz  |

| f <sub>OUT</sub>  | Output Frequency       | Spread Off                                                                            | 28 |      | 75   | MHz  |

| t <sub>R</sub>    | Output Rise Time       | V <sub>DD</sub> , 15-pF load 0.8V-2.4V                                                |    | 2    | 5    | ns   |

| t <sub>F</sub>    | Output Fall Time       | V <sub>DD</sub> , 15-pF load 2.4V–0.8V                                                |    | 2    | 5    | ns   |

| t <sub>OD</sub>   | Output Duty Cycle      | 15-pF load                                                                            | 40 |      | 60   | %    |

| t <sub>ID</sub>   | Input Duty Cycle       |                                                                                       | 40 |      | 60   | %    |

| t <sub>JCYC</sub> | Jitter, Cycle-to-Cycle |                                                                                       |    | 250  | 300  | ps   |

|                   | Harmonic Reduction     | f <sub>out</sub> = 40 MHz, third harmonic<br>measured, reference board,<br>15-pF load | 8  |      |      | dB   |

### **Application Information**

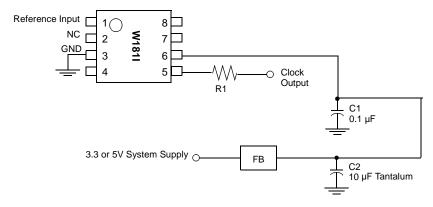

### **Recommended Circuit Configuration**

For optimum performance in system applications the power supply decoupling scheme shown in *Figure 4* should be used.

$V_{DD}$  decoupling is important to both reduce phase jitter and EMI radiation. The 0.1- $\!\mu F$  decoupling capacitor should be placed as close to the  $V_{DD}$  pin as possible, otherwise the in-

creased trace inductance will negate its decoupling capability. The 10- $\mu$ F decoupling capacitor shown should be a tantalum type. For further EMI protection, the V<sub>DD</sub> connection can be made via a ferrite bead, as shown.

### **Recommended Board Layout**

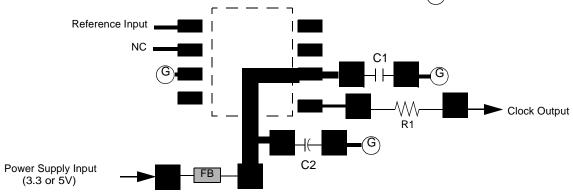

Figure 5 shows a recommended 2-layer board layout.

Figure 4. Recommended Circuit Configuration

- C1 = High frequency supply decoupling capacitor (0.1-µF recommended).

- C2 = Common supply low frequency decoupling capacitor (10-µF tantalum recommended).

- R1 = Match value to line impedance

- FB = Ferrite Bead

- (G) = Via To GND Plane

Figure 5. Recommended Board Layout (2-Layer Board)

## **Ordering Information**

| Ordering Code | Freq. Mask<br>Code       | Package<br>Name | Package Type                 | Temperature Range               |

|---------------|--------------------------|-----------------|------------------------------|---------------------------------|

| W181I         | 01, 02, 03<br>51, 52, 53 | G               | 8-pin Plastic SOIC (150-mil) | I = Industrial (-40°C to +85°C) |

Document #: 38-07115 Rev. \*A

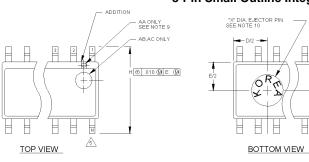

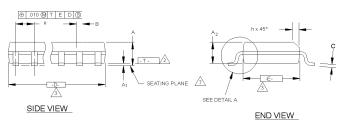

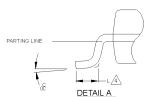

### Package Diagram

### 8-Pin Small Outline Integrated Circuit (SOIC, 150 mils)

NOTES:

- 1. MAXIMUM DIE THICKNESS ALLOWABLE IS .015.

- 2 DIMENSIONING & TOLERANCES PER ANSI.Y14.5M 1982.

- 3 "T" IS A REFERENCE DATUM.

- AT THE MOLD PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006 INCHES PER SIDE.

- 5. "L" IS THE LENGTH OF TERMINAL FOR SOLDERING TO A SUBSTRATE

- 6. "N" IS THE NUMBER OF TERMINAL POSITIONS.

- TERMINAL POSITIONS ARE SHOWN FOR

- REFERENCE ONLY.

REFERENCE ONLY.

REFERENCE ONLY.

REFERENCE ONLY.

REFERENCE ONLY.

ONE ANOTHER WITHIN .003 INCHES AT SEATING PLANE.

THE APPEARANCE OF PIN #1 I.D ON THE 8 LD IS OPTIONAL,

ROUND TYPE ON SINGLE LEADFRAME AND RECTANGULAR TYPE ON MATRIX LEADFRAME

- 10. COUNTRY OF ORIGIN LOCATION AND EJECTOR PIN ON PACKAGE BOTTOM IS OPTIONAL AND DEPEND ON ASSEMBLY LOCATION.

- 11, CONTROLLING DIMENSION: INCHES

### THIS TABLE IN INCHES

| S              |       | COMMON         |       |                | NOTE   |      | 3    |      | 5  |

|----------------|-------|----------------|-------|----------------|--------|------|------|------|----|

| M<br>B         | D     | IMENSIO        | NS    | N <sub>O</sub> | VARI-  |      | D    |      | N  |

| °L             | MIN.  | NOM.           | MAX.  | T <sub>E</sub> | ATIONS | MIN. | NOM. | MAX. |    |

| Α              | .061  | .064           | .068  |                | AA     | .189 | .194 | .196 | 8  |

| A <sub>1</sub> | .004  | .006           | .0098 |                | AB     | .337 | .342 | .344 | 14 |

| $A_2$          | .055  | .058           | .061  |                | AC     | .386 | .391 | .393 | 16 |

| В              | .0138 | .016           | .0192 |                |        |      |      |      |    |

| С              | .0075 | .008           | .0098 |                |        |      |      |      |    |

| D              | SEE   | SEE VARIATIONS |       | 3              |        |      |      |      |    |

| E              | .150  | .155           | .157  |                |        |      |      |      |    |

| е              |       | .050 BSC       |       |                |        |      |      |      |    |

| H              | .230  | .236           | .244  |                |        |      |      |      |    |

| h              | .010  | .013           | .016  |                |        |      |      |      |    |

| L              | .016  | .025           | .035  |                |        |      |      |      |    |

| Ŋ              | SEE   | VARIATION      | IS    | 5              |        |      |      |      |    |

| œ              | 0°    | 5°             | 8°    |                |        |      |      |      |    |

| X              | .085  | .093           | .100  |                |        |      | •    |      |    |

#### THIS TABLE IN MILLIMETERS

| S      |       | COMMON          |      |                  | NOTE   |      | 3    |      | 5  |

|--------|-------|-----------------|------|------------------|--------|------|------|------|----|

| M<br>B | D     | <b>IMENSION</b> | VS . | N <sub>O</sub> T | VARI-  |      | D    |      | N  |

| °L     | MIN.  | NOM.            | MAX. | T <sub>E</sub>   | ATIONS | MIN. | NOM. | MAX. |    |

| Α      | 1.55  | 1.63            | 1.73 |                  | AA     | 4.80 | 4.93 | 4.98 | 8  |

| Αı     | 0.127 | 0.15            | 0.25 |                  | AB     | 8.58 | 8.69 | 8.74 | 14 |

| $A_2$  | 1.40  | 1.47            | 1.55 |                  | AC     | 9.80 | 9.93 | 9.98 | 16 |

| B      | 0.35  | 0.41            | 0.49 |                  |        |      |      |      |    |

| С      | 0.19  | 0.20            | 0.25 |                  |        |      |      |      |    |

| D      | SEE   | SEE VARIATIONS  |      | 3                |        |      |      |      |    |

| E      | 3.81  | 3.94            | 3.99 |                  |        |      |      |      |    |

| е      |       | 1.27 BSC        |      |                  |        |      |      |      |    |

| H      | 5.84  | 5.99            | 6.20 |                  |        |      |      |      |    |

| h      | 0.25  | 0.33            | 0.41 |                  |        |      |      |      |    |

| L      | 0.41  | 0.64            | 0.89 |                  |        |      |      |      |    |

| Ŋ      | SEE   | VARIATION       | IS   | 5                |        |      |      |      |    |

| oc     | 0°    | 5°              | 8°   |                  |        |      |      |      |    |

| X      | 2.16  | 2.36            | 2.54 |                  |        |      |      |      |    |

<sup>©</sup> Cypress Semiconductor Corporation, 2001. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

| Document Title: W181I Peak Reducing EMI Solution<br>Document Number: 38-07115 |         |               |                    |                                                                    |  |  |  |  |

|-------------------------------------------------------------------------------|---------|---------------|--------------------|--------------------------------------------------------------------|--|--|--|--|

| REV.                                                                          | ECN NO. | Issue<br>Date | Orig. of<br>Change | Description of Change                                              |  |  |  |  |

| **                                                                            | 108762  | 09/14/01      | IKA                | New spec.                                                          |  |  |  |  |

| *A                                                                            | 122683  | 12/22/02      | RBI                | Add power up requirements to Absolute Maximum Ratings information. |  |  |  |  |