# mos integrated circuit $\mu$ PD98402A

# LOCAL ATM SONET FRAMER

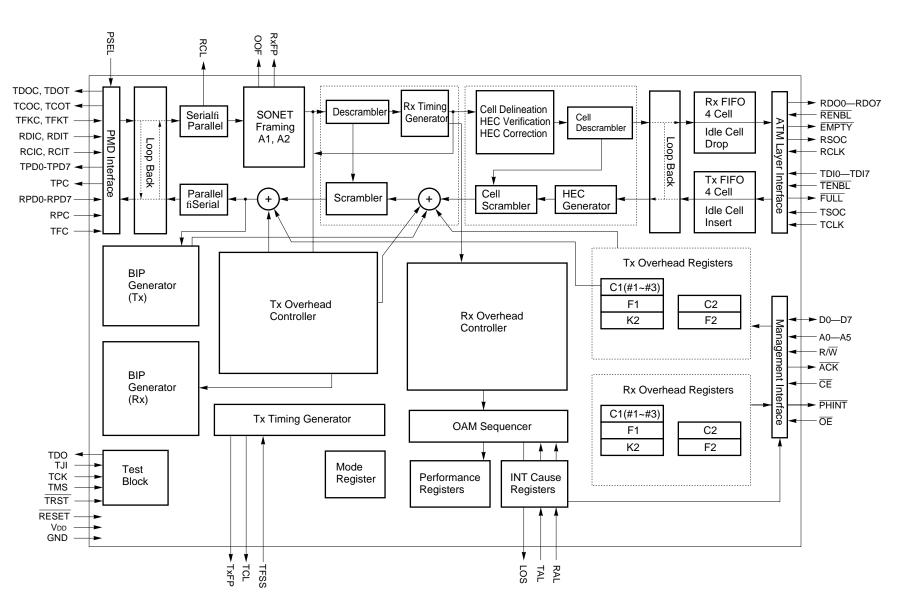

The  $\mu$ PD98402A is one of the ATM-LAN LSIs and incorporates the TC sublayer function in the SONET/SDHbased physical layer of the ATM protocol. The main functions of the  $\mu$ PD98402A include a transmit function for mapping ATM cells received from the ATM layer onto the payload block of the SONET STS-3c/SDH STM-1 frame and sending them to PMD (Physical Media Dependent) in the physical layer, and a receive function for separating the overhead block and ATM cells from the data string received from the PMD sublayer and sending the ATM cells to the ATM layer.

Futhermore, the  $\mu$ PD98402A is compliant with the ATM Forum UNI Recommendations.

#### **FEATURES**

NEC

- Provision of TC sublayer function of ATM protocol physical layer

- Support of SONET STS-3c frame/SDH STM-1 frame format

- Provision of stop mode for cell scramble/descramble and frame scramble/descramble

- Disposal/transitory selection of unassigned cells is possible.

- Compliant with UTOPIA interface

- · Incorporation of internal loopback function at PMD and ATM layer turns

- Incorporation of OAM (Operation And Maintenance) function

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

• Incorporation of OAM (Operation And Maintenance) function

#### Transmitting side

Transmission of various alarms

- Transmission by generation of sources Line RDI (FERF), Path RDI (FERF) Line FEBE, Path FEBE

- Transmission by command instruction Line AIS, Path AIS Line FEBE, Path FEBE

#### Receiving side

- Detection of alarms and error signals

- LOS (Loss Of Signal)

- OOF (Out Of Frame)

- LOF (Loss Of Frame)

- LOP (Loss Of Pointer)

- LOC (Loss Of Cell delineation)

Line RDI (FERF), Path RDI (FERF) Line AIS, Path AIS

- Detection and display of quality deterioration sources B1 error, B2 error, B3 error, Line FEBE, Path FEBE

- Incorporation of counter for counting number of performance monitoring errors

- B1 byte error counter

- B2 byte error counter

- B3 byte error counter

- Line FEBE error counter

- Path FEBE error counter

## **ORDERING INFORMATION**

Part Number Package µPD98402AGM-KED160-pin plastic QFP (FINE PITCH) (24 × 24 mm)

#### **APPLICATION EXAMPLES**

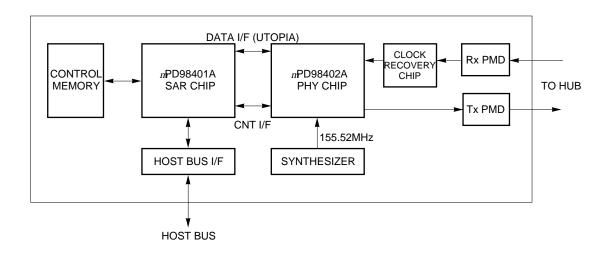

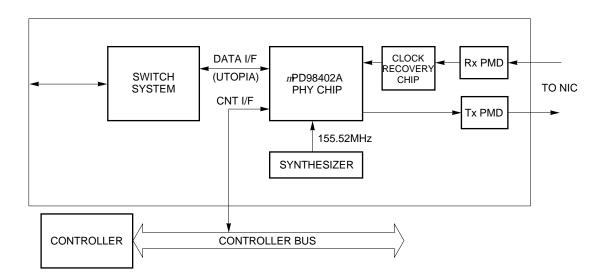

The followings are examples of the terminal equipment and the ATM Hub application using the  $\mu$ PD98402A.

Z

n

#### FUNCTIONAL PIN GROUPS

Note This function can be supported at the customer's request.

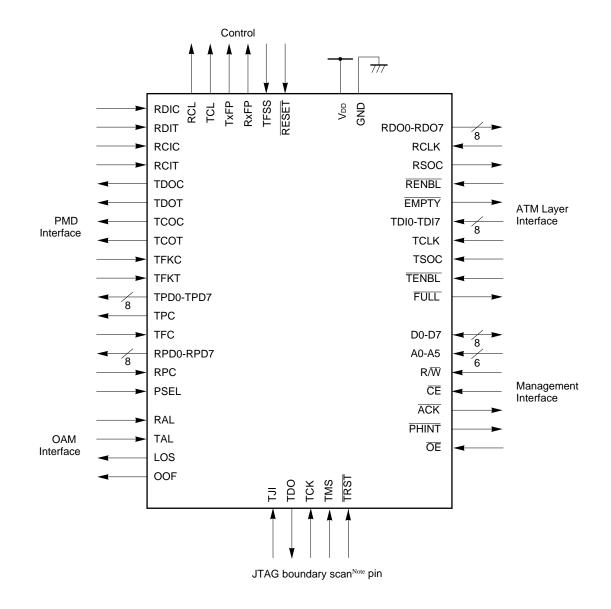

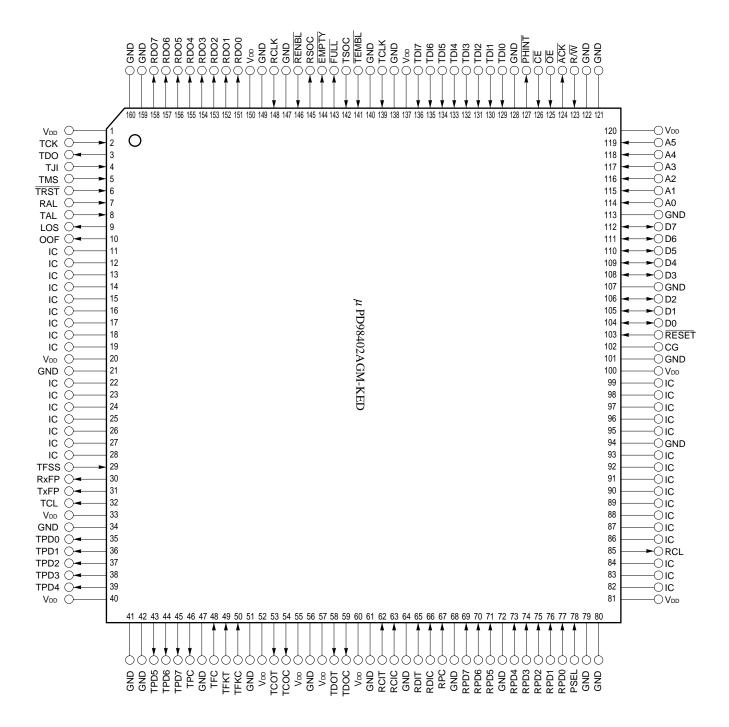

#### **PIN CONFIGURATION**

160-pin plastic QFP (FINE PITCH) (24  $\times$  24 mm) (Top View)

Remarks 1. IC : Internally Connected. Leave open.

2. CG: Connect to GND.

| A0-A5     | : Address Bus                                                |

|-----------|--------------------------------------------------------------|

| ACK       | : Read/write Cycle Receive Acknowledge                       |

|           | : Chip Enable                                                |

| D0-D7     | : Data Bus                                                   |

| EMPTY     | : Output Buffer Empty                                        |

| FULL      | : Buffer Full                                                |

| GND       | : Ground                                                     |

| LOS       | : Loss of Signal                                             |

|           | : Output Enable                                              |

| OOF       | : Out of Frame                                               |

| PHINT     | : Physical Interrupt                                         |

| PSEL      | : PMD I/F Select                                             |

| RAL       | : Receive Alarm                                              |

|           | : Receive Clock Input Complement                             |

| RCIT      | : Receive Clock Input True                                   |

| RCL       | : Internal Receive System Clock                              |

| RCLK      | : Receive Data Transferring Clock from the ATM Layer Device  |

| RDIC      | : Receive Data Input Complement                              |

| RDIC      | : Receive Data Input Complement                              |

|           | : Receive Data Input The                                     |

| RENBL     | : Receive Data Enable                                        |

| RESET     | : System Reset                                               |

| RPC       | : Receive Parallel Data Clock                                |

| -         | : Receive Parallel Data                                      |

| RSOC      | : Receive Start Address of ATM Cell                          |

| R/W       | : Read/write Control                                         |

| RxFP      | : Receive Frame Pulse                                        |

| TAL       | : Transmit Alarm                                             |

| TCK       | : Test Clock                                                 |

| TCL       | : Internal Transmit System Clock                             |

| TCLK      | : Transmit Data Transferring Clock from the ATM Layer Device |

| TCOC      | : Transmit Clock Output Complement                           |

| тсот      | : Transmit Clock Output True                                 |

| TDI0-TDI7 | : Transmit Data Input from the ATM Layer                     |

| TDO       | : Test Data Output                                           |

| TDOC      | : Transmit Data Output Complement                            |

| TDOC      | : Transmit Data Output Complement                            |

| TENBL     | : Transmit Data Fnable                                       |

| TFC       | : Transmit Reference Clock                                   |

| TFKC      | : Transmit Reference Clock Complement                        |

| TEKT      | : Transmit Reference Clock True                              |

| TFSS      | : Transmit Frame Set Signal                                  |

| TJI       | : Test JTAG Data Input                                       |

| TPC       | : Transmit Parallel Data Clock                               |

| -         | : Transmit Parallel Data                                     |

| TMS       | : Test Mode Select                                           |

| TRST      | : Test Reset                                                 |

| TSOC      | : Transmit Start Address of ATM Cell                         |

| TxFP      | : Transmit Frame Pulse                                       |

| VDD       | : Supply Voltage                                             |

|           |                                                              |

# 1. PIN FUNCTIONS

#### • PMD Interface

| Symbol    | Pin No.      | I/O | I/O Level                    | Function                                                                                                                                                                                                                                                                                         |

|-----------|--------------|-----|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDIC      | 66           | I   | Pseudo ECL<br>Complement (-) | These pins are used to input receive serial data when serial interface mode is used (PSEL pin input = low level). Ground                                                                                                                                                                         |

| RDIT      | 65           | I   | Pseudo ECL<br>True (+)       | them when Parallel interface mode is used.                                                                                                                                                                                                                                                       |

| RCIC      | 63           | Ι   | Pseudo ECL<br>Complement (-) | These pins are used to input the receive system clock when serial interface mode is used (PSEL pin input = low level).                                                                                                                                                                           |

| RCIT      | 62           | Ι   | Pseudo ECL<br>True (+)       | Clocks are input in synchronization with receive data. Ground them when parallel interface mode is used.                                                                                                                                                                                         |

| TDOC      | 59           | 0   | Pseudo ECL<br>Complement (-) | These pins are used to output transmit serial data when serial interface mode is used (PSEL pin input = low level). They are                                                                                                                                                                     |

| TDOT      | 58           | 0   | Pseudo ECL<br>True (+)       | open-drain pins. Terminate them with V <sub>DD</sub> –2 V via a 50 $\Omega$ resistor. To be undefined after reset.                                                                                                                                                                               |

| тсос      | 54           | 0   | Pseudo ECL<br>Complement (-) | These pins are used to output transmit clocks when serial<br>interface mode is used (PSEL pin input = low level). Transmit<br>clocks to be input to the TFKC/TFKT pins are output passing                                                                                                        |

| тсот      | 53           | 0   | Pseudo ECL<br>True (+)       | through internal gates. They are open-drain pins. Terminate them with $V_{DD}$ –2 via a 50 $\Omega$ resistor. To be undefined after reset.                                                                                                                                                       |

| TFKC      | 50           | I   | Pseudo ECL<br>Complement (-) | These pins are used to input transmit system clocks when<br>serial interface mode is used (PSEL pin input = low level).<br>Transmit data output from the TDOC/TDOT pins is output in                                                                                                             |

| TFKT      | 49           | I   | Pseudo ECL<br>True (+)       | synchronization with clocks that are input to these pins.<br>Ground them when parallel interface mode is used.                                                                                                                                                                                   |

| RPD0-RPD7 | 77-73, 71-69 | I   | TTL                          | These pins are used to input receive parallel data when<br>parallel interface mode is used (PSEL pin input = high level).<br>Leave them open when serial interface mode is used.                                                                                                                 |

| RPC       | 67           | I   | TTL                          | This pin is used to input the receive system clock when<br>parallel interface mode is used (PSEL pin input = high level).<br>Input clocks synchronous with the receive data. Leave it open<br>when serial interface mode is used.                                                                |

| TPD0-TPD7 | 35-39, 43-45 | 0   | CMOS                         | These pins are used to output transmit parallel data when<br>parallel interface mode is used (PSEL pin input = high level).<br>Leave them open when serial interface mode is used.                                                                                                               |

| TPC       | 46           | 0   | CMOS                         | This pin is used to output transmit clocks when parallel<br>interface mode is used (PSEL pin input = high level). Transmit<br>clocks to be input to the TFC pin are output passing through<br>internal gates. Leave it open when serial interface mode is<br>used.                               |

| TFC       | 48           | I   | TTL                          | This pins is used to input transmit system clocks when parallel<br>interface mode is used (PSEL pin input = high level). Transmit<br>data output from pins TPD0 to TPD7 are output in<br>synchronization with the clocks input to this pin. Leave it open<br>when serial interface mode is used. |

| PSEL      | 78           | I   | CMOS                         | This pin is used to select the mode for PMD interface serial/<br>parallel interface.<br>Low level: Serial interface mode<br>High level: Parallel interface mode                                                                                                                                  |

#### • Power supply

| Symbol | Pin No.                                                                                                                                 | I/O | Function                      |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------|

| Vdd    | 1, 20, 33, 40,<br>52, 55, 57, 60,<br>81, 100, 120,<br>137, 150                                                                          | _   | Supply voltage, 5 V $\pm$ 5 % |

| GND    | 21, 34, 41, 42,<br>47, 51, 56, 61,<br>64, 68, 72, 79,<br>80, 94, 101,<br>107, 113, 121,<br>122, 128, 138,<br>140, 147, 149,<br>159, 160 | _   | Ground                        |

#### • ATM Layer Interface

| Symbol    | Pin No. | I/O | I/O Level | Function                                                                                                                                                              |  |  |  |

|-----------|---------|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RDO0-RDO7 | 151-158 | 0   | CMOS      | Connected to 8-bit data bus to output the receive data to the ATM Layer device. Output is synchronized with the RCLK rising up. To be undefined after reset.          |  |  |  |

| RCLK      | 148     | I   | TTL       | Input pin of the receive data transferring clock from the ATM Layer device.                                                                                           |  |  |  |

| RSOC      | 145     | 0   | CMOS      | Receive cell start address signal. To the ATM Layer device this signal indicates the start address byte of the receive A cell. To be undefined after reset.           |  |  |  |

| RENBL     | 146     | I   | TTL       | Receive enable signal. Input pin of the signal indicating the the ATM layer device can receive data.                                                                  |  |  |  |

| EMPTY     | 144     | 0   | CMOS      | Output buffer empty signal. This signal indicates that there is no data to be transferred to the receive FIFO of the $\mu$ PD98402A. To be inactive after reset.      |  |  |  |

| TDI0-TDI7 | 129-136 | Ι   | TTL       | 8-bit data bus to input the transmit data from the ATM Layer device. Reading a data on the bus is synchronized with the TCLK rising-up.                               |  |  |  |

| TCLK      | 139     | Ι   | TTL       | Input pin of the transmit data transferring clock from the ATM layer device.                                                                                          |  |  |  |

| TSOC      | 142     | Ι   | TTL       | Transmit cell start address signal. Input pin of the signal indicating the start byte of the transmit ATM cell input from the ATM Layer device to the $\mu$ PD98402A. |  |  |  |

| TENBL     | 141     | I   | TTL       | Transmit enable signal. This signal indicates that the ATM Layer device is transmitting the valid data to the TDI0-TDI7.                                              |  |  |  |

| FULL      | 143     | 0   | CMOS      | Input buffer full signal. When 4 bytes remain as the acceptable bytes of transmit FIFO at last, this signal changes to active. To be inactive after reset.            |  |  |  |

# • Management Interface

| Symbol | Pin No.            | I/O | I/O Level                                                                          | Function                                                                                                                                                                                                                              |  |  |  |

|--------|--------------------|-----|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| D0-D7  | 104-106<br>108-112 | I/O | CMOS                                                                               | 8-bit data bus for data transfer between the control processor and the internal register of the $\mu$ PD98402A.                                                                                                                       |  |  |  |

| A0-A5  | 114-119            | I   | TTL                                                                                | Address bus. Used for setting the internal register address of the $\mu\text{PD98402A}.$                                                                                                                                              |  |  |  |

| R/W    | 123                | I   | TTL Read/write control signal.<br>Low level: Write cycle<br>High level: Read cycle |                                                                                                                                                                                                                                       |  |  |  |

| CE     | 126                | I   | TTL                                                                                | Chip enable signal.<br>At low level, internal register access is to be enable.                                                                                                                                                        |  |  |  |

| ACK    | 124                | 0   | CMOS                                                                               | Read/write cycle receive acknowledge or ready signal.<br>After reset, this signal indicates inactive level.                                                                                                                           |  |  |  |

| PHINT  | 127                | 0   | CMOS                                                                               | Signal which indicates the interrupt cause occurrence to the processor.<br>After reset, this signal indicates inactive level.                                                                                                         |  |  |  |

| ŌĒ     | 125                | Ι   | TTL                                                                                | Output enable. When this signal is set to low level, the $\mu$ PD98402A outputs data to the control bus. Even if the $\overline{CE}$ signal is inactive, when this signal is at low level, the $\mu$ PD98402A drives the control bus. |  |  |  |

#### • OAM Interface

| Symbol | Pin No. | I/O | I/O Level | Function                                                                                                                                                                                                                                                                                                                                    |

|--------|---------|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOS    | 9       | 0   | CMOS      | Loss of signal detection. Output high level when receive serial data input is "0" for 50 $\mu$ s continuously or optical input stop signal (RAL) is input. When 2 consecutive frames of valid synchronous pattern is detected, or when input of the optical input stop signal is released, low level is output. To be inactive after reset. |

| OOF    | 10      | 0   | CMOS      | Out of frame detection. When 4 consecutive frames of wrong synchronous pattern are detected, high level is output. When 2 consecutive frames of normal synchronous pattern are detected, low level is output. To be inactive after reset.                                                                                                   |

| RAL    | 7       | I   | TTL       | Receive alarm. Inputs receiver-side optical input stop signal<br>by the optical module.<br>Low level: Normal<br>High level: Optical input stopped.                                                                                                                                                                                          |

| TAL    | 8       | I   | TTL       | Transmit alarm. Inputs transmit-side optical output stop signal<br>output by the optical module.<br>Low level: Normal<br>High level: Optical output stopped.                                                                                                                                                                                |

#### Control

| Symbol | Pin No. | I/O | I/O Level | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|---------|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TFSS   | 29      | I   | TTL       | This is the transmit frame setting signal input pin.<br>It allows synchronization timing of transmit frame output to be<br>set. The $\mu$ PD98402A samples this input signal by the internal<br>transmit system clock (TCL).<br>Initial output of the transmit frame is restarted 9 clocks into<br>TCL clock cycle after a high level is latched at TCL rise.                                                                                                                                                           |

| RESET  | 103     | I   | TTL       | This is the system reset signal input pin.<br>It initializes the $\mu$ PD98402A. It is necessary to input a reset<br>signal with a pulse width of 2 cycles or more of the clock that<br>has the longest cycle among the following clocks input to the<br>$\mu$ PD98402A.<br>ATM layer : TCLK, RCLK clock cycles<br>PMD layer : 1/8 cycle of TFKT/TFKC, RCIC/RCIT clocks,<br>TFC, RPC clock cycles<br>Immediately after a reset, no read/write is possible to registers<br>during 5 clocks of the TCL clock (19.44 MHz). |

| TCL    | 32      | 0   | CMOS      | This pin is used to output an internal transmit system clock.<br>The $\mu$ PD98402A outputs as the internal transmit system clock,<br>the TFKT/TFKC input clock (155.52 MHz) scaled by 8 in serial<br>interface mode, and the TFC input clock (19.44 MHz) in<br>parallel interface mode.                                                                                                                                                                                                                                |

| RCL    | 85      | 0   | CMOS      | This pin is used to output an internal receive system clock.<br>The $\mu$ PD98402A outputs as the internal receive system clock,<br>the RCIC/RCIT input clock (155.52 MHz) scaled by 8 in serial<br>interface mode, and the RFC input clock (19.44 MHz) in<br>parallel interface mode.                                                                                                                                                                                                                                  |

| TxFP   | 31      | 0   | CMOS      | This is a frame pulse signal on the transmitting side. It outputs pulses synchronous with the transmit frame start. To be inactive after reset.                                                                                                                                                                                                                                                                                                                                                                         |

| RxFP   | 30      | 0   | CMOS      | This is a frame pulse signal on the receiving side. It outputs pulses synchronous with the receive frame start. To be inactive after reset.                                                                                                                                                                                                                                                                                                                                                                             |

# • JTAG boundary scan pins (This function can be supported at the customer's request.)

| Symbol | Pin No. | I/O | I/O Level | Function                                                                              |

|--------|---------|-----|-----------|---------------------------------------------------------------------------------------|

| TJI    | 4       | I   | TTL       | This is a pin for JTAG boundary scan.<br>Pull it up or ground it in normal operation. |

| TDO    | 3       | 0   | CMOS      | This is a pin for JTAG boundary scan.<br>Leave it open in normal operation.           |

| тск    | 2       | I   | TTL       | This is a pin for JTAG boundary scan.<br>Pull it up or ground it in normal operation. |

| TMS    | 5       | I   | TTL       | This is a pin for JTAG boundary scan.<br>Pull it up or ground it in normal operation. |

| TRST   | 6       | I   | TTL       | This is a pin for JTAG boundary scan.<br>Ground it in normal operation.               |

• Recommended Connection for Unused Pins

| Pin                                                    | Recommended connection |

|--------------------------------------------------------|------------------------|

| TDOC, TDOT, TCOC, TCOT, ACK, LOS, OOF, TCL, TxFP, RxFP | leave open             |

| RAL, TAL, TFSS                                         | connect to GND         |

## 2. ELECTRICAL SPECIFICATION

#### Absolute maximum ratings

| Parameters                    | Symbol Conditions |  | Ratings          | Unit |

|-------------------------------|-------------------|--|------------------|------|

| Supply voltage                | Vdd               |  | -0.5 to +6.5     | V    |

| Input/output voltage          | Vı/Vo             |  | -0.5 to VDD +0.5 | V    |

| Operating ambient temperature | TA                |  | 0 to +70         | °C   |

| Storage temperature           | Tstg              |  | -65 to +150      | °C   |

Caution Exposure to absolute maximum ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The parameters apply independently. The device should be operated within the limits specified under DC and AC characteristics.

#### Capacitance

| Parameters               | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|--------------------------|--------|------------|------|------|------|------|

| Input capacitance        | Cı     |            |      | 10   | 20   | pF   |

| Output capacitance       | Co     | f = 1 MHz  |      | 10   | 20   | pF   |

| Input/output capacitance | Сю     |            |      | 10   | 20   | pF   |

#### **Recommended operating conditions**

| Parameters                    | Symbol | Conditions | MIN.    | TYP. | MAX.    | Unit |

|-------------------------------|--------|------------|---------|------|---------|------|

| Supply voltage                | Vdd    |            | 4.75    |      | 5.25    | V    |

| Operating ambient temperature | TA     |            | 0       |      | +70     | °C   |

| Low level input voltage       | VIL1   | Note1      | 0       |      | +0.8    |      |

|                               | VIL2   | Note2      | Vdd-2   |      | Vdd-1.5 | V    |

|                               | VIL3   | Note3      | 0       |      | 0.3 Vdd |      |

| High level input voltage      | VIH1   | Note1      | 2.2     |      | Vdd     |      |

|                               | VIH2   | Note2      | Vdd-1.1 |      | Vdd     | V    |

|                               | Vінз   | Note3      | 0.7 Vdd |      | Vdd     |      |

#### Notes 1. TTL input pin

- 2. Pseudo ECL input pin

- 3. CMOS input pin

# DC Characteristics (V<sub>DD</sub> = 5 V $\pm$ 0.25 V, T<sub>A</sub> = 0 to +70 °C)

| Parameters                | Symbol | Conditions                             | MIN.    | TYP. | MAX.    | Unit |

|---------------------------|--------|----------------------------------------|---------|------|---------|------|

| Off-state output current  | loz    | $V_I = V_{DD} \text{ or } GND^{Note1}$ | _       |      | 10      | μΑ   |

| Input leak current        | ILI1   | $V_I = V_{DD} \text{ or } GND^{Note2}$ | _       |      | 10      |      |

|                           | ILI2   | Note 3                                 | _       |      | 10      | μΑ   |

|                           | Vон1   | Iон = -0.5 mA <sup>Note4</sup>         | 0.7 Vdd |      | _       |      |

| High level output voltage | Vон2   | Note 5                                 | Vdd-0.9 |      | VDD-0.4 | V    |

| Low level output voltage  | Vol1   | IoL = 6.0 mA <sup>Note4</sup>          | _       |      | 0.4     | N    |

|                           | Vol2   | Note 5                                 | Vdd-2.0 |      | Vdd-1.7 | V    |

| Supply current            | ldd    | Normal operation                       | _       |      | 300     | mA   |

#### Notes 1. 3-state data bus

- 2. TTL input pin

- 3. Pseudo ECL input pin

- 4. CMOS output pin

- 5. Pseudo ECL output pin

#### **AC Characteristics**

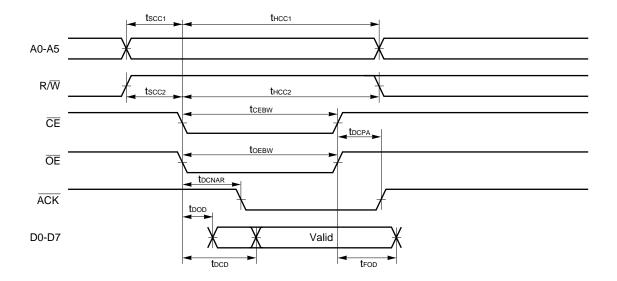

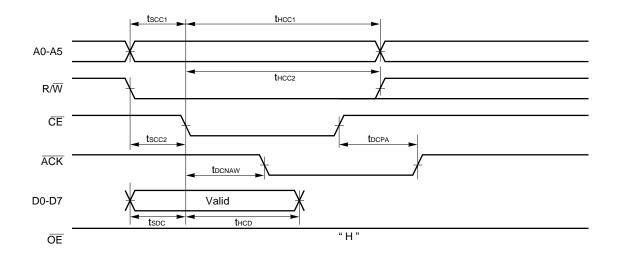

#### (1) Management Interface

#### Internal Register Read/Write

| Parameters                                                                          | Symbol         | Conditions                                                                                     | MIN.                                                 | TYP. | MAX.                                                     | Unit |

|-------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------|------------------------------------------------------|------|----------------------------------------------------------|------|

| A0-A5 setup time (to $\overline{CE}\downarrow$ )                                    | tscc1          |                                                                                                | 5                                                    |      |                                                          | ns   |

| $R/\overline{W}$ setup time (to $\overline{CE}\downarrow$ )                         | tscc2          |                                                                                                | 5                                                    |      |                                                          | 115  |

| A0-A5 hold time (to $\overline{CE}\downarrow$ )                                     | tHCC1          |                                                                                                | 3                                                    |      |                                                          | ns   |

| $R/\overline{W}$ hold time (to $\overline{CE}\downarrow$ )                          | tHCC2          |                                                                                                | 3                                                    |      |                                                          | 115  |

| $\overline{CE} \downarrow \rightarrow \overline{ACK} \downarrow$ delay time (read)  | <b>t</b> dcnar | Load capacitor 15 pF<br>At parallel data input                                                 | 3 ×<br>tcyppr                                        |      | 4.5 ×<br>tcyppr                                          | 20   |

|                                                                                     |                | Load capacitor 15 pF<br>At serial data input                                                   | $3 \times$ (tcypsr $\times 8$ )                      |      | 4.5 ×<br>(tcypsr × 8)                                    | ns   |

| $\overline{CE} \downarrow \rightarrow \overline{ACK} \downarrow$ delay time (write) | <b>t</b> dcnaw | Load capacitor 15 pF<br>At parallel data input<br>Load capacitor 15 pF<br>At serial data input | $2 \times t_{CYPPR}$ $2 \times (t_{CYPSR} \times 8)$ |      | $3.5 \times t_{CYPPR}$ $3.5 \times (t_{CYPSR} \times 8)$ | ns   |

| $\overline{CE}\uparrow\rightarrow\overline{ACK}\uparrow$ delay time                 | tdcpa          | Load capacitor 15 pF<br>At parallel data input                                                 | 1 ×<br>tcyppr                                        |      | 2.5 ×<br>tcyppr                                          | ns   |

|                                                                                     |                | Load capacitor 15 pF<br>At serial data input                                                   | $1 \times$ (tcypsr $\times$ 8)                       |      | $2.5 \times$ (tcypsr $\times$ 8)                         |      |

| $\overline{\text{CE}} {\downarrow} {\rightarrow}$ data output delay time            | toco           | Load capacitor 15 pF<br>At parallel data input                                                 | 2 ×<br>tcyppr                                        |      | 3.5 ×<br>tcyppr                                          | ns   |

|                                                                                     |                | Load capacitor 15 pF<br>At serial data input                                                   | $2 \times$ (tcypsr $\times$ 8)                       |      | $3.5 \times$ (tcypsr $\times$ 8)                         | 115  |

| $\overline{\text{OE}} {\downarrow} { ightarrow}$ data output delay time             | tDOD           | Load capacitor 15 pF                                                                           | _                                                    |      | 9.4                                                      | ns   |

| $\overline{\text{OE}} \hat{\uparrow} \rightarrow$ data floating output delay time   | tfod           | Load capacitor 15 pF                                                                           | —                                                    |      | 10                                                       | ns   |

| D0-D7 setup time (to $\overline{CE}\downarrow$ )                                    | tspc           |                                                                                                | 5                                                    |      | —                                                        | ns   |

| D0-D7 hold time (to $\overline{CE}\downarrow$ )                                     | tнср           |                                                                                                | 3                                                    |      | —                                                        | ns   |

| CE low-level width                                                                  | tсевw          | At parallel data input                                                                         | 3.5 ×<br>tcyppr                                      |      | —                                                        | 20   |

|                                                                                     |                | At serial data input                                                                           | $3.5 \times$ (tcypsr $\times$ 8)                     |      | -                                                        | ns   |

| OE low-level width                                                                  | tоевw          | At parallel data input                                                                         | 2.5 ×<br>tcyppr                                      |      | _                                                        | ns   |

|                                                                                     |                | At serial data input                                                                           | $2.5 \times$ (tcypsr $\times$ 8)                     |      | -                                                        | 10   |

**Remarks 1.** For tCYPPR, refer to (6) PMD parallel interface timing.

2. For tCYPSR, refer to (7) PMD serial interface timing.

# NEC

#### **Management Interface**

#### **Internal Register Read**

(a) Case 1 When the host uses  $\overline{\text{ACK}}$  signal

# (b) Case 2 When the host does not use $\overline{ACK}$ signal

# Internal Register Write

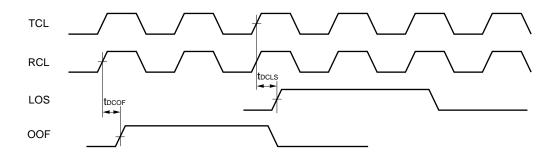

# (2) OAM Interface

| Parameters                       | Symbol        | Conditions             | MIN. | TYP. | MAX. | Unit |

|----------------------------------|---------------|------------------------|------|------|------|------|

| TCL↑→LOS delay time              | <b>t</b> DCLS | load capacitor = 15 pF | 5    |      | 30   | ns   |

| RCL <sup>↑</sup> →OOF delay time | <b>t</b> DCOF | load capacitor = 15 pF | -5   |      | +7   | ns   |

#### **OAM Interface**

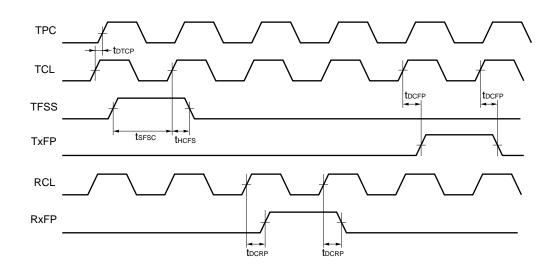

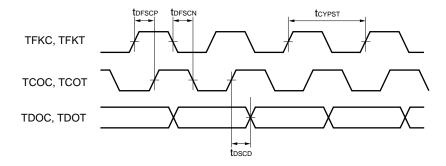

# (3) Control Signal Interface

| Parameters                            | Symbol        | Conditions             | MIN. | TYP. | MAX. | Unit |

|---------------------------------------|---------------|------------------------|------|------|------|------|

| TCL↑→TPC delay time                   | <b>t</b> dtcp | load capacitor = 15 pF | 0    |      | +5   | ns   |

| TFSS setup time (to TCL↑)             | tsfsc         |                        | 10   |      | _    | ns   |

| TFSS hold time (to TCL <sup>↑</sup> ) | thcfs         |                        | 5    |      | _    | ns   |

| TCL↑→TxFP delay time                  | <b>t</b> DCFP | load capacitor = 15 pF | 0    |      | +20  | ns   |

| RCL <sup>↑</sup> →RxFP delay time     | <b>t</b> DCRP | load capacitor = 15 pF | -5   |      | +20  | ns   |

# **Control Signal Interface**

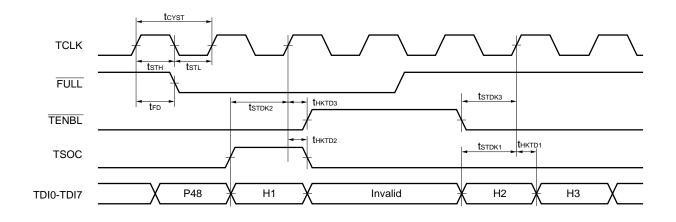

# (4) SAR Interface (Transmitter Side)

| Parameters                                                            | Symbol | Conditions             | MIN. | TYP. | MAX. | Unit |

|-----------------------------------------------------------------------|--------|------------------------|------|------|------|------|

| TCLK cycle time                                                       | tсүзт  |                        | 30   |      | 125  | ns   |

| TCLK high level width                                                 | tsтн   |                        | 12   |      | 110  | ns   |

| TCLK low level width                                                  | ts⊤∟   |                        | 12   |      | 110  | ns   |

| $TCLK^{\uparrow} \rightarrow \overline{FULL}^{\downarrow}$ delay time | tro    | load capacitor = 15 pF | 5    |      | 17   | ns   |

| TDI0-TDI7 setup time (to TCLK↑)                                       | tstdk1 |                        | 5    |      | _    | ns   |

| TSOC setup time (to TCLK↑)                                            | tstdk2 |                        | 12   |      | _    | ns   |

| TENBL setup time (to TCLK <sup>↑</sup> )                              | tsтркз |                        | 5    |      | _    | ns   |

| TDI0-TDI7 hold time (to TCLK <sup>↑</sup> )                           | thktd1 |                        | 3    |      | _    | ns   |

| TSOC hold time (to TCLK↑)                                             | thktd2 |                        | 3    |      | _    | ns   |

| TENBL hold time (to TCLK <sup>↑</sup> )                               | thktd2 |                        | 3    |      | _    | ns   |

# SAR Interface (Transmitter Side)

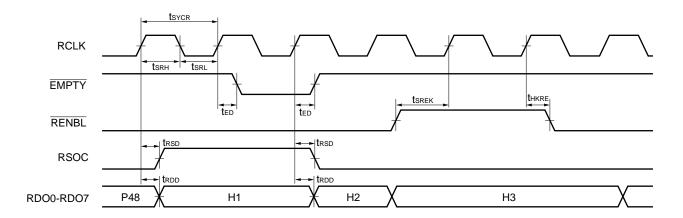

#### (5) SAR Interface (Receiver Side)

| Parameters                  | Symbol        | Conditions             | MIN. | TYP. | MAX. | Unit |

|-----------------------------|---------------|------------------------|------|------|------|------|

| RCLK cycle time             | tsycr         |                        | 30   |      | 125  | ns   |

| RCLK high level width       | tsrн          |                        | 12   |      | 110  | ns   |

| RCLK low level width        | tsrl          |                        | 12   |      | 110  | ns   |

| RCLK↑→EMPTY↑↓delay time     | ted           | load capacitor = 15 pF | 5    |      | 17   | ns   |

| RENBL setup time (to RCLK↑) | <b>t</b> SREK |                        | 12   |      | _    | ns   |

| RENBL hold time (to RCLK↑)  | tнкке         |                        | 3    |      | _    | ns   |

| RCLK↑→RSOC↑↓ delay time     | trsd          | load capacitor = 15 pF | 0    |      | 17   | ns   |

| RCLK∱→RDO0-RDO7 delay time  | trdd          | load capacitor = 15 pF | 0    |      | 17   | ns   |

# SAR Interface (Receiver Side)

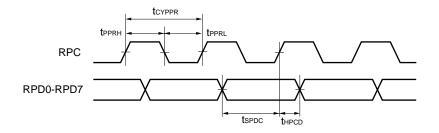

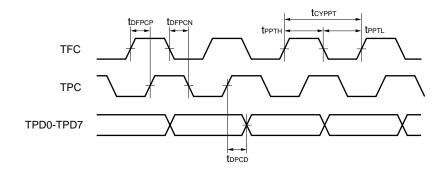

# (6) PMD Parallel Interface

| Parameters                                             | Symbol         | Conditions             | MIN. | TYP. | MAX. | Unit |

|--------------------------------------------------------|----------------|------------------------|------|------|------|------|

| RPC cycle time                                         | <b>t</b> cyppr |                        | 50   |      | _    | ns   |

| RPC high level width                                   | <b>t</b> PPRH  |                        | 20   |      | _    | ns   |

| RPC low level width                                    | <b>t</b> PPRL  |                        | 20   |      | _    | ns   |

| TFC cycle time                                         | tсуррт         |                        | 50   |      | _    | ns   |

| TFC high level width                                   | tрртн          |                        | 20   |      | _    | ns   |

| TFC low level width                                    | <b>t</b> PPTL  |                        | 20   |      | _    | ns   |

| RPD0-RPD7 setup time (to RPC↑)                         | tspdc          |                        | 5    |      | _    | ns   |

| RPD0-RPD7 hold time (to RPC↑)                          | tнрср          |                        | 3    |      | _    | ns   |

| TFC $\uparrow \rightarrow$ TPC $\uparrow$ delay time   | <b>t</b> DFPCP | load capacitor = 15 pF | 3    |      | 25   | ns   |

| $TFC \downarrow \rightarrow TPC \downarrow$ delay time | <b>t</b> dfpcn | load capacitor = 15 pF | 3    |      | 25   | ns   |

| TPC $\uparrow \rightarrow$ TPD0-TPD7 delay time        | tdpcd          | load capacitor = 15 pF | -3.0 |      | +1.0 | ns   |

#### **PMD** Parallel Interface

#### **Receive Side**

#### **Transmit Side**

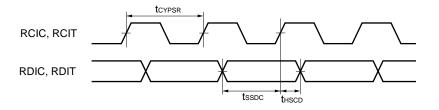

## (7) PMD Serial Interface

| Parameters                        | Symbol         | Conditions           | MIN. | TYP. | MAX. | Unit |

|-----------------------------------|----------------|----------------------|------|------|------|------|

| RCIT (RCIC) cycle time            | tcypsr         |                      | 6.4  |      | _    | ns   |

| TFKT (TFKC) cycle time            | <b>t</b> CYPST |                      | 6.4  |      | _    | ns   |

| Serial data setup time            | tsspc          |                      | 1.0  |      | _    | ns   |

| Serial data hold time             | thscd          |                      | 1.0  |      | _    | ns   |

| Serial clock delay time (rising)  | <b>t</b> DFSCP | Load capacitor 15 pF | _    |      | 8    | ns   |

| Serial clock delay time (falling) | <b>t</b> DFSCN | Load capacitor 15 pF | _    |      | 8    | ns   |

| Transmit serial data delay time   | tosco          | Load capacitor 15 pF | _    |      | 3    | ns   |

#### **PMD Serial Interface**

#### **Receive Side**

## Transmit Side

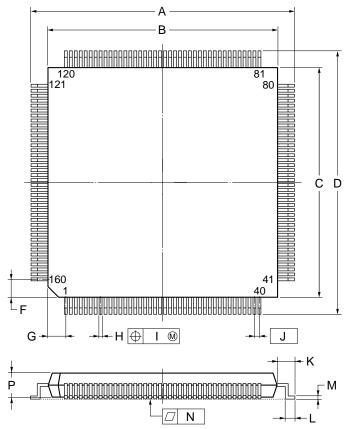

# 3. PACKAGE DRAWING

# 160 PIN PLASTIC QFP (FINE PITCH) (24)

റ

R

detail of lead end

#### NOTE

Each lead centerline is located within 0.10 mm (0.004 inch) of its true position (T.P.) at maximum material condition.

| ITEM                      | MILLIMETERS                   | INCHES                            |  |  |  |  |

|---------------------------|-------------------------------|-----------------------------------|--|--|--|--|

| А                         | 26.0±0.2                      | 1.024+0.008                       |  |  |  |  |

| В                         | 24.0±0.2                      | 0.945±0.008                       |  |  |  |  |

| С                         | 24.0±0.2                      | 0.945±0.008                       |  |  |  |  |

| D                         | 26.0±0.2                      | 1.024 <sup>+0.008</sup><br>-0.009 |  |  |  |  |

| F                         | 2.25                          | 0.089                             |  |  |  |  |

| G                         | 2.25                          | 0.089                             |  |  |  |  |

| н                         | $0.22^{+0.05}_{-0.04}$        | 0.009±0.002                       |  |  |  |  |

| I                         | 0.10                          | 0.004                             |  |  |  |  |

| J                         | 0.5 (T.P.)                    | 0.020 (T.P.)                      |  |  |  |  |

| к                         | 1.0±0.2                       | $0.039^{+0.009}_{-0.008}$         |  |  |  |  |

| L                         | 0.5±0.2                       | $0.020^{+0.008}_{-0.009}$         |  |  |  |  |

| М                         | $0.17\substack{+0.03\\-0.07}$ | $0.007^{+0.001}_{-0.003}$         |  |  |  |  |

| Ν                         | 0.10                          | 0.004                             |  |  |  |  |

| Р                         | 2.7                           | 0.106                             |  |  |  |  |

| Q                         | 0.125±0.075                   | 0.005±0.003                       |  |  |  |  |

| R                         | 5°±5°                         | 5°±5°                             |  |  |  |  |

| S                         | 3.0 MAX.                      | 0.119 MAX.                        |  |  |  |  |

| S160GM-50-3ED, JED, KED-2 |                               |                                   |  |  |  |  |

## 4. RECOMMENDED SOLDERING CONDITIONS

For the  $\mu$ PD98402A, soldering must be performed under the following conditions.

For details of recommended conditions for surface mounting, refer to information document "Semiconductor

### Device Mounting Technology Manual" (IEI-1207).

For other soldering methods, please consult with NEC sales personnel.

#### • $\mu$ PD98402AGM-KED: 160-pin plastic QFP (FINE PITCH) (24 $\times$ 24 mm)

| Soldering Method    | Soldering Conditions                                                                                                                                                                                                                                                                                                                                                                                                                              | Symbol     |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Infrared reflow     | <ul> <li>Package peak temperature: 235 °C, time: 30 sec. max. (over 210 °C), count: twice or less, restriction days: 3<sup>Note</sup> (after that, 125 °C pre-baking for 20 hours is necessary)</li> <li>Precautions: <ol> <li>Reflow a second time should be started when the device temperature has returned to its normal state after the first reflow.</li> <li>Avoid flux cleaning with water after the first reflow.</li> </ol> </li> </ul> | IR35-203-2 |

| Pin partial heating | Pin temperature: 300 °C max., time: 3 seconds max. (per side)                                                                                                                                                                                                                                                                                                                                                                                     | —          |

**Note** This means the number of days after unpacking the dry pack. Storage conditions are 25 °C and 65 % RM max.

[MEMO]

\_\_\_\_\_

[MEMO]

The export of this product from Japan is prohibited without governmental license. To export or re-export this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

- The information in this document is current as of December, 1995. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC semiconductor products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades:

"Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products

developed based on a customer-designated "quality assurance program" for a specific application. The

recommended applications of a semiconductor product depend on its quality grade, as indicated below.

Customers must check the quality grade of each semiconductor product before using it in a particular

application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

(Note)

- (1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).