# MOS INTEGRATED CIRCUIT $\mu$ PD78P0208

# 8-BIT SINGLE-CHIP MICROCOMPUTER

The  $\mu$ PD78P0208 is a product in the  $\mu$ PD780208 subseries within the 78K/0 series, in which on-chip mask ROM of the  $\mu$ PD780208 is replaced with one-time PROM or EPROM.

Since user programs can be written to PROM, this microcomputer is best suited for evaluation in system development, manufacture of small quantities of multiple products, and fast start-up of applications.

For specific functions and other detailed information, consult the following user's manual.

This manual is required reading for design work.

μPD780208 Subseries User's Manual : IEU-1413 78K/0 Series User's Manual, Instruction: IEU-1372

#### **FEATURES**

Pin compatible with mask ROM products (except for VPP pin)

Internal PROM: 60K bytes<sup>Note 1</sup>

• μPD78P0208KL-T : EPROM (best suited for system evaluation)

μPD78P0208GF : PROM (best suited for manufacture of small quantities)

Internal high-speed RAM : 1024 bytes

Internal expansion RAM : 1024 bytes<sup>Note 2</sup>

Buffer RAM : 64 bytes FIP® display RAM : 80 bytes

Can be operated at the same power supply voltage as mask ROM products:

$V_{DD} = 2.7$  to 5.5 V (except for A/D converter).

A/D converter's power supply voltage: AVDD = 4.0 to 5.5 V.

- QTOP<sup>TM</sup> microcomputer

- Notes 1. Internal PROM capacity can be changed according to the internal memory switching register (IMS).

- 2. Internal expansion RAM capacity can be changed according to the internal expansion RAM switching register (IXS).

**Remark** The QTOP microcomputer is a single-chip microcomputer with a built-in one-time PROM that is totally supported by NEC. The support includes writing application programs, marking, screening, and verification.

#### This product differs from mask ROM products in the following respects.

- It can use the same memory mapping as mask ROM products, depending upon the IMS and IXS settings.

- FIP0 to FIP12 have on-chip pull-down resistors.

- Port 3 and FIP13 to FIP52 (port 8 to port 12) do not have on-chip pull-down resistors.

- Port 7 does not have a on-chip pull-up resistor.

In this reference, all ROM components that are common to one-time PROM and EPROM are referred to as PROM.

The information in this document is subject to change without notice.

Printed in Japan

#### ORDERING INFORMATION

| Part No.         | Package              |                             | Internal ROM  |

|------------------|----------------------|-----------------------------|---------------|

| μPD78P0208GF-3BA | 100-pin plastic QFP  | $(14 \times 20 \text{ mm})$ | One-Time PROM |

| μPD78P0208KL-T   | 100-pin ceramic WQFN | $(14 \times 20 \text{ mm})$ | EPROM         |

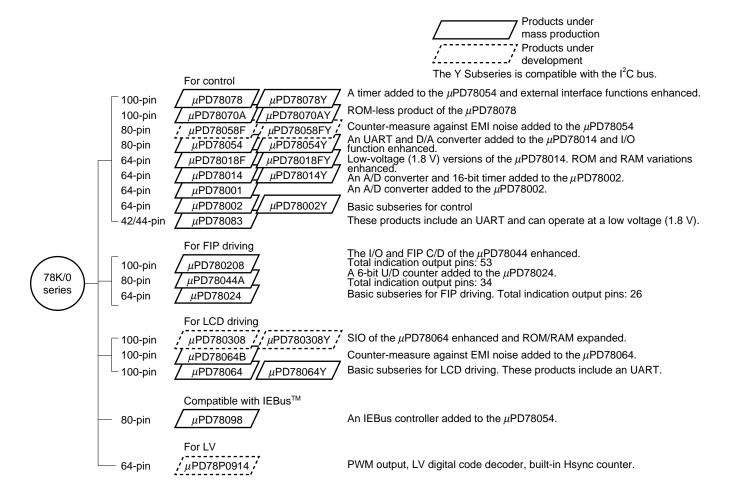

#### **★** 78K/0 SERIES PRODUCT DEVELOPMENT

The 78K/0 series products were developed as shown below. The subseries names are indicated in frames.

The table below shows the main differences between subseries.

| Function              |            | ROM      | Timer |        | 8-bit | 8-bit | Serial | I/O  | V <sub>DD</sub> Min. | External |       |           |

|-----------------------|------------|----------|-------|--------|-------|-------|--------|------|----------------------|----------|-------|-----------|

| Subseries na          | me         | capacity | 8-bit | 16-bit | Watch | WDT   | A/D    | D/A  | interface            | 1/0      | value | expansion |

| For control           | μPD78078   | 32K-60K  | 4ch   | 1ch    | 1ch   | 1ch   | 8ch    | 2ch  | 3ch (UART : 1ch)     | 88 pins  | 1.8 V | 0         |

|                       | μPD78070A  | _        |       |        |       |       |        |      |                      | 61 pins  | 2.7 V |           |

|                       | μPD78058F  | 48K-60K  | 2ch   |        |       |       |        |      |                      | 69 pins  |       |           |

|                       | μPD78054   | 16K-60K  |       |        |       |       |        |      |                      |          | 2.0 V |           |

|                       | μPD78018F  | 8K-60K   |       |        |       |       |        | _    | 2ch                  | 53 pins  | 1.8 V |           |

|                       | μPD78014   | 8K-32K   |       |        |       |       |        |      |                      |          | 2.7 V |           |

|                       | μPD780001  | 8K       |       | _      | _     |       |        |      | 1 ch                 | 39 pins  |       | _         |

|                       | μPD78002   | 8K-16K   |       |        | 1 ch  |       | _      |      |                      | 53 pins  |       | 0         |

|                       | μPD78083   |          |       |        | _     |       | 8 ch   |      | 1 ch (UART : 1 ch)   | 33 pins  | 1.8 V | _         |

| For FIP               | μPD780208  | 32K-60K  | 2 ch  | 1 ch   | 1 ch  | 1 ch  | 8 ch   | -    | 2 ch                 | 74 pins  | 2.7 V | _         |

| driving               | μPD78044A  | 16K-40K  |       |        |       |       |        |      |                      | 68 pins  |       |           |

|                       | μPD78024   | 24K-32K  |       |        |       |       |        |      |                      | 54 pins  |       |           |

| For LCD               | μPD780308  | 48K-60K  | 2 ch  | 1 ch   | 1 ch  | 1 ch  | 8 ch   | _    | 3 ch (UART : 1 ch)   | 57 pins  | 1.8 V | _         |

| driving               | μPD78064B  | 32K      |       |        |       |       |        |      | 2 ch (UART : 1 ch)   |          | 2.0 V |           |

|                       | μPD78064   | 16K-32K  |       |        |       |       |        |      |                      |          |       |           |

| Compatible with IEBus | μPD78098   | 32K-60K  | 2 ch  | 1 ch   | 1 ch  | 1 ch  | 8 ch   | 2 ch | 3 ch (UART : 1 ch)   | 69 pins  | 2.7 V | 0         |

| For LV                | μPD78P0914 | 32K      | 6 ch  | _      | _     | 1 ch  | 8 ch   | _    | 2 ch                 | 54 pins  | 4.5 V | 0         |

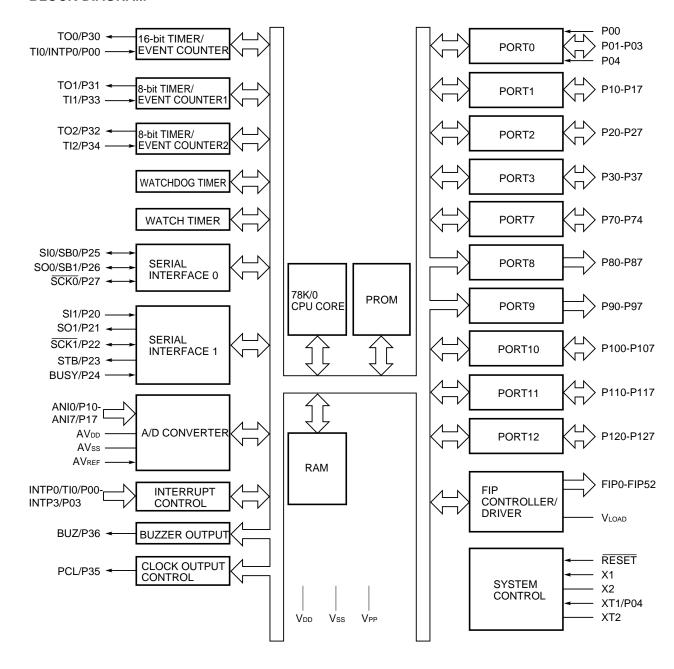

# **OVERVIEW OF FUNCTIONS**

|                                                    | Item                       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|----------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Internal memory                                    |                            | <ul> <li>PROM: 60K bytes Note 1</li> <li>RAM         <ul> <li>Internal high-speed RAM</li> <li>Internal expansion RAM</li></ul></li></ul> |  |  |  |  |

| General reg                                        | ister                      | 8 bits × 32 registers (8 bits × 8 registers × 4 banks)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

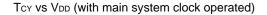

| Instruction                                        |                            | On-chip instruction execution time cycle modification function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| cycle                                              | Main system clock selected | 0.4 μs/0.8 μs/1.6 μs/3.2 μs/6.4 μs (5.0 MHz operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                                                    | Subsystem clock selected   | 122 μs (32.768 kHz operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Instruction s                                      | set                        | <ul> <li>Multiplier/divider (8 bits × 8 bits, 16 bits ÷ 8 bits)</li> <li>Bit handling (set, reset, test, Boolean operations)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| I/O ports<br>(including pins also used<br>for FIP) |                            | Total         : 74 pins           • CMOS input         : 2           • CMOS I/O         : 27           • N-ch open-drain I/O         : 5           • P-ch open-drain I/O         : 24           • P-ch open-drain output         : 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

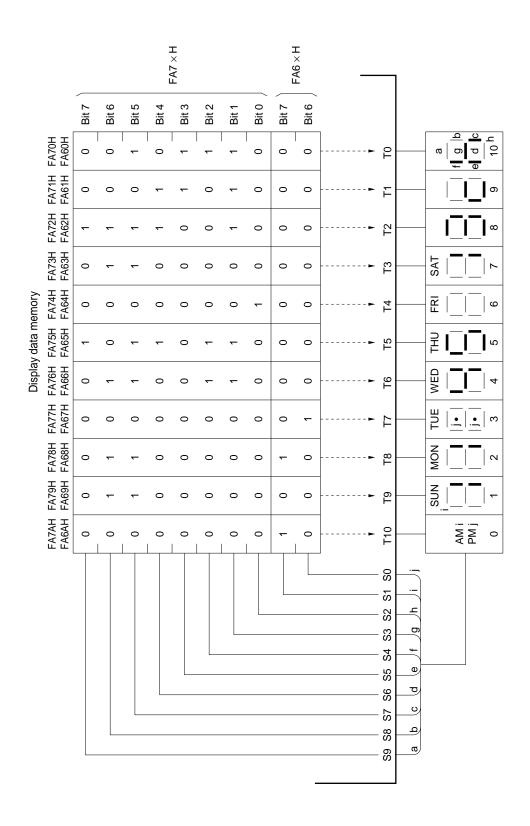

| FIP controlle                                      | er/driver                  | Display output total       : 53         • No. of segments       : 9 to 40         • No. of digits       : 2 to 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| A/D convert                                        | er                         | <ul> <li>8-bit resolution × 8 channels</li> <li>Supply voltage: AVDD = 4.0 to 5.5 V</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Serial interfa                                     | ace                        | 3-wire serial I/O/SBI/2-wire serial I/O selectable modes: 1 channel     3-wire serial I/O mode (on-chip maximum 64-byte automatic transmit/receive function): 1 channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Timers                                             |                            | <ul> <li>16-bit timer/event counter</li> <li>8-bit timer/event counters</li> <li>2 channels</li> <li>Watch timer</li> <li>1 channel</li> <li>Watchdog timer</li> <li>1 channel</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Timer outpu                                        | its                        | 3 (1 with 14 bit PWM output capability)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Clock output                                       |                            | 19.5 kHz, 39.1 kHz, 78.1 kHz, 156 kHz, 313 kHz, 625 kHz (5.0 MHz main system clock operation) 32.768 kHz (32.768 kHz subsystem clock operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Buzzer outp                                        | out                        | 1.2 kHz, 2.4 kHz, 4.9 kHz (5.0 MHz main system clock operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

**Notes 1.** The capacity of internal PROM can be changed according to the internal memory switching register (IMS) settings

**2.** The capacity of internal expanded RAM can be changed according to the internal expanded RAM switching register (IXS) settings.

| Item              |                        | Function                                                               |

|-------------------|------------------------|------------------------------------------------------------------------|

| Vector interrupts | Maskable interrupt     | Internal: 9, external: 4                                               |

|                   | Non-maskable interrupt | Internal: 1                                                            |

|                   | Software interrupt     | Internal: 1                                                            |

| Test input        |                        | Internal: 1                                                            |

| Supply volt       | age                    | VDD = 2.7 to 5.5 V                                                     |

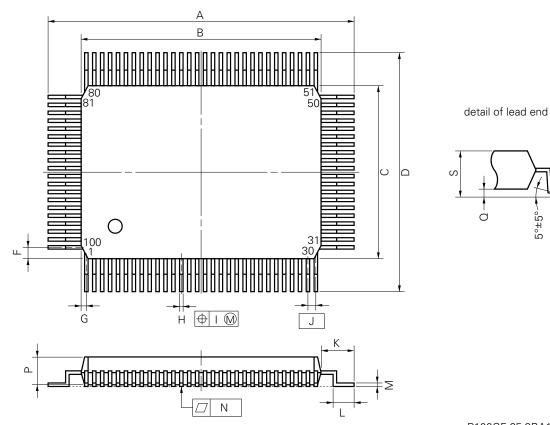

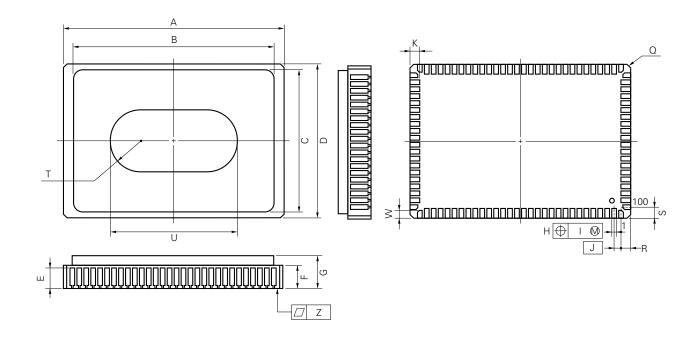

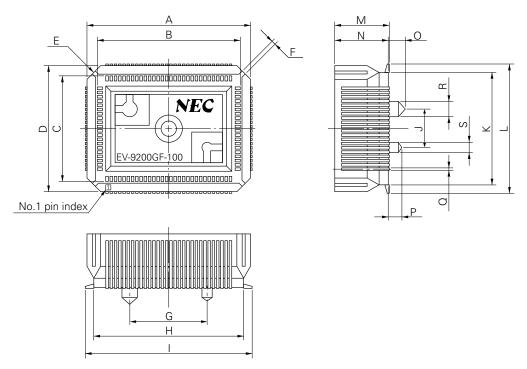

| Package           |                        | 100-pin plastic QFP (14 × 20 mm)     100-pin ceramic WQFN (14 × 20 mm) |

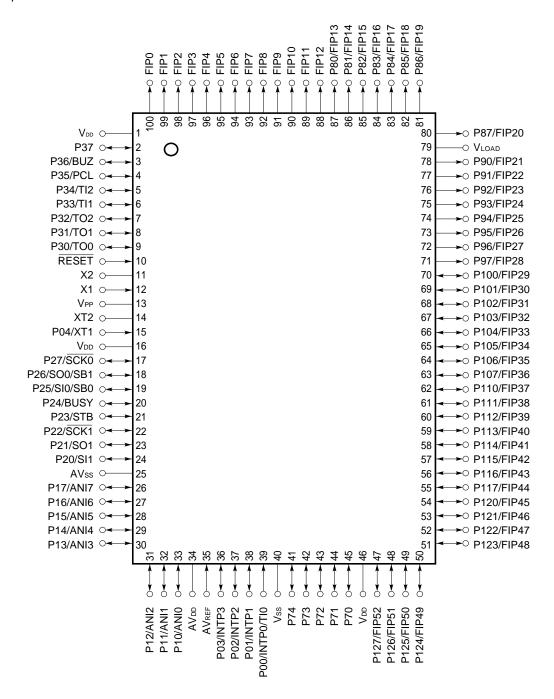

#### PIN CONFIGURATION (TOP VIEW)

#### (1) Normal operating mode

- 100-pin plastic QFP (14  $\times$  20 mm)  $\mu$ PD78P0208GF-3BA

- 100-pin ceramic WQFN (14  $\times$  20 mm)  $\mu$ PD78P0208KL-T

Cautions 1. Connect the VPP pin to Vss directly.

- 2. Connect the AVDD pin to VDD.

- 3. Connect the AVss pin to Vss.

P120-P127

SCK0, SCK1 : Serial Clock

PCL P00-P04 Port 0 Programmable Clock **Buzzer Clock** P10-P17 Port 1 BUZ

P20-P27 : Port 2 STB Strobe P30-P37 Port 3 BUSY Busy

P70-P74 : Port 7 FIP0-FIP52 Fluorescent Indicator Panel : Port 8 : Negative Power Supply P80-P87 VLOAD : Crystal (Main System Clock) P90-P97 : Port 9 X1, X2 P100-P107 : Port 10 XT1, XT2 : Crystal (Subsystem Clock)

P110-P117 : Port 11 RESET : Reset : Port 12 ANI0-ANI7 : Analog Input

INTP0-INTP3: Interrupt from Peripherals  $AV_{DD}$ : Analog Power Supply

TI0-TI2 : Timer Input AVss : Analog Ground

TO0-TO2 : Timer Output AVREF Analog Reference Voltage

SB0, SB1 Serial Bus  $V_{DD}$ **Power Supply**

SI0, SI1 Serial Input  $V_{\mathsf{PP}}$ **Programming Power Supply**

SO0, SO1 : Serial Output Ground Vss

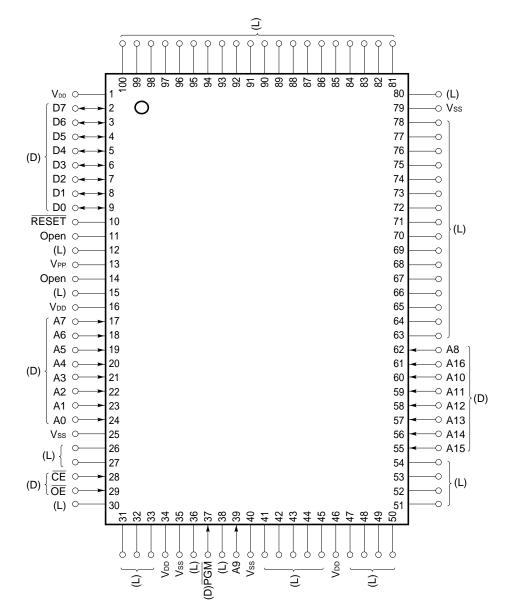

#### (2) PROM programming mode

- 100-pin plastic QFP (14  $\times$  20 mm)  $\mu$ PD78P0208GF-3BA

- 100-pin ceramic WQFN (14  $\times$  20 mm)  $\mu$ PD78P0208KL-T

Cautions 1. (L) : Connect to Vss through individual pull-down resistors.

2. (D) : To be connected through drivers.

3. Vss : Connect to ground.

4. RESET : Set to low level.

5. Open : Do not connect.

A0-A16 : Address Bus RESET : Reset

D0-D7 : Data Bus VDD : Power Supply

CE : Chip Enable VPP : Programming Power Supply

OE : Output Enable Vss : Ground

PGM : Program

#### **BLOCK DIAGRAM**

# **CONTENTS**

|   | 1.  | DIFFERENCES BETWEEN THE $\mu$ PD/8P0208 AND MASK ROM PRODUCTS           | 11 |

|---|-----|-------------------------------------------------------------------------|----|

|   | 2.  | LIST OF PIN FUNCTIONS                                                   | 12 |

|   |     | 2.1 PINS FOR NORMAL OPERATING MODE                                      | 12 |

|   |     | 2.2 PINS FOR PROM PROGRAMMING MODE                                      | 15 |

|   |     | 2.3 I/O CIRCUITS FOR PINS AND TREATMENT OF UNUSED PINS                  | 16 |

|   | 3.  | INTERNAL MEMORY SWITCHING (IMS) REGISTER                                | 20 |

|   | 4.  | INTERNAL EXPANDED RAM SWITCHING (IXS) REGISTER                          | 21 |

|   | 5.  | PROM PROGRAMMING                                                        | 22 |

|   |     | 5.1 OPERATION MODE                                                      | 22 |

|   |     | 5.2 PROM WRITE SEQUENCE                                                 | 24 |

|   |     | 5.3 PROM READ SEQUENCE                                                  | 28 |

|   | 6.  | ERASURE CHARACTERISTICS (μPD78P0208KL-T ONLY)                           | 29 |

|   | 7.  | PROTECTIVE FILM COVERING THE ERASURE WINDOW ( $\mu$ PD78P0208KL-T ONLY) | 29 |

|   | 8.  | SCREENING ONE-TIME PROM PRODUCTS                                        | 29 |

| * | 9.  | ELECTRICAL SPECIFICATIONS                                               | 30 |

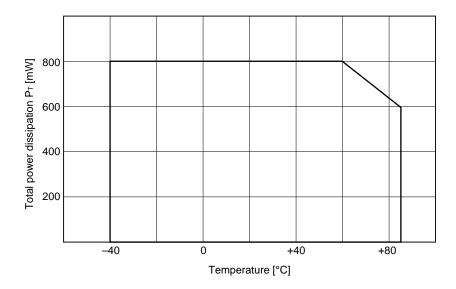

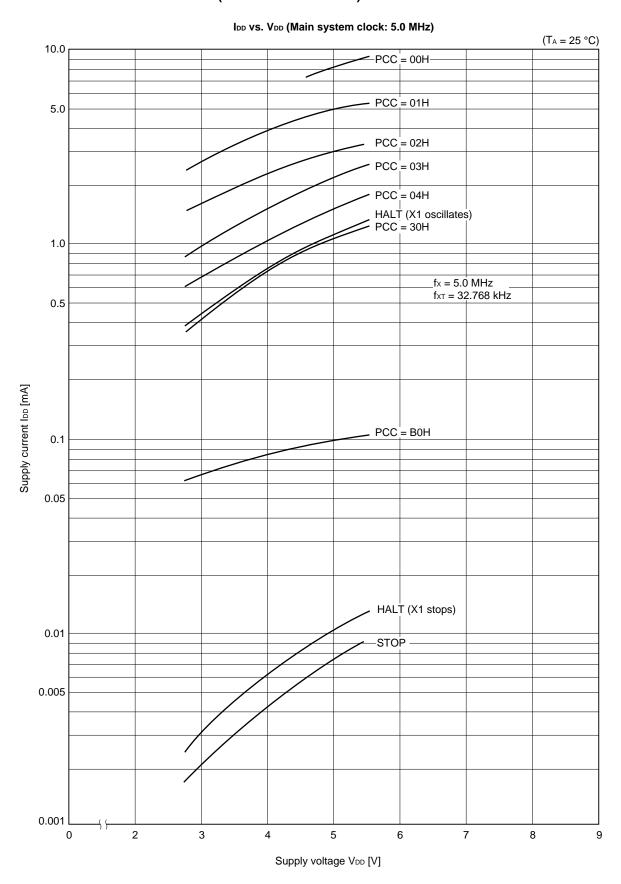

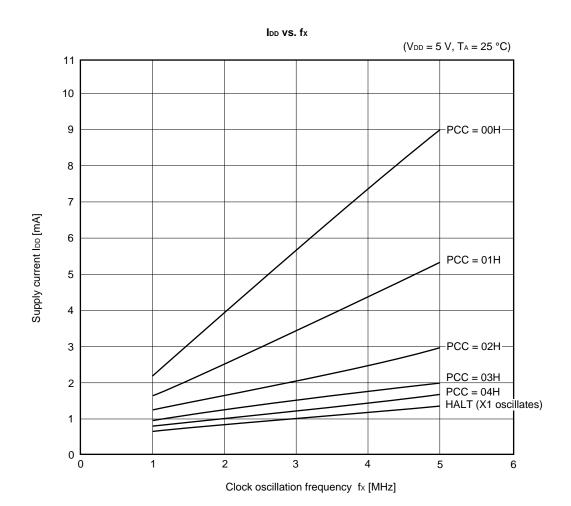

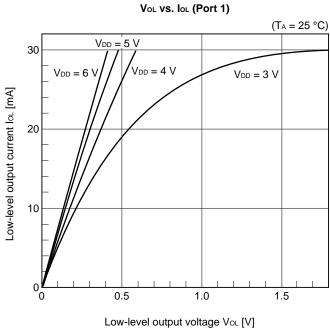

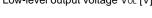

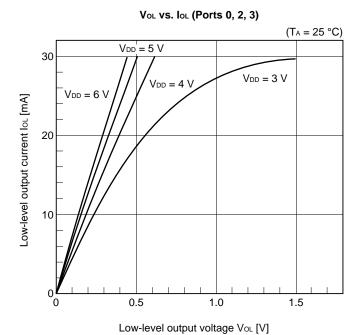

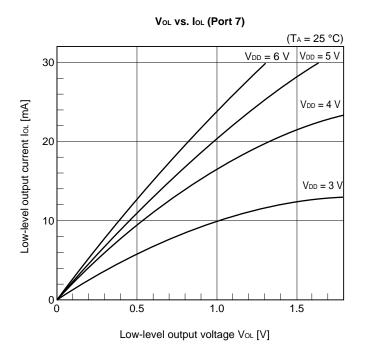

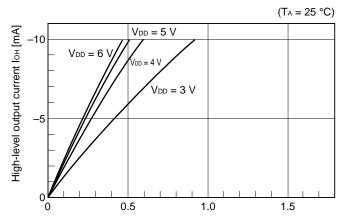

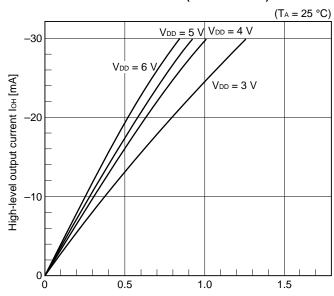

| * | 10. | CHARACTERISTIC CURVE (REFERENCE VALUE)                                  | 57 |

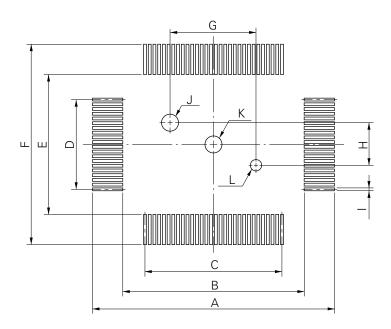

|   | 11. | PACKAGE DRAWINGS                                                        | 62 |

| * | 12. | RECOMMENDED SOLDERING CONDITIONS                                        | 64 |

|   | ΑP  | PENDIX A DEVELOPMENT TOOLS                                              | 65 |

|   | ΔΡ  | PENDIX B. RELATED DOCUMENTS                                             | 69 |

# 1. DIFFERENCES BETWEEN THE $\mu$ PD78P0208 AND MASK ROM PRODUCTS

The  $\mu$ PD78P0208 contains an on-chip one-time PROM in which data can be written once or an EPROM featuring repetitive program write and deletion.

Functions other than PROM specifications and mask options can be set as equivalent to those of mask ROM products, by setting the internal memory switching register (IMS) and internal expansion RAM switching register (IXS) accordingly.

Table 1-1 lists the points of difference between the  $\mu$ PD78P0208 and mask ROM products.

Table 1-1 Differences between μPD78P0208 and Mask ROM Products

| Item                                                                                                      | μPD78P0208                                              | Mask ROM products                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROM structure                                                                                             | One-time PROM/EPROM                                     | Mask ROM                                                                                                                                                    |

| ROM capacity                                                                                              | 60K bytes                                               | μPD780204: 32K bytes<br>μPD780205: 40K bytes<br>μPD780206: 48K bytes<br>μPD780208: 60K bytes                                                                |

| Internal expansion RAM capacity                                                                           | 1024 bytes                                              | μPD780204: None<br>μPD780205: None<br>μPD780206: 1024 bytes<br>μPD780208: 1024 bytes                                                                        |

| Changing the internal ROM capacity using the internal memory switching register (IMS)                     | PossibleNote 1                                          | Impossible                                                                                                                                                  |

| Changing the internal expansion RAM capacity using the internal expansion RAM switching register (IXS)    | PossibleNote 2                                          | Impossible                                                                                                                                                  |

| Includes IC pins                                                                                          | No                                                      | Yes                                                                                                                                                         |

| Includes VPP pins                                                                                         | Yes                                                     | No                                                                                                                                                          |

| P30/T00-P32/T02,P33/TI1<br>P34/TI2, P35/PCL, P36/BUZ, P37                                                 | No on-chip pull-down resistors                          | An on-chip pull-down resistor can be incorporated for each pin by specifying mask options.                                                                  |

| P70-P74                                                                                                   | No on-chip pull-up resistors                            | An on-chip pull-up resistor can be incorporated for each pin by specifying mask options.                                                                    |

| FIP0-FIP12                                                                                                | On-chip pull-down resistors provided (connect to VLOAD) | An on-chip pull-down resistor can be incorporated for each pin by specifying mask options.                                                                  |

| P80/FIP13-P87/FIP20 P90/FIP21-P97/FIP28 P100/FIP29-P107/FIP36 P110/FIP37-P117/FIP44 P120/FIP45-P127/FIP52 | No on-chip pull-down resistors                          | An on-chip pull-down resistor can be incorporated for each pin by specifying mask options. (These pins can be connected to VLOAD or Vss in four-bit units.) |

| Electrical characteristics                                                                                | Refer to the data sheet of each product                 |                                                                                                                                                             |

Notes 1. A RESET input sets the internal PROM capacity to 60K bytes.

2. A RESET input sets the internal expansion RAM capacity to 1024 bytes.

## 2. LIST OF PIN FUNCTIONS

# 2.1 PINS FOR NORMAL OPERATING MODE

# (1) Port pins (1/2)

| Pin name              | I/O   |                   | Function                                                                                                                            | Reset | Combination pin |

|-----------------------|-------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|

| P00                   | Input | Port 0.           | Input only                                                                                                                          | Input | INTP0/TI0       |

| P01                   | I/O   | 5-bit I/O port.   | Each pin can be designated as an input                                                                                              | Input | INTP1           |

| P02                   |       |                   | or output pin separately. If used as an input port, an on-chip pull-up resistor can                                                 |       | INTP2           |

| P03                   |       |                   | be used by software.                                                                                                                |       | INTP3           |

| P04 <sup>Note 1</sup> | Input |                   | Input only                                                                                                                          | Input | XT1             |

| P10-P17               | I/O   | separately.       | e designated as an input or output pin put port, an on-chip pull-up resistor can be                                                 | Input | ANIO-ANI7       |

| P20                   | I/O   | Port 2.           |                                                                                                                                     | Input | SI1             |

| P21                   |       | 8-bit I/O port.   | a decimated as an input or output pin                                                                                               |       | SO1             |

| P22                   |       | separately.       | h pin can be designated as an input or output pin arately.  sed as an input port, an on-chip pull-up resistor can be d by software. |       | SCK1            |

| P23                   |       |                   |                                                                                                                                     |       | STB             |

| P24                   |       | used by softwar   |                                                                                                                                     |       | BUSY            |

| P25                   |       |                   |                                                                                                                                     |       | SI0/SB0         |

| P26                   |       |                   |                                                                                                                                     |       | SO0/SB1         |

| P27                   |       |                   |                                                                                                                                     |       | SCK0            |

| P30                   | I/O   | Port 3.           |                                                                                                                                     | Input | TO0             |

| P31                   |       | 8-bit I/O port.   | e designated as an input or output pin                                                                                              |       | TO1             |

| P32                   |       | separately.       | accignated ac an input of output pin                                                                                                |       | TO2             |

| P33                   |       | Can directly driv |                                                                                                                                     |       | TI1             |

| P34                   |       | used by softwar   | put port, an on-chip pull-up resistor can be re.                                                                                    |       | TI2             |

| P35                   |       |                   |                                                                                                                                     |       | PCL             |

| P36                   |       |                   |                                                                                                                                     |       | BUZ             |

| P37                   |       |                   |                                                                                                                                     |       | _               |

- **Notes 1.** When using pin combination P04/XT1 as an input port, set bit 6 of the processor clock control register (PCC) to 1 (do not use the subsystem clock oscillator circuit's on-chip feedback resistor).

- 2. When using pin combination P10/ANI0-P17/ANI7 as the analog input for the A/D converter, set input mode for port 1. This setting disables the on-chip pull-up resistors.

\*

# (1) Port pins (2/2)

| Pin name  | I/O    | Function                                                                                                                                                     | Reset  | Combination pin |

|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------|

| P70-P74   | I/O    | Port 7.  N-ch open-drain 5-bit I/O port.  Each pin can be designated as an input or output pin separately.  Can directly drive LEDs.                         | Input  |                 |

| P80-P87   | Output | Port 8. P-ch open-drain 8-bit high withstand voltage output port. Can directly drive LEDs.                                                                   | Output | FIP13-FIP20     |

| P90-P97   | Output | Port 9. P-ch open-drain 8-bit high withstand voltage output port. Can directly drive LEDs.                                                                   | Output | FIP21-FIP28     |

| P100-P107 | I/O    | Port 10. P-ch open-drain 8-bit high withstand voltage output port. Each pin can be designated as an input or output pin separately. Can directly drive LEDs. | Input  | FIP29-FIP36     |

| P110-P117 | I/O    | Port 11. P-ch open-drain 8-bit high withstand voltage I/O port. Each pin can be designated as an input or output pin separately. Can directly drive LEDs.    | Input  | FIP37-FIP44     |

| P120-P127 | I/O    | Port 12. P-ch open-drain 8-bit high withstand voltage I/O port. Each pin can be designated as an input or output pin separately. Can directly drive LEDs.    | Input  | FIP45-FIP52     |

# (2) Non-port pins (1/2)

| Pin name    | I/O    | Function                                                                                                                                                | Reset  | Combination pin |

|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------|

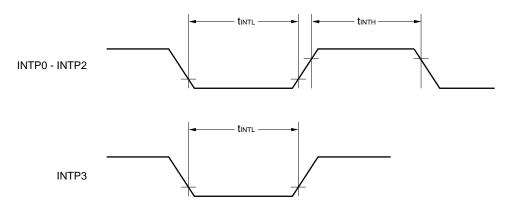

| INTP0       | Input  | Can be set for effective edge (rising edge, falling edge, or                                                                                            | Input  | P00/TI0         |

| INTP1       |        | both rising and falling edges).                                                                                                                         |        | P01             |

| INTP2       |        | Inputs external interrupts.                                                                                                                             |        | P02             |

| INTP3       |        | Falling edge detection and external interrupt input                                                                                                     | Input  | P03             |

| SI0         | Input  | Input of serial data for serial interface                                                                                                               | Input  | P25/SB0         |

| SI1         |        |                                                                                                                                                         |        | P20             |

| SO0         | Output | Output of serial data for serial interface                                                                                                              | Input  | P26/SB1         |

| SO1         |        |                                                                                                                                                         |        | P21             |

| SB0         | I/O    | Input/output of serial data for serial interface                                                                                                        | Input  | P25/SI0         |

| SB1         |        |                                                                                                                                                         |        | P26/SO0         |

| SCK0        | I/O    | Serial clock input/output for serial interface                                                                                                          | Input  | P27             |

| SCK1        |        |                                                                                                                                                         |        | P22             |

| STB         | Output | Output of automatic transmit/receive strobe signal for serial interface                                                                                 | Input  | P23             |

| BUSY        | Input  | Input of automatic transmit/receive busy signal for serial interface                                                                                    | Input  | P24             |

| TI0         | Input  | External count clock input to 16-bit timer (TM0)                                                                                                        | Input  | P00/INTP0       |

| TI1         |        | External count clock input to 8-bit timer (TM1)                                                                                                         |        | P33             |

| TI2         |        | External count clock input to 8-bit timer (TM2)                                                                                                         |        | P34             |

| TO0         | Output | 16-bit timer (TM0) output (combined with 14-bit PWM output)                                                                                             | Input  | P30             |

| TO1         |        | 8-bit timer (TM1) output                                                                                                                                |        | P31             |

| TO2         |        | 8-bit timer (TM2) output                                                                                                                                |        | P32             |

| PCL         | Output | Clock output (for trimming main system clock or subsystem clock)                                                                                        | Input  | P35             |

| BUZ         | Output | Buzzer output                                                                                                                                           | Input  | P36             |

| FIP0-FIP12  | Output | High current output with high withstand voltage for the grids/segments of FIP controller/driver On-chip pull-down resistors provided (connect to VLOAD) | Output | _               |

| FIP13-FIP20 | Output | High current output with high withstand voltage for the grids/segments of FIP controller/driver                                                         | Output | P80-P87         |

| FIP21-FIP28 | Output | High current output with high withstand voltage for the                                                                                                 | Output | P90-P97         |

| FIP29-FIP36 | 1      | grids/segments of FIP controller/driver                                                                                                                 | Input  | P100-P107       |

| FIP37-FIP44 | ]      |                                                                                                                                                         |        | P110-P117       |

| FIP45-FIP52 | 1      |                                                                                                                                                         |        | P120-P127       |

| VLOAD       | _      | Pull-down resistor connection for FIP controller/driver                                                                                                 | _      | _               |

^

# (2) Non-port pins (2/2)

| Pin name        | I/O   | Function                                               | Reset | Combination pin |

|-----------------|-------|--------------------------------------------------------|-------|-----------------|

| ANI0-ANI7       | Input | Analog input for A/D converter                         | Input | P10-P17         |

| AVREF           | Input | Reference voltage input for A/D converter              | _     | _               |

| AVDD            | _     | Analog power supply for A/D converter. Connect to Vdd. | _     | _               |

| AVss            | _     | Ground for A/D converter. Connect to Vss.              | _     | _               |

| RESET           | Input | System reset input                                     | _     | _               |

| X1              | Input | Crystal connection for main system clock oscillation   | _     | _               |

| X2              | _     |                                                        | _     | _               |

| XT1             | Input | Crystal connection for subsystem clock oscillation     | Input | P04             |

| XT2             | _     |                                                        | _     |                 |

| V <sub>DD</sub> | _     | Positive power supply                                  | _     | _               |

| V <sub>PP</sub> | _     | Connect to Vss.                                        | _     | _               |

| Vss             | _     | Ground level                                           | _     | _               |

# 2.2 PINS FOR PROM PROGRAMMING MODE

| Pin name        | I/O   | Function                                                                                                                                                       |  |

|-----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RESET           | Input | PROM programming mode selection.  PROM programming mode is selected when +5 V or +12.5 V is added to the VPP pin or low-level input is added to the RESET pin. |  |

| V <sub>PP</sub> | Input | PROM programming mode selection and high voltage input during program write or verification                                                                    |  |

| A0-A16          | Input | Address bus                                                                                                                                                    |  |

| D0-D7           | I/O   | Data bus                                                                                                                                                       |  |

| CE              | Input | PROM enable input/program pulse input                                                                                                                          |  |

| ŌĒ              | Input | Read strobe input to PROM                                                                                                                                      |  |

| PGM             | Input | Program/program inhibit input during PROM programming mode                                                                                                     |  |

| V <sub>DD</sub> | _     | Positive power supply                                                                                                                                          |  |

| Vss             | _     | Ground level                                                                                                                                                   |  |

# 2.3 I/O CIRCUITS FOR PINS AND TREATMENT OF UNUSED PINS

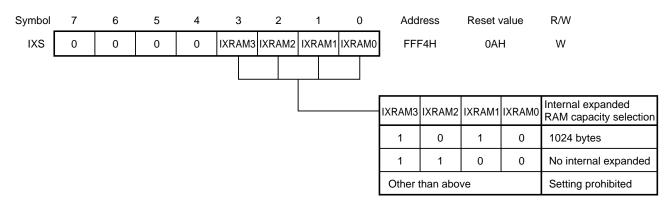

Table 2-1 describes the types of I/O circuits for pins and the treatment of unused pins.

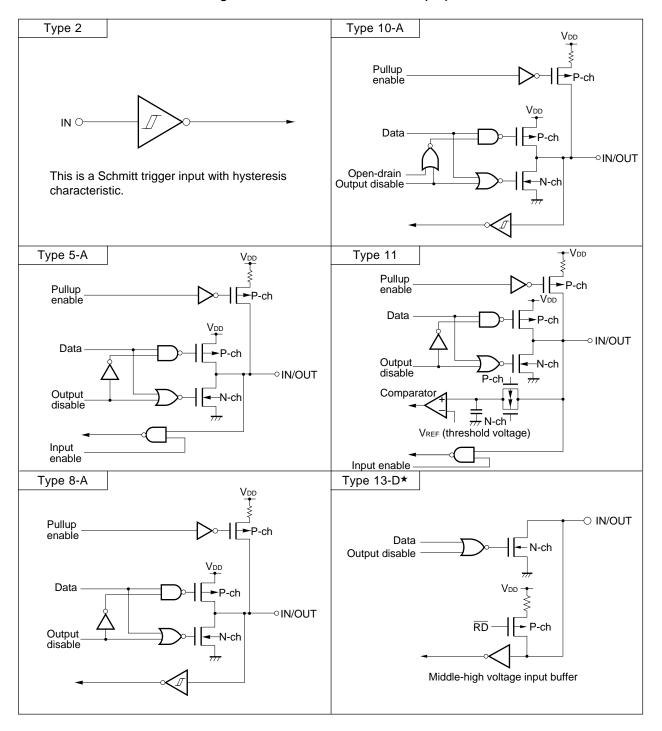

Fig. 2-1 shows the configuration of these various types of I/O circuits.

Table 2-1 Types of I/O Circuits for Pins (1/2)

| Pin name            | I/O circuit type | I/O    | Recommended connection method for unused pins                              |

|---------------------|------------------|--------|----------------------------------------------------------------------------|

| P00/INTP0/TI0       | 2                | Input  | Connect to Vss.                                                            |

| P01/INTP1           | 8-A              | I/O    | Connect to Vss through a separate resistor.                                |

| P02/INTP2           |                  |        |                                                                            |

| P03/INTP3           |                  |        |                                                                            |

| P04/XT1             | 16               | Input  | Connect to V <sub>DD</sub> or V <sub>SS</sub> .                            |

| P10/ANI0-P17/ANI7   | 11               | I/O    | Connect to V <sub>DD</sub> or V <sub>SS</sub> through a separate resistor. |

| P20/SI1             | 8-A              | ]      |                                                                            |

| P21/SO1             | 5-A              |        |                                                                            |

| P22/SCK1            | 8-A              |        |                                                                            |

| P23/STB             | 5-A              |        |                                                                            |

| P24/BUSY            | 8-A              |        |                                                                            |

| P25/SI0/SB0         | 10-A             |        |                                                                            |

| P26/SO0/SB1         | ]                |        |                                                                            |

| P27/SCK0            | =                |        |                                                                            |

| P30/TO0             | 5-A              |        |                                                                            |

| P31/TO1             |                  |        |                                                                            |

| P32/TO2             |                  |        |                                                                            |

| P33/TI1             | 8-A              |        |                                                                            |

| P34/TI2             |                  |        |                                                                            |

| P35/PCL             | 5-A              |        |                                                                            |

| P36/BUZ             |                  |        |                                                                            |

| P37                 |                  |        |                                                                            |

| P70-P74             | 13-D             |        |                                                                            |

| FIP0-FIP12          | 14               | Output | Open                                                                       |

| P80/FIP13-P87/FIP20 | 14-B             |        |                                                                            |

| P90/FIP21-P97/FIP28 | 1                |        |                                                                            |

\_

Table 2-1 Types of I/O Circuits for Pins (2/2)

| Pin name              | I/O circuit type | I/O   | Recommended connection method for unused pins                              |

|-----------------------|------------------|-------|----------------------------------------------------------------------------|

| P100/FIP29-P107/FIP36 | 15-B             | I/O   | Connect to V <sub>DD</sub> or V <sub>SS</sub> through a separate resistor. |

| P110/FIP37-P117/FIP44 |                  |       |                                                                            |

| P120/FIP45-P127/FIP52 |                  |       |                                                                            |

| RESET                 | 2                | Input | _                                                                          |

| XT2                   | 16               | _     | Open                                                                       |

| AVREF                 | _                |       | Connect to Vss.                                                            |

| AV <sub>DD</sub>      |                  |       | Connect to V <sub>DD</sub> .                                               |

| AVss                  |                  |       | Connect to Vss.                                                            |

| VLOAD                 |                  |       |                                                                            |

| Vpp                   |                  |       | Connect to Vss directly.                                                   |

\*

Fig. 2-1 List of I/O Circuits for Pins (1/2)

Fig. 2-1 List of I/O Circuits for Pins (2/2)

Type 15-B\*

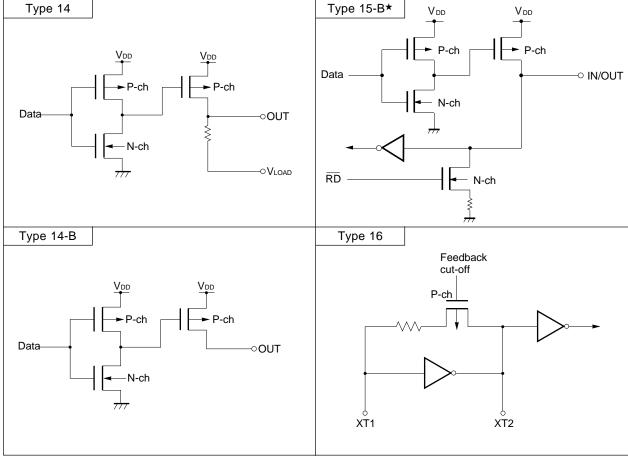

# 3. INTERNAL MEMORY SWITCHING (IMS) REGISTER

This register enables the software to avoid using part of the internal memory. The IMS register can be set to establish the same memory mapping as used in ROM products that have a different internal ROM capacity.

The IMS register is set using 8-bit memory operation instructions.

A RESET input sets the IMS register to CFH.

Fig. 3-1 Format of IMS Register

Table 3-1 lists IMS register settings for memory mapping equivalent to various mask ROM products.

Table 3-1 IMS Register Settings

| Target mask ROM product | IMS setting |

|-------------------------|-------------|

| μPD780204               | C8H         |

| μPD780205               | CAH         |

| μPD780206               | ССН         |

| μPD780208               | CFH         |

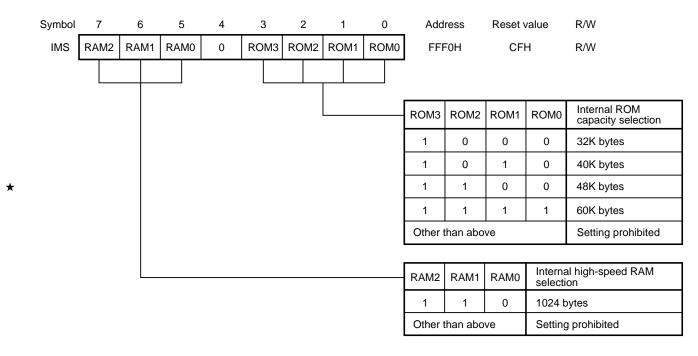

# 4. INTERNAL EXPANDED RAM SWITCHING (IXS) REGISTER

The  $\mu$ PD78P0208 can set the IXS register to establish the same memory mapping as used in ROM products that have a different internal expanded RAM capacity.

The IXS register is set using 8-bit memory operation instructions.

A RESET input sets the IXS register to 0AH.

Fig. 4-1 Format of IXS Register

Table 4-1 lists IXS register settings for memory mapping equivalent to various mask ROM products.

Table 4-1 IXS Register Settings

| Target mask ROM product | IXS setting |

|-------------------------|-------------|

| μPD780204               | 0CH         |

| μPD780205               |             |

| μPD780206               | 0AH         |

| μPD780208               |             |

•

$\star$

#### 5. PROM PROGRAMMING

The  $\mu$ PD78P0208 has an on-chip 60KB PROM device for use as program memory. When programming, set the VPP and  $\overline{\text{RESET}}$  pins for PROM programming mode. See **(2) PROM programming mode** in PIN CONFIGURATION (TOP VIEW) with regard to treatment of other, unused pins.

Caution Write a program in the range between addresses 0000H and EFFFH. (Set EFFFH in the programend address.) PROM programmers which cannot specify the writing address cannot be used.

#### 5.1 OPERATION MODE

PROM programming mode is selected when +5 V or +12.5 V is added to the VPP pin or low-level input is added to the  $\overline{\text{RESET}}$  pin. This mode can be set to operation mode by setting the  $\overline{\text{CE}}$  pin,  $\overline{\text{OE}}$  pin, and  $\overline{\text{PGM}}$  pin as shown in Table 5-1 below.

In addition, the PROM contents can be read by setting read mode.

**Table 5-1 PROM Programming Operation Mode**

| Pin Operation mode | RESET | Vpp     | V <sub>DD</sub> | CE | ŌĒ | PGM | D0-D7          |

|--------------------|-------|---------|-----------------|----|----|-----|----------------|

| Page data latch    | L     | +12.5 V | +6.5 V          | Н  | L  | Н   | Data input     |

| Page write         |       |         |                 | Н  | Н  | L   | High impedance |

| Byte write         |       |         |                 | L  | Н  | L   | Data input     |

| Program verify     |       |         |                 | L  | L  | Н   | Data output    |

| Program inhibit    |       |         |                 | ×  | Н  | Н   | High impedance |

|                    |       |         |                 | ×  | L  | L   |                |

| Read               |       | +5 V    | +5 V            | L  | L  | Н   | Data output    |

| Output disable     |       |         |                 | L  | Н  | ×   | High impedance |

| Standby            |       |         |                 | Н  | ×  | ×   | High impedance |

$\times$  = L or H

#### (1) Read mode

Set  $\overline{CE}$  to L and  $\overline{OE}$  to L to set read mode.

#### (2) Output disable mode

Set  $\overline{\mathsf{OE}}$  to H to set high impedance for data output and output disable mode.

Consequently, if several  $\mu$ PD78P0208 devices are connected to a data bus, the  $\overline{OE}$  pins can be controlled to select data output from any of the devices.

#### (3) Standby mode

Set  $\overline{CE}$  to H to set standby mode.

In this mode, data output is set to high impedance regardless of the  $\overline{\sf OE}$  setting.

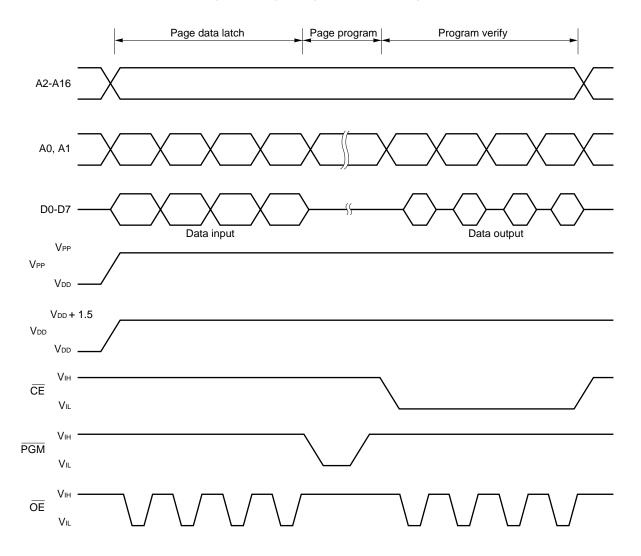

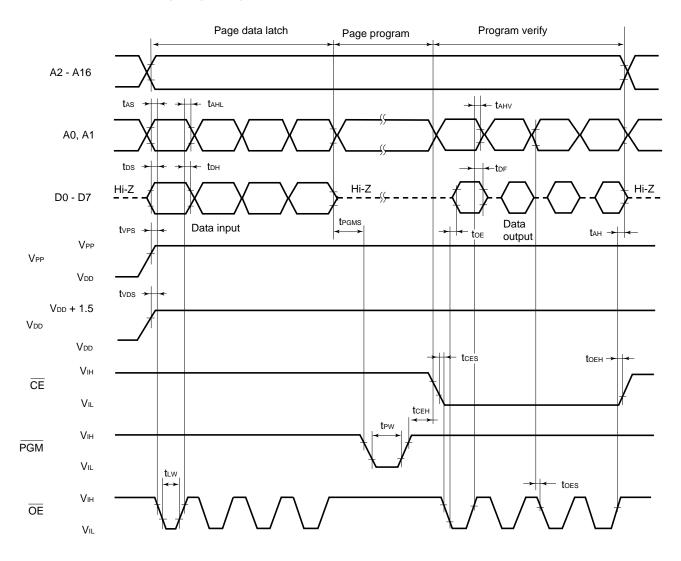

#### (4) Page data latch mode

At the beginning of page write mode, set  $\overline{CE}$  to H,  $\overline{PGM}$  to H, and  $\overline{OE}$  to L to set page data latch mode. In this mode, 1 page (4 bytes) of data are latched to the internal address/data latch circuit.

#### (5) Page write mode

After latching the address and data for one page (4 bytes) using page data latch mode, adding a 0.1 ms program pulse (active, low) to the  $\overline{PGM}$  pin with both  $\overline{CE}$  and  $\overline{OE}$  set to H causes page write to be executed. Later, setting both  $\overline{CE}$  and  $\overline{OE}$  to L causes program verification to be executed.

If programming is not completed after one program pulse, the write and verify operations may be repeated X times (where X - 10).

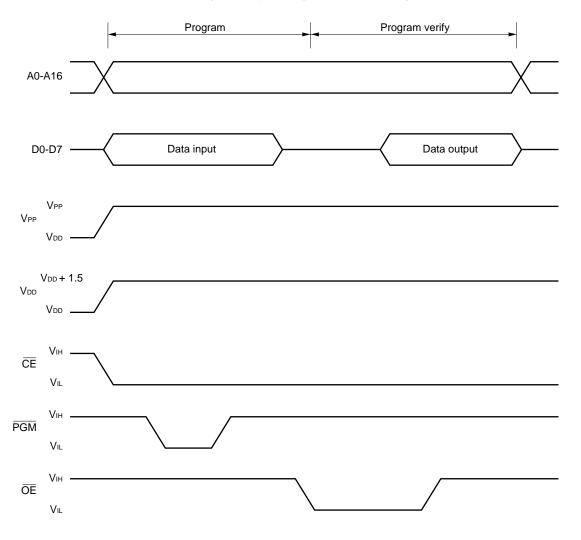

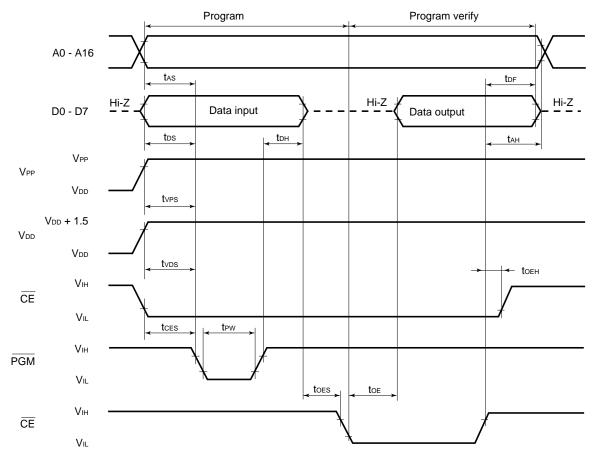

#### (6) Byte write mode

Adding a 0.1 ms program pulse (active, low) to the PGM pin with CE set to L and OE set to H causes byte write to be executed. Later, setting OE to L causes program verification to be executed.

If programming is not completed after one program pulse, the write and verify operations may be repeated X times (where X - 10).

### (7) Program verify mode

Set  $\overline{CE}$  to L,  $\overline{PGM}$  to H, and  $\overline{OE}$  to L to set program verify mode. Use verify mode for verification following each write operation.

#### (8) Program inhibit mode

Program inhibit mode is used to write to a single device when several  $\mu$ PD78P0208 devices are connected in parallel to  $\overline{OE}$ , VPP, and D0 to D7 pins.

Use the page write mode or byte write mode described above for each write operation. Write operations cannot be done for devices in which the  $\overline{PGM}$  pin has been set to H.

#### 5.2 PROM WRITE SEQUENCE

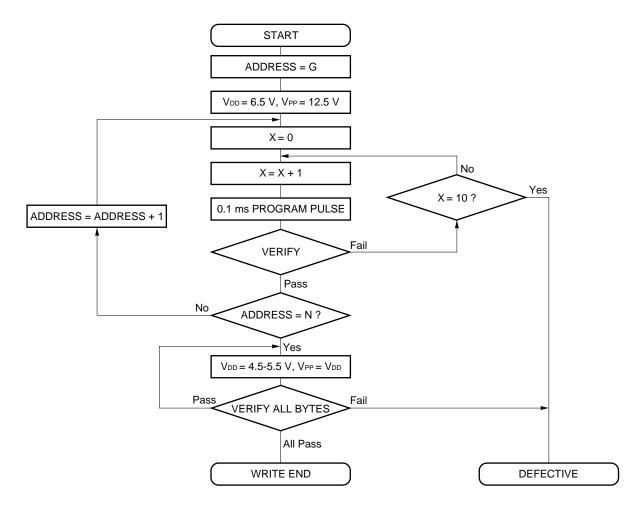

START ADDRESS = G  $V_{\text{DD}} = 6.5 \text{ V}, \text{ Vpp} = 12.5 \text{ V}$ X = 0LATCH ADDRESS = ADDRESS + 1 LATCH ADDRESS = ADDRESS + 1 LATCH ADDRESS = ADDRESS + 1 ADDRESS = ADDRESS + 1 LATCH No X = X + 1Yes X = 10 ? 0.1 ms PROGRAM PULSE Fail **VERIFY 4 BYTES Pass** ADDRESS = N? Yes  $V_{DD} = 4.5-5.5 \text{ V}, V_{PP} = V_{DD}$ Pass Fail VERIFY ALL BYTES All Pass WRITE END DEFECTIVE

Fig. 5-1 Page Program Mode Flowchart

G = Start address

N = Program end address

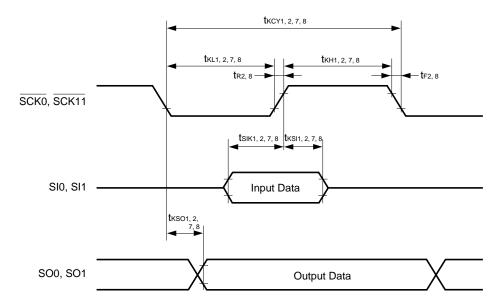

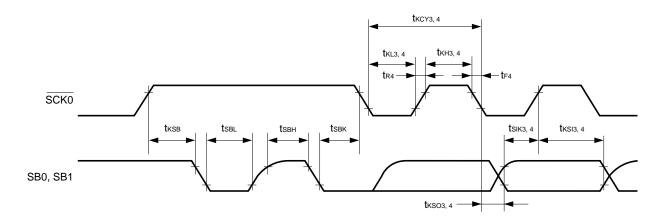

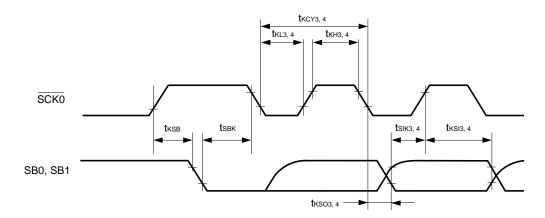

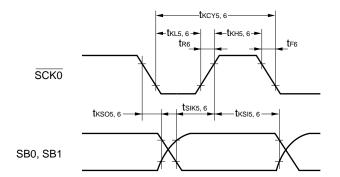

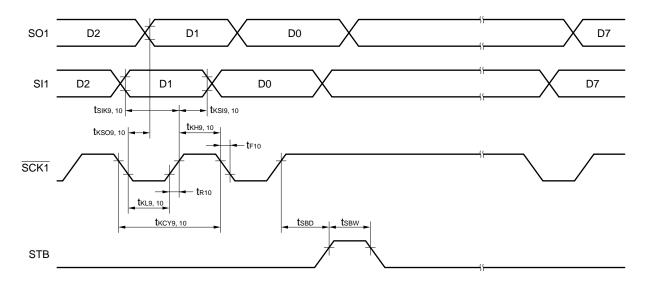

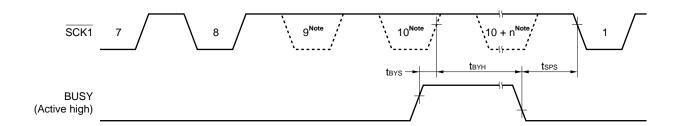

Fig. 5-2 Page Program Mode Timing

Fig. 5-3 Byte Program Mode Flowchart

G = Start address

N = Program end address

Fig. 5-4 Byte Program Mode Timing

Cautions 1. Add VDD before VPP, and turn off the VDD after VPP.

- 2. Do not allow VPP to exceed +13.5 V including overshoot.

- 3. Reliability problems may result if the device is inserted or pulled out while +12.5 V is applied at VPP.

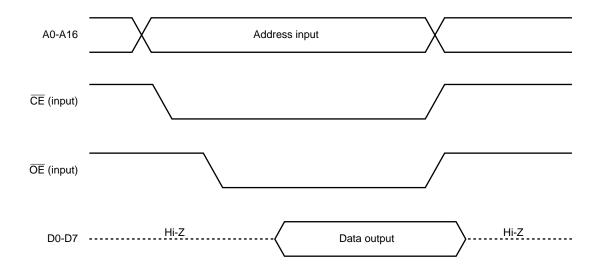

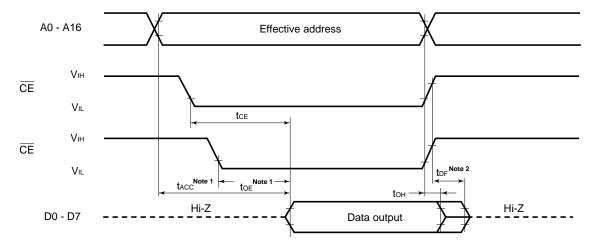

#### 5.3 PROM READ SEQUENCE

Follow this sequence to read the PROM contents to an external data bus (D0 to D7).

- (1) Set the RESET pin to low level and add +5 V to the VPP pin. See (2) PROM programming mode in PIN CONFIGURATION (TOP VIEW) with regard to treatment of other, unused pins.

- (2) Add +5 V to the VDD and VPP pins.

- (3) Input the data address to be read to pins A0 to A16.

- (4) Set read mode.

- (5) Output the data to pins D0 to D7.

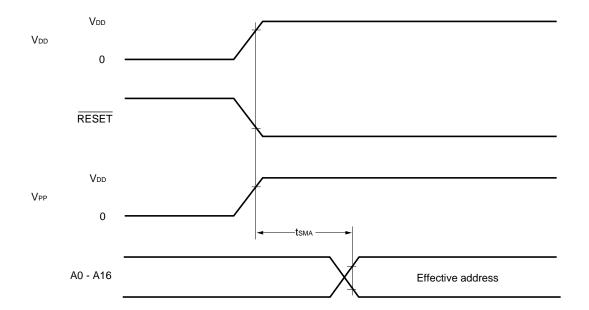

Fig. 5-5 shows the timing of steps (2) to (5) above.

Fig. 5-5 PROM Read Timing

#### 6. ERASURE CHARACTERISTICS (μPD78P0208KL-T ONLY)

Data written in the  $\mu$ PD78P0208KL-T program memory can be erased (FFH); therefore users can write other data in the memory.

To erase the written data, expose the erasure window to light with a wavelength shorter than approx. 400 nm. Normally, ultraviolet light with a wavelength of 254 nm is employed. The amount of light required to completely erase the data is as follows:

- Intensity of ultraviolet light × erasing time: 30 W•s/cm² min.

- Erasing time: 40 minutes or more (When using a 12000 μW/cm² ultraviolet lamp. It may, however, take more time due to lamp deterioration, dirt on the erasure window, or the like.)

The ultraviolet lamp should be placed within 2.5 cm from the erasure window during erasure. In addition, if a filter is attached to the ultraviolet lamp, remove the filter before erasure.

## 7. PROTECTIVE FILM COVERING THE ERASURE WINDOW (µPD78P0208KL-T ONLY)

To prevent EPROM from being erased inadvertently by light other than that from the lamp used for erasing EPROM, or to prevent the internal circuits other than EPROM from malfunctioning by light, stick a protective film on the erasure window except when EPROM is to be erased.

## 8. SCREENING ONE-TIME PROM PRODUCTS

NEC cannot execute a complete test of one-time PROM products ( $\mu$ PD78P0208GF-3BA) due to their structure before shipment. It is recommended that you screen (verify) PROM products after writing necessary data into them and storing them at 125 °C for 24 hours.

NEC offers a charged service called QTOP microcomputer service. This service includes writing to one-time PROM, marking, screening, and verification. Ask your sales representative for details.

# **★** 9. ELECTRICAL SPECIFICATIONS

## ABSOLUTE MAXIMUM RATINGS (TA = 25 °C)

| Parameter                     | Symbol                | Conditions                                                                  | Rating                                        | Unit        |                                               |    |

|-------------------------------|-----------------------|-----------------------------------------------------------------------------|-----------------------------------------------|-------------|-----------------------------------------------|----|

| Supply voltage                | V <sub>DD</sub>       |                                                                             |                                               |             | -0.3 to +7.0                                  | V  |

|                               | VLOAD                 |                                                                             |                                               |             | V <sub>DD</sub> - 45 to V <sub>DD</sub> + 0.3 | V  |

|                               | V <sub>PP</sub>       |                                                                             |                                               |             | -0.3 to +13.5                                 | V  |

|                               | AV <sub>DD</sub>      |                                                                             |                                               |             | -0.3 to V <sub>DD</sub> + 0.3                 | V  |

|                               | AVREF                 |                                                                             |                                               |             | -0.3 to V <sub>DD</sub> + 0.3                 | V  |

|                               | AVss                  |                                                                             |                                               |             | -0.3 to +0.3                                  | V  |

| Input voltate                 | VI1                   | P01 to P04, P10 to P17, P20 to P27, P30 to P3                               | 37, X1                                        | , X2, RESET | -0.3 to V <sub>DD</sub> + 0.3                 | V  |

|                               | V <sub>I2</sub>       | P00/A9                                                                      | -0.3 to +13.5                                 | V           |                                               |    |

|                               | Vıз                   | P70-P74                                                                     | -0.3 to +16                                   | V           |                                               |    |

|                               | V <sub>14</sub>       | P100 to P107, P110 to P117, P120 to P127                                    | V <sub>DD</sub> - 45 to V <sub>DD</sub> + 0.3 | V           |                                               |    |

| Output voltage                | Vo                    | P01 to P03, P10 to P17, P20 to P27, P30 to                                  | P37,                                          | P70 to P74  | -0.3 to V <sub>DD</sub> + 0.3                 | V  |

|                               | Vod                   | P80 to P87, P90 to P97, P100 to P107, P110<br>P127, FIP0 to FIP12           | V <sub>DD</sub> – 45 to V <sub>DD</sub> + 0.3 | V           |                                               |    |

| Analog input voltage          | Van                   | ANI0 to ANI7                                                                | AVss - 0.3 to AVREF + 0.3                     | V           |                                               |    |

| High-level                    | <sub>OH</sub> Note1   | 1 pin of P01 to P03, P10 to P17, P20 to P27                                 | -10                                           | mA          |                                               |    |

| output current                |                       | Total for P01 to P03, P10 to P17, P02 to P2                                 | -30                                           | mA          |                                               |    |

|                               |                       | 1 pin of FIP0 to FIP12, P80 to P87, P90 to P9<br>P110 to P117, P120 to P127 | -30                                           | mA          |                                               |    |

|                               |                       | Total for P80 to P87, FIP0 to FIP12 Peak value                              |                                               | Peak value  | -240                                          | mA |