# **MOS INTEGRATED CIRCUIT** μ**PD77C25, 77P25**

# DIGITAL SIGNAL PROCESSOR

The µPD77C25, 77P25 are 16-bit fixed point CMOS signal processors intended for real-time digital processing of speech signals.

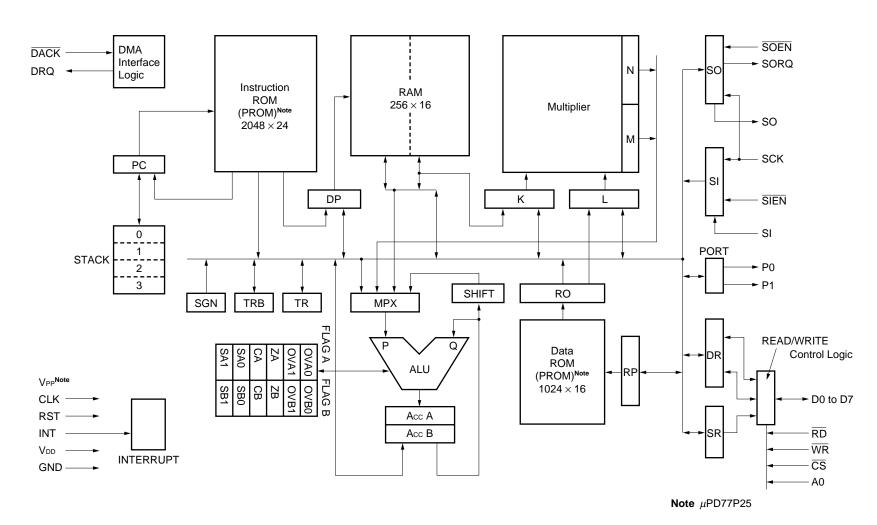

Each device consists of a parallel multiplier (16 x 16 bits  $\rightarrow$  31 bits), an ALU (16 bits), an instruction ROM (2,048 x 24 bits), a data ROM (1,024 x 16 bits), a data RAM (256 x 16 bits), I/O ports, and others. All instructions consist of 24 bits or one word instruction are executed in 122 ns (at fcLK = 8.192 MHz) including sum of product computations.

Since signals that interfaces with the host CPU are provided, the  $\mu$ PD77C25, 77P25 can cover a variety of applications, serving as an I/O processor. Moreover, they can also be used as single-chip CPU.

The  $\mu$ PD77C25, 77P25 provide an instruction ROM each four times larger than that of the former product  $\mu$ PD7720 signal processor. Additionally, each device has a data ROM and a data RAM, both of which are two times larger, and a processing speed faster. Furthermore, the  $\mu$ PD77C25, 77P25 can replace the  $\mu$ PD7720 as they have the same pin connections.

The instruction sets of the  $\mu$ PD77C25, 77P25 are upward-compatible with that of the  $\mu$ PD7720 at the assembler source program level.

The  $\mu$ PD77C25 is version with on-chip resources including the instruction ROM and data ROM are constructed in mask ROMs; the µPD77P25 has PROMs. The µPD77P25D is an UVEPROM type and the µPD77P25C/L/GW is an one time PROM (OTP) type.

**Remark** In this document, the  $\mu$ PD77C25 refers to the  $\mu$ PD77C25, 77P25 unless otherwise specified.

#### **FEATURES**

JE

- Biquad Digital Filter (with sampling performed at 8 kHz): Equivalent to 113 filters

- · On-chip exclusive parallel multiplier

- Instruction ROM

- Data ROM

- Data RAM

- Dual accumulator method

- On-chip serial input and serial output interfaces

- · On-chip host CPU bus interface

- · On-chip DMA interface

- Upward-compatible with the μPD7720 at assembler source program level

- Pin-compatible with μPD7720

- Low-power CMOS

The information in this document is subject to change without notice

- : 16 bits x 16 bits  $\rightarrow$  31 bits

- : 2,048 words x 24 bits

- : 1,024 words x 16 bits

- : 256 words x 16 bits

# **\*** ORDERING INFORMATION

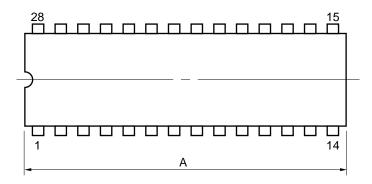

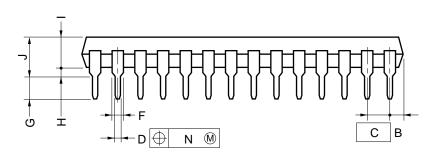

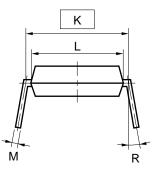

| Part Number     | Package                            |

|-----------------|------------------------------------|

| μPD77C25C-xxx   | 28-pin plastic DIP (600 mil)       |

| μPD77C25GW-xxx  | 32-pin plastic SOP (525 mil)       |

| μPD77C25L-xxx   | 44-pin plastic QFJ (650 x 650 mil) |

| μPD77P25C       | 28-pin plastic DIP (600 mil)       |

| μPD77P25D       | 28-pin ceramic DIP (600 mil)       |

| $\mu$ PD77P25GW | 32-pin plastic SOP (525 mil)       |

| μPD77P25L       | 44-pin plastic QFJ (650 x 650 mil) |

|                 |                                    |

\_\_\_\_\_

**Remark** xxx is a ROM code suffix.

NEC

µPD77C25, 77P25

**BLOCK DIAGRAM**

ω

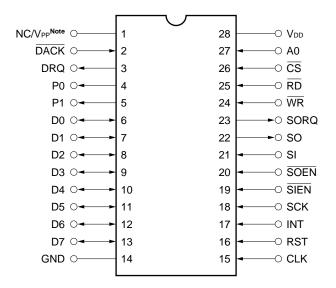

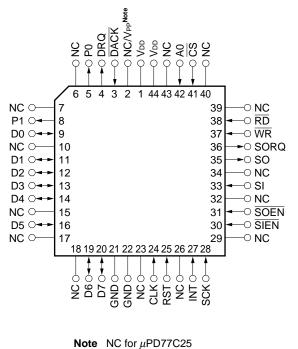

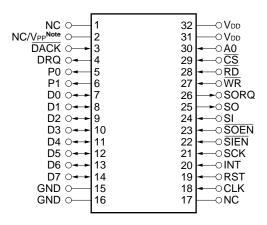

\* PIN CONFIGURATIONS (Top View)

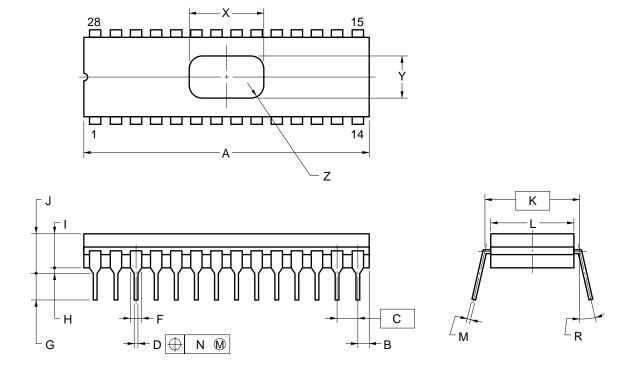

28-pin plastic DIP (600 mil): μPD77C25C-xxx, μPD77P25C 28-pin ceramic DIP (600 mil): μPD77P25D

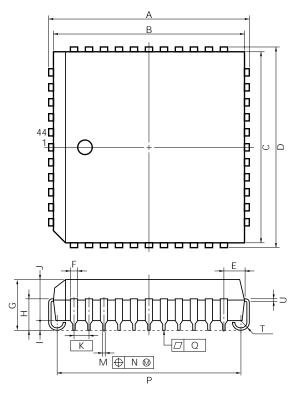

44-pin plastic QFJ (650 x 650 mil): µPD77C25L-xxx, µPD77P25L

V<sub>PP</sub> for *μ*PD77P25

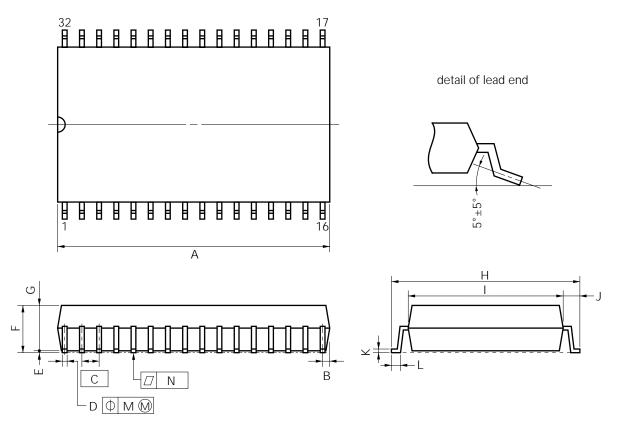

32-pin plastic SOP (525 mil): µPD77C25GW-xxx, µPD77P25GW

**Note** NC for μPD77C25 V<sub>PP</sub> for μPD77P25

| A0       | : Address Input                | RST : Reset Input          |                    |

|----------|--------------------------------|----------------------------|--------------------|

| CLK      | : Clock Input                  | SCK : Serial Data Clock    |                    |

| CS       | : Chip Select Input            | SI : Serial Data Input     |                    |

| DACK     | : DMA Acknowledge Signal Input | SIEN : Serial Input Enable | Э                  |

| DRQ      | : DMA Request Signal Output    | SO : Serial Data Output    | t                  |

| D0 to D7 | : Data Bus Input/Output        | SOEN : Serial Output Enab  | ole                |

| GND      | : Ground                       | SORQ : Serial Output Requ  | uest Signal Output |

| INT      | : Interrupt Input              | VDD : Power Supply         |                    |

| NC       | : No Connection                | VPP : Power Supply         |                    |

| P0, P1   | : General Purpose Output Port  | WR : Write Signal Input    |                    |

| RD       | : Read Signal Input            |                            |                    |

# DIFFERENCES BETWEEN $\mu \text{PD77C25}$ and $\mu \text{PD7720}$ family

The  $\mu$ PD77C25 has enhanced functions of the conventional  $\mu$ PD7720 16-bit signal processor family and thus is compatible with the  $\mu$ PD7720 family at an assembler source program level.

Differences between  $\mu \text{PD77C25}$  and  $\mu \text{PD7720}$  family is shown below.

#### Differences between $\mu$ PD77C25 and $\mu$ PD7720 Family

|              | Item                      | μPD7720                       | μPD77C25                                   |  |  |  |  |  |

|--------------|---------------------------|-------------------------------|--------------------------------------------|--|--|--|--|--|

| Memory       | Instruction ROM           | 512 x 23 bits                 | 2,048 x 24 bits                            |  |  |  |  |  |

|              | Data ROM                  | 510 x13 bits                  | 1,024 x 16 bits                            |  |  |  |  |  |

|              | RAM                       | 128 x 16 bits                 | 256 x 16 bits                              |  |  |  |  |  |

| Register     | PC                        | 9 bits                        | 11 bits                                    |  |  |  |  |  |

|              | STACK                     | 9 bits x 4 levels             | 11 bits x 4 levels                         |  |  |  |  |  |

|              | RP                        | 9 bits                        | 10 bits                                    |  |  |  |  |  |

|              | RO                        | 13 bits                       | 16 bits                                    |  |  |  |  |  |

|              | DP                        | 7 bits                        | 8 bits                                     |  |  |  |  |  |

|              | TRB                       | without                       | with                                       |  |  |  |  |  |

| Instruction  | length                    | 23 bits (w/3-bit DPH.M field) | 24 bits (w/4-bit DPH.M field)              |  |  |  |  |  |

| Added inst   | ructions                  | _                             | JDPLNO<br>JDPLNF<br>M8 to MF (Modified DP) |  |  |  |  |  |

| RQM flag o   | operations                | Not affected in DMA mode      | Affected even in DMA mode                  |  |  |  |  |  |

| Operation    | clock (Instruction cycle) | 8.192 MHz (244 ns)            | 77C25: 8.192 MHz (122 ns)                  |  |  |  |  |  |

| Serial inter | face clock                | 2.048 MHz                     | 77C25: 4.096 MHz                           |  |  |  |  |  |

# CONTENTS

| 1. | PIN FUNCTIONS                                                           |    |

|----|-------------------------------------------------------------------------|----|

|    | 1.1 Pin Functions for Normal Operation                                  | 8  |

|    | 1.2 Pin Functions for Programming/reading $\mu$ PD77P25's Internal PROM | 10 |

| 2. | INTERNAL FUNCTIONS                                                      | 11 |

| 3. | INSTRUCTION                                                             |    |

|    | 3.1 OP Instruction                                                      | 16 |

|    | 3.2 RT Instruction                                                      | 17 |

|    | 3.3 JP Instruction                                                      | 17 |

|    | 3.4 LD Instruction                                                      | 17 |

|    | 3.5 Instruction Code                                                    |    |

| 4. | INSTRUCTION EXECUTION TIMING                                            |    |

| 5. | $\mu$ PD77P25 PROM INTERFACE                                            | 27 |

| 6. | ELECTRICAL SPECIFICATIONS                                               |    |

| 7. | PACKAGE DRAWINGS                                                        | 47 |

| 8. | RECOMMENDED SOLDERING CONDITIONS                                        | 51 |

# 1. PIN FUNCTIONS

# 1.1 Pin Functions for Normal Operation

| Pin                                                           |                                           | Pin Number                    |                               | I/O              | Function                                                                                                                                                                           |  |  |  |  |

|---------------------------------------------------------------|-------------------------------------------|-------------------------------|-------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Designation                                                   | 28-pin Plastic DIP,<br>28-pin Ceramic DIP | 32-pin Plastic SOP            | 44-pin Plastic QFJ            |                  |                                                                                                                                                                                    |  |  |  |  |

| Vdd                                                           | 28                                        | 31<br>32                      | 1<br>44                       | —                | Power input pin.<br>Inputs +5 V.                                                                                                                                                   |  |  |  |  |

| GND                                                           | 14                                        | 15<br>16                      | 21<br>22                      | _                | Ground pin                                                                                                                                                                         |  |  |  |  |

| V <sub>PP</sub> Note                                          | 1                                         | 2                             | 2                             | _                | Program power input pin of internal PROM.<br>Connected to +12.5 V for programming<br>PROM or to +5 V for normal operation.                                                         |  |  |  |  |

| CLK                                                           | 15                                        | 18                            | 24                            | I                | Inputs system clock having frequency as high as instruction cycle.                                                                                                                 |  |  |  |  |

| RST                                                           | 16                                        | 19                            | 25                            | I                | Inputs system reset signal (active high).<br>Width of signal must be wider than 2<br>system clock periods.                                                                         |  |  |  |  |

| INT                                                           | 17                                        | 20                            | 27                            | I                | Inputs mask able interrupt signal (active<br>high). Program execution jumps to<br>interrupt address at rising edge of this pin<br>and with interrupt enabled.                      |  |  |  |  |

| CS                                                            | 26                                        | 29                            | 41                            | I                | Inputs chip select signal (active low). "0"<br>input to this pin enables read/write<br>operation by host CPU via D0 through D7.                                                    |  |  |  |  |

| AO                                                            | 27                                        | 30                            | 42                            | I                | Inputs address signal.<br>Signal input to this pin selects register<br>whose contents are to be output from D0<br>through D7 during read operation. "0"<br>selects DR and "1", SR. |  |  |  |  |

| RD                                                            | 25                                        | 28                            | 38                            | I                | Inputs read signal (active low).<br>"0" to this pin causes D0 through D7 to<br>output data (with $\overline{CS} = "0"$ ).                                                          |  |  |  |  |

| WR                                                            | 24                                        | 27                            | 37                            | I                | Inputs write signal (active low).<br>"0" to this pin causes D0 through D7 to<br>input data (with $\overline{CS} =$ "0").                                                           |  |  |  |  |

| D0 to D7 Refer to PIN Refer to PI<br>CONFIGURATION CONFIGURAT |                                           | Refer to PIN<br>CONFIGURATION | Refer to PIN<br>CONFIGURATION | I/O<br>(3-state) | Constitute 8-bit data bus for host CPU and perform input/output according to $\overline{CS}$ , $\overline{RD}$ , and $\overline{WR}$ .                                             |  |  |  |  |

| DRQ                                                           | 3                                         | 4                             | 4                             | 0                | Outputs DMA request signal (active high) and requests data transfer in DMA mode.                                                                                                   |  |  |  |  |

\* Note This pin serves as VPP only for the  $\mu$ PD77P25 and is NC for the  $\mu$ PD77C25. When designing the  $\mu$ PD77C25 application system compatible with the  $\mu$ PD77P25, it is no problem to supply +5 V to pin 1.

| Pin         |                                           | Pin Number         |                    | I/O            | Function                                                                                                                                                                                                                                   |  |  |  |  |

|-------------|-------------------------------------------|--------------------|--------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Designation | 28-pin Plastic DIP,<br>28-pin Ceramic DIP | 32-pin Plastic SOP | 44-pin Plastic QFJ |                |                                                                                                                                                                                                                                            |  |  |  |  |

| DACK        | 2                                         | 3                  | 3                  | I              | Inputs DMA acknowledge signal (active<br>low). "0" is input when DMA is enabled.<br>When DACK = "0", this pin performs similar<br>operation to when CS = "0" and A0 = "0".<br>Since it is always valid, input "1" when<br>DMA is not used. |  |  |  |  |

| P0, P1      | 4<br>5                                    | 5<br>6             | 5<br>8             | 0              | Constitute general-purpose output port.                                                                                                                                                                                                    |  |  |  |  |

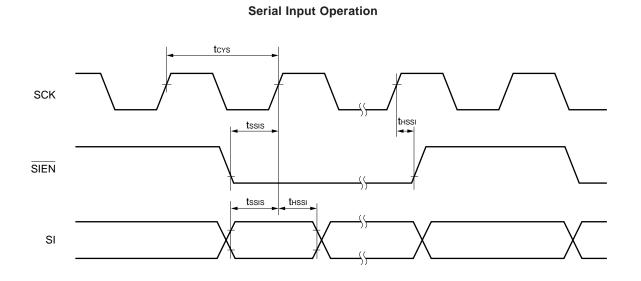

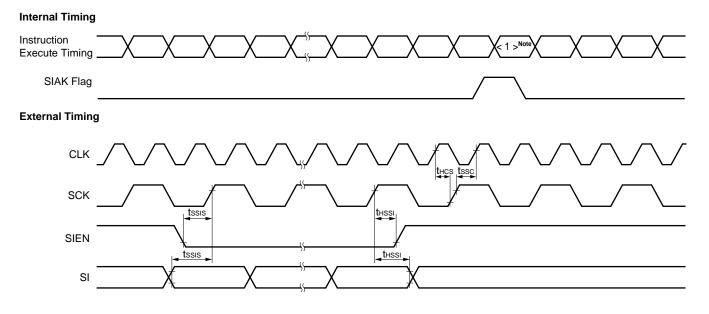

| SI          | 21                                        | 24                 | 33                 | I              | Inputs serial data which is read into the processor in synchronization with rising edge of SCK clock.                                                                                                                                      |  |  |  |  |

| SIEN        | 19                                        | 22                 | 30                 | I              | Inputs serial input enable signal (active<br>low) to enable serial data input from SI.<br>This signal must be kept high level during<br>the RST is high level and two instruction<br>cycles after the RST becames low level.               |  |  |  |  |

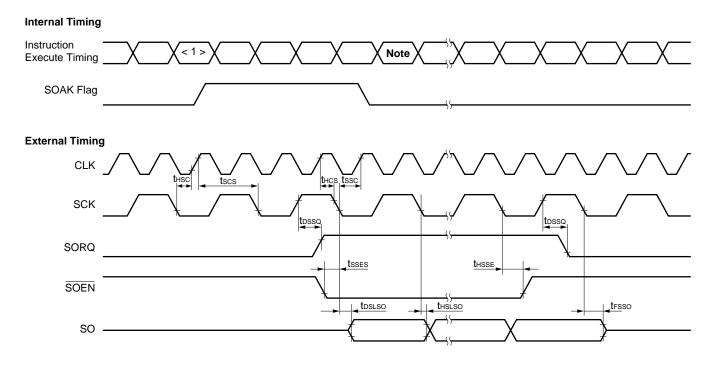

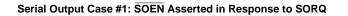

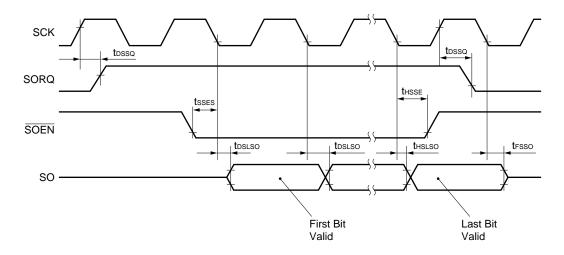

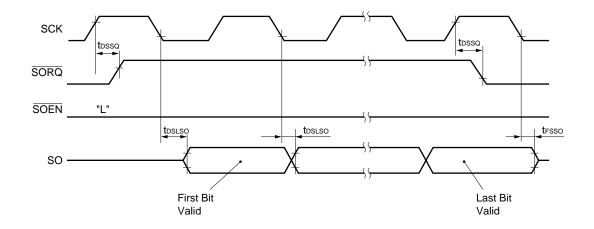

| SO          | 22                                        | 25                 | 35                 | O<br>(3-state) | Outputs serial data which is output in synchronization with falling edge of SCK clock.                                                                                                                                                     |  |  |  |  |

| SOEN        | 20                                        | 23                 | 31                 | I              | Outputs serial output enable signal (active<br>low) to enable serial data output from SO.<br>This signal must be kept high level during<br>the RST is high level and two instruction<br>cycles after the RST becames low level.            |  |  |  |  |

| SORQ        | 23                                        | 26                 | 36                 | Ο              | Outputs serial output request signal (active<br>high).<br>It is set to "1" when output data are set in<br>SO register and cleared to "0" when on<br>completion of output.                                                                  |  |  |  |  |

| SCK         | 18                                        | 21                 | 28                 | I              | Inputs serial data clock with which serial data input/output is synchronized.                                                                                                                                                              |  |  |  |  |

#### Pin Name Pin Number Pin Name Function for Normal 28-pin Plastic DIP, 32-pin Plastic SOP 44-pin Plastic QFJ Operation 28-pin Ceramic DIP A0 27 30 42 A0 Input address (viewed from external device) for programming/reading PROM WR A1 24 27 37 (instruction ROM and data ROM). A2 23 36 SORQ 26 A3 22 25 35 SO A4 24 33 21 SI A5 20 23 31 SOEN A6 19 22 30 SIEN A7 18 21 28 SCK A8 17 20 27 INT A9 15 18 24 CLK 5 8 P1 A10 5 A11 4 6 5 P0 4 4 DRQ A12 3 A13 2 3 DACK 3 D0 to D7 9 D0 to D7 Inputs/outputs data for PROM (instruction 6 to 13 7 to 14 ROM and data ROM) 11 to 14 16 19, 20 CE CS 26 29 41 PROM program strobe signal (active low) OE 25 RD 28 38 PROM read strobe signal (active low) Vpp 1 2 2 Vpp Power pin for programming PROM Apply +12.5 V for writing and +5 V for reading. Vdd 28 32 1 Vdd Power pin 31 44 Apply +6 V for programming and +5 V for reading. GND 14 15 21 GND Ground pin 16 22 16 19 25 RST Sets PROM program or read mode. Mode is set when +12.5 V is applied.

# 1.2 Pin Functions for Programming/reading $\mu$ PD77P25's Internal PROM

# 2. INTERNAL FUNCTIONS

# (1) Instruction ROM

This ROM stores the program of the  $\mu$ PD77C25 and has a capacity of 2K words x 24 bits. In the  $\mu$ PD77C25 this is a mask ROM and in the  $\mu$ PD77P25 is a PROM. The address to be accessed is specified by Program Counter (PC).

# (2) PC (Program Counter)

This is a 11-bit binary counter which specifies an address of the instruction ROM. Usually, the contents of PC are incremented by one each time an instruction is fetched, and accordingly the instructions are read from ROM in order.

When jump instruction or subroutine call instruction is executed, the NA (Next address) field value of the instruction is input to the PC. The return address saved in the stack is input to the PC in case that the return instruction is executed, and the interrupt address (100H) is input in case that an interrupt request is input to the INT pin with the interrupt enabled.

The reset input clears the PC contents to 00H and the program execution starts from address 0.

(3) STACK

The stack has 11 bit x 4 level, LIFO (Last-In First-Out) configuration and stores the return address when the subroutine call instruction is executed or an interrupt is generated. The return address is read out from the stack and input to the PC when the return instruction is executed.

(4) RAM

The RAM stores the data and is configured of 256 words x 16 bits. The address to be accessed is specified by Data Pointer (DP). In addition to transferring data to and from the internal data bus, the RAM can directly output data to the P input of ALU. It can also directly output to the K register the address data with DP6 replaced with "1".

(5) DP (Data Pointer)

The data pointer is an 8-bit register which specifies a RAM address. It is connected to the lower 8 bits of the internal data bus, and transfers data to and from the other registers through it.

The upper 4 bits of DP (DPH) can be qualified when exclusively ORed with the 4 bits of the DPHM field in an instruction.

The contents of the lower 4 bits of DP (DPL) can be incremented, decremented, or cleared depending on the specification of the DPL field in an instruction.

(6) Data ROM

The data ROM is a mask ROM in the  $\mu$ PD77C25 and a PROM in the  $\mu$ PD77P25. It stores various fixed data such as coefficients of filter and has a capacity of 1K words x 16 bits. The address to be accessed is specified by ROM Pointer (RP) and is output to the data bus and the input register L of the multiplier through ROM Output Buffer (RO).

# (7) RP (ROM Pointer)

The ROM Pointer is a 10-bit register which specifies a data ROM address to be accessed. It is connected to the lower 10 bits of the internal data bus.

The contents of RP can be decremented by specifying the RPDCR bit of an instruction.

# (8) RO (ROM Output Buffer)

The ROM output buffer is a 16 bits register which holds the data output by the data ROM. The contents of this register are directly output to the internal data bus and the input register L of the multiplier.

# (9) Multiplier

This is a parallel multiplier using secondary Booth's algorithm. It multiplies the 2's complement of the 16-bit data stored in the K and L registers in each instruction cycle. As a result, a sign bit and 30-bit data are obtained. The multiplier then stores the sign bit and the upper 15 bits of the 30-bit data in the M register. The lower 15 bits are stored in the upper 15 bits of the N register. ("0" is stored in the LSB.)

# (10) K and L registers

These are 16-bit registers which hold the data input from the multiplier. The K register can not only directly input the data from RAM but also transfer data to and from the internal data bus. The L register can directly input the data from the data ROM, in addition, it can transfer data to and from the internal data bus. The data which are input to the K and L registers are input to the multiplier simultaneously, and performs an arithmetic operation.

# (11) M and N registers

These are 16-bit registers which hold the results of the multiplication performed by the multiplier. The upper 16 bits of the multiplication results (i.e., sign bit plus the upper 15 bits) are stored in the M register. The lower 15 bits are stored in the N register ("0" is stored in the LSB). Both the M and N registers are connected to the P input of the ALU.

# (12) ALU and AccA, AccB

The ALU performs the following arithmetic operations of 16-bit data on two inputs: P and Q.

- OR

- AND

- XOR (Exclusive OR)

- SUB

- ADD

- Shift (only AccA and AccB)

- 1's complement (only AccA and AccB)

- P input: RAM, Internal DATA bus, M register, N register, SHIFT, 0000 (H)

- Q input: AccA, AccB

Both AccA and AccB are 16-bit accumulators which store the results of the arithmetic operation performed by the ALU. They are connected to the output of the ALU and the internal data bus. The ASL field of an instruction specifies which accumulator is to be used. The contents of AccA and AccB can be output to the internal data bus, and can input to Q input of the ALU and SHIFT.

(13) SHIFT

This is a register which shifts 16-bit data input from AccA and AccB. 1-bit shift right, 1-bit shift left, 2-bit shift left, 4-bit shift left, and 8-bit exchange can be performed.

(14) Flag registers FLAG A and FLAG B

FLAG A and FLAG B are both 6-bit registers that hold the result of the ALU operation. FLAG A operates when AccA is selected, while FLAG B operates when AccB is selected.

FLAG A and FLAG B consist of the following flag bits:

| FLAG A | SA1 | SA0 | CA | ZA | OVA1 | OVA0 |

|--------|-----|-----|----|----|------|------|

| FLAG B | SB1 | SB0 | СВ | ZB | OVB1 | OVB0 |

(a) CA, CB (Carry)

The flags store the carry or borrow resulting from the executed operation. (OPERATION: SUB, ADD, SBB, ADC, DEC, INC)

(b) ZA, ZB (Zero)

The flags are set to "1" if the result of the executed operation is "0"; otherwise, cleared to "0".

- (c) SA0, SB0 (Sign 0)The flags store the sign bit (MSB) of the result of the operation.

- (d) OVA0, OVB0 (Overflow 0)

The flags are set to "1" if an overflow in positive or negative direction has occurred as a result of the executed operation; otherwise, cleared to "0".

(e) OVA1, OVB1 (Overflow 1)

The flags set to "1" if an overflow has occurred the odd number of times as a result of the 3 operations executed, and set to "0" if it has occurred the even number of times. (OPERATION: SUB, ADD, SBB, ADC, DEC, INC)

(f) SA1, SB1 (Sign 1)

The flags are used with OVA1 or OVB1 to effectively process overflow. These indicates the direction in which the overflow (positive or negative) has, if any, occurred.

(15) TR, TRB (Temporary Register)

TR and TRB are 16-bit general-purpose registers which can be used to temporary latch data. They are connected to the internal data bus.

#### (16) SGN (Sign Register)

SGN is set to 8000H if the SA1 flag is "0" and to 7FFFH if the flag is "1". Therefore, the overflow compensation can be performed with one instruction by simply transferring the contents of the SGN register without a test instruction.

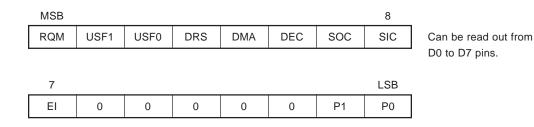

(17) SR (Status Register)

The status register is a register which hold the status the  $\mu$ PD77C25 needs to transfer data to/from external devices. It is internally handled as a 16-bit register, and the upper 8 bits can be read from an external device through D0 to D7 pins.

# NEC

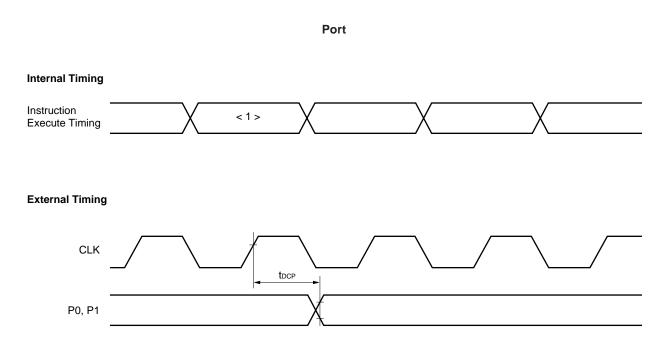

(a) P0, P1

The P0 and P1 correspond to output ports P0 and P1, and to which values input to these bits are directly output.

(b) EI (Enable Interrupt)

El is the bit to specify whether enables or disables interrupt.

- "0": Interrupt is disabled.

- "1": Interrupt is enabled.

- (c) SIC (SI Control)

SIC is the bit to specify the length of serial data input to SI pins.

- "0": The length of serial input data is specified 16-bit.

- "1": The length of serial input data is specified 8-bit.

- (d) SOC (SO Control)

SOC is the bit to specify the length of serial data output to SO pins.

"0": The length of serial output data is specified 16-bit.

"1": The length of serial output data is specified 8-bit.

(e) DRC (DR Control)

DRC is the bit to specify the length of data transfer to and from host CPU.

- "0": 16-bit length is specified.

- "1": 8-bit length is specified.

- (f) DMA (Direct Memory Access)

- DMA is the bit to specify mode to transfer data to and from host CPU.

- "0": non-DMA mode is specified.

- "1": DMA mode is specified.

- (g) DRS (DR Status)

DRS is the bit to indicate data transfer status of DR register in case of transferring 16-bit data. (DRC = 0)

- "0": It indicates transfer is terminated. (8-bit data is transferred two times.)

- "1": It indicates transfer is in progress.

- (h) USF0, USF1 (User's Flag)

USF0 and USF1 are the flag bits which can be freely used by user and can be used as a status bit in transferring data to/from external device.

(i) RQM (Request for Master)

RQM is the bit to indicate that  $\mu$ PD77C25 is requesting host CPU for data write/read.

- "0": It indicates that data read/write is externally performed.

- "1": It indicates that DR register is internally read/written.

This flag bit also changes in DMA mode.

(18) PORT

Ports are internally assigned to the same address as SR register (P0, P1) and can be used as output ports to external devices.

(19) DR (Data Register)

DR is the 16-bit register to interface to/from CPU. Since it is externally connected to the 8-bit bus, data is read from/written to external in units of 8 bits. Internally writing and reading are performed by 16-bit at a time. When the 8-bit mode is specified by DRC bit, only the lower 8 bits of the DR register (16 bits long) are valid.

# (20) READ/WRITE Control Logic

R/W logic constructs the control part to transfer data to/from external devices through D0-D7. The following operations are performed depending on the status of  $\overline{CS}$ , A0,  $\overline{RD}$ , and  $\overline{WR}$ .

| CS | A0 | WR | RD | Function                                         |

|----|----|----|----|--------------------------------------------------|

| 1  | Х  | Х  | Х  | Internal operation is not affected.              |

| Х  | Х  | 1  | 1  | D0-D7 are at high impedance levels.              |

| 0  | 0  | 0  | 1  | Data on D0 to D7 are latched to DR register.Note |

| 0  | 0  | 1  | 0  | Contents of DR are output D0-D7.Note             |

| 0  | 1  | 0  | 1  | Inhibit (SR is read only)                        |

| 0  | 1  | 1  | 0  | Eight MSBs of SR are output to D0-D7.            |

| 0  | х  | 0  | 0  | Inhibit (may not read and write simultaneously)  |

Note Eight MSBs or 8 LSBs of data register (DR) are used, depending on DR status bit (DRS).

(21) DMA Interface Logic

DMA Interface Logic controls DRQ signal using DACK signal. DRQ signal requests data transfer between DR register and external host processor or memory.

(22) SI (Serial Input Register)

The serial data from an external devices is input to the SI register. The data are taken into the register in synchronization of SCK, and are changed to the parallel data by the register. The parallel data is output to the internal data bus by the instruction. The serial data can be treated not only LSB first but MSB first.

# (23) SO (Serial Output Register)

This register loads the parallel data to be output from the internal data bus, and changes the data into serial, then outputs to the external devices. It can treat both LSB-first data and MSB-first data. The serial data is output in synchronization of SCK.

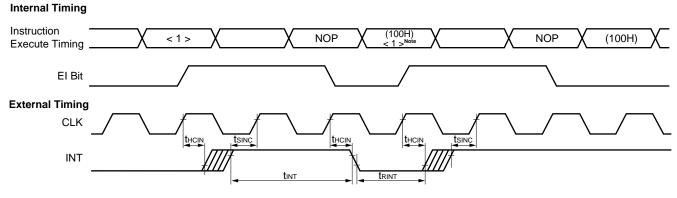

(24) INTERRUPT

This is the part to execute the interrupt process. An interrupt is detected at the rising edge of the INT signal when the EI bit of the SR register is set to "1". When the interrupt is accepted, the interrupt process that address is from 100H is executed.

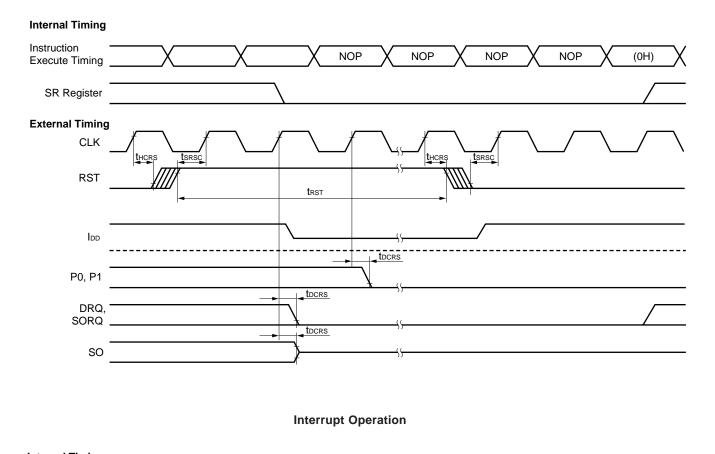

# (25) RST (Reset)

The followings are initialized to "0" by the RST signal.

- PC

- FLAG A, FLAG B

- SR register

- DRQ

- SORQ

- SI ACK flag, SO ACK flag

RP register is set to "3FFH". The other registers and contents of DATA RAM are not changed.

# NEC

# 3. INSTRUCTION

All instructions of the  $\mu$ PD77C25 are one word instruction; one instruction is composed of 24 bits. The instructions are divided into the following four types.

| OP instruction : | This instruction is used to perform operations such as ordinary arithmetic operations and data |

|------------------|------------------------------------------------------------------------------------------------|

|                  | transfer.                                                                                      |

- RT instruction : This instruction is return instruction.

- JP instruction : This instruction causes unconditional or conditional jump of program execution, or calls a subroutine.

- LD instruction : This loads 16-bit immediate data to the specified register.

# 3.1 OP Instruction

| 23 22 | 21        | 20  | 19 | 18 | 17  | 16 | 15          | 14 | 13 | 12 | 11 | 10   | 9 | 8     | 7 | 6  | 5  | 4 | 3 | 2 | 1  | 0 |

|-------|-----------|-----|----|----|-----|----|-------------|----|----|----|----|------|---|-------|---|----|----|---|---|---|----|---|

| 00    | P-<br>SEL | ЕСТ |    | Al | U_U |    | A<br>S<br>L | DI | PL |    | DF | Рн∙М |   | RPDCR |   | SF | RC |   |   | D | ST |   |

OP instruction has the following functions.

- (i) This instruction consists of six fields and two bits.

- (ii) Program Counter is incremented to the address hold at that time.

- (1) P-SELECT Field

This field selects P input of ALU.

(2) ALU Field

This field specifies ALU operation.

(3) ASL (Acc Selection) bit

This bit selects Q input of ALU and specifies AccA or AccB.

(4) DPL Field

This field specifies operation of lower 4 bits of DP (Data Pointer). The new value of DP<sub>L</sub> specified by this field becomes valid from the next instruction.

(5) DPH•M (DPH Modify) Field

This field qualifies changes value of the upper 4 bits of DP (Data Pointer). The value of this field is qualified exclusively ORed with the value of the upper 4 bits in DP (Data Pointer). The qualified value of DP<sub>H</sub> valid from the next instruction.

(6) RPDCR (RP Decrement) bit

This bit specifies decrement operation of RP (ROM Pointer). The decremented value becomes valid from the next instruction.

(7) SRC (Source) Field

This field specifies source register to the internal data bus for transfer instruction.

(8) DST (Destination) Field

This field specifies the destination register for a transfer instruction. The data specified in SRC Field (output to the internal data bus) is written to the specified register.

# 3.2 RT Instruction

| 23 | 3  | 22 | 21        | 20  | 19 | 18 | 17 | 16 | 15          | 14 | 13 | 12 | 11 | 10   | 9 | 8     | 7 | 6  | 5  | 4 | 3 | 2  | 1  | 0 |

|----|----|----|-----------|-----|----|----|----|----|-------------|----|----|----|----|------|---|-------|---|----|----|---|---|----|----|---|

|    | 0′ |    | P-<br>SEL | ЕСТ |    | AL | _U |    | A<br>S<br>L | DI | PL |    | DF | Рн∙М |   | RPDCR |   | SF | RC |   |   | DS | бт |   |

RT instruction is a return instruction and has the following functions.

- (1) This instruction consists of six fields and two bits like the OP instruction.

- (2) It restores the return address saved to the stack to PC after performing the same operation as the OP instruction.

# 3.3 JP Instruction

| 23 22 | 2 21 | 20 | 19 | 18 | 17  | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------|----|----|----|-----|----|----|----|----|----|----|----|---|---|----|---|---|---|---|---|---|---|

| 10    |      |    |    | В  | RCH |    |    |    |    |    |    |    |   |   | NA |   |   |   |   |   |   |   |

JP instruction causes program execution of jump unconditionally or conditionally. It also calls a subroutine. (1) BRCH (Branch) Field

This field specifies type of jump instruction and conditional jump instruction.

(2) NA (Next Address) Field This field specifies jump address.

#### 3.4 LD Instruction

| 23 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1  | 0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|----|----|---|

| 11    |    |    |    |    |    |    |    |    | ID |    |    |    |   |   |   |   |   |   |   | DS | ST |   |

This is an immediate data load instruction which loads 16-bit data to the specified register.

- ID (Immediate Data) Field

This field specifies the immediate 16-bit data. The immediate data is loaded to the register specified in DST field.

- (2) DST (Destination) Field

This field specifies the register that the data specified by ID field is loaded to. This field is the same as DST field in OP instruction.

# 3.5 Instruction Code

# THE LIST OF INSTRUCTION CODE

| Bit | D D<br>23 22 | D D<br>21 20 | D D<br>19 18           | D<br>17 | D<br>16 | D<br>15     | D<br>14 | D<br>13 | D<br>12           | D<br>11 | D<br>10 | D<br>9 | D<br>8 | D<br>7 | D<br>6 | D<br>5 | D<br>4 | D<br>3 | D<br>2 | D<br>1 | D<br>0 |

|-----|--------------|--------------|------------------------|---------|---------|-------------|---------|---------|-------------------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| OP  | 0 0          | P-<br>SELECT | AL                     | JU      |         | A<br>S<br>L | DI      | PL      | DPH•M D<br>C<br>R |         |         |        |        | SRC    |        |        |        | DST    |        |        |        |

| RT  | 0 1          |              | Same as OP instruction |         |         |             |         |         |                   |         |         |        |        |        |        |        |        |        |        |        |        |

| JP  | 10           | BRCH NA      |                        |         |         |             |         |         |                   |         |         |        |        |        |        |        |        |        |        |        |        |

| LD  | 11           |              | ID                     |         |         |             |         |         |                   |         |         |        | ST     |        |        |        |        |        |        |        |        |

# ALL INSTRUCTIONS

| Instruction | OP  | field | Contents of instruction           |

|-------------|-----|-------|-----------------------------------|

|             | D23 | D22   |                                   |

| OP          | 0   | 0     | Arithmetic and Transfer Operation |

| RT          | 0   | 1     | Return Instruction                |

| JP          | 1   | 0     | Jump Instruction                  |

| LD          | 1   | 1     | Immediate Data Load Instruction   |

# **OP, RT INSTRUCTIONS**

| Mnemonic | P-SELE | CT field | Input Data        |  |  |  |  |  |  |

|----------|--------|----------|-------------------|--|--|--|--|--|--|

|          | D21    | D20      |                   |  |  |  |  |  |  |

| RAM      | 0      | 0        | RAM               |  |  |  |  |  |  |

| IDB      | 0      | 1        | Internal Data Bus |  |  |  |  |  |  |

| М        | 1      | 0        | M register        |  |  |  |  |  |  |

| N        | 1      | 1        | N register        |  |  |  |  |  |  |

# **OP, RT INSTRUCTIONS**

| Mnemonic |     | ALU | field |     | Fund                            | ction                                    |

|----------|-----|-----|-------|-----|---------------------------------|------------------------------------------|

|          | D19 | D18 | D17   | D16 |                                 |                                          |

| NOP      | 0   | 0   | 0     | 0   | No Operation                    |                                          |

| OR       | 0   | 0   | 0     | 1   | OR                              | $(Acc) \gets (Acc) \lor (P)$             |

| AND      | 0   | 0   | 1     | 0   | AND                             | $(Acc) \gets (Acc) \land (P)$            |

| XOR      | 0   | 0   | 1     | 1   | Exclusive OR                    | $(Acc) \gets (Acc) \nleftrightarrow (P)$ |

| SUB      | 0   | 1   | 0     | 0   | Subtract                        | $(Acc) \gets (Acc) - (P)$                |

| ADD      | 0   | 1   | 0     | 1   | Add                             | $(Acc) \gets (Acc) + (P)$                |

| SBB      | 0   | 1   | 1     | 0   | Subtract with Borrow            | $(Acc) \gets (Acc) - (P) - (C)$          |

| ADC      | 0   | 1   | 1     | 1   | Add with Carry                  | $(Acc) \gets (Acc) + (P) + (C)$          |

| DEC      | 1   | 0   | 0     | 0   | Decrement Acc                   | $(Acc) \leftarrow (Acc) - 1$             |

| INC      | 1   | 0   | 0     | 1   | Increment Acc                   | $(Acc) \leftarrow (Acc) + 1$             |

| CMP      | 1   | 0   | 1     | 0   | Complement Acc (1's complement) | $(Acc) \leftarrow (\overline{Acc})$      |

| SHR1     | 1   | 0   | 1     | 1   | 1-bit R-Shift                   |                                          |

| SHL1     | 1   | 1   | 0     | 0   | 1-bit L-Shift                   |                                          |

| SHL2     | 1   | 1   | 0     | 1   | 2-bit L-Shift                   |                                          |

| SHL4     | 1   | 1   | 1     | 0   | 4-bit L-Shift                   |                                          |

| XCHG     | 1   | 1   | 1     | 1   | 8-bit Exchange                  |                                          |

# **OP, RT INSTRUCTIONS**

| Mnemonic | ASL bit | Selection for Acc and FLAG |

|----------|---------|----------------------------|

|          | D15     |                            |

| ACCA     | 0       | Acc A                      |

| ACCB     | 1       | Acc B                      |

# **OP, RT INSTRUCTIONS**

| Mnemonic | DP∟ | field | Operation     |

|----------|-----|-------|---------------|

|          | D14 | D13   |               |

| DPNOP    | 0   | 0     | No Operation  |

| DPINC    | 0   | 1     | Increment DPL |

| DPDEC    | 1   | 0     | Decrement DP∟ |

| DPCLR    | 1   | 1     | Clear DPL     |

# **OP, RT INSTRUCTIONS**

| Mnemonic | [   | ОРн <b>∙</b> № | /l fielo | d  | Exclusive OR                                                                   |

|----------|-----|----------------|----------|----|--------------------------------------------------------------------------------|

|          | D12 | D11            | D10      | D9 |                                                                                |

| MO       | 0   | 0              | 0        | 0  | (DP <sub>7</sub> DP <sub>6</sub> DP <sub>5</sub> DP <sub>4</sub> ) ₩ (0 0 0 0) |

| M1       | 0   | 0              | 0        | 1  | (DP <sub>7</sub> DP <sub>6</sub> DP <sub>5</sub> DP <sub>4</sub> ) ₩ (0 0 0 1) |

| M2       | 0   | 0              | 1        | 0  | (DP7 DP6 DP5 DP4) ₩ (0 0 1 0)                                                  |

| M3       | 0   | 0              | 1        | 1  | (DP <sub>7</sub> DP <sub>6</sub> DP <sub>5</sub> DP <sub>4</sub> ) ₩ (0 0 1 1) |

| M4       | 0   | 1              | 0        | 0  | (DP <sub>7</sub> DP <sub>6</sub> DP <sub>5</sub> DP <sub>4</sub> ) ₩ (0 1 0 0) |

| M5       | 0   | 1              | 0        | 1  | (DP7 DP6 DP5 DP4) ₩ (0 1 0 1)                                                  |

| M6       | 0   | 1              | 1        | 0  | (DP <sub>7</sub> DP <sub>6</sub> DP <sub>5</sub> DP <sub>4</sub> ) ₩ (0 1 1 0) |

| M7       | 0   | 1              | 1        | 1  | (DP7 DP6 DP5 DP4) ₩ (0 1 1 1)                                                  |

| M8       | 1   | 0              | 0        | 0  | (DP7 DP6 DP5 DP4) ∀ (1 0 0 0)                                                  |

| M9       | 1   | 0              | 0        | 1  | (DP <sub>7</sub> DP <sub>6</sub> DP <sub>5</sub> DP <sub>4</sub> ) ₩ (1 0 0 1) |

| MA       | 1   | 0              | 1        | 0  | (DP7 DP6 DP5 DP4) ₩ (1 0 1 0)                                                  |

| MB       | 1   | 0              | 1        | 1  | (DP7 DP6 DP5 DP4) ∀ (1 0 1 1)                                                  |

| MC       | 1   | 1              | 0        | 0  | (DP <sub>7</sub> DP <sub>6</sub> DP <sub>5</sub> DP <sub>4</sub> ) ₩ (1 1 0 0) |

| MD       | 1   | 1              | 0        | 1  | (DP7 DP6 DP5 DP4) ₩ (1 1 0 1)                                                  |

| ME       | 1   | 1              | 1        | 0  | (DP7 DP6 DP5 DP4) ₩ (1 1 1 0)                                                  |

| MF       | 1   | 1              | 1        | 1  | (DP7 DP6 DP5 DP4) ₩ (1 1 1 1)                                                  |

# **OP, RT INSTRUCTIONS**

| Mnemonic | RPDCR bit | Operation    |

|----------|-----------|--------------|

|          | D8        |              |

| RPNOP    | 0         | No Operation |

| RPDEC    | 1         | Decrement RP |

# **OP, RT INSTRUCTIONS**

| Mnemonic                    |    | SRC            | field |    | Specified register                                    |

|-----------------------------|----|----------------|-------|----|-------------------------------------------------------|

|                             | D7 | D <sub>6</sub> | D5    | D4 |                                                       |

| NON <sup>Note 1</sup> , TRB | 0  | 0              | 0     | 0  | TRB register                                          |

| A                           | 0  | 0              | 0     | 1  | Acc A register                                        |

| В                           | 0  | 0              | 1     | 0  | Acc B register                                        |

| TR                          | 0  | 0              | 1     | 1  | TR register                                           |

| DP                          | 0  | 1              | 0     | 0  | DP register                                           |

| RP                          | 0  | 1              | 0     | 1  | RP register                                           |

| RO                          | 0  | 1              | 1     | 0  | RO register                                           |

| SGN                         | 0  | 1              | 1     | 1  | SGN register                                          |

| DR                          | 1  | 0              | 0     | 0  | DR register                                           |

| DRNF                        | 1  | 0              | 0     | 1  | DR register <sup>Note 2</sup>                         |

| SR                          | 1  | 0              | 1     | 0  | SR register                                           |

| SIM                         | 1  | 0              | 1     | 1  | SI register $(1st \rightarrow MSB)^{Note 3}$          |

| SIL                         | 1  | 1              | 0     | 0  | SI register (1st $\rightarrow$ LSB) <sup>Note 4</sup> |

| К                           | 1  | 1              | 0     | 1  | K register                                            |

| L                           | 1  | 1              | 1     | 0  | L register                                            |

| MEM                         | 1  | 1              | 1     | 1  | RAM                                                   |

**Notes** 1. The contents of the TRB register are also output if NON is specified.

- 2. Although the contents of the DR register are output to the internal data bus, the RQM flag is not set. Neither is the DRQ flag in DMA mode.

- **3.** With the 16-bit data, the serial data input first is output to the MSB of the internal data bus; the data input last is output to the LSB.

- **4.** With the 16-bit data, the serial data input first is output to the LSB of the internal data bus; the data input last is output to the MSB.

# **OP, RT, LD INSTRUCTIONS**

| Mnemonic |    | DST | field |    | Specified register                                    |  |

|----------|----|-----|-------|----|-------------------------------------------------------|--|

|          | D3 | D2  | D1    | Do |                                                       |  |

| @NON     | 0  | 0   | 0     | 0  | No specified register                                 |  |

| @A       | 0  | 0   | 0     | 1  | Acc A register                                        |  |

| @B       | 0  | 0   | 1     | 0  | Acc B register                                        |  |

| @TR      | 0  | 0   | 1     | 1  | TR register                                           |  |

| @DP      | 0  | 1   | 0     | 0  | DP register                                           |  |

| @RP      | 0  | 1   | 0     | 1  | RP register                                           |  |

| @DR      | 0  | 1   | 1     | 0  | DR register                                           |  |

| @SR      | 0  | 1   | 1     | 1  | SR register                                           |  |

| @SOL     | 1  | 0   | 0     | 0  | SO register (LSB $\rightarrow$ 1st) <sup>Note 1</sup> |  |

| @SOM     | 1  | 0   | 0     | 1  | SO register (MSB $\rightarrow$ 1st) <sup>Note 2</sup> |  |

| @K       | 1  | 0   | 1     | 0  | K register                                            |  |

| @KLR     | 1  | 0   | 1     | 1  | KLR <sup>Note 3</sup>                                 |  |

| @KLM     | 1  | 1   | 0     | 0  | KLM <sup>Note 4</sup>                                 |  |

| @L       | 1  | 1   | 0     | 1  | L register                                            |  |

| @TRB     | 1  | 1   | 1     | 0  | TRB register                                          |  |

| @MEM     | 1  | 1   | 1     | 1  | RAM                                                   |  |

**Notes 1.** With 16-bit data, the serial output is sequentially performed from the LSB bit of the internal data bus.

2. With 16-bit data, the serial output is sequentially performed from the MSB of the internal data bus.

- 3. The data on the internal bus and the output from the RO register (ROM) are set to the K and L registers, respectively.

- 4. The data on the internal bus and the contents of RAM (DP7, "1", DP5, DP4, DP3, DP2, DP1, and DP0) specified by DP6 = ("1") are set to the L and K registers, respectively.

**Remark** Following combination are prohibited in OP or RT instruction

DST field = @KLR, SRC field = K or L register DST field = @KLM, SRC field = K or L register DST field and SRC field specify the same register P-SELECT field = RAM, DST field = @MEM (for ALU operation)

# JP INSTRUCTION

| Mnemonic |     |     |     | BR  | CH f | ield |     |     |     | Condition          |

|----------|-----|-----|-----|-----|------|------|-----|-----|-----|--------------------|

|          | D21 | D20 | D19 | D18 | D17  | D16  | D15 | D14 | D13 |                    |

| JMP      | 1   | 0   | 0   | 0   | 0    | 0    | 0   | 0   | 0   | Unconditional jump |

| CALL     | 1   | 0   | 1   | 0   | 0    | 0    | 0   | 0   | 0   | Unconditional jump |

| JNCA     | 0   | 1   | 0   | 0   | 0    | 0    | 0   | 0   | 0   | CA = 0             |

| JCA      | 0   | 1   | 0   | 0   | 0    | 0    | 0   | 1   | 0   | CA = 1             |

| JNCB     | 0   | 1   | 0   | 0   | 0    | 0    | 1   | 0   | 0   | CB = 0             |

| JCB      | 0   | 1   | 0   | 0   | 0    | 0    | 1   | 1   | 0   | CB = 1             |

| JNZA     | 0   | 1   | 0   | 0   | 0    | 1    | 0   | 0   | 0   | ZA = 0             |

| JZA      | 0   | 1   | 0   | 0   | 0    | 1    | 0   | 1   | 0   | ZA = 1             |

| JNZB     | 0   | 1   | 0   | 0   | 0    | 1    | 1   | 0   | 0   | ZB = 0             |

| JZB      | 0   | 1   | 0   | 0   | 0    | 1    | 1   | 1   | 0   | ZB = 1             |

| JNOVA0   | 0   | 1   | 0   | 0   | 1    | 0    | 0   | 0   | 0   | OVA0 = 0           |

| JOVA0    | 0   | 1   | 0   | 0   | 1    | 0    | 0   | 1   | 0   | OVA0 = 1           |

| JNOVB0   | 0   | 1   | 0   | 0   | 1    | 0    | 1   | 0   | 0   | OVB0 = 0           |

| JOVB0    | 0   | 1   | 0   | 0   | 1    | 0    | 1   | 1   | 0   | OVB0 = 1           |

| JNOVA1   | 0   | 1   | 0   | 0   | 1    | 1    | 0   | 0   | 0   | OVA1 = 0           |

| JOVA1    | 0   | 1   | 0   | 0   | 1    | 1    | 0   | 1   | 0   | OVA1 = 1           |

| JNOVB1   | 0   | 1   | 0   | 0   | 1    | 1    | 1   | 0   | 0   | OVB1 = 0           |

| JOVB1    | 0   | 1   | 0   | 0   | 1    | 1    | 1   | 1   | 0   | OVB1 = 1           |

| JNSA0    | 0   | 1   | 0   | 1   | 0    | 0    | 0   | 0   | 0   | SA0 = 0            |

| JSA0     | 0   | 1   | 0   | 1   | 0    | 0    | 0   | 1   | 0   | SA0 = 1            |

| JNSB0    | 0   | 1   | 0   | 1   | 0    | 0    | 1   | 0   | 0   | SB0 = 0            |

| JSB0     | 0   | 1   | 0   | 1   | 0    | 0    | 1   | 1   | 0   | SB0 = 1            |

| JNSA1    | 0   | 1   | 0   | 1   | 0    | 1    | 0   | 0   | 0   | SA1 = 0            |

| JSA1     | 0   | 1   | 0   | 1   | 0    | 1    | 0   | 1   | 0   | SA1 = 1            |

| JNSB1    | 0   | 1   | 0   | 1   | 0    | 1    | 1   | 0   | 0   | SB1 = 0            |

| JSB1     | 0   | 1   | 0   | 1   | 0    | 1    | 1   | 1   | 0   | SB1 = 1            |

| JDPL0    | 0   | 1   | 0   | 1   | 1    | 0    | 0   | 0   | 0   | DPL = 0            |

| JDPLN0   | 0   | 1   | 0   | 1   | 1    | 0    | 0   | 0   | 1   | DPL ≠ 0            |

| JDPLF    | 0   | 1   | 0   | 1   | 1    | 0    | 0   | 1   | 0   | DP∟ = F (HEX)      |

| JDPLNF   | 0   | 1   | 0   | 1   | 1    | 0    | 0   | 1   | 1   | DP∟ ≠ F (HEX)      |

| JNSIAK   | 0   | 1   | 0   | 1   | 1    | 0    | 1   | 0   | 0   | SI ACK = 0         |

| JSIAK    | 0   | 1   | 0   | 1   | 1    | 0    | 1   | 1   | 0   | SI ACK = 1         |

| JNSOAK   | 0   | 1   | 0   | 1   | 1    | 1    | 0   | 0   | 0   | SO ACK = 0         |

| JSOAK    | 0   | 1   | 0   | 1   | 1    | 1    | 0   | 1   | 0   | SO ACK = 1         |

| JNRQM    | 0   | 1   | 0   | 1   | 1    | 1    | 1   | 0   | 0   | RQM = 0            |

| JRQM     | 0   | 1   | 0   | 1   | 1    | 1    | 1   | 1   | 0   | RQM = 1            |

# JP INSTRUCTION

|     |     |             |    | 1  | NA field | b              |    |    |    |    | Jump address                         |

|-----|-----|-------------|----|----|----------|----------------|----|----|----|----|--------------------------------------|

| D12 | D11 | <b>D</b> 10 | D9 | D8 | D7       | D <sub>6</sub> | D5 | D4 | Dз | D2 |                                      |

| 0   | 0   | 0           | 0  | 0  | 0        | 0              | 0  | 0  | 0  | 0  | Specify address 0 as jump address    |

| 0   | 0   | 0           | 0  | 0  | 0        | 0              | 0  | 0  | 0  | 1  | Specify address 1 as jump address    |

| 0   | 0   | 0           | 0  | 0  | 0        | 0              | 0  | 0  | 1  | 0  | Specify address 2 as jump address    |

|     |     |             |    |    | to       |                |    |    |    |    | to                                   |

| 1   | 1   | 1           | 1  | 1  | 1        | 1              | 1  | 1  | 1  | 1  | Specify address 2047 as jump address |

# LD INSTRUCTION

|     | ID field |     |     |     |     |     |     |     |     |     |     |    | HEX |    |                |         |

|-----|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|-----|----|----------------|---------|

| D21 | D20      | D19 | D18 | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D۹ | D8  | D7 | D <sub>6</sub> |         |

| 0   | 0        | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0   | 0  | 0              | 0 0 0 0 |

| 0   | 0        | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0   | 0  | 1              | 0 0 0 1 |

| 0   | 0        | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0   | 1  | 0              | 0 0 0 2 |

|     |          |     |     |     |     |     | t   | 0   |     |     |     |    |     |    |                | to      |

| 1   | 1        | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1   | 1  | 1              | FFFF    |

|      |                |               | Selecte        | d FLAG         |                |                |    | Nonselec | ted FLAG     | i |     |     |

|------|----------------|---------------|----------------|----------------|----------------|----------------|----|----------|--------------|---|-----|-----|

|      | S1             | S0            | С              | Z              | OV1            | OV0            | S1 | S0       | С            | Z | OV1 | OV0 |

| NOP  | •              | •             | •              | •              |                |                |    | •        | •            |   |     |     |

| OR   | Х              | \$            | 0              | \$             | 0              | 0              | •  | •        | •            |   |     | •   |

| AND  | Х              | \$            | 0              | $\updownarrow$ | 0              | 0              |    |          | •            |   |     |     |

| XOR  | Х              | €             | 0              | $\updownarrow$ | 0              | 0              |    |          | •            |   |     |     |

| SUB  | $\updownarrow$ | \$            | \$             | $\uparrow$     | \$             | \$             | •  | •        | •            |   |     | •   |

| ADD  | $\Rightarrow$  | \$            | \$             | \$             | \$             | \$             | •  |          | •            | • |     | •   |

| SBB  | $\Rightarrow$  | \$            | \$             | $\uparrow$     | $\uparrow$     | $\uparrow$     | •  | •        | <i>←</i>     | • | •   | •   |

| ADC  | $\updownarrow$ | \$            | \$             | \$             | \$             | \$             |    | •        | $\leftarrow$ |   |     |     |

| DEC  | $\updownarrow$ | \$            | \$             | $\updownarrow$ | $\uparrow$     | $\uparrow$     |    |          | •            |   |     |     |

| INC  | $\Rightarrow$  | $\Rightarrow$ | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ |    |          | •            |   |     |     |

| CMP  | Х              | \$            | 0              | $\uparrow$     | 0              | 0              | •  | •        | •            |   |     | •   |

| SHR1 | Х              | \$            | \$             | $\updownarrow$ | 0              | 0              |    |          | •            |   |     |     |

| SHL1 | Х              | $\Rightarrow$ | $\updownarrow$ | $\updownarrow$ | 0              | 0              |    |          | $\leftarrow$ |   |     |     |

| SHL2 | Х              | \$            | 0              | $\uparrow$     | 0              | 0              | •  | •        | •            |   | •   | •   |

| SHL4 | Х              | \$            | 0              | \$             | 0              | 0              | •  | •        | •            |   |     | •   |

| XCHG | Х              | $\uparrow$    | 0              | $\updownarrow$ | 0              | 0              | •  | •        | •            | • |     | •   |

# EFFECT OF ALU OPERATION ON FLAGS

$\leftarrow$  : Affects the result of operation

$\updownarrow$  : Affected by the result of operation

0 : Cleared to 0

1 : Set to 1

• : Retains the previous state

X : Undefined

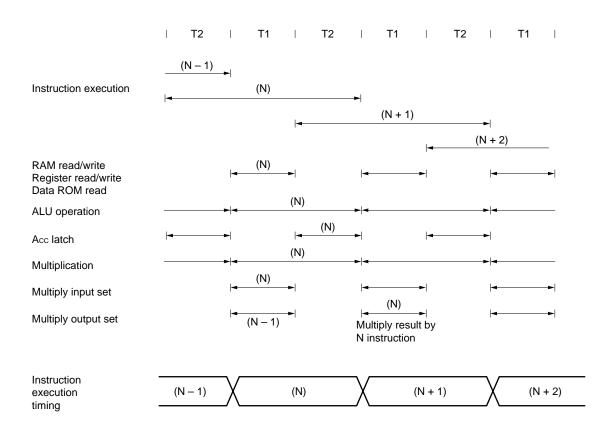

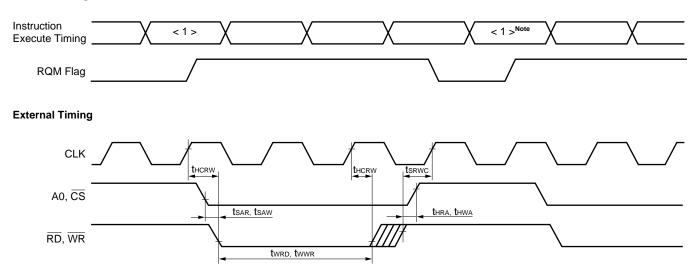

# 4. INSTRUCTION EXECUTION TIMING

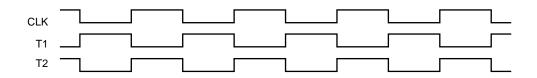

The  $\mu$ PD77C25 operates according to the external square wave applied to the CLK pin. This square wave is internally divided into two to generate two phases of clocks as shown for internal operation.

#### **Internal Clock Timing**

The instruction is executed as follows.

- (1) An instruction is executed with two T2's.

- (2) Data is read from and written to RAM and registers and is read from the data ROM at T1.

- (3) ALU performs an operation in T1 and T2 and the output result is latched to an Acc in one T2.

- (4) The input data to the multiplier is set in one at T1. At the same time, a multiplication is performed and its result is output at the next T1.

The instruction execution timing in the timing chart indicates the cycle of T1 or T2.

#### Instruction Execution Timing

# 5. µPD77P25 PROM INTERFACE

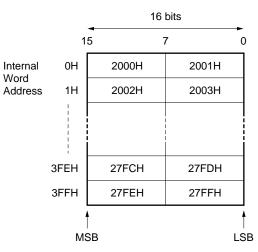

(1) Input/Output Data Format

One word of the instruction ROM consists of 24 bits, while 16 bits make up one data ROM word. Data are programed to or read from these PROMs in units of 8 bits (byte). Therefore, special address are assigned to the PROMs. Address 0H through 1FFFH are assigned to the 2K-word instruction ROM. The following address, 2000H through 27FFH are assigned to the 1K-word data ROM.

Since the instruction ROM is configured on a 1-word-for-24-bit basis, one dummy byte address is provided per word. This dummy byte address is used for the instruction ROM code protection.

For example, data in word address 0H of the instruction ROM is equivalent to three bytes of byte address 0H to 2H. 3H is a dummy byte address.

#### Memory Map of $\mu$ PD77P25 On-Chip PROM

- 24 bits dummy byte 23 15 7 0 Internal 0H 0H 1H 2H ЗH Word 1H 4H 6H 7H Address 5H 7FEH 1FF8H 1FF9H 1FFAH 1FFBH 7FFH 1FFCH 1FFEH 1FFDH 1FFFH MSB

- (a) Instruction ROM (1 word = 24 bits)

Remark Numeric values within the boxes are byte addresses of the instruction ROM.

(b) Data ROM (1 word = 16 bits)

**Remark** Numeric values within the boxes are byte addresses of the data ROM.

(2) Erasing Data

The data in the  $\mu$ PD77P25D's UVEPROMs can be erased by exposing them to a light with a wavelength shorter than 400 nm. All data in the UVEPROMs are set to "1s" after the erasure.

Note that, if the  $\mu$ PD77P25D is exposed to the direct sunlight or fluorescent light for a long time, the data might be erased. To prevent this, the UVEPROM window must be masked with a cover or film for shielding from the ultraviolet light.

Usually, the UVEPROMs are erased exposed to the ultraviolet light with a wavelength of 254 nm. The total light quantity required to completely erase the written data is 15 Ws/cm<sup>2</sup> (UV intensity x erase time) that is equivalent to exposure to a UV lamp with a wavelength of 12000  $\mu$ W/cm<sup>2</sup> for about 15 to 20 minutes. However, a longer erasing time may be required due to such factors as the life of the UV lamp and stains on the window of the package.

The  $\mu$ PD77P25D must be positioned within one inch away from the UV lamp.

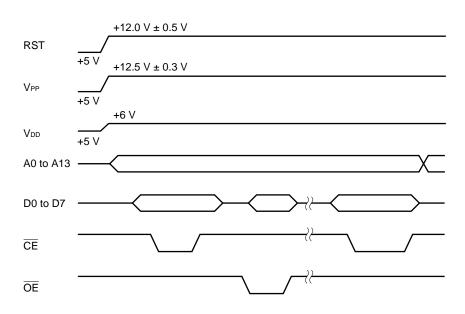

- (3) Procedure to Program Data

- To Program data, perform the programming operation observing the following procedure.

- <1> Apply +12.5 V to RST (pin 16), +6 V to VDD, and +12.5 V to VPP. This causes the PROMs to enter program mode.

- <2> Specify the desired ROM byte address from address input pins A0 to A13.

- <3> Program the data on the data bus (D0 to D7) by applying "0" to  $\overline{CE}$  while  $\overline{OE}$  is "1". (program mode).

- <4> Output the programed data to the data bus (D0 to D7) by applying "0" to OE while CE is "1" (program verify mode).

- <5> Repeat steps <2> through <4> 25 times maximum until the data is properly programed to the specified address.

- <6> After verifying that the data has been properly programed, apply additional pulses by setting OE to "1" (clear CE to "0". The pulse width of it is 3Xms if the number of repetitions in <3> and <4> is X).

The above procedure completes writing one byte of data.

In case the data will not be properly programed even after steps <2> to <4> have been repeated more than 25 times, it means that the  $\mu$ PD77P25 is defective.

Since the area from byte address 2800H to 3FFFH is for internal testing, the area to program data must be set from byte address 0H to 27FFH. Please set the data FFH to program data to the dummy byte address in the normal programming.

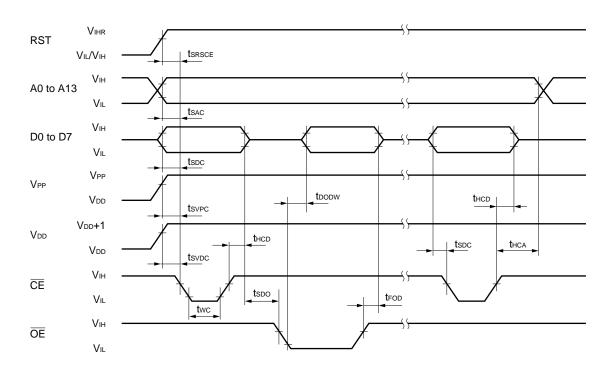

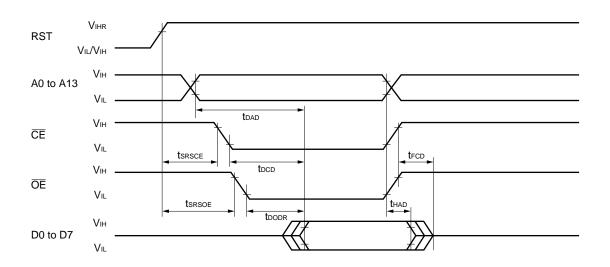

# **On-Chip PROM Program Timing**

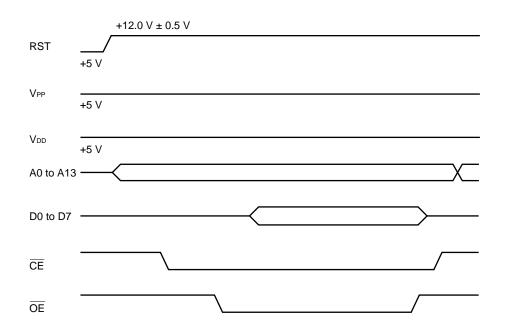

- (4) Procedure to Read Data

- <1> Apply +12.5 V to RST (pin 16), +6 V to VDD, and +12.5 V to VPP. This causes the PROMs to enter read mode.

- <2> Specify the desired ROM byte address from the address input pins A0 to A13.

- <3> Data will be output to the data bus (D0 to D7) by clearing  $\overline{OE}$  and  $\overline{CE}$  to "0".

#### **On-Chip PROM Read Timing**

(5) Instruction ROM code protection

A word of the instruction ROM can be protected if the data FEH is programmed to a dummy byte address. For example, the three bytes of addresses 0H through 2H (word address 0H) is protected if the data FEH is programmed to the dummy byte of address 3H. To protect the instruction ROM, perform the protecting operation observing the following procedure.

- <1> Set the data FFH to the dummy addresses, then program the data as the procedure described (3).

- <2> Verify the programmed data as the procedure described (4).

- <3> Set the data FEH to the dummy addresses, then program the data as the procedure described (3).

# 6. ELECTRICAL SPECIFICATIONS

# **ABSOLUTE MAXIMUM RATINGS** (TA = 25 °C)

| Parameters                    | Symbol | Product names | Conditions       | Ratings          | Unit |

|-------------------------------|--------|---------------|------------------|------------------|------|

| Power Supply Voltage          | Vdd    | μPD77C25      |                  | -0.5 to +7.0     | V    |

|                               |        | μPD77P25      |                  |                  |      |

|                               | Vpp    | μPD77P25      |                  | -0.5 to +13.5    |      |

| Input Voltage                 | Vi     | μPD77C25      |                  | -0.5 to VDD +0.5 | V    |

|                               |        | μPD77P25      |                  |                  |      |

|                               | Vrst   | μPD77P25      | RST Pin          | -0.5 to +13.0    |      |

| Output Voltage                | Vo     | μPD77C25      |                  | -0.5 to VDD +0.5 | V    |

|                               |        | μPD77P25      |                  |                  |      |

| Operating Ambient Temperature | TA     | μPD77C25      |                  | -40 to +80       | °C   |

|                               |        | μPD77P25      | Normal operation | -10 to +70       |      |

|                               |        |               | PROM mode        | +20 to +30       |      |

| Storage Temperature           | Tstg   | μPD77C25      |                  | -65 to +150      | °C   |

|                               |        | μPD77P25      |                  |                  |      |

Caution Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The parameters apply independently. The device should be operated within the limits specified under DC and AC Characteristics.

| Parameters                          | Symbol | Product names | Conditions                   | MIN. | TYP. | MAX.     | Unit |

|-------------------------------------|--------|---------------|------------------------------|------|------|----------|------|

| Power Supply Voltage                | Vdd    | μPD77C25      | Normal operation             | 4.5  | 5.0  | 5.5      | V    |

|                                     |        | μPD77P25      |                              |      |      |          |      |

|                                     |        | μPD77P25      | Programming                  | 5.75 | 6.0  | 6.25     |      |

|                                     | Vpp    | μPD77P25      | Reading and normal operation | 4.5  | 5.0  | 5.5      |      |

|                                     |        |               | Programming                  | 12.2 | 12.5 | 12.8     |      |

| Low Level Input Voltage             | VIL    | μPD77C25      |                              | -0.3 |      | +0.8     | V    |

|                                     |        | μPD77P25      |                              |      |      |          |      |

| High Level Input Voltage            | Vін    | μPD77C25      |                              | 2.2  |      | Vdd +0.3 | V    |

|                                     |        | μPD77P25      |                              |      |      |          |      |

| Low Level Clock Input Voltage       | VILC   | μPD77C25      |                              | -0.3 |      | +0.5     | V    |

|                                     |        | μPD77P25      |                              |      |      |          |      |

| High Level Clock Input Voltage      | VIHC   | μPD77C25      |                              | 3.5  |      | Vdd +0.3 | V    |

|                                     |        | μPD77P25      |                              |      |      |          |      |

| Input Voltage for Setting PROM mode | Vrst   | μPD77P25      | Reading and writing          | 11.5 | 12.0 | 12.5     | V    |

| Operating Ambient Temperature       | TA     | μPD77C25      |                              | -40  | +25  | +85      | °C   |

|                                     |        | μPD77P25      | Normal operation             | -10  | ]    | +70      |      |

|                                     |        |               | PROM mode                    | +20  |      | +30      |      |

# **DC CHARACTERISTICS [NORMAL OPERATION]** ( $\mu$ PD77C25: T<sub>A</sub> = -40 to +85 °C,

$\mu$ PD77P25: T<sub>A</sub> = -10 to +70 °C, V<sub>DD</sub> = 4.5 V to 5.5 V)

| Parameters                     | Symbol | Conditions                  | MIN.    | TYP. | MAX. | Unit |

|--------------------------------|--------|-----------------------------|---------|------|------|------|

| Low-level Output Voltage       | Vol    | IoL = 2.0 mA                |         |      | 0.45 | V    |

| High-level Output Voltage      | Vон    | Іон = -400 μА               | 0.7 Vdd |      |      | V    |

| Low-level Input Leak Current   | LIL    | $V_{IN} = 0 V$              |         |      | -10  | μA   |

| High-level Input Leak Current  | Іцн    | Vin = Vdd                   |         |      | 10   | μA   |

| Low-level Output Leak Current  | ILOL   | Vout = 0.47 V               |         |      | -10  | μA   |

| High-level Output Leak Current | Ігон   | Vout = Vdd                  |         |      | 10   | μA   |

| Supply Current (µPD77C25)      | loo    | fclк = 8.192 MHz            |         | 25   | 50   | mA   |

|                                |        | fclк = 8.192 MHz, RST = "1" |         | 15   | 25   | mA   |

| Supply Current (µPD77P25)      | loo    | fclк = 8.192 MHz            |         | 35   | 60   | mA   |

|                                |        | fclк = 8.192 MHz, RST = "1" |         | 20   | 35   | mA   |

|                                | Ірр    |                             |         |      | 1    | mA   |

# DC CHARACTERISTICS [PROM MODE] (T<sub>A</sub> = +20 to +30 °C, V<sub>DD</sub> = 5.75 V to 6.25 V)

| Parameters         | Symbol      | Conditions                                | MIN. | TYP. | MAX. | Unit |

|--------------------|-------------|-------------------------------------------|------|------|------|------|

| Input Leak Current | IRST        | $V_{\text{RST}} = 12.0 \pm 0.5 \text{ V}$ |      |      | 30   | μΑ   |

| Supply Current     | ldd         |                                           |      |      | 60   | mA   |

|                    | <b>I</b> PP |                                           |      |      | 30   | mA   |

# **CAPACITANCE** (TA = 25 °C, VDD = 0 V)

| Parameters                 | Symbol         | Conditions | MIN. | TYP. | MAX. | Unit |

|----------------------------|----------------|------------|------|------|------|------|

| CLK, SCK Input Capacitance | C <sub>0</sub> | fc = 1 MHz |      |      | 20   | pF   |

| Input Capacitance          | CIN            |            |      |      | 20   | pF   |

| Output Capacitance         | Соит           |            |      |      | 20   | pF   |

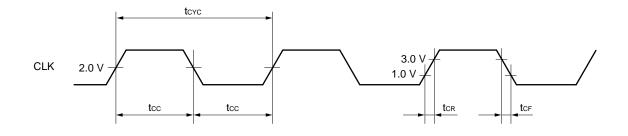

# **CLOCK TIMING REQUIREMENTS**

# **Clock Timing** ( $\mu$ PD77C25: T<sub>A</sub> = -40 to +85 °C, $\mu$ PD77P25: T<sub>A</sub> = -10 to +70 °C, V<sub>DD</sub> = 5 V ±10 %)

| Parameters           | Symbol | Product names | Conditions              | MIN. | TYP. | MAX. | Unit |

|----------------------|--------|---------------|-------------------------|------|------|------|------|

| CLK Cycle Time       | tcyc   | μPD77C25      | Measuring at 2.0 V      | 120  | 122  | 2000 | ns   |

|                      |        | μPD77P25      |                         |      |      |      |      |

| CLK Pulse Width      | tcc    | μPD77C25      | Measuring at 2.0 V      | 55   |      |      | ns   |

|                      |        | μPD77P25      |                         | 60   |      |      |      |

| CLK Rise Time        | tcr    | μPD77C25      | Measuring at 1.0, 3.0 V |      |      | 10   | ns   |

|                      |        | μPD77P25      |                         |      |      |      |      |

| CLK Fall Time        | tcF    | μPD77C25      | Measuring at 1.0, 3.0 V |      |      | 10   | ns   |

|                      |        | μPD77P25      |                         |      |      |      |      |

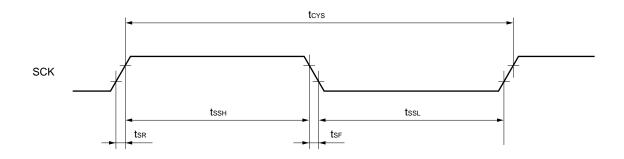

| SCK Cycle Time       | tcys   | μPD77C25      |                         | 240  | 244  |      | ns   |

|                      |        | μPD77P25      |                         |      |      |      |      |

| SCK High Pulse Width | tssн   | μPD77C25      |                         | 100  |      |      | ns   |

|                      |        | μPD77P25      |                         |      |      |      |      |

| SCK Low Pulse Width  | tss∟   | μPD77C25      |                         | 100  |      |      | ns   |

|                      |        | μPD77P25      |                         |      |      |      |      |

| SCK Rise Time        | tsr    | μPD77C25      |                         |      |      | 20   | ns   |

|                      |        | μPD77P25      |                         |      |      |      |      |

| SCK Fall Time        | tsr    | μPD77C25      |                         |      |      | 20   | ns   |

|                      |        | μPD77P25      |                         |      |      |      |      |

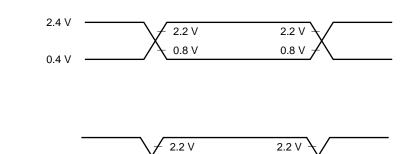

# **VOLTAGE REFERENCE LEVELS**

Input

Output

0.8 V

0.8 V

TIMING CHART

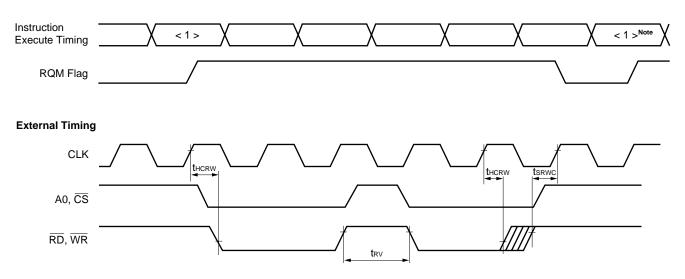

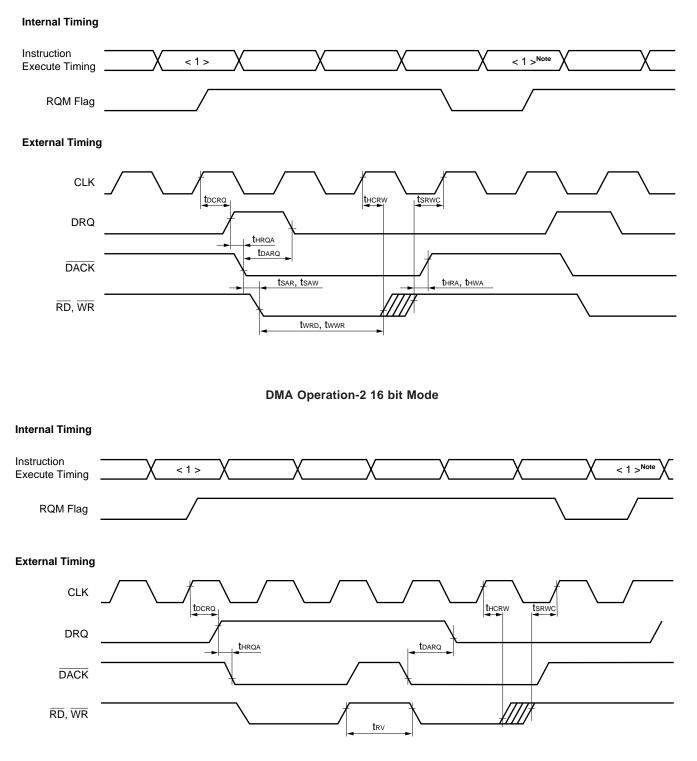

# HOST INTERFACE TIMING

| $\frac{1}{1000} \text{ ($\mu PD77C23. TA = -40 (0 +85 C, $\mu PD77F23. TA = -10 (0 +70 C, $v DD = 5 V \pm 10 %)}{10000}$ |               |            |         |      |      |      |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------|---------------|------------|---------|------|------|------|--|--|--|--|--|--|

| Parameters                                                                                                               | Symbol        | Conditions | MIN.    | TYP. | MAX. | Unit |  |  |  |  |  |  |

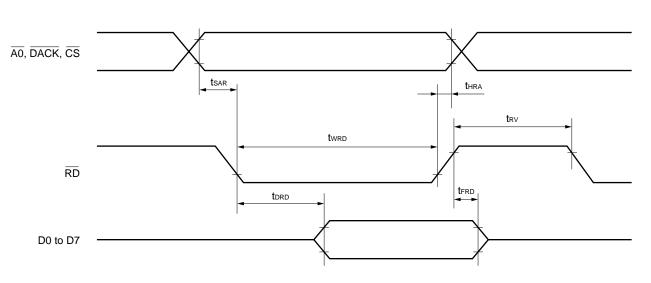

| A0, $\overline{CS}$ , $\overline{DACK}$ Setup Time for $\overline{RD}$                                                   | <b>t</b> sar  |            | 0       |      |      | ns   |  |  |  |  |  |  |

| A0, $\overline{CS}$ , $\overline{DACK}$ Hold Time for $\overline{RD}$                                                    | <b>t</b> hra  |            | 0       |      |      | ns   |  |  |  |  |  |  |

| RD Pulse Width                                                                                                           | twrd          |            | 120     |      |      | ns   |  |  |  |  |  |  |

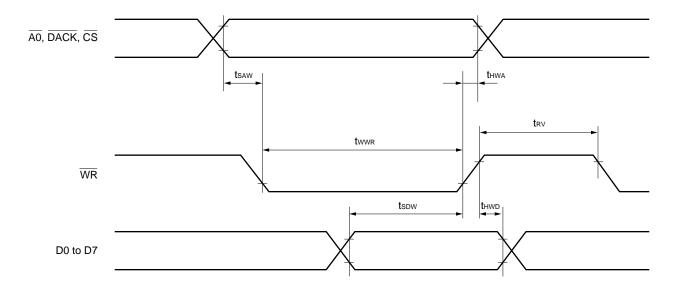

| A0, $\overline{\text{CS}}$ , $\overline{\text{DACK}}$ Setup Time for $\overline{\text{WR}}$                              | tsaw          |            | 0       |      |      | ns   |  |  |  |  |  |  |

| A0, $\overline{\text{CS}}$ , $\overline{\text{DACK}}$ Hold Time for $\overline{\text{WR}}$                               | thwa          |            | 0       |      |      | ns   |  |  |  |  |  |  |

| WR Pulse Width                                                                                                           | twwr          |            | 120     |      |      | ns   |  |  |  |  |  |  |

| Data Setup Time for WR                                                                                                   | tsdw          |            | 100     |      |      | ns   |  |  |  |  |  |  |

| Data Hold Time for WR                                                                                                    | thwd          |            | 0       |      |      | ns   |  |  |  |  |  |  |

| RD, WR Recovery Time                                                                                                     | trv           |            | 100     |      |      | ns   |  |  |  |  |  |  |