## MOS INTEGRATED CIRCUIT

# $\mu$ PD17P005

# 4-BIT SINGLE-CHIP MICROCONTROLLER WITH ONE-TIME PROM AND HARDWARE FOR DIGITAL TUNING SYSTEM

#### **DESCRIPTION**

$\mu$ PD17P005 is a model of  $\mu$ PD17005 equipped with one-time PROM instead of a mask ROM.

Since the user program can be written to the PROM of the  $\mu$ PD17P005, this 4-bit microcontroller is ideal for experimental or small-scale production of application systems using  $\mu$ PD17005 or  $\mu$ PD17003A (a model of  $\mu$ PD17005 with reduced ROM and RAM).

Also refer to the Data Sheets of the  $\mu$ PD17005 and  $\mu$ PD17003A.

The electrical characteristics (such as the supply current) of the  $\mu$ PD17P005 and the analog characteristics of the PLL are different from those of the  $\mu$ PD17005. Therefore, take these differences into consideration when designing and producing the application systems.

#### **FEATURES**

- Compatible with μPD17005 and 17003A

- Internal one-time PROM: 7932 x 16 bits

- Operating voltage range: 5 V±10%

- I<sup>2</sup>C bus (μPD17P005GF-E00-3B9)

- QTOP<sup>TM</sup> microcontroller model available (μPD17P005GF-xxx-3B9)

#### ORDERING INFORMATION

| PART NUMBER           | PACKAGE                  | QUALITY GRADE   |

|-----------------------|--------------------------|-----------------|

| μPD17P005GF-3B9       | 80-pin plastic QFP (14 x | 20 mm) Standard |

| μPD17P005GF-E00-3B9*1 | 80-pin plastic QFP (14 x | 20 mm) Standard |

| μPD17P005GF-xxx-3B9*2 | 80-pin plastic QFP (14 x | 20 mm) Standard |

- \* 1: I<sup>2</sup>C bus model

- \* 2: QTOP microcontroller model

Remarks: QTOP microcontroller is the generic name of a single-chip microcontroller with a one-time PROM that is programmed, stamped, screened, and verified by NEC.

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grades on the devices and their recommended applications.

The information in this document is subject to change without notice.

Document No. IC-2703A (0.D.No. IC-8081A) Date Published August 1992 P Printed in Japan

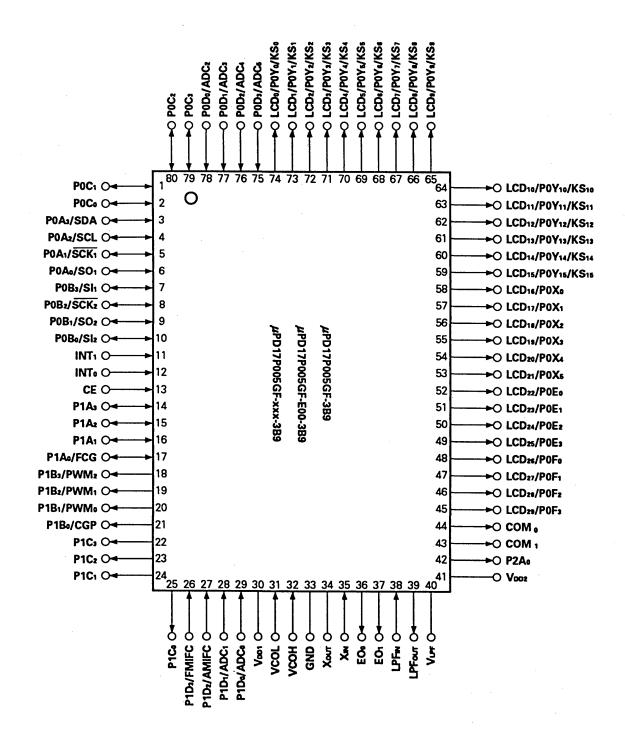

## PIN CONFIGURATION (Top View)

(1) In normal operation mode

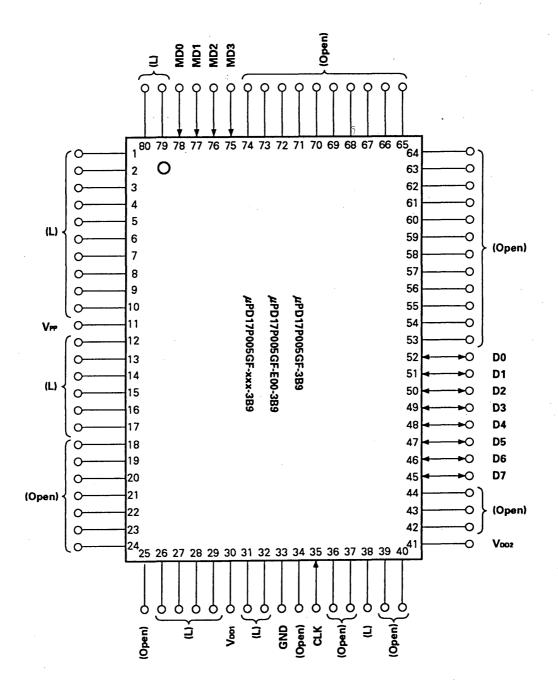

#### (2) In PROM programming mode

Note: ( ) indicates the processing of the pins not used in the PROM programming mode.

L :Ground these pins through an individual resistor (470 $\Omega$ )

Open :Do not connect anything to these pins.

## PIN NAME

| ADCo-ADCs : A/D converter input                                 | P0E <sub>0</sub> -P0E <sub>3</sub> : Port 0E           |

|-----------------------------------------------------------------|--------------------------------------------------------|

| AMIFC : Frequency counter input                                 | P0Fo-P0F3 : Port 0F                                    |

| CE : Chip enable input                                          | P0X <sub>0</sub> -P0X <sub>3</sub> : Port 0X           |

| CGP : Clock generator port                                      | P0Yo-P0Y3 : Port 0Y                                    |

| COMo, COM1: LCD common signal output                            | P1A <sub>0</sub> -P1A <sub>3</sub> : Port 1A           |

| CLK : PROM address updating clock input                         | P1Bo-P1B3 : Port 1B                                    |

| D0-D7 : PROM data I/O                                           | P1C <sub>0</sub> -P1C <sub>3</sub> : Port 1C           |

| EO <sub>0</sub> , EO <sub>1</sub> : Error out output            | P1D <sub>0</sub> -P1D <sub>3</sub> : Port 1D           |

| FCG : External gate counter input                               | P2Ao : Port 2A                                         |

| FMIFC : Frequency counter input                                 | PWMo-PWM2: D/A converter output                        |

| GND : Ground                                                    | SCK <sub>1</sub> , SCK <sub>2</sub> : Serial clock I/O |

| INTo, INTo : External interrupt input                           | SCL : Serial clock I/O                                 |

| KS <sub>0</sub> -KS <sub>15</sub> : Key source signal output    | SDA : Serial data I/O                                  |

| LCD <sub>0</sub> -LCD <sub>29</sub> : LCD segment signal output | Sl <sub>1</sub> , Sl <sub>2</sub> : Serial data input  |

| LPF <sub>IN</sub> : LPF amplifier input                         | SO <sub>1</sub> , SO <sub>2</sub> : Serial data output |

| LPFουτ : LPF amplifier output                                   | VCOH : Local oscillator input, high                    |

| MD0-MD3 : Operation mode select                                 | VCOL : Local oscillator input, low                     |

| P0A <sub>0</sub> -P0A <sub>3</sub> : Port 0A                    | VDD1, VDD2 : Positive power supply                     |

| P0Bo-P0B3 : Port 0B                                             | VLPF : LPF amplifier power source                      |

| P0C <sub>0</sub> -P0C <sub>3</sub> : Port 0C                    | VPP : PROM write power source                          |

| P0Do-P0D3 : Port 0D                                             | XIN, XOUT: Main clock oscillator                       |

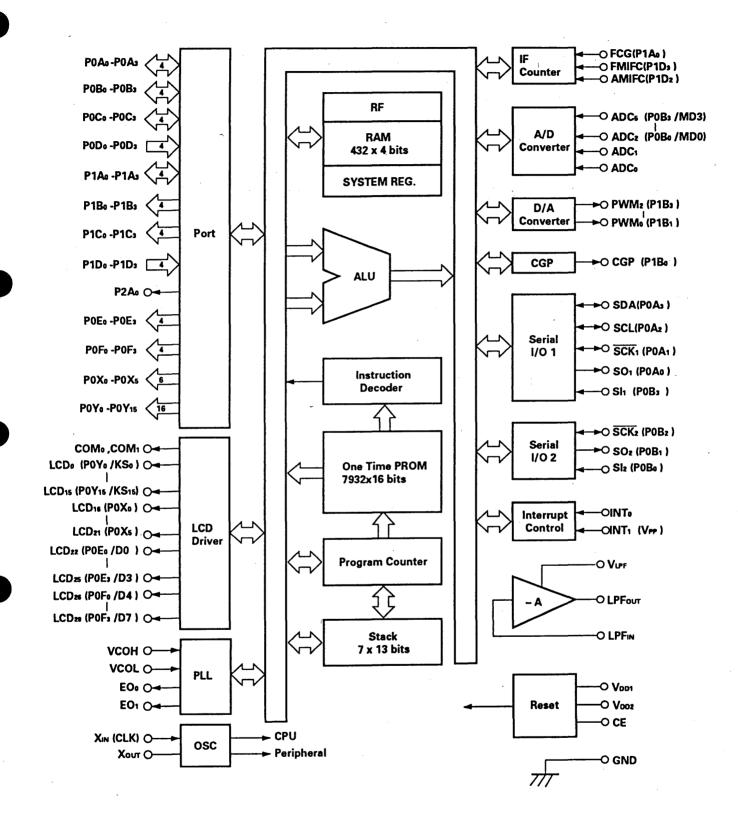

#### **BLOCK DIAGRAM**

## **Table of Contents**

| 1. | PINF | UNCTIONS                                                          | 7  |

|----|------|-------------------------------------------------------------------|----|

|    | 1.1  | NORMAL OPERATION MODE                                             | _  |

|    | 1.2  | PROM PROGRAMMING MODE                                             |    |

|    | 1.3  | EQUIVALENT CIRCUIT OF PIN                                         | 11 |

| 2. | FUN  | CTION LIST                                                        | 15 |

| 3. |      | TING, READING, AND VERIFYING ONE-TIME PROM (PROGRAM MEMORY)       |    |

|    | 3.1  | OPERATION MODE FOR WRITING, READING, AND VERIFYING PROGRAM MEMORY | 18 |

|    | 3.2  | WRITING PROGRAM MEMORY                                            | 40 |

|    | 3.3  | READING PROGRAM MEMORY                                            | 20 |

| 4. | ELE( | CTRICAL SPECIFICATIONS                                            | 21 |

|    |      |                                                                   |    |

| 5. | PAC  | KAGE DRAWINGS                                                     | ~~ |

|    |      |                                                                   |    |

| 6. | REC  | OMMENDED SOLDERING CONDITIONS                                     | 27 |

| ΑP | PEND | IX DEVELOPMENT TOOLS                                              | 20 |

|    |      |                                                                   | 40 |

## 1. PIN FUNCTIONS

## 1.1 NORMAL OPERATION MODE

| PIN NO. | SYMBOL FUNCTION                    |                                                           | OUTPUTFORM                            | WHENPOWER-ON<br>RESET                 |  |

|---------|------------------------------------|-----------------------------------------------------------|---------------------------------------|---------------------------------------|--|

| 79      | P0C <sub>3</sub>                   | 4-bit I/O port.                                           |                                       |                                       |  |

| 80      | P0C <sub>2</sub>                   | Can be set in input or output mode in 4-bit units         | CMOS push-pull                        | Input                                 |  |

| 1       | P0C <sub>1</sub>                   |                                                           |                                       | input                                 |  |

| 2       | P0C₀                               |                                                           |                                       | ·                                     |  |

|         |                                    | I/O lines of port 0A, port 0B, and serial interface.      | N-ch open-drain                       |                                       |  |

| 3       | P0A <sub>3</sub> /SDA              | • P0A <sub>3</sub> -P0A <sub>0</sub>                      | 5 V                                   |                                       |  |

|         |                                    | · 4-bit I/O port                                          | POA3/SDA,                             |                                       |  |

| 4 ,     | P0A <sub>2</sub> /SCL              | Can be set in input or output mode in 1-bit units.        | P0A2/SCL                              |                                       |  |

|         |                                    | • P0B <sub>3</sub> -P0B <sub>0</sub>                      |                                       |                                       |  |

| 5       | POA1/SCK1                          | 4-bit CMOS I/O port                                       |                                       |                                       |  |

|         |                                    | Can be set in input or output mode in 1-bit units.        |                                       |                                       |  |

| 6       | P0A <sub>0</sub> /SO <sub>1</sub>  | • SDA, SCL                                                |                                       |                                       |  |

|         |                                    | · SDA: Serial data I/O                                    | CMOS push-pull                        | Input                                 |  |

| 7       | P0B <sub>3</sub> /Sl <sub>1</sub>  | SCL: Serial clock I/O                                     | POA1, SCK1,                           | P0A <sub>3</sub> -P0A <sub>0</sub> ,  |  |

|         |                                    | • SCK1, SO1, SI1                                          | P0Ao/SO1,                             | P0B <sub>3</sub> -P0B <sub>0</sub>    |  |

| 8       | P0B <sub>2</sub> /SCK <sub>2</sub> | SCK1: Serial clock I/O                                    | POB <sub>3</sub> ,                    |                                       |  |

|         |                                    | - SO <sub>1</sub> : Serial data output                    | P0B2/SCK2,                            |                                       |  |

| 9       | P0B1/SO2                           | Sh: Serial data input                                     | P0B1/SO2,                             |                                       |  |

|         |                                    | • SCK2, SO2, SI2                                          | POB <sub>0</sub>                      |                                       |  |

| 10      | P0Bo/SI2                           | · SCK <sub>2</sub> : Serial clock I/O                     |                                       |                                       |  |

|         |                                    | - SO₂: Serial data output                                 | ]                                     |                                       |  |

|         |                                    | · Sl <sub>2</sub> : Serial data input                     |                                       |                                       |  |

| 11      | INT <sub>1</sub>                   | Edge-detectable vector interrupt input.                   | _                                     | Input                                 |  |

| 12      | INT <sub>0</sub>                   | Both rising and falling edges can be selected             |                                       |                                       |  |

| 13      | CE                                 | Selects operation of µPD17P005 and inputs reset signal    | _                                     | Input                                 |  |

|         |                                    | I/O lines of port 1A and external gate counter input line |                                       |                                       |  |

| 14      | P1A <sub>3</sub>                   | • P1A <sub>3</sub> -P1A <sub>0</sub>                      |                                       |                                       |  |

| 1 1     |                                    | · 4-bit CMOS I/O port                                     | CMOS push-pull                        | Input                                 |  |

| 16      | P1A <sub>1</sub>                   | Can be set in input or output mode in 1-bit units         | (P1A <sub>3</sub> -P1A <sub>0</sub> ) | (P1A <sub>3</sub> -P1A <sub>0</sub> ) |  |

| 17      | P1A <sub>4</sub> /FCG              | • FCG                                                     |                                       |                                       |  |

|         |                                    | External gate counter input                               |                                       |                                       |  |

| 18      | P1B <sub>3</sub> /PWM <sub>2</sub> | Output lines of port 1B, D/A converter, and clock genera- | N-ch open-drain                       |                                       |  |

|         |                                    | tor port                                                  | 16 V _                                |                                       |  |

| 19      | P1B <sub>2</sub> /PWM <sub>1</sub> | • P1B <sub>3</sub> -P1B <sub>0</sub>                      | P1B <sub>3</sub> /PWM <sub>2</sub>    | 0                                     |  |

|         | 1 1021 11111                       | - 4-bit output port                                       |                                       | Outputs undefined data                |  |

| 20      | P1B <sub>1</sub> /PWM <sub>0</sub> | • PWM2-PWMo                                               | P1B1/PWMo                             | (P1B <sub>3</sub> -P1B <sub>0</sub> ) |  |

|         |                                    | Output of D/A converter with 8-bit resolution             |                                       |                                       |  |

| 21      | P1B <sub>4</sub> /CGP              | • CGP                                                     | CMOS push-pull                        |                                       |  |

|         |                                    | Clock generator port output                               | (P1B <sub>0</sub> /CGP)               |                                       |  |

| 22      | P1C <sub>3</sub>                   |                                                           |                                       | 0.4                                   |  |

|         | 1                                  | 4-bit CMOS output port                                    | CMOS push-pull                        | Outputs undefined data                |  |

| 25      | P1C₀                               |                                                           |                                       |                                       |  |

| PIN NO.   | SYMBOL                               | FUNCTION                                                                                                                       | OUTPUTFORM              | WHENPOWER-ON<br>RESET  |

|-----------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|

| 26        | P1D <sub>3</sub> /FMIFC              | Analog input to port 1D, frequency counter, and A/D converter                                                                  |                         |                        |

| 27        | P1D2/AMIFC                           | • P1D <sub>3</sub> -P1D <sub>0</sub>                                                                                           |                         |                        |

|           | ·                                    | 4-bit input port                                                                                                               |                         |                        |

| 28        | P1D1/ADC1                            | • FMIFC, AMIFC                                                                                                                 |                         | Input                  |

|           | ·                                    | Input of frequency counter                                                                                                     |                         | (P1D3-P1Do)            |

| 29        | P1Do/ADCo                            | • ADC <sub>1</sub> , ADC <sub>0</sub>                                                                                          |                         | ·                      |

|           |                                      | · Analog input to A/D converter with 6-bit resolution                                                                          |                         |                        |

| 30        | Voot                                 | Positive power supply. Apply 5 V±10% to this pin in normal operation mode. Apply 6 V to write, read, or verify program memory. | _                       | _                      |

| 31        | VCOL                                 |                                                                                                                                |                         |                        |

| 32        | vсон                                 | Inputs local oscillation frequency of PLL                                                                                      | _                       | Input                  |

| 33        | GND                                  | Ground                                                                                                                         |                         |                        |

| 34        | Хоит                                 | Connect crystal oscillator for system clock oscillation                                                                        | CMOS push-pull          |                        |

| 35        | Xin                                  | across these pins.                                                                                                             |                         |                        |

| 36        | EO <sub>0</sub>                      | Output from charge pump of PLL frequency synthesizer.<br>Compares divided value of local oscillation frequency                 | CMOS                    | HighImpedance          |

| 37        | EO <sub>1</sub>                      | with phase of reference frequency, and outputs result of comparison                                                            | 3-state                 | riigiriinpedance       |

| 38        | LPFin                                | Input of amplifier for low-pass filter                                                                                         | _                       |                        |

| 39        | LPFout                               | Output of amplifier for low-pass filter                                                                                        | N-ch open-drain<br>16 V |                        |

| 40        | VLPF                                 | Power to amplifier for low-pass filter                                                                                         | _                       |                        |

| 41        | VDO2                                 | Positive power supply. Apply 5 V±10% to this pin in normal operation mode. Apply 6 V to write, read, or verify program memory. | · <b>-</b>              | _                      |

| 42        | P2A₀                                 | 1-bit CMOS output port                                                                                                         | CMOS push-pull          | Outputs undefined data |

| 43<br>44  | COM <sub>1</sub><br>COM <sub>0</sub> | Outputs common signal of LCD controller/driver                                                                                 | CMOS<br>3-value output  | Low-level output       |

| <b>45</b> | LCD29/P0F3                           | Output lines of ports 0F, 0E, 0X, 0Y, and segment signals of LCD controller/driver, and key source signals of key matrix       |                         |                        |

| 48        | LCD26/P0Fo                           | • P0F <sub>3</sub> -P0F <sub>0</sub>                                                                                           |                         |                        |

| 49        | LCD25/P0E3                           | 4-bit CMOS output port                                                                                                         |                         |                        |

|           |                                      | • P0E <sub>3</sub> -P0E <sub>0</sub>                                                                                           |                         |                        |

| 52        | LCD22/P0Eo                           | · 4-bit CMOS output port                                                                                                       |                         |                        |

| 53        | LCD21/P0X5                           | • P0X₅-P0X₀                                                                                                                    | CMOS push-pull          | Low-level output       |

| 1         |                                      | · 6-bit CMOS output port                                                                                                       |                         | (LCDze-LCDo)           |

| 58        | LCD1e/P0Xe                           | • P0Y15-P0Y0                                                                                                                   |                         | ,                      |

| 59        | LCD15/P0Y15/KS15                     | 16-bit CMOS output port                                                                                                        |                         |                        |

|           |                                      | • LCD <sub>28</sub> -LCD <sub>0</sub>                                                                                          |                         |                        |

| 74        | LCDv/P0Yv/KSo                        | <ul> <li>Segment signal output of LCD controller/driver</li> <li>KS<sub>15</sub>-KS<sub>0</sub></li> </ul>                     |                         |                        |

|           |                                      | Key source signal output of key matrix                                                                                         |                         | l                      |

|           |                                      | ,g easper or noy much                                                                                                          |                         | •                      |

| PIN NO.                                   | SYMBOL    | FUNCTION                                                                                                                                                                                                                                                                      | OUTPUTFORM | WHEN POWER-ON RESET                              |

|-------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------------|

| 75<br> <br> <br> <br> <br> <br> <br> <br> | P0Da/ADCs | Port 0D, analog input line to A/D converter, and key source signal return input line of LCD segment  • P0D3-P0D0  • 4-bit input port  • Connected to pull-down resistor  • ADC5-ADC2  • Analog input to A/D converter with 6-bit resolution  • Key source signal return input | _          | Input with pull-<br>down resistor<br>(P0D3-P0Do) |

## 1.2 PROMPROGRAMMING MODE

| PIN NO.              | SYMBOL              | FUNCTION                                                                                                       | OUTPUT FORM    |

|----------------------|---------------------|----------------------------------------------------------------------------------------------------------------|----------------|

| 11                   | VPP                 | Positive power supply for PROM programming. Apply 12.5 V to this pin to write, read, or verify program memory. | _              |

| 30                   | V <sub>D</sub> D1   | Positive power supply.  Apply 6 V to this pin to write, read, or verify program memory.                        | _              |

| 33                   | GND                 | Ground                                                                                                         | _              |

| 35                   | CLK                 | Clock input for PROM programming                                                                               | _              |

| 41                   | VDD2                | Positive power supply. Apply 6 V to this pin to write, read, or verify program memory.                         | _              |

| 45<br> <br> <br>  52 | D7<br> <br> <br> D0 | 8-bit data I/O for PROM programming                                                                            | CMOS push-pull |

| 75<br> <br> <br>78   | MD3<br> <br>MD0     | Input to select operation mode when PROM is programmed                                                         | _              |

Remarks: Pins other than the above are not used in the PROM programming mode. For the processing of the unused pins, refer to (2) PROM programming mode in Pin Connections.

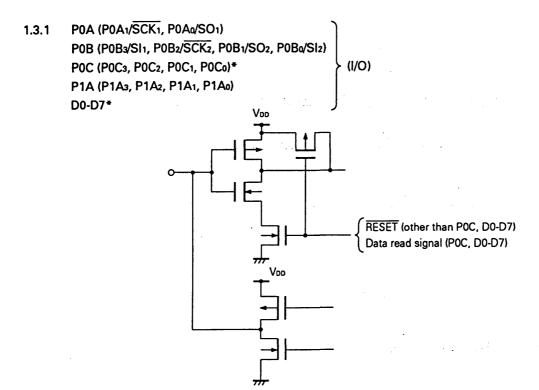

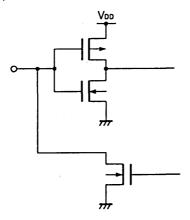

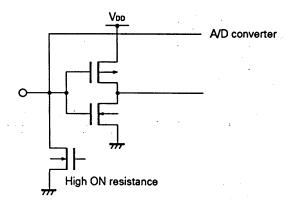

#### 1.3 EQUIVALENT CIRCUIT OF PIN

\* :The RESET signal is not supplied to P0C and D0-D7.

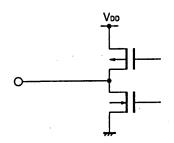

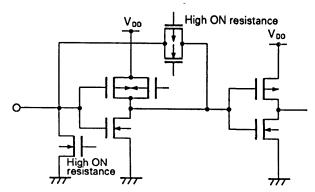

### 1.3.2 POA (POA3/SDA, POA2/SCL) (I/O)

1.3.3 P1B (P1Bo/CGP)

P1C (P1C<sub>3</sub>, P1C<sub>2</sub>, P1C<sub>1</sub>, P1C<sub>0</sub>)

P2A (P2A<sub>0</sub>)

LCD<sub>0</sub>/P0Y<sub>0</sub>/KS<sub>0</sub>-LCD<sub>29</sub>/P0F<sub>3</sub>

(Output)

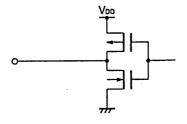

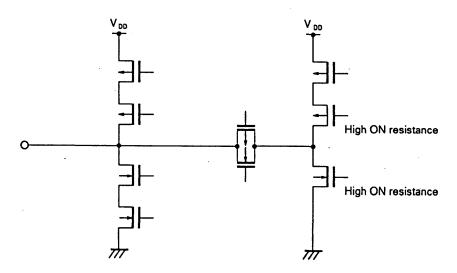

### 1.3.4 P1B (P1B<sub>3</sub>/PWM<sub>2</sub>, P1B<sub>2</sub>/PWM<sub>1</sub>, P1B<sub>1</sub>/PWM<sub>0</sub>) (Output)

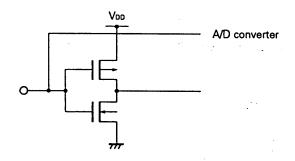

## 1.3.5 P0D (P0D<sub>3</sub>/ADC<sub>5</sub>/MD3, P0D<sub>2</sub>/ADC<sub>4</sub>/MD2, P0D<sub>1</sub>/ADC<sub>3</sub>/MD1, P0D<sub>0</sub>/ADC<sub>2</sub>/MD0) (Input)

## 1.3.6 P1D (P1D<sub>1</sub>/ADC<sub>1</sub>, P1D<sub>0</sub>/ADC<sub>0</sub>) (Input)

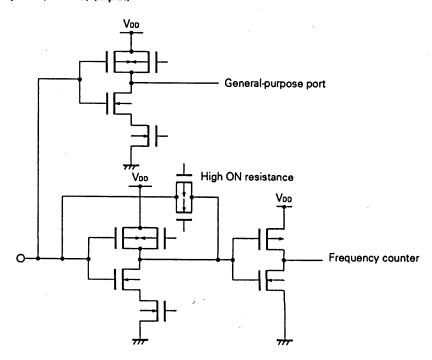

## 1.3.7 P1D (P1D<sub>3</sub>/FMIFC, P1D<sub>2</sub>/AMIFC) (Input)

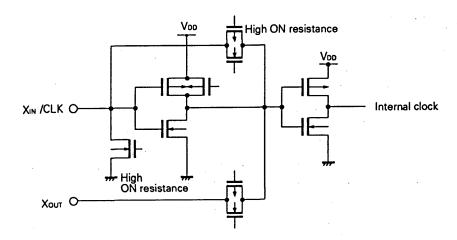

## 1.3.9 Хоит (output), XIN/CLK (input)

$$\begin{array}{cc}

1.3.10 & EO_1 \\

EO_0

\end{array} \right\} (Output)$$

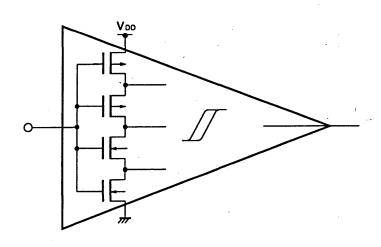

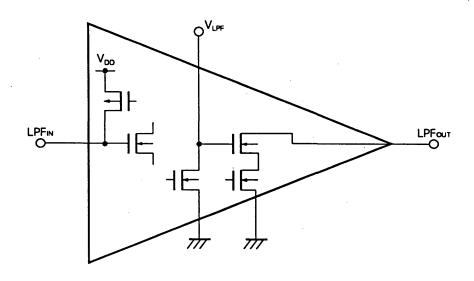

## 1.3.11 LPFIN (input), LPFout (output), VLPF

$$\begin{array}{cc} 1.3.12 & COM_1 \\ & COM_0 \end{array} \right\} \mbox{ (Output)}$$

## 2. FUNCTION LIST

| ITEM                                    | PRODUCT NAME   | μPD17003A                                                                                                                                                               | μPD17005                            | μPD17P005   |  |  |  |

|-----------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------|--|--|--|

| ROM (×16 bits)                          |                | 3836 (mask ROM)                                                                                                                                                         | 7932 (mask ROM)                     | 7932 (PROM) |  |  |  |

| Table reference area RAM (x4 bits)      |                | 256 7932                                                                                                                                                                |                                     |             |  |  |  |

|                                         |                | 320 432                                                                                                                                                                 |                                     |             |  |  |  |

| Data b                                  | uffer          |                                                                                                                                                                         | 4                                   |             |  |  |  |

| Genera                                  | al register    |                                                                                                                                                                         | 16                                  |             |  |  |  |

| System regi                             | ster           |                                                                                                                                                                         | 12×4 bits                           |             |  |  |  |

| Register file                           |                |                                                                                                                                                                         | 33 × 4 bits (control register)      |             |  |  |  |

| General-pur<br>register                 | pose port      |                                                                                                                                                                         | 24 × 4 bits                         |             |  |  |  |

| Instruction e                           | execution time | 4.                                                                                                                                                                      | 44 μs (at 4.5 MHz, crystal oscillat | tor)        |  |  |  |

| Stack level                             |                |                                                                                                                                                                         | 7 (stack can be manipulated)        | ·           |  |  |  |

| General-                                | I/O port       |                                                                                                                                                                         | 16 lines                            |             |  |  |  |

| purpose                                 | Input port     |                                                                                                                                                                         | 8 lines                             |             |  |  |  |

| port                                    | Output port    | 9 lines (+30: LCD segment pin)                                                                                                                                          |                                     |             |  |  |  |

| Clock gener                             | ator port      | 1 line                                                                                                                                                                  |                                     |             |  |  |  |

| LCD controller/driver  Serial interface |                | Segment pins multiplexed<br>All 30 lines can be used as                                                                                                                 |                                     |             |  |  |  |

|                                         |                | 2 systems (3 channels) Serial interface 1: 2-line I <sup>2</sup> C bus mode*, serial I/O mode  3-line Serial I/O mode  Serial interface 2: 3-line Serial I/O mode       |                                     |             |  |  |  |

| D/A converte                            | er             | · 8 bits × 3 lines (PWM output, output voltage: 16 V max.)                                                                                                              |                                     |             |  |  |  |

| A/D converte                            | r              | 6 bits × 6 lines (successive approximation method by software)                                                                                                          |                                     |             |  |  |  |

| Interrupt                               |                | • 5 channels (maskable interrupt)  External interrupt : 2 channels (INTo pin, INTo pin)  Internal interrupt : 3 channels (timer, serial interface 1, frequency counter) |                                     |             |  |  |  |

| Timer                                   |                | · 2 systems Timer carry (1, 5, 100, 250 ms) Timer interrupt (1, 5, 100, 250 ms)                                                                                         |                                     |             |  |  |  |

| Reset function                          | on             | <ul> <li>Power-ON reset (on power application)</li> <li>Reset by CE pin (CE pin: low level→high level)</li> <li>Power failure detection function</li> </ul>             |                                     |             |  |  |  |

<sup>\*:</sup> Among the PROM models, only  $\mu$ PD17P005GF-E00-3B9 can use the l<sup>2</sup>C bus mode. For the mask ROM model, it is confirmed when an order for the custom code is received.

## (con't)

| ITEM                            | RODUCT NAME         | μPD17003A                                                                                                              | μPD17005                                                                               | μPD17P005 |  |  |  |  |

|---------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------|--|--|--|--|

|                                 | Division<br>modes   | Pulse swallow method                                                                                                   | (VCOL pin 30 MHz max.)<br>(VCOL pin 40 MHz max.)<br>(VCOH pin 150 MHz max.)            |           |  |  |  |  |

| PLL<br>frequency<br>synthesizer | Reference frequency | • •                                                                                                                    | 12 types selected by program<br>1, 1.25, 2.5, 3, 5, 6.25, 9, 10, 12.5, 25, 50, 100 kHz |           |  |  |  |  |

| Synthesizer                     | Charge pump         | · Two independent error outputs                                                                                        |                                                                                        |           |  |  |  |  |

|                                 | Phase comparator    | <ul> <li>Unlock can be detected<br/>Delay time of unlock FF</li> </ul>                                                 |                                                                                        |           |  |  |  |  |

|                                 | LPF amp             | · CMOS operational amp.                                                                                                | Output withstand voltage: 16 V                                                         | max.      |  |  |  |  |

| Frequency co                    | unter               | Frequency measurement P1D₂/FMIFC pin 5 to 15 I P1D₂/AMIFC pin 0.1 to 1 External gate width mea P1A₂/FCG pin            | MHz<br>MHz                                                                             |           |  |  |  |  |

| Supply voltage                  |                     | <ul> <li>VDD = 4.5 to 5.5 V (PLL ar</li> <li>VDD = 3.5 to 5.5 V (PLL st</li> <li>VDD = 2.2 to 5.5 V (crysta</li> </ul> | ops, CPU operates)                                                                     |           |  |  |  |  |

| Package                         |                     | 80-pin plastic QFP (14 × 20                                                                                            | 0 mm)                                                                                  |           |  |  |  |  |

### 3. WRITING, READING, AND VERIFYING ONE-TIME PROM (PROGRAM MEMORY)

The internal program memory of the  $\mu$ PD17P005 is a 15864  $\times$  8 bit one-time PROM to which data can be electrically written. This PROM is accessed in 1-word or 16-bit units in a normal operation mode. When the program memory is written, read, or verified, the PROM is accessed in 1-word or 8-bit units. The higher 8 bits of 1 word or 16 bits are assigned to an even address, while the lower 8 bits are assigned to an odd address.

When the PROM is to be written, read, or verified, set the PROM mode and use the pins shown in Table 3-1 below.

Note that there is no address input pin. Instead, the clock signal input from the CLK pin is used to update the address.

Table 3-1 Pins Used to Write, Read, or Verify Program Memory

| PIN NAME   | FUNCTION                         |

|------------|----------------------------------|

| VPP        | Applies program voltage (12.5 V) |

| CLK        | Inputs address updating clock    |

| MD0-MD3    | Select operation mode            |

| D0-D7      | Input/output 8-bit data          |

| VDD1, VDD2 | Apply supply voltage (6 V)       |

Write the internal PROM by using the following PROM programmer and program adapter:

PROM programmer

AF-9703 (Ando Electric.)

AF-9704 (ditto)

Program adapter

AF-9803 (ditto)

#### 3.1 OPERATION MODE FOR WRITING, READING, AND VERIFYING PROGRAM MEMORY

The  $\mu$ PD17P005 is set in a mode to write, read, or verify the program memory when +6 V is applied to the Vpp pin and +12.5 V is applied to the VPP pin.

To set the program memory write, read, and verify modes, use the MD0 through MD3 pins as shown in Table 3-2.

The pins not used to write, read, or verify the program memory should be either opened, or connected to GND through a pull-down resistor (470  $\Omega$ ). (Refer to (2) PROM programming mode in Pin Configuration.)

Table 3-2 Operation Mode When Program Memory is Written, Read, or Verified

|        | SPECIF       | IES OPE | RATION | OPERATIONAGE |            |                                |

|--------|--------------|---------|--------|--------------|------------|--------------------------------|

| Vpp    | VDD          | MD0     | MD1    | MD2          | MD3        | OPERATION MODE                 |

|        |              | Н       | L      | Н            | L          | Clears program memoryaddressto |

| 40.51/ | <b>6</b> ) ( | L H     | Н      | Н            | Write mode |                                |

| +12.5V | +6V          | L       | L      | Н            | Н          | Read, verify modes             |

|        |              | Н       | X      | Н            | Н          | Program inhibit mode           |

Remarks: X: L or H

## 3.2 WRITING PROGRAM MEMORY

The program memory can be written at high speeds in the following sequence:

- (1) Pull down the unused pins to GND through a resistor. Keep the CLK pin at the low level.

- (2) Supply 5 V to the VDD and VPP pins.

- (3) Wait for 10 us.

- (4) Set the program memory address 0 clear mode.

- (5) Supply 6 V to the Voo pin and 12.5 V to the VPP pin.

- (6) Set the program inhibit mode.

- (7) Write data in 1-ms write mode.

- (8) Set the program inhibit mode.

- (9) Set the verify mode. If the program memory has been correctly written, proceed to step (10). If not, repeat steps (7) through (9).

- (10) Additional writing of (Number of times the program memory has been written in (7) through (9): X) × 1 ms

- (11) Set the program inhibit mode.

- (12) Input a pulse to the CLK pin four times to update the program memory address by one (+1).

- (13) Repeat steps (7) through (12) until the last address is written.

- (14) Set the program memory address 0 clear mode.

- (15) Change the voltage on the VDD and VPP pins to 5 V.

- (16) Turn off the power.

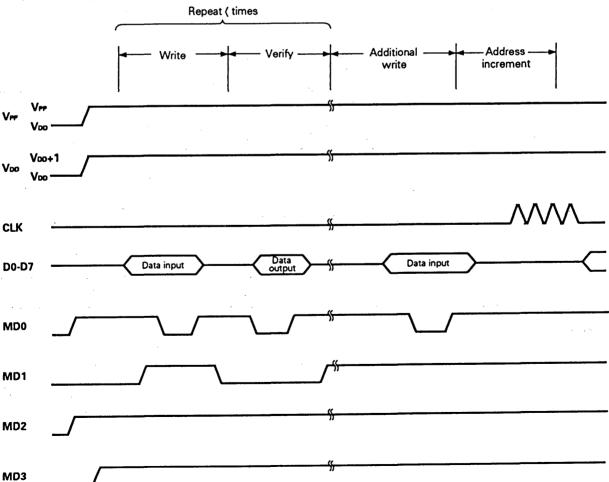

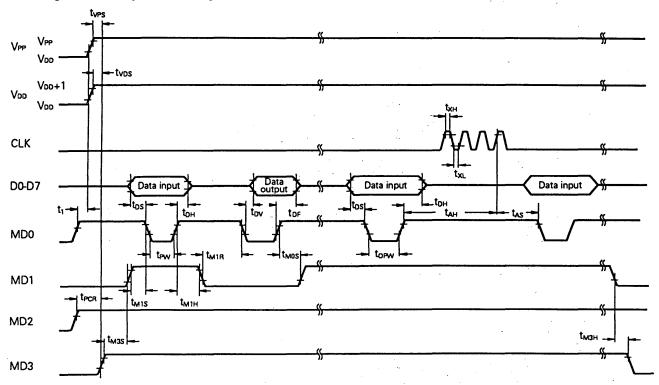

Steps (2) through (12) are illustrated below.

#### 3.3 READING PROGRAM MEMORY

Read the contents of the program memory of the  $\mu$ PD17P005 in the following sequence:

- (1) Pull down the unused pins to GND through a resistor. Keep the CLK pin at the low level.

- (2) Supply 5 V to the Voo and VPP pins.

- (3) Wait for 10 us.

- (4) Set the program memory address 0 clear mode.

- (5) Supply 6 V to the Vop pin and 12.5 V to the VPP pin.

- (6) Set the program inhibit mode.

- (7) Set the verify mode. When the clock pulse is input to the CLK pin, data is sequentially output one address at a time with four clocks constituting one cycle.

- (8) Set the program inhibit mode.

- (9) Set the program memory address 0 clear mode

- (10) Change the voltage on the VDD and VPP pins to 5 V.

- (11) Turn off the power.

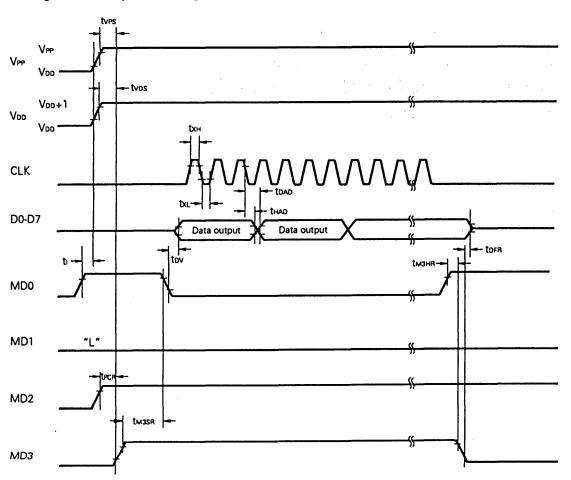

Steps (2) through (9) are illustrated below.

## 4. ELECTRICAL SPECIFICATIONS

## Absolute Maximum Ratings (Ta = 25±2°C)

| PARMETER                  | SYMBOL            | CONDITION                                                                                 | RATINGS                        | UNIT |

|---------------------------|-------------------|-------------------------------------------------------------------------------------------|--------------------------------|------|

| Supply Voltage            | Voo               |                                                                                           | - 0.3 to +6.0                  | V    |

| Input Voltage             | Vi                |                                                                                           | - 0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output Voltage            | Vo                | Except P1B <sub>1</sub> - P1B <sub>3</sub> , P0A <sub>2</sub> , P0A <sub>3</sub> , LPFout | - 0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output Withstand Voltage  | V <sub>BD81</sub> | P1B1 - P1B3, LPFout                                                                       | 18.0                           | V    |

|                           | V <sub>BDS2</sub> | P0A <sub>2</sub> , P0A <sub>3</sub>                                                       | Voo + 0.3                      | V    |

|                           |                   | 1 pin                                                                                     | - 12                           | mA   |

| High-Level Output Current | Юн                | Total of all pins                                                                         | - 20                           | mA   |

|                           |                   | 1 pin                                                                                     | 12                             | mA   |

| Low-Level Output Current  | loL               | Total of all pins                                                                         | 20                             | mA   |

| Operating Temperature     | Topt              |                                                                                           | - 40 to + 85                   | °C   |

| Storage Temperature       | Tstg              |                                                                                           | - 55 to + 125                  | °C   |

## **Recommended Operating Conditions**

| SYMBOL           | CONDITIONS                          | MIN.                                                  | TYP.                                                  | MAX                                                   | UNIT                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|-------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD1             | PLL and CPU operate                 | 4.5                                                   | 5.0                                                   | 5.5                                                   | ٧                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>DD2</sub> | PLL stops, CPU operates             | 3.5                                                   | 5.0                                                   | 5.5                                                   | ٧                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VDDR             | Crystal oscillator stops            | 2.2                                                   |                                                       | 5.5                                                   | · V                                                                                                                                                                                                                                                                                                                                                                                                                     |

| trise            | V <sub>DD</sub> = 0 → 4.5 V         |                                                       |                                                       | 500                                                   | ms                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Vin1             | VCOL, VCOH                          | 0.5                                                   |                                                       | Voo                                                   | V <sub>P-P</sub>                                                                                                                                                                                                                                                                                                                                                                                                        |

| Vin2             | AMIFC, FMIFC                        | 0.5                                                   |                                                       | Voo                                                   | V <sub>P-P</sub>                                                                                                                                                                                                                                                                                                                                                                                                        |

| Vaos             | P1B1 - P1B3, LPFouт                 |                                                       |                                                       | 16.0                                                  | ٧                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Topt             | · ,                                 | - 40                                                  |                                                       | +85                                                   | °C                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                  | VDD1 VDD2 VDDR trise Vin1 Vin2 VBDS | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | VDD1       PLL and CPU operate       4.5       5.0       5.5         VDD2       PLL stops, CPU operates       3.5       5.0       5.5         VDDR       Crystal oscillator stops       2.2       5.5         trise       VDD = 0 $\rightarrow$ 4.5 V       500         VIn1       VCOL, VCOH       0.5       VDD         VIn2       AMIFC, FMIFC       0.5       VDD         VBDS       P1B1 - P1B3, LPFout       16.0 |

## DC Characteristics (Ta = -40 to $+85^{\circ}$ C, $V_{DD}$ = 4.5 to 5.5 V)

| PARAMETER                            | SYMBOL                                           | CONDITIONS                                                                                  | MIN.                | TYP.  | MAX             | UNIT |

|--------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------|-------|-----------------|------|

| Supply Voltage                       | VDD1                                             | CPU and PLL operate                                                                         | 4.5                 | 5.0   | 5.5             | V    |

|                                      | VD02                                             | CPU operates, PLL stops                                                                     | 3.5                 | 5.0   | 5.5             | V    |

|                                      |                                                  | CPU operates, PLL stops. X <sub>IN</sub> pin                                                |                     |       |                 |      |

|                                      | loo1                                             | Sine wave input (fin = 4.5 MHz,<br>Vin = Voo), Ta = 25°C                                    |                     | 2.8   | 5.6             | mA   |

| Supply Current                       | lob2 executed in 1 ms) XIN pin                   |                                                                                             |                     | 1.9   | 3.8             | mA   |

|                                      |                                                  | Sine wave input (fin = 4.5 MHz,<br>Vin = Voo), Ta = 25°C                                    |                     |       |                 |      |

|                                      | VDDR1                                            | Power failure detected by timer FF; with crystal oscillator                                 | 3.5                 |       | 5.5             | ٧    |

| Data Retention Voltage               | . VDDR2                                          | Power failure detected by timer FF; crystal oscillator stops                                | 2.2                 |       | 5.5             | V    |

|                                      | VDDR3                                            | Data memory (RAM) retained                                                                  | 2.0                 |       | 5.5             | V    |

|                                      | IDDR1                                            | Crystal oscillator stops Ta = 25°C                                                          |                     | 2     | 15              | μА   |

| Data Retention Current               | I DDR2                                           | Crystal oscillator stops V <sub>DD</sub> = 5.0 V,<br>Ta = 25°C                              | ·                   | 2     | 10              | μΑ   |

| Intermediate Level Output<br>Voltage | Vом1                                             | COMo, COM1 VDD= 5 V                                                                         | 2.3                 | 2.5   | 2.7             | ٧    |

| High-Level Input Voltage             | Vін1                                             | P0Ao-P0As, P0Bo-P0Bs, P0Co-P0Cs,<br>P1Ao-P1As, P1Do-P1Ds,<br>CE, INTo, INTs                 | 0.8 V <sub>DD</sub> |       | V <sub>DD</sub> | ٧    |

| •                                    | VIH2                                             | P0Do-P0D3                                                                                   | 0.6 Vpp             |       | Voo             | V    |

|                                      | <del>                                     </del> | P0Ao-P0A3, P0Bo-P0B3, P0Co-P0C3,                                                            | 0.0.00              |       | 730             | •    |

| Low-Level Input Voltage              | ViL                                              | P0Do-P0D3, P1Ao-P1A3, P1Do-P1D3,                                                            | 0                   |       | 0.2 VDD         | . V  |

|                                      |                                                  | CE, INTo, INTo                                                                              | <u> </u>            |       |                 |      |

| High-Level Output Current            | <b>ј</b> он1                                     | P0Ao, P0A1, P0Bo-P0B3, P0Co-P0C3,<br>P1Ao-P1A3, P1Co-P1C3, P1Bo, P2A3,                      | - 1.0               | - 5.0 |                 | mA   |

|                                      |                                                  | Vон = V <sub>DD</sub> - 1 V                                                                 |                     |       |                 |      |

|                                      | IOH2                                             | LCDo-LCD29, EOo, EO1 VoH = VDD - 1 V                                                        | - 1.0               | - 4.0 |                 | mA   |

| Low-Level Output Current             | lou                                              | P0Ao-P0A3, P0Bo-P0B3, P0Co-P0C3,<br>P1Ao-P1A3, P1Co-P1C3, P1Bo, P2Ao,<br>Vol = 1 V          | 1.0                 | 7.0   |                 | mA   |

| Low-Level Output current             | louz                                             | LCDo-LCD29, EOo, EO1 VoL = 1 V                                                              | 1.0                 | 3.5   |                 | mA   |

|                                      | lous                                             | P1B <sub>1</sub> -P1B <sub>3</sub> Vo <sub>L</sub> = 1 V                                    | 1.0                 | 2.0   |                 | mA   |

| ·                                    | lo <sub>L4</sub>                                 | P0A <sub>2</sub> , P0A <sub>3</sub> V <sub>OL</sub> = 1 V                                   | 1.0                 | 10.0  |                 | mA   |

|                                      | lini                                             | VCOH pulled down ViH = Vpp                                                                  | 0.1                 | 0.8   |                 | mA   |

| High-Level Input Current             | lih2                                             | VCOL pulled down Vin = Vpp                                                                  | 0.1                 | 0.8   |                 | mA   |

| g., acros impor contont              | Іінз                                             | Xin pulled down ViH = VDD                                                                   | 0.1                 | 1.3   |                 | mA   |

|                                      | lin4                                             | P0Da-P0Da pulled down ViH = Voo                                                             | 0.05                | 0.13  | 0.30            | mA   |

|                                      | lu                                               | POA <sub>2</sub> , POA <sub>3</sub> VoH = VoD                                               |                     |       | 500             | nA   |

| Output Off Leakage Current           | lı2                                              | P1B1-P1B3, LPFout Von = 16 V                                                                |                     |       | 500             | nA   |

|                                      | 11.3                                             | EO <sub>0</sub> , EO <sub>1</sub> V <sub>OH</sub> = V <sub>DD</sub> , V <sub>OL</sub> = 0 V |                     |       | ±100            | nA   |

## AC Characteristics (Ta = -40 to $+85^{\circ}$ C, VDD = 4.5 to 5.5 V)

| PARAMETER                 | SYMBOL | CONDITIONS                                                              | MIN. | TYP. | MAX  | UNIT |

|---------------------------|--------|-------------------------------------------------------------------------|------|------|------|------|

|                           | fina   | VCOL MF mode, sine wave input<br>V <sub>IN</sub> = 0.3 V <sub>P-P</sub> | 0.5  |      | 30   | MHz  |

|                           | fin2   | VCOL HF mode, sine wave input<br>V <sub>IN</sub> = 0.3 V <sub>P-P</sub> | 5    |      | 40   | MHz  |

|                           | fins   | VCOH, sine wave input VIN = 0.3 VP-P                                    | 9    |      | 150  | MHz  |

| Operating Fequency        | fin4   | AMIFC, sine wave input VIN = 0.5 VP-P                                   | 0.1  |      | 1    | MHz  |

|                           | fins   | AMIFC, sine wave input VIN = 0.05 VP-P                                  | 0.44 |      | 0.46 | MHz  |

|                           | fine   | FMIFC, sine wave input VIN = 0.5 VP-P                                   | 5    |      | 15   | MHz  |

|                           | fin7   | FMIFC, sine wave input VIN = 0.06 VP-P                                  | 10.5 |      | 10.9 | MHz  |

| A/D Converter Resolution  |        |                                                                         |      |      | 6    | bit  |

| A/D Converter Total Error |        | Ta = -10 to +50°C                                                       |      | ±1   | ±1.5 | LSB  |

## Reference Characteristics

| PARAMETER                         | SYMBOL | CONDITIONS  CPU and PLL operate  VCOH sine wave input  fin = 150 MHz, Vin = 0.5 Vp.p  Voo = 5 V, Ta = 25°C |                       | MIN. | TYP.  | MAX | UNIT |

|-----------------------------------|--------|------------------------------------------------------------------------------------------------------------|-----------------------|------|-------|-----|------|

| Supply Current                    | loos   |                                                                                                            |                       |      |       |     | · mA |

| High-Level Output Current         | 1он4   | COMo, COM1                                                                                                 | VoH = VDD - 1 V       |      | - 0.2 |     | mA   |

|                                   | Іомі   | COMo, COM1                                                                                                 | Vom = Voo - 1 V       |      | - 20  |     | μА   |

| Intermediate Level Output Current | lom2   | COMo, COM1                                                                                                 | V <sub>OM</sub> = 1 V |      | 20    |     | μΑ   |

| Low-Level Output Current          | lous   | COMo, COM1                                                                                                 | Vol = 1 V             |      | 0.2   |     | mA   |

## DC Programming Characteristics (Ta = 25°C, VDD = 6.0±0.25 V, VPP = 12.5±0.5 V)

| PARAMETER                      | SYMBOL          | CONDITIONS           | MIN.      | TYP. | MAX                 | UNIT |

|--------------------------------|-----------------|----------------------|-----------|------|---------------------|------|

| 11:-b-1                        | ViH1            | Other than CLK       | 0.7 Vpp   |      | Voo                 | V    |

| High-Level Input Voltage       | VIH2            | CLK                  | VDD - 0.5 |      | Voo                 | V    |

| Low Lovel Lanut Voltage        | VILI            | Other than CLK       | 0         |      | 0.3 V <sub>DD</sub> | V    |

| Low-Level Input Voltage        | VIL2            | CLK                  | . 0       |      | 0.4                 | ٧    |

| Input Leakage Current          | lu .            | Vin = Vil or Vih     |           |      | ±10                 | μА   |

| High-Level Output Voltage      | Vон             | lон = −1 mA          | Vpp - 1.0 |      |                     | V    |

| Low-Level Output Voltage       | Val             | loc = 1 mA           |           |      | 1.0                 | V    |

| Voo Supply Current             | loo             |                      |           |      | 30                  | mA   |

| V <sub>PP</sub> Supply Current | l <sub>PP</sub> | MD0 = VIL, MD1 = VIH |           |      | 30                  | mA   |

Note:Note: 1. Keep VPP to within +13.5 V including the overshoot.

2. Apply VDD before VPP and turn it off after VPP.

## AC Programming Characteristics (Ta = 25°C, $V_{DD}$ = $6.0\pm0.25$ V, $V_{PP}$ = $12.5\pm0.5$ V)

| PARAMETER                             | SYMBOL           | CONDITIONS                | MIN.  | TYP. | MAX.                                             | UNIT |

|---------------------------------------|------------------|---------------------------|-------|------|--------------------------------------------------|------|

| Address Setup Time* (vs. MD01)        | tas              |                           | 2     |      |                                                  | μs   |

| MD1 Setup Time (vs. MD0↓)             | tmis             |                           | 2     |      |                                                  | μs   |

| Data Setup Time (vs. MD0↓)            | tos              |                           | 2     |      |                                                  | μs   |

| Address Hold Time* (vs. MD01)         | tah              |                           | 2     |      |                                                  | μs   |

| Data Hold Time (vs. MD01)             | tон              |                           | 2     |      | <del>                                     </del> | μs   |

| MD01→ Data Output Float Delay<br>Time | tor              |                           | 0     |      | 130                                              | ns   |

| Ver Setup Time (vs. MD31)             | tives            |                           | 2     |      | · · · · · · · · · · · · · · · · · · ·            | μs   |

| Voo Setup Time (vs. MD31)             | tvos             |                           | 2     |      |                                                  | μs   |

| Initial Program Pulse Width           | tew              |                           | 0.95  | 1.0  | 1.05                                             | ms   |

| Additional Program Pulse Width        | topw             |                           | 0.95  |      | 21.0                                             | ms   |

| MD0 Setup Time (vs. MD11)             | tmos             |                           | 2     |      |                                                  | μз   |

| MD0↓→ Data Output Delay Time          | tov              | MD0 = MD1 = ViL           |       |      | 1                                                | μs   |

| MD1 Hold Time (vs. MD01)              | tмін             |                           | 2     |      |                                                  | μs   |

| MD1 Recovery Time (vs. MD0↓)          | t <sub>M1R</sub> | tm1+ tm1s ≥ 50 <i>μ</i> s | 2     |      |                                                  | μs   |

| Program Counter Reset Time            | teca             |                           | 10    |      |                                                  | μs   |

| CLK Input High-, Low-Level Width      | txH, txL         |                           | 0.125 |      |                                                  | μs   |

| CLK Input Frequency                   | fx               |                           |       |      | 4.19                                             | MHz  |

| Initial Mode Set Time                 | tı               |                           | 2     |      |                                                  | μз   |

| MD3 Setup Time (vs. MD11)             | tмзв             |                           | 2     |      |                                                  | μs   |

| MD3 Hold Time (vs. MD11)              | tмзн             |                           | 2     |      |                                                  | μs   |

| MD3 Setup Time (vs. MD0↓)             | tmasa            | Program memory read       | 2     |      |                                                  | μs   |

| Address*→Data Output Delay Time       | toad             | Program memory read       | 2     |      |                                                  | μs   |

| Address*→Data Output Hold<br>Time     | thad             | Program memory read       | 0     |      | 130                                              | ns   |

| MD3 Hold Time (vs. MD01)              | tмзня            | Program memory read       | 2     |      |                                                  | μз   |

| MD3↓→ Data Output Float Delay<br>Time | tora             | Program memory read       | 2     |      |                                                  | μs   |

<sup>\*:</sup> The internal address signal is incremented (+1) at the falling edge of thernal address signal is incremented (+1) at the falling edge of the third CLK signal (with one cycle consisting of four clocks). The internal address is not connected to a pin.

### **Program memory write timing**

## Program memory read timing

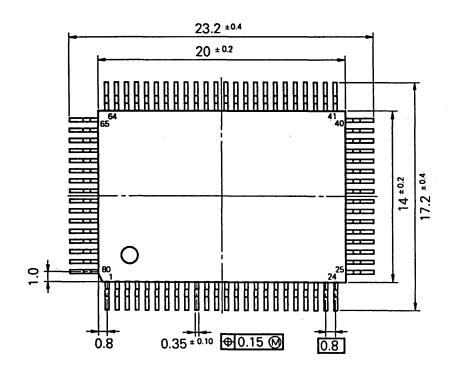

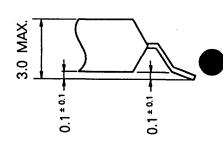

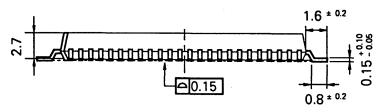

### 5. PACKAGE DRAWINGS

80-Pin Plastic QFP (14  $\times$  20) (Unit: mm)

Details of tip of pin

#### 6. RECOMMENDED SOLDERING CONDITIONS

The  $\mu$ PD17P005 should be soldered under the following recommended conditions. For soldering conditions other than those recommended below, consult NEC.

**Table 6-1 List of Recommended Soldering Conditions**

| PRODUCT NAME        | PACKAGE | CODE                |

|---------------------|---------|---------------------|

|                     |         | ·IR30-162           |

| μPD17P005GF-3B9     |         | ·VP15-162           |

| l'                  |         | ·WS60-162           |

| μPD17P005GF-xxx-3B9 | •       | Pin partial heating |

**Table 6-2 Soldering Conditions**

| CODE                | SOLDERING METHOD    | SOLDERING CONDITIONS                                                                                                                                                   |

|---------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IR30-162            | Infrared reflow     | Package peak temperature: 230°C, Time: 30 seconds max. (210°C min.), Number of times: 1, Number of days*: 2 (after this, prebaking is necessary at 125°C for 16 hours) |

| VP15-162            | VPS                 | Package peak temperature: 215°C, Time: 40 seconds max. (200°C min.), Number of times: 1, Number of days*: 2 (after this, prebaking is necessary at 125°C for 16 hours) |

| WS60-162            | Wave soldering      | Soldering oven temperature: 260°C max., Time: 10 seconds max., Number of times: 1, Number of days*: 2 (after this, prebaking is necessary at 125°C for 16 hours)       |

| Pin partial heating | Pin partial heating | Pin temperature: 300°C max., Time: 10 seconds max.                                                                                                                     |

<sup>\*:</sup> The number of days the device can be stored after the dry pack has been opened. The storing conditions are 25°C, 65% RH max.

$Note: \quad \text{Do not use two or more soldering methods in combination (except for the pin partial heating method)}.$

Remarks: For details of the recommended soldering conditions, refer to "Semiconductor Device Mounting Manual" (IEI-616).

## APPENDIX DEVELOPMENT TOOLS

The following development tools are readily available to support the development of the  $\mu$ PD17P005 program:

#### Hardware

| NAME                | OUTLINE                                                                                                                                                                                                                                                                         | ORDERCODE                             |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|                     | This in-circuit emulator is used in common with the 17K series products. When developing the program of $\mu$ PD17P005, a system evaluation board (SE board) is used in combination with the in-circuit emulator.                                                               | 15.474                                |

| In-circuit Emulator | The in-circuit emulator operates with a RAM base. By connecting it to a console, the program can be added to and edited on the console. In addition, more sophisticated program development environments can be created by using the support software SIMPLEHOST <sup>M</sup> . | IE-17K<br>IE-17K-ET*                  |

| SE board            | Used to evaluate the system of $\mu$ PD17P005 in stand-alone mode, or in combination with the in-circuit emulator.                                                                                                                                                              | SE-17010                              |

| Emulation Probe     | Connects the SE board to the target system.                                                                                                                                                                                                                                     | EP-17003GF                            |

| Conversion socket   | Connects to the target system in combination with the emulation probe.                                                                                                                                                                                                          | EV-9200G-80                           |

| PROM programmer     | The PROM of the $\mu$ PD17P005 can be programmed by using a dedicated program adapter AF-9803.                                                                                                                                                                                  | AF-9703<br>AF-9704<br>(Ando Electric) |

| Program adapter     | Used in combination with the PROM programmer.                                                                                                                                                                                                                                   | AF-9803<br>(Ando Electric)            |

Remarks: For the details of the PROM programmer and program adapter, consult Ando Electric.

### **Software**

| NAME                                                                                      | OUTLINE                                                                                           | HOSTMACHINE                    | os                               | SUPPLY MEDIA        | ORDERCODE            |             |               |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------|---------------------|----------------------|-------------|---------------|

| 17K series                                                                                | AS17K is an assembler that can be                                                                 |                                | MS-DOS <sup>™</sup>              | 5"2HD               | μS5A10AS17K          |             |               |

| assembler                                                                                 | ssembler used in common with the 17K series products. When developing the                         |                                | (Ver.3.1toVer.3.30C)             | 3.5*2HD             | μS5A13AS17K          |             |               |

| program of the $\mu$ PD17P005, AS17K is used in combination with a device file (AS17005). |                                                                                                   | IBM PC/AT™                     | PCDOS <sup>™</sup><br>(Ver. 3.1) | 5"2HC               | μS7B10AS17K          |             |               |

| Device file                                                                               | AS17005 is a device file for μPD17005                                                             |                                | MS-DOS                           | 5*2HD               | μS5A10AS17005        |             |               |

| (AS17005)                                                                                 | (AS17005) and μPD17P005, and is used in combination with an assembler for the 17K series (AS17K). | 1                              | ,                                | Ma                  | (Ver.3.1toVer.3.30C) | 3.5*2HD     | μS5A13AS17005 |