#### 1. General Decription

The UM82C231 is a system/memory controller. It performs the CPU interface, AT system bus interface and memory interface functions.

#### 2. Features

- CPU interface and bus control.

- PC/AT expansion bus interface.

- · Clock generation.

- Numericl processor 80287 interface.

- Peripheral chip interface.

- Refresh and DMA logic.

- Reset and shut down logic.

- Supports 64K > 256K and 1M DRAM

- Supports up to 4M Bytes on board memory.

- Advanced 1.2 µ m CMOS technology.

- TTL compatible inputs.

- 136 pin flat package.

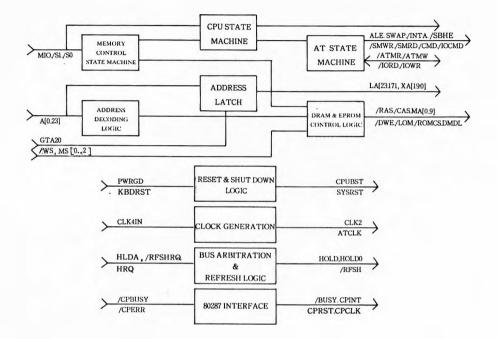

## 3. UM82C231 Block Diagram

÷

ŧ

.

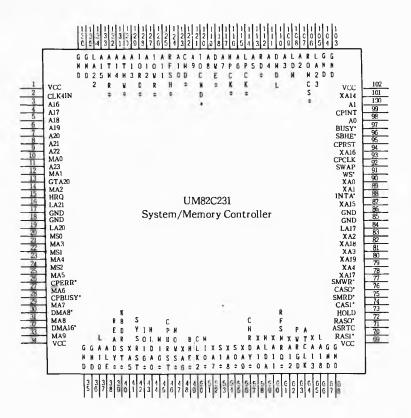

## 4.UM82C231 Pin Configuration

## 5.82C231 Pin Description

| Pin Name. | Pin Type | Pin No.                                                                                                                  | Description                                                                                                                                                                                                 |

|-----------|----------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A(23:0)   | I        | 11,9,8, 7,6,<br>5,4, 3,133,<br>131, 129,<br>127, 125,<br>123, 121,<br>119, 117,<br>115, 113,<br>111, 109,<br>107,100,98, | Local address lines from CPU; A(23:17)<br>also connected to 82C206 to represent<br>the DMA page address during DMA<br>cycles.                                                                               |

| LA(23:17) | В        | 105,134, 16,<br>19,37, 66,84                                                                                             | AT bus unlatched address bus Bit 23 -<br>Bit 17; These pins are outputs during<br>CPU or DMA cycles and become inputs<br>during REFRESH or MASTER cycles.<br>They have 24 ma current sinking<br>cabability. |

| XA(19:17) | TO       | 80,82,78                                                                                                                 | AT bus latched address bus Bit 19 - Bit<br>17. They are activated during CPU and<br>DMA cycles; tri-stated otherwise.                                                                                       |

| XA(16:1)  | В        | 94, 87, 101,<br>65, 62, 60,<br>58, 56, 54,<br>52, 48, 41,<br>79,81,83, 89                                                | AT bus latched address bus Bit 16; It is<br>an output pin for CPU or REFRESH<br>cycles and becomes input during DMA<br>or MASTER cycles. XA15 and XA14<br>have 24 ma current. sinking capability.           |

| XA0       | В        | 90                                                                                                                       | AT bus latched address bus Bit 0; It is an<br>output pin for CPU, REFRESH or 16-bit<br>DMA cycles and becomes input during<br>8-bit DMA or MASTER cycles.                                                   |

| GTA20     | Ι        | 13                                                                                                                       | AT bus unlatched address bit 20 enable<br>control; the logic low of this signal will<br>force LA20 stay low during CPU cycles.                                                                              |

| Pin Name. | Pin Type | Pin No. | Description                                                                                                                           |  |  |

|-----------|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| M-I/O     | Ι        | 51      | Memory or I/O cycle status signal from CPU.                                                                                           |  |  |

| BHE*      | Ι        | 49      | Byte high enable signal from CPU to<br>indicate that high byte accessing is<br>required for the current cycle.                        |  |  |

| SBHE*     | В        | 96      | System Byte high enable to AT bus<br>through buffer; it is output normally<br>and becomes input when MASTER has<br>the AT bus.        |  |  |

| CLK4IN    | Ι        | 2       | OSC. input; divided by two to derive<br>CPU CLK2. This signal is also used to<br>control DRAM access timing.                          |  |  |

| CLK2      | 0        | 50      | OSC. output; used as the CPU CLK2 source.                                                                                             |  |  |

| ATCLK     | 0        | 64      | AT system clock connected to AT bus<br>through buffer. This clock output<br>synchronized with CLK2 and generated<br>from CLK4IN/6.    |  |  |

| SO*       | Ι        | 55      | CPU status line 0; normally it indicates that the current cycle is write cycle.                                                       |  |  |

| S1*       | Ι        | 53      | CPU status line 1; normally it indicates that the current cycle is read cycle.                                                        |  |  |

| INTA*     | 1        | 88      | Interrupt acknowledge cycle indication;<br>when S0*, S1* and M-I/O are monitored<br>low, this signal will be activated.               |  |  |

| READY*    | 0        | 39      | CPU ready signal; CPU samples this<br>signal at the end of every Tc state. The<br>current cycle will be terminated if<br>sampled low. |  |  |

| HLDA      | Ι        | 59      | Hold acknowledge input from CPU;<br>CPU will relinquish the local buses<br>when this signal is active.                                |  |  |

| Pin Name. F | in Type | Pin No. | Description .                                                                                                                                                                                                                                   |  |  |  |

|-------------|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| HRQ         | I       | 15      | DMA or MASTER cycle request from 82C206.                                                                                                                                                                                                        |  |  |  |

| RFSHRQ*     | Ι       | 61      | Refresh request signal from 82C206's timer 1 output. normally this signal is activated around 15.6 micro second.                                                                                                                                |  |  |  |

| HOLD        | 0       | 73      | Hold request to CPU; either HRQ or RFSHRQ* is arbitrated. Hold will be generated to ask for the buses.                                                                                                                                          |  |  |  |

| HLDAO       | 0       | 44      | DMA or MASTER cycle acknowledge signal<br>to 82C206; if HRQ is arbitrated and CPU<br>relinquishes the buses, HLDAO is activated<br>to notice that the DMA controller or<br>MASTER can issue the control signals to<br>perfrom the transactions. |  |  |  |

| RFSH*       | В       | 124     | Refresh cycle indication; it is an output pir<br>normally and become input pin during<br>MASTER cycles.                                                                                                                                         |  |  |  |

| PWRGD       | Ι       | 63      | Power good or bad indication; if this signal<br>is low, the system will stay at the reset<br>condition.                                                                                                                                         |  |  |  |

| KBDRST*     | Ι       | 40      | CPU reset request from keyboard controller;<br>when detect a low pulse of this signal,<br>82C231 will reset CPU.                                                                                                                                |  |  |  |

| CPURST      | 0       | 46      | CPU reset; for both PWRGD and KBDRST* are low, CPURST will be activated.                                                                                                                                                                        |  |  |  |

| SYSRST      | 0       | 42      | System reset; for PWRGD is low Sysrst will be activated.                                                                                                                                                                                        |  |  |  |

| CPBUSY*     | Ι       | 28      | Co-processor busy signal; which indicates co-processor is accessed.                                                                                                                                                                             |  |  |  |

| Pin Name. | Pin Type | Pin No. | Description                                                                                                                                                               |  |  |  |

|-----------|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CPERR*    | Ι        | 26      | Co-processor error signal; indicates co-processor's accessing has error.                                                                                                  |  |  |  |

| BUSY*     | 0        | 97      | Busy signal to CPU; which indicates that co-processor is busy or has error.                                                                                               |  |  |  |

| CPINT     | 0        | 99      | Co-processor interrupt; which indicates<br>that the co-processor has error and the<br>system software has to do somthing.                                                 |  |  |  |

| CPRST     | 0        | 95      | Co-processor reset; a system reset or<br>write to IO address F1 hex will trigge<br>this signal active.                                                                    |  |  |  |

| CPCLK     | 0        | 93      | CLK4IN/3 clock output has 33% duty cycle.                                                                                                                                 |  |  |  |

| DMA8*     | I        | 30      | 8-bit DMA cycle indication.                                                                                                                                               |  |  |  |

| DMA16*    | I        | 32      | 16-bit DMA cycle indication.                                                                                                                                              |  |  |  |

| CHRDY*    | Ι        | 57      | Channel ready signal from AT bus;<br>82C231 monitors this signal to<br>determine that if the accessed device<br>requires more wait states to complete<br>the transaction. |  |  |  |

| NOWS*     | I        | 47      | No wait state signal from AT bus;<br>82C231 monitors this signal to<br>terminate the current AT cycle<br>immediately.                                                     |  |  |  |

| M16*      | Ι        | 45      | Memory data size 16-bit signal from AT<br>bus; 82C231 monitors this signal to<br>determine the memory slave's data size.                                                  |  |  |  |

| IO16*     | I        | 43      | IO data size 16-bit signal from AT bus;<br>82C231 monitors this signal to determine<br>the IO slave's data size.                                                          |  |  |  |

| ALE       | 0        | 38      | AT bus address latch enable; 82C231 issues this signal to start the AT cycle.                                                                                             |  |  |  |

| Pin Name. | Pin Type | Pin No. | Description                                                                                                                                                                        |  |  |  |

|-----------|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RAS*(1:0) | 0        | 70,72   | Row address strobes for the local memory; used as bank select.                                                                                                                     |  |  |  |

| CAS*(1:0) | 0        | 74,76   | Column address strobe for the local memory; used as byte enable.                                                                                                                   |  |  |  |

| DWE*      | Ο        | 118     | DRAM write or read control signal.                                                                                                                                                 |  |  |  |

| ROMCS*    | 0        | 106     | BIOS ROM output enable; this signal is<br>activated when the BIOS area either<br>from 0E0000-0FFFFF or FE0000<br>FFFFFF address range is accessed.                                 |  |  |  |

| RD*       | 0        | 112     | Read cycle status signal for CPU, DMA<br>or MASTER cycle; either IO or memory<br>read in CPU or MASTER cycle, and the<br>the memory read in DMA cycle this<br>signal is activated. |  |  |  |

| DMDL      | 0        | 110     | Local DRAM read data latch enable;<br>this signal is used to latch the data and<br>parity bits read from local DRAM by<br>the 82C232.                                              |  |  |  |

| HPCK*     | 0        | 116     | High byte parity checking enable;<br>82C231 issues this signal if to check high<br>byte read data is required.                                                                     |  |  |  |

| LPCK*     | 0        | 114     | Low byte parity checking enable;<br>82C231 issues this signal if to check low<br>byte read data is required.                                                                       |  |  |  |

| LDM*      | 0        | 108     | Local DRAM accessed indication; when<br>local DRAM is accessed by the bus<br>controllers, 82C231 enables this signal.                                                              |  |  |  |

| ASRTC     | 0        | 71      | Read Time clock address strobe.                                                                                                                                                    |  |  |  |

| WS*       | Ι        | 91      | Local DRAM wait state control; a low input, 82C231 will insert one wait state.                                                                                                     |  |  |  |

| Pin Name. | Pin Type | Pin No.                                    | Description                                                                                                                                                                                 |

|-----------|----------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATMW*     | В        | 130                                        | AT bus memory write command signal;<br>it is an output pin during CPU cycle and<br>becomes input during DMA and<br>MASTER cycles.                                                           |

| ATMR*     | В        | 132                                        | AT bus memory read command signal;<br>it is an output pin during CPU and<br>REFRESH cycle and becomes input<br>during DMA and MASTER cycles.                                                |

| SMWR*     | 0        | 77                                         | AT bus memory write command signal<br>when the memory access address is<br>below one mega byte.                                                                                             |

| SMRD*     | 0        | 75                                         | AT bus memory read command signal<br>when the memory access address is<br>below one mega byte.                                                                                              |

| IOWR*     | В        | 126                                        | AT bus IO write command signal; it is<br>an output pin during CPU cycle and<br>becomes input during DMA and<br>MASTER cycles.                                                               |

| IORD*     | В        | 128                                        | AT bus IO read command signal; it is an<br>output pin during CPU cycle and<br>becomes input during DMA and<br>MASTER cycles.                                                                |

| SWAP      | 0        | 92                                         | High byte data and low byte data<br>swapping control signal; the 82C231<br>monitors the transaction data size and<br>the slave device's data width, then<br>enable this signal if required. |

| CMD*      | 0        | 122                                        | Command signal; for every AT cycle's read or write cycle this signal will be active and has the same timing as read or write command.                                                       |

| IOCMD*    | 0        | 120                                        | IO command signal; for every AT IO<br>cycle's read or write cycle this signal<br>will be active.                                                                                            |

| MA(9: 0)  | 0        | 33, 31, 29,<br>27, 25, 23,<br>21,14,12, 10 | Multiplexed DRAM row and column address for the local memory                                                                                                                                |

| Pin Name. | Pin Type | Pin No.                                              | Description                             |

|-----------|----------|------------------------------------------------------|-----------------------------------------|

| MS(2:0)   | Ι        | 24,22,20                                             | Local DRAM memory configuration select. |

| VCC       |          | 1,34,69 102                                          |                                         |

| GND       |          | 17,18,35 36,<br>67,68 85,86,<br>103, 104,<br>135 136 |                                         |

| Total Pin |          | 136                                                  |                                         |

#### 6. Functional Description

The UM82C231 Bus & Memory Controller consists of the following functional sub-modules:

- \* Reset and Shut Down Logic.

- \* Clock Generation.

- \* CPU State Machine, AT Bus State Machine and Memory Control State Machine.

- \* Bus Abitration Logic, DMA/Master and Refresh Logic.

- \* Numeric Processor Interface.

- \* System Control Logic.

- \* Address Decoding Logic.

- \* DRAM & EPROM Control Logic.

#### Overview

The UM82C231 performs the CPU interface, AT system bus interface and the memory control functions. The various functional modules are discussed in this section.

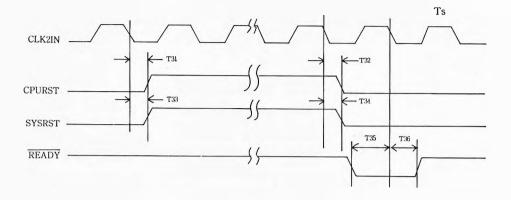

#### 6.1 Reset and Shut Down Logic

Two reset inputs PWRGD and KBDRST# are provided on the UM82C231 chip. PWRGD is the Power Good signal from the power supply. When PWRGD is low, the UM82C231 asserts CPURST for CPU reset and SYSRST for system reset. KBDRST# is generated from the 8042 keyboard controller when a CPU reset is required. CPURST is also activated by the UM82C231 when a shut down condition is detected from CPU status. Both CPURST and SYSRST are asserted for at least 16 CLK2 cycles and are synchronized with respect to CLK2 to meet the setup and hold time requirements of the 80286 CPU.

#### 6.2 Clock Generation

The UM82C231 provides two synchronous clocks CLK2 and ATCLK for the system. There is only one input clock CLK4IN, driven from a TTL crystal oscillator, running at twice of the CPU clock frequency. ATCLK is also derived from CLK4IN at 1/3 of the CPU clock frequency.

#### 6.3 CPU, AT Bus and Memory Control State Machine.

In order to achieve maximum performance of the 80286 CPU and maintain 100% IBM PC/AT compatibity, it is desirable to run the local memory at the rated maximum CPU frequency and the AT bus at a slower clock frequency. The two state machines still maintain a synchronous protocol.

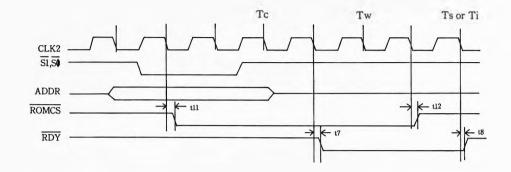

#### 6.31 CPU State Machine

Interface to the 80286 requires interpretation of the status lines S0#, S1# and M-I/O from CPU during phase 1 of TS and generation of READY# during TC to the CPU upon completion of the cycle. A(23:0) will be latched during phase 2 of TS for internal use. Address Decoding Logic then activates Memory Control State Machine for a local memory cycle or AT State Machine for AT cycle. Either State Machine terminates itself and CPU State machine upon completion of its function. READY# will be sent out to the 80286 CPU to finish the cycle.

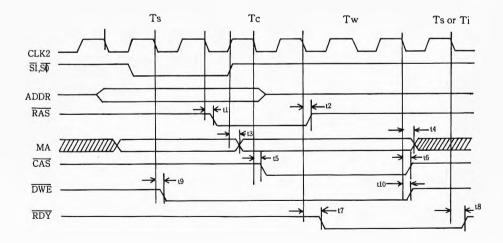

#### 6.3.2 AT Bus State Machine

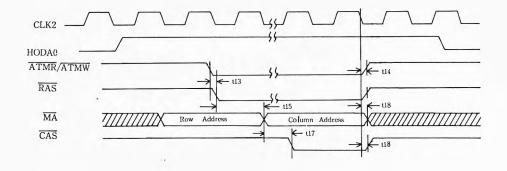

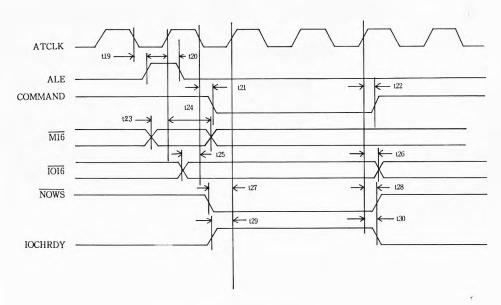

The At Bus State Machine gains control when Address Decoding Logic decodes a non-local memory cycle. It uses BCLK which is twice the frequency of AT system clock ATCLK, it also performs the necessary synchronization of control and status signals between the AT bus and the processor. The UM82C231 supports 8 and 16 bit memory or I/O devices located on the AT bus.

AT bus cycle is initiated by asserting ALE in AT-TS 1 state. On the trailing edge of ALE, M16# is sampled for a memory cycle to determine the bus size.

It then enters AT-TC state and provides the command signal. For an I/O cycle, IO16\* is sampled after the trailing edge of ALE till the end of the command. Typically, the wait state for an AT 8/16 bit transaction is 5/3 respectively. The command cycle is extended when CHRDY is detected inactive, or is terminated when zero wait state request signal NOW# from AT bus is active. Upon expiration of the wait states, AT State Machine terminates itself and passes internal READY to CPU State Machine for outputting synchronous READY# to the 80286.

#### 6.3.3 Memory Control State Machine

Address Decoding Logic activates Memory Control State Machine when local memory is to be accessed. Memory Control State Machine initiates memory interfacing signals by adapting the configuration strap pin MS(2:0) and information from Address Decoding Logic. The definitions of MS(2:0) are given in the following table.

| MS2 | MS2 | MS0 | Bank0     | Bankl | Total Memory |

|-----|-----|-----|-----------|-------|--------------|

| 0   | 0   | 0   | 256k      | -     | 512k         |

| 0   | 0   | 1   | 256k      | 64k   | 640k         |

| 0   | 1   | 0   | 256k      | 256k  | 1Meg         |

| 0   | 1   | 1   | 1M        |       | 2Meg         |

| 1   | 1   | 1   | 1M        | 1M    | 4Meg         |

| 1   | 0   | Х   | Not Valid |       |              |

| 1   | 1   | 0   | Not Valid |       |              |

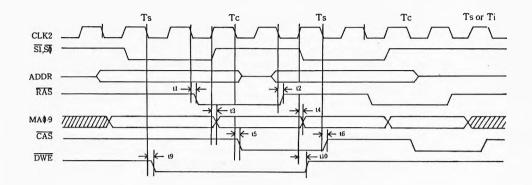

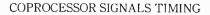

#### 6.4 Bus Arbitration Logic, DMA/Master and Refresh Logic

The UM82C231 provides arbitration between the CPU, DRAM refresh logic and DMA/Master devices. It handles HRQ and RESHRQ by generating HOLD request to the CPU. CPU will respond to an active HOLD signal by asserting HLDA and placing most of its output and I/O pins in a high impedance state after completing its current bus cycle. After the CPU relinquishes the bus, the UM82C231 responds by issuing RFSH# or HLDA0 depending on the requesting device.

The arbitration between Refresh and DMA/Master is based on FIFO or first come first serve. However, RFSHRQ will be internally latched and served immediately after DMA/Master finishes its request if RFSHRQ is queued behind HRQ. HRQ has to remain active to be served if RFSHRQ comes first.

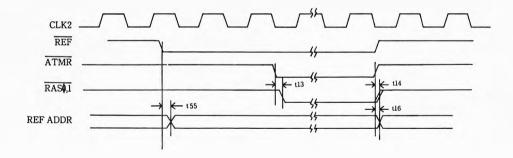

During a refresh cycle, refresh address is put out on XA0-XA9 and MA0-MA9 address lines, RFSH# and LDM# are asserted, SMRD# is active 2 SYSCLK after RFSH# is active and RAS#(1:0) are asserted to refresh DRAMS accordingly.

DMA and Bus Master share the same request pin HRQ. After the UM82C231 receives HRQ it asserts HOLD request to the CPU. Upon finishing the current cycle, the CPU relinquishes the bus by asserting HLDA. The UM82C231 issues HLDAO to the requesting device to start gaining control of the bus. During an active HLDAO period the only way to distinguish between DMA and Bus Master request is to monitor the DMA8# and DMA16# signals. DMA8#/DMA16# active indicates an 8-bit/16bit DMA transfer, while both inactive means a Master cycle.

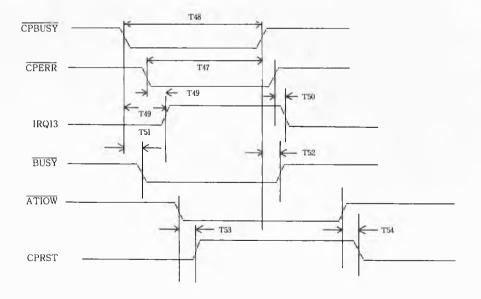

#### 6.5 Numeric Processor Interface

Incorporated in the UM82C231 is the circuitry to interface an 80287 Numeric Coprocessor to 80286. The circuitry handles the decoding required for selecting and resetting the Numeric Coprocessor, handling CPBUSY# and CPERR# signals from the 80287 to the CPU, and generating interrupt signals for error handling.

While executing a task, the 80287 issues a CPBUSY# signal to the UM82C231 and is passed to the CPU as BUSY#. If during this busy period, a numeric coprocessor error CPERR# occurs it results in an internal latching of the BUSY# output and assertion of IRQ13 for a NP exception request. Latched BUSY# stays active until cleared by an I/O write cycle to address 0F0H or 0F1H. IRQ13 is cleared only when CPERR# from 80287. The 80287 is reset through the CPRST output, which can be activated by a system reset or by performing a write operation to I/O port 0F1H.

The 80287 can operate either directly from the CPU clock or with a 33% duty cycle 1/3 the frequency of the CPU clock. The UM82C231 provides both clock, CLK2 and CPCLK, to the 80287.

#### 6.6 System Control Logic

The UM82C231 activates bus swapping control signal SWAP to the UM82C232 to guide the data bus flow during AT bus accessing and high low data byte swapping is required. Other control signals ALE, ATMW#, ATMW#, ATMR#, SMWR#, SMRD#, IOWR#, IORD#, CMD#, IOCMD# and RD# are provided for AT bus interfacing and controlling.

#### 6.7 DRAM & EPROM Control Logic

The DRAM and EPROM control logic in the UM82C231 is responsible for the generation of the RAS#, CAS# and DWE# signals for DRAM accessed and ROMCS# for EPROM accesses. This sub-module also generates READY# to the CPU upon completion of the desired local memory operation. The appropriate number of wait states are inserted, as programmed by strap pins externally.

## 7. Electrical Characteristics (Vcc=4.75~5.25V, TA=0°C-70°C)

## 7.1 DC Characteristics

| Parameters                   | Symbol | Min. | Max. | Units |

|------------------------------|--------|------|------|-------|

| Input Low Voltage            | Vil    | -    | 0.8  | V     |

| Input High Voltage           | Vih    | 2.0  | •    | v     |

| Output Low Voltage           | Vol    | •    | 0.45 | V     |

| Output High Voltage          | Voh    | 2.4V | -    | v     |

| Input Current                | Iil    | •    | +-10 | ua    |

| Power Supply Current         | Icc    | -    | 100- | ma    |

| Output High-Z Current        | Ioz    | •    | +-10 | ua    |

| Standby Power Supply Current | Iccsb  | •    | 1    | ma    |

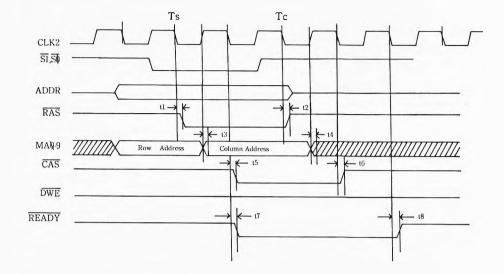

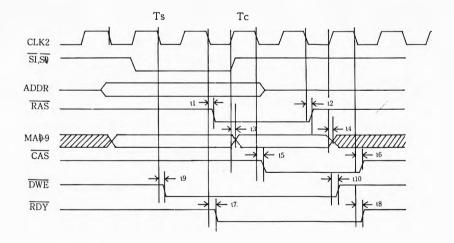

## 72 AC Characteristics

| Symbol | Description                                               | MIN | ТҮР | MAX | UNIT |

|--------|-----------------------------------------------------------|-----|-----|-----|------|

| tl     | RAS active from CLK2 ↓                                    | 8   | 14  | 19  | ns   |

| t2     | RAS inactive from CLK2 ↓                                  | 10  | 19  | 25  | ns   |

| t3     | Column address valid from CLK2 †                          | 8   | 15  | 20  | ns   |

| t4     | Column address invalid from CLK2 †                        | 9   | 18  | 24  | ns   |

| t5     | CAS active from CLK2 ↓                                    | 8   | 14  | 19  | ns   |

| t6     | CAS inactive from CLK2 ↓                                  | 10  | 19  | 25  | ns   |

| t7     | RDY active from CLK2 ↓                                    | 11  | 20  | 30  | ns   |

| t8     | RDY inactive from CLK2↓                                   | 13  | 22  | 32  | ns   |

| t9     | WE active from CLK2 ↓                                     | 8   | 15  | 20  | ns   |

| t10    | WE inactive from CLK2 ↑                                   | 9   | 16  | 21  | ns   |

| t11    | ROMCS active from CLK2↓                                   | 8   | 15  | 20  | ns   |

| t12    | ROMCS inactive from CLK2↓                                 | 9   | 16  | 21  | ns   |

| t13    | RAS active from ATMR ↓                                    | 6   | 10  | 17  | ns   |

| t14    | RAS inactive from ATMR †                                  | 7   | 12  | 19  | ns   |

| t15    | ROW address hold time from $\overline{RAS}\downarrow$     |     | 1   |     | CLK2 |

| t16    | Column address hold time from ATMR †                      | 6 . | 10  | 17  | ns   |

| t17    | Column address setup time from $\overline{CAS}\downarrow$ | 0.5 |     | 1   | CLK2 |

| t18    | CAS inactive from ATMR †                                  | 6   | 10  | 17  | ns   |

| Symbol | Description                         | MIN | TYP | MAX | UNIT |

|--------|-------------------------------------|-----|-----|-----|------|

| t19    | ALE active delay from ATCLK ↓       | 0   | 4   | 8   | ns   |

| t20    | ALE inactive delay from ATCLK ↓     | 0   | 4   | 8   | ns   |

| t21    | COMMAND active delay from ATCLK↓    | 0   | 4   | 8   | ns   |

| t22    | COMMAND inactive delay from ATCLK ↓ | 0   | 4   | 8   | ns   |

| t23    | M16 set-up time to ATCLK↑           | 10  |     |     | ns   |

| t24    | M16 hold time to ATCLK †            | 4   |     |     | ns   |

| t25    | 1016 set-up time to ATCLK ↓         | 10  |     |     | ns   |

| t26    | 1016 hold time to ATCLK ↓           | 8   |     |     | ns   |

| t27    | NOWS set-yp time to ATCLK ↑         | 8   |     |     | ns   |

| t28    | NOWS hold time to ATCLK ↑           | 10  |     |     | ns   |

| t29    | IOCHROY set-yp time to ATCLK ↑      | 10  |     |     | ns   |

| t30    | IOCHROY hold time to ATCLK †        | 4   | 6   | 12  | ns   |

| t31    | CPURST active delay from CLK20 ↓    | 2   | 6   | 16  | ns   |

| t32    | CPURST inactive delay from CLK20↓   | 2   | 6   | 12  | ns   |

| t33    | SYSRST active delay from CLK20 ↓    | 2   | 6   | 16  | ns   |

| t34    | SYSRST inactive delay from CLK20 ↓  | 2   |     |     | ns   |

| t35    | READY input set up from CLK20 ↓     | 12  |     |     | ns   |

| t36    | READY input hold from CLK20 \$      | 8   |     |     | ns   |

| t37    | HOLD active delay from ATCLK †      | 2   | 4   | 8   | ns   |

. .

| Symbol      | Description                           | MIN | ТҮР | MAX | UNIT |

|-------------|---------------------------------------|-----|-----|-----|------|

| t38         | HOLD inactive delay from ATCLK ↓      | 2   | 4   | 8   | ns   |

| t39         | RFSH delay from HLDAI                 | 3   | 7   | 14  | ns   |

| t40         | RFSH inactive delsy from ATCLK ↑      | 2   | 4   | 8   | ns   |

| t41         | ATMR active delay from ATCLK †        | 1   | 5   | 9   | ns   |

| t42         | ATMR inactive delay from ATCLK ↓      | 2   | 4   | 6   | ns   |

| t43         | HRQ set-yp time to ATCLK ↑            | 10  |     |     | ns   |

| t44         | HRQ hold time to ATCLK †              | 4   |     |     | ns   |

| t45         | HLDAO active delay from HLDAI         | 5   | 9   | 18  | ns   |

| t46         | HLDAO inactive delay from HLDAI       | 5   | 10  | 20  | ns   |

| t47         | overlap of CPBUSY & CPERR             | 8   |     |     | ns   |

| t48         | CPBUSY active pulse                   | 12  |     |     | ns   |

| t49         | IRQ13 active delay from CPBUSY, CPERR | 7   | 12  | 16  | ns   |

| <b>t</b> 50 | IRQ13 inactive delay from CPERR       | 3   | 7   | 11  | ns   |

| t51         | BUSY active delay from CPBUSY ↓       | 4   | 8   | 16  | ns   |

| t52         | BUSY inactive delay from CPBUSY ↑     | 4   | 8   | 16  | ns   |

| t53         | CPRST active delay from ATIOW ↓       | 2   | 5   | 10  | ns   |

| t54         | CPRST inactive delay from ATIOW 1     | 2   | 5   | 10  | ns   |

| t55         | REFRESH address valid from REF ↓      | 7   | 10  | 15  | ns   |

Read after Write 0 W.S.

1 W.S. Read/Write

Refresh Cycle

AT BUS TIMING

#### ARBITRATION SIGNALS' TIMING

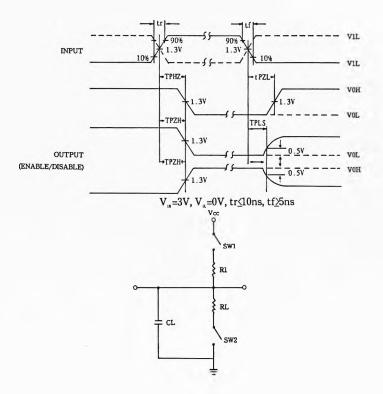

#### 7.3 Testing Conditions

#### Load Circuit Measurerrient Conditions

| Parameter                    | Output Type                            | Symbol                               | CL(pF) | Rt(Ω) | RL(Ω) | SW1       | SW2      |

|------------------------------|----------------------------------------|--------------------------------------|--------|-------|-------|-----------|----------|

| Propagation<br>Delay<br>Time | Totem pole<br>3-state<br>Bidirectional | t <sub>PDI</sub><br>t <sub>PIL</sub> | 50     |       | 1.0K  | OFF       | ON       |

| Propagation<br>Delay Time    | Open drain or<br>Open Collector        | t <sub>ela</sub><br>t <sub>ell</sub> | 50     | 0.5K  | _     | ON        | OFF      |

| Disable<br>Time              | 3-state<br>Bidirectional               | t <sub>nz</sub><br>t <sub>ne</sub>   | 5      | 0.5K  | 1.0K  | ON<br>OFF | ON       |

| Enable<br>Time               | 3-state<br>Bidirectional               | t <sub>PZ</sub><br>t <sub>M2</sub>   | 50     | _     | 1.0K  | ON<br>OFF | ON<br>ON |