### **UM74HCT646**

# Octal Bus Transceiver and Register

#### **Features**

- 8 bi-directional data bus

- Transmits real-time data or stored data in either direction

- 3-state outputs with driving capability for direct bus interface

- Low power consumption with function, pin-out, speed and drive compatibility with 74LS logic family and interfaces directly with TTL, NMOS and CMOS devices

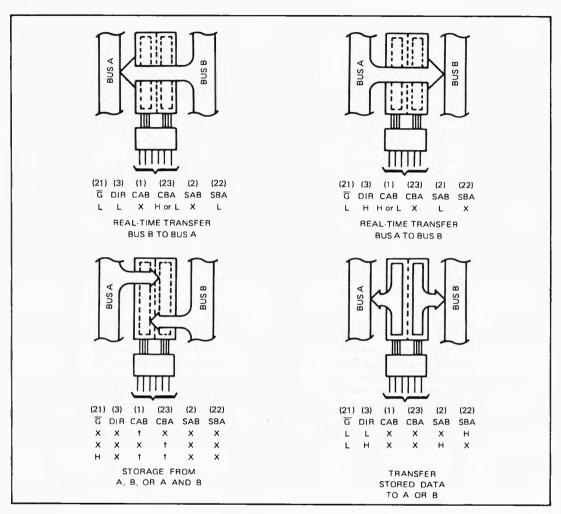

Data on the A or B bus will be clocked into the registers

on the low-to-high transition of the appropriate clock pin

(CAB or CBA). The examples demonstrate the four fund-

amental bus-management functions that can be performed

with the octal bus transceivers and registers.

Available in 24 lead DIP

### General Description

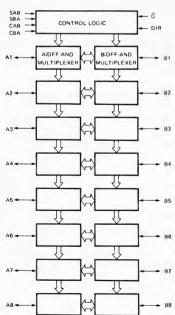

The UM74HCT646, fabricated using the UMC silicon gate CMOS process, is a bi-directional bus transceiver with D-type flip-flops and control circuitry arranged for multiplexed transmission of data directly from the input bus or from the internal registers.

### Pin Configuration Block Diagram

### Absolute Maximum Ratings\*

##

### \*Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **D.C. Electrical Characteristics** ( $V_{CC} = 5V$ , $T_A = 25^{\circ}C$ unless otherwise specified)

| Symbol          | Parameter                                          | Min. | Тур. | Max. | Unit | Condition                                            |

|-----------------|----------------------------------------------------|------|------|------|------|------------------------------------------------------|

| V <sub>CC</sub> | Power Supply Voltage                               | 4.5  | 5.0  | 5.5  | V    |                                                      |

| VIH             | High-Level Input Voltage                           | 2.0  | _    | _    | V    |                                                      |

| VIL             | Low-Level Input Voltage                            | -    | 0.5  | 0.8  | V    |                                                      |

| I <sub>I</sub>  | Input Current<br>(all except I/O pins)             | -    | 0.01 | 0.1  | μА   | V <sub>1</sub> = 0∨ ~ 5∨                             |

|                 | High-Level Output Voltage                          | 4.8  | -    | _    | V    | OH   = 20 μA                                         |

| V <sub>OH</sub> | riigh-Level Output Voltage                         | 3.0  | _    | _    | V    | I I <sub>OH</sub> I = Max                            |

|                 | Low-Level Output Voltage                           | _    | -    | 0.1  | V    | I <sub>OL</sub> = 20 μA                              |

| VoL             | Low-Level Output Voltage                           | -    | -    | 0.5  | V    | I <sub>OL</sub> = 24 mA                              |

| loz             | 3-state Leakage Current<br>When Output is Disabled | _    | -    | 0.5  | μΑ   | V <sub>O</sub> = 0 ~ 5∨                              |

| l <sub>CC</sub> | Quiescent Supply Current                           | _    | -    | 8    | μΑ   | V <sub>IN</sub> = 0U or V <sub>CC</sub> with No Load |

### **AC Characteristics** (Input $t_r$ , $t_f \le 2 \text{ ns}$ )

| S hal            | Parameter                                                       | 0                                               | dition <sup>†</sup>    | T <sub>A</sub> = 25°C, V <sub>CC</sub> = 5.0V |      |      |       |

|------------------|-----------------------------------------------------------------|-------------------------------------------------|------------------------|-----------------------------------------------|------|------|-------|

| Symbol           | rarameter                                                       | Condition                                       |                        | Min.                                          | Тур. | Max. | Unit  |

| f <sub>max</sub> | Maximum Clock Frequency                                         | C <sub>L</sub> = 50 pF                          |                        | 30                                            | 45   | -    | MHz   |

| t <sub>PLH</sub> | Maximum Propagation Delay,                                      | $C_L = 50 pF$                                   |                        | _                                             | 12   | 25   | ns    |

| t <sub>PHL</sub> | A or B Input to B or A Output                                   | C <sub>L</sub> = 50 pF                          |                        | _                                             | 12   | 25   |       |

| t <sub>PLH</sub> | Maximum Propagation Delay,<br>CBA or CAB Input to               | C <sub>L</sub> = 50 pF                          |                        | _                                             | 16   | 35   | ns    |

| t <sub>PHL</sub> | A or B Output                                                   | C <sub>L</sub> = 50 pF                          |                        | _                                             | 16   | 35   |       |

| t <sub>PLH</sub> | Maximum Propagation Delay,<br>SBA or SAB Input to A or B Output | C <sub>L</sub> = 50 pF                          |                        | _                                             | 16   | 35   |       |

| t <sub>PHL</sub> | (with A or B High)                                              | C <sub>L</sub> = 50 pF                          |                        | -                                             | 16   | 35   | ns    |

| t <sub>PLH</sub> | Maximum Propagation Delay,<br>SBA or SAB Input to A or B Output | C <sub>L</sub> = 50 pF                          |                        | _                                             | 16   | 35   | 200   |

| t <sub>PHL</sub> | (with A or B High)                                              | C <sub>L</sub> = 50 pF                          |                        | -                                             | 16   | 35   | ns    |

| t <sub>PZL</sub> | Maximum Output Enable Time,                                     | R <sub>L</sub> = 1 kΩ                           | C <sub>L</sub> = 50 pF | -                                             | 20   | 45   | ns    |

| t <sub>PZH</sub> | G or DIR Input to A or B Output                                 |                                                 | C <sub>L</sub> = 50 pF | _                                             | 20   | 45   | 1 115 |

| t <sub>PHZ</sub> | Maximum Output Disable Time,                                    | R <sub>L</sub> = 1 kΩ<br>C <sub>L</sub> = 50 pF |                        | -                                             | 20   | 45   | D.C.  |

| t <sub>PLZ</sub> | G or DIR Input to A or B Output                                 |                                                 |                        | _                                             | 20   | 45   | ns    |

| tw               | Pulse Duration, Clock<br>High or Low                            |                                                 |                        | 12                                            | -    | -    | ns    |

| t <sub>SU</sub>  | Setup Time, A before CAB ↑ or B before CAB ↑                    |                                                 |                        | 15                                            | _    | -    | ns    |

#### Pin Description

| Symbol  | Description                                                                                                      |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| A1 ~ A8 | Bi-directional data bus and register input                                                                       |  |  |  |  |  |

| B1 ~ B8 | Bi-directional data bus and register input                                                                       |  |  |  |  |  |

| G       | Output enable. This pin is an active low pin, when high all outputs are disabled and A and B ports are isolated. |  |  |  |  |  |

| DIR     | Direction control. This pin is used to determine the direction of data flow.                                     |  |  |  |  |  |

|         | When DIR = 1 ⇒ From A → B                                                                                        |  |  |  |  |  |

| 1       | $DIR = 0 \Rightarrow From B \rightarrow A$                                                                       |  |  |  |  |  |

| SAB     | Determines whether data transmitted is from the data inputs or the register associated with those                |  |  |  |  |  |

| SBA     | pins.                                                                                                            |  |  |  |  |  |

| 5.0     | When SAB (SBA) = 1 ⇒ Register → B (A) Bus.                                                                       |  |  |  |  |  |

|         | $SAB (SBA) = 1 \Rightarrow A (B) \rightarrow B (A)$                                                              |  |  |  |  |  |

| CAB     | Positive trigger clock. When rising edge is triggered, data from A (B) input are loaded into their               |  |  |  |  |  |

| CBA     | associated register.                                                                                             |  |  |  |  |  |

The transceiver function can work only when  $\overline{G}$  is active low (G=0). DIR determines the direction of data flow. In the transceiver mode, data present at the high-impedance port may be stored in either register or in both.

Enable ( $\overline{G}$ ) and direction (DIR) pins are provided to control the transceiver functions. In the transceiver mode, data present at the high-impedance port may be stored in either register or in both. The select controls (SAB and SBA) can multiplex stored and real-time (transparent mode)

data. The direction control determines which bus will receive data when enable  $\overline{G}$  is active (low). In the isolation mode (control  $\overline{G}$  high). Data may be stored in one register and/or B data may be stored in the other register.

When an output function is disabled, the input function is still enabled and may be used to store and transmit data. Only one of the two buses, A or B, may be driven at a time.

#### **Function Table**

|        | Inputs |             |            | Data I/O <sup>†</sup> |        |                        |                        |                                                     |

|--------|--------|-------------|------------|-----------------------|--------|------------------------|------------------------|-----------------------------------------------------|

| G      | DIR    | CAB         | СВА        | SAB                   | SBA    | A1 Thru A8             | B1 Thru B8             | Operation or Function                               |

| X<br>X | ×      | †<br>X      | ×          | ×                     | ×      | Input<br>Not specified | Not specified<br>Input | Store A, B unspecified<br>Store B, A unspecified    |

| Н      | ×      | †<br>Hor L  | ↑<br>Hor L | X                     | ×      | Input                  | Input                  | Store A and B Data<br>Isolation, hold storage       |

| L      | L<br>L | ×           | H or L     | X                     | L<br>H | Output                 | Input                  | Real-time B Data to A Bus<br>Stored B Data to A Bus |

| L      | Н      | H or L<br>X | ×          | L<br>H                | ×      | Input                  | Output                 | Real-time A Data to B Bus<br>Stored A Data to B Bus |

<sup>†</sup> The data output functions may be enabled or disabled by various signals at the G and DTR inputs. Data input functions are always anabled, i.e., data at the bus pins will be stored on every low-to-high transition on the clock inputs.

### **Bus Management Functions**

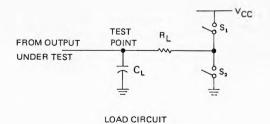

### **Parameter Measurements**

| ı    | Parameter        |                  | R <sub>L</sub> | CL    | S <sub>1</sub> | S <sub>2</sub> |  |

|------|------------------|------------------|----------------|-------|----------------|----------------|--|

|      |                  | t <sub>PZH</sub> | 1 ΚΩ           | 50 pF | OPEN           | CLOSED         |  |

| l 'e | t <sub>en</sub>  | t <sub>PZL</sub> | 1 1 1 2 2      | 50 рі | CLOSED         | OPEN           |  |

|      |                  | t <sub>PHZ</sub> | 1 ΚΩ           | 50 pF | OPEN           | CLOSED         |  |

|      | <sup>1</sup> dis | t <sub>PLZ</sub> | 1 1 1 2 2      | 50 pr | CLOSED         | OPEN           |  |

Figure 1, 3-state Outputs

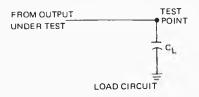

|                      | CL                   |       |

|----------------------|----------------------|-------|

| t <sub>pd</sub>      | Standard outputs     | 50 pF |

| or<br>t <sub>t</sub> | High-current outputs | 50 pF |

Figure 2. Totem-Pole Outputs

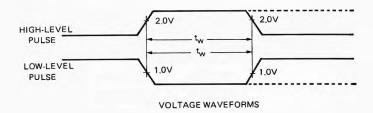

Figure 3. Pulse Durations

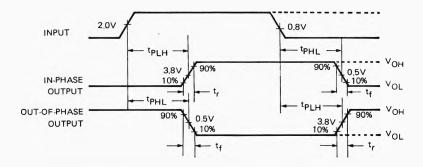

Figure 4. Propagation Delay Times and Output Transition Times

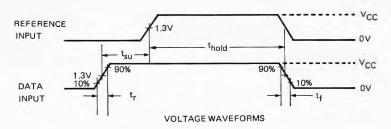

Figure 5. Setup and Hold Times and Input Rise and Fall Time

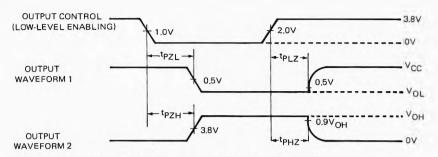

Figure 6. Enable and Disable Times for 3-state Outputs

### **Ordering Information**

| Number     | Package |

|------------|---------|

| UM74HCT646 | 24L DIP |