# A.C. PLASMA PANEL DRIVER

- 32-BIT SHIFT REGISTER WITH LATCHES

- DECODING LOGIC CIRCUIT

- LOW TO HIGH VOLTAGE INTERFACE FOR DI-RECT CONNECTION TO 32 ELECTRODES

# **DIP-40** (Plastic)

**ORDER CODE**: UEB4732DP

### DESCRIPTION

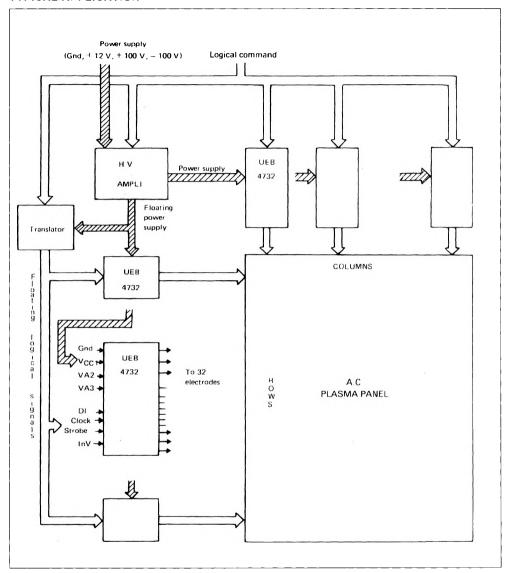

UEB4732 is a BIMOS\* IC's especially designed to provide selective and sustain signals needed by the X and Y electrodes of an A.C. plasma panel.

Realizing a complete A.C. plasma panel control system requires only UEB4732 and two high voltage common amplifiers for rows and columns of the panel. The whole network is driven by a few CMOS logical signals.

Bipolar CMOS and complementary DMOS on same chip.

#### PIN CONNECTION

| Clock           | d. O        | 40 7 VCC1        |

|-----------------|-------------|------------------|

|                 | 5           |                  |

| Inverting input | Ц2          | 39 DI            |

| Strobe          | [] 3        | 38 Ground (logic |

| Output 1        | [4          | 37 Output 32     |

| Output 2        | [ 5         | 36 Output 31     |

| Output 3        | [ 6         | 35 Output 30     |

| Output 4        | Q٦          | 34 🗎 Output 29   |

| Output 5        | C 8         | 33 Dutput 28     |

| Output 6        | [ 9         | 32 Output 27     |

| Output 7        | [ 10        | 31 Output 26     |

| Output 8        | []11        | 30 Output 25     |

| Output 9        | [] 12       | 29 Output 24     |

| Output 10       | [] 13       | 28 Output 23     |

| Output 11       | []14        | 27 Output 22     |

| Output 12       | [ 15        | 26 Output 21     |

| Output 13       | [ 16        | 25 Output 20     |

| Output 14       | <b>[</b> 17 | 24 Output 19     |

| Output 15       | []18        | 23 Dutput 18     |

| Output 16       | [ 19        | 22 ] Output 17   |

| VA3             | [ 20        | 21 VA2           |

|                 |             |                  |

- 4 CMOS compatible logic inputs: DI, Clock, Strobe, Inv.

- 32 totem pole 100 V outputs, with clamping diodes to the VA2 and VA3 inputs.

- Logic supplies (Ground and V<sub>CC1</sub>) separated from hight voltage (VA2, VA3) to avoid disturbances.

# TYPICAL APPLICATION

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol                                | Parameter                                                    | Value                           |   |  |  |  |

|---------------------------------------|--------------------------------------------------------------|---------------------------------|---|--|--|--|

| V <sub>CC1</sub> Logic Supply Voltage |                                                              | 18                              |   |  |  |  |

| V <sub>A2</sub>                       | V <sub>A2</sub> Voltage (V <sub>A2</sub> ≥ V <sub>A3</sub> ) | 120                             | V |  |  |  |

| V <sub>A3</sub>                       | V <sub>A3</sub> Voltage                                      | 10                              | V |  |  |  |

| Vi                                    | Input Voltage Range                                          | - 0.3 to V <sub>CC1</sub> + 0.3 | V |  |  |  |

NOTE: Voltage values are with respect to network ground terminal (ground logic).

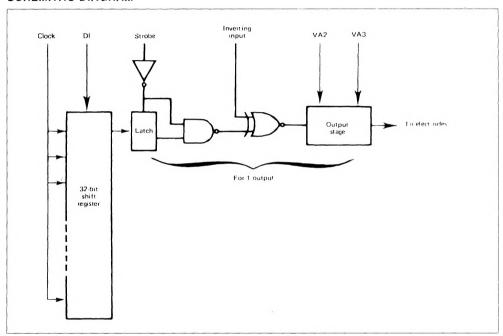

## SCHEMATIC DIAGRAM

# **ELECTRICAL OPERATING CHARACTERISTICS** (over recommended operating range)

| Symbol             | Parameter                                                                                                                       | Min. | Тур.    | Max.     | Unit |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------|------|---------|----------|------|

| V <sub>OH</sub>    | High Level Dropout Voltage (for one output) $V_{A2} > 20 \text{ V}$<br>$-I_{OH} = -10 \text{ mA}$<br>$-I_{OH} = -20 \text{ mA}$ |      | 5<br>10 | 10<br>20 | V    |

| V <sub>OL</sub>    | Low Level Dropout Voltage (for one output) V <sub>A3</sub> = Ground - I <sub>OL</sub> = 10 mA - I <sub>OL</sub> = 20 mA         |      | 5<br>10 | 10<br>20 | ٧    |

| V <sub>OK</sub>    | Dropout Clamp Voltage $-I_0 = \pm 100$ mA in One Output $-I_0 = \pm 100$ mA Simultaneously in the 32 Outputs                    |      |         | 2        | V    |

| f <sub>clock</sub> | Maximum Clock Pulse Frequency                                                                                                   | 4    | 8       |          | MHz  |

All typical values are at V<sub>CC1</sub> = 12 V, T<sub>amb</sub> = 25 °C.

# RECOMMANDED OPERATING CONDITIONS (voltage values are referred to logic ground of the IC)

| Symbol           | Parameter                                                                                                | Min.  | Тур.       | Max. | Unit |  |

|------------------|----------------------------------------------------------------------------------------------------------|-------|------------|------|------|--|

| Vcc              | Logic Supply Voltage                                                                                     | 10    |            | 15   | V    |  |

| V <sub>A2</sub>  | $V_{A2}$ Voltage $(V_{A2} \ge V_{A3})$                                                                   | - 0.6 |            | 120  | ٧    |  |

| V <sub>A3</sub>  | V <sub>A3</sub> Voltage                                                                                  | - 0.6 |            | 10   | V    |  |

| 10               | Peak Current (for one output)  - High Level $V_{A2} > 20 \text{ V}$ - Low Level $V_{A3} = \text{Ground}$ |       | - 20<br>20 |      | mA   |  |

| 10               | Peak Clamp Current (for one output)                                                                      |       | ± 100      |      | mA   |  |

| T <sub>amb</sub> | Operating Free Air Temperature<br>UEB4732                                                                | 0     |            | + 70 | °C   |  |

## **FUNCTION TABLE**

| Functions | Data        | Data        | Inputs      |              | Strobe                                                                        | Shift Register |                        | Latchs                 |                            |                      | Outputs                                                                     |                        |              |

|-----------|-------------|-------------|-------------|--------------|-------------------------------------------------------------------------------|----------------|------------------------|------------------------|----------------------------|----------------------|-----------------------------------------------------------------------------|------------------------|--------------|

|           |             | Clock       | Inv.        | R1           |                                                                               | R2             | R32                    | L1                     | L2                         | L32                  | 01                                                                          | 02                     | 032          |

| LOAD      | H<br>L      | <b>†</b>    | X           | ×            | H                                                                             | R1n<br>R1n     | R31n<br>R31n           | R1s<br>R1s             | R2s<br>R2s                 | R32s<br>R32s         | Levels at 01 through<br>032 depend on Inv.<br>and strobe (see<br>"strobe"). |                        |              |

| LATCH     | X           | H           | L           | $\downarrow$ | R1n<br>R1n                                                                    | R2n<br>R2n     | R32n<br>R32n           | R1n<br>R1n             | R2n<br>R2n                 | R32n<br>R32n         | R1n<br>R1n                                                                  | R2n<br>R2n             | R32n<br>R32n |

| STROBE    | X<br>X<br>X | X<br>X<br>X | L<br>H<br>L | L<br>H<br>H  | Levels at R1 through<br>R32 depend only on<br>data and clock (see<br>"load"). |                | R1s<br>R1s<br>R1<br>R1 | R2s<br>R2s<br>R2<br>R2 | R32s<br>R32s<br>R32<br>R32 | R1s<br>R1s<br>L<br>H | R2s<br>R2s<br>L<br>H                                                        | R32s<br>R32s<br>L<br>H |              |

H = High level

X = Irrelevant

↓ = High to low transition

For the outputs, the high level (H) is VA2, the low level (L) is VA3.

R1.....R32 = Levels currently at internal outputs of shift register.

R1n....R32n = Levels at shift register outputs R1 through R32, respectively, before the most recent 1 transition of clock.

R1s....R32s = Levels at shift register outputs R1 through R32, respectively, before the most recent ↓ transition of strobe (levels currently stored by the 32 latchs L1 through L32).

R1s....R32s = Logical inversion of R1s....R32s.

L = Low level

<sup>↑ =</sup> Low to high transition

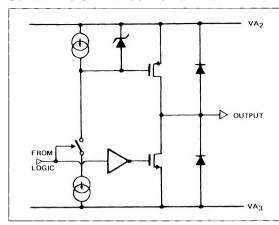

#### SCHEMATIC OF ONE OUTPUT STAGE

During the sustaining signal,  $V_{A2} = V_{A3}$  and the current flows through the two clamp diodes.

During the selective signals (write and erase on the plasma panel), V<sub>A2</sub> is at high voltage (typ.100 V, referred to logic ground) V<sub>A3</sub> is equal to logic ground, and the output is selectively adressed by complementary by DMOS stage.

## DESCRIPTION

The UEB4732 is designed to provide easily the line and the column select operation of a plasma display panel. For an use on the X axis of the panel, the Inv. input is set at a steady low level, the outputs are normally low and are selectively switched high when the strobe input is low. For an use on the Y axis of the panel, the Inv. input is set at a steady high level, the outputs are normally high and are selectively switched low when the strobe input is low (the 32 bit data is inverted).

The Inv. input may also be used as a sustain input: when strobe is high, if the Inv. input is switched low, all outputs switch low, if the Inv. input is switched high, all outputs switch high.

Data is enterred serially in the shift register, on the low to high level transition of clock. It is stored in the 32 latchs on the high to low level transition of strobe, so the outputs are stable during the low level of strobe, regradless of the state of clock and data, and a new data can be enterred immediately.

The logical voltage reference (ground logic) and the high voltage reference (VA3) are separated to avoid disturbances.

All output stages are complementary DMOS and contain clamp diodes to the  $V_{A2}$  and  $V_{A3}$  supply inputs. These diodes are designed to provide the peak current of the sustaining signal (typ. 100 mA/output) without distorsion of the signal.

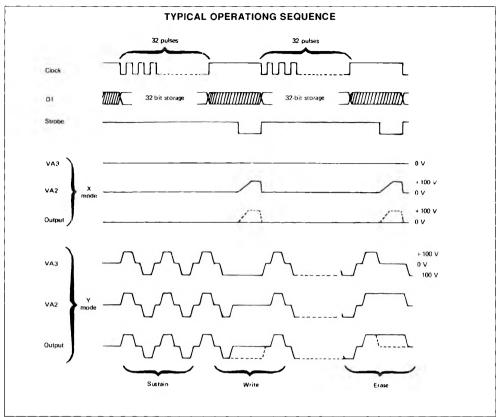

# **TIMING DIAGRAM**

Note: X mode circuits are referred to ground. Y mode ones are floating on sustaining voltage.

In X mode, Inv. input is low.

In Y mode, Inv. input is high.