# Natural Interleaving™ DUAL-PHASE TRANSITION-MODE PFC CONTROLLER

## NATURAL INTERLEAVING FEATURES

- Easy Phase Management Facilitates

Compliance to Light-Load Efficient Standards

- FailSafe OVP with Dual Paths Prevents Output Over-voltage Conditions Caused by Voltage-Sensing Failures

- Sensorless Current Shaping Simplifies Board Layout and Improves Efficiency

- Inrush Safe Current Limiting:

- Prevents MOSFET conduction during inrush

- Eliminates reverse recovery events in output rectifiers

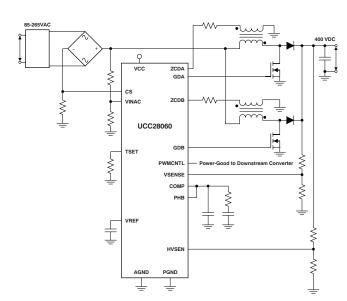

**Typical Application Circuit**

#### SYSTEM FEATURES

- Cost Savings

- Improved Efficiency and Design Flexibility over Traditional, Single-Phase Continuous Conduction Mode (CCM)

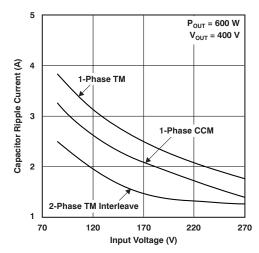

- Input Filter and Output Capacitor Current Cancellation:

- Reduced current ripple for higher system reliability and smaller bulk capacitor

- Reduced EMI filter size

- Enables Use of Low-Cost Diodes without Extensive Snubber Circuitry

- Improved Light-Load Efficiency

- Improved Transient Response

- Complete System-Level Protection

- 1-A Source/1.8-A Sink Gate Drivers

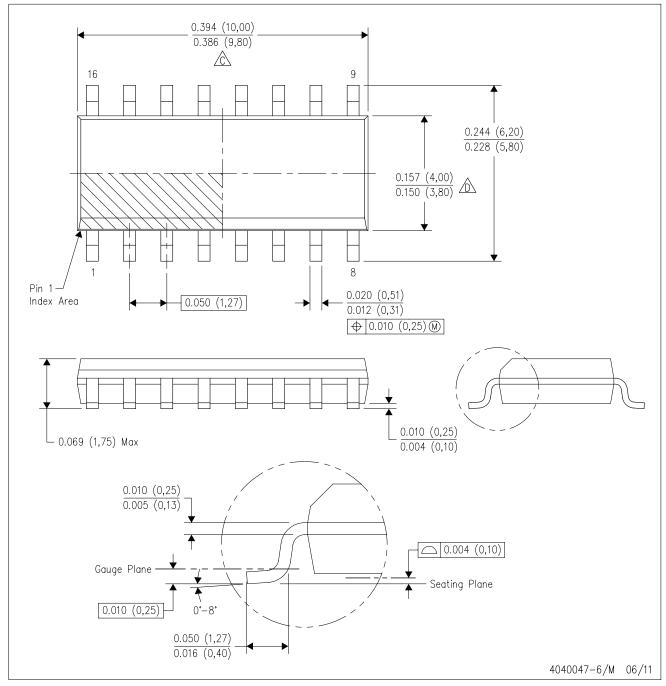

- Operating Temperature Range: -40°C to +125°C in an SOIC 16-pin package

#### **APPLICATIONS**

- 100-W to 800-W Power Supplies

- LCD. Plasma, and DLP<sup>®</sup> TVs

- Computer Power Supplies

- Entry Level Servers

- Electronic Lighting Ballasts

**Ripple Current Reduction**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

DLP is a registered trademark of Texas Instruments.

Natural Interleaving is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### CONTENTS

- Ordering Information 2

- Electrical Characteristics 4

- Device Information 7

- Functional Block Diagram 9

- Typical Characteristics 10

- Application Information 17

- Design Example 23

- Additional References 30

#### DESCRIPTION

Optimized for high-volume consumer applications, this solution extends the advantages of transition mode—high efficiency with low-cost components—to higher power ratings than previously possible. By utilizing a Natural Interleaving technique, both channels operate as *masters* (that is, there is no slave channel) synchronized to the same frequency. This approach delivers inherently strong matching, faster responses, and ensures that each channel operates in transition mode.

Complete system-level protections feature input brownout, output over-voltage, open-loop, overload, soft-start, phase-fail detection, and thermal shutdown. The additional FailSafe over-voltage protection (OVP) feature protects against shorts to an intermediate voltage that, if undetected, could lead to catastrophic device failure.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ORDERING INFORMATION(1)

| PART NUMBER | PACKAGE <sup>(2)</sup> | OPERATING TEMPERATURE RANGE, TA |

|-------------|------------------------|---------------------------------|

| UCC28060D   | SOIC 16-Pin (D)        | -40°C to +125°C                 |

- (1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

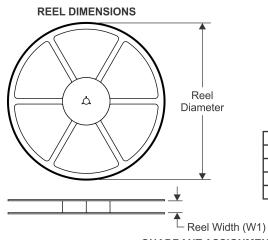

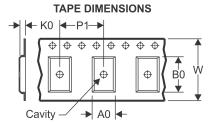

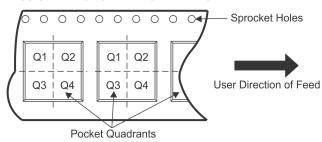

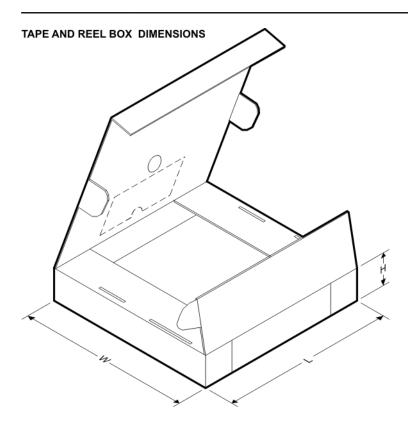

- (2) SOIC (D) package is available taped and reeled by adding R to the above part number. Reeled quantities for UCC28060DR are 2500 devices per reel.

## ABSOLUTE MAXIMUM RATINGS(1)

All voltages are with respect to GND,  $-40^{\circ}$ C <  $T_J = T_A < +125^{\circ}$ C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                                      |                                                                                                    | UCC28060    | UNIT |

|--------------------------------------|----------------------------------------------------------------------------------------------------|-------------|------|

|                                      | VCC <sup>(2)</sup>                                                                                 | -0.5 to +21 |      |

| Leavel coefficient manager           | PWMCNTL                                                                                            | -0.5 to +20 | V    |

| Input voltage range                  | COMP <sup>(3)</sup> , CS, PHB, HVSEN <sup>(4)</sup> , VINAC <sup>(4)</sup> , VSENSE <sup>(4)</sup> | -0.5 to +7  | V    |

|                                      | ZCDA, ZCDB                                                                                         | -0.5 to +4  |      |

| Continuous input current             | VCC                                                                                                | 20          |      |

| Input current                        | PWMCNTL                                                                                            | 10          |      |

| Input current range                  | ZCDA, ZCDB, VSENSE                                                                                 | −5 to +5    | mA   |

| Output current                       | VREF                                                                                               | -10         |      |

| Continuous gate current              | GDA, GDB <sup>(5)</sup>                                                                            | ±25         |      |

| lunction temperature T               | Operating                                                                                          | -40 to +125 |      |

| Junction temperature, T <sub>J</sub> | Storage                                                                                            | -65 to +150 | °C   |

| Lead temperature, T <sub>SOL</sub>   | Soldering, 10s                                                                                     | +260        |      |

- (1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those included under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods of time may affect device reliability.

- (2) Voltage on VCC is internally clamped. VCC may exceed the absolute maximum input voltage if the source is current limited below the absolute maximum continuous VCC input current level.

- (3) In normal use, COMP is connected to capacitors and resistors and is internally limited in voltage swing.

- (4) In normal use, VINAC, VSENSE, and HVSEN are connected to resistors and are internally limited in voltage swing. Although not recommended for extended use, VINAC, VSENSE, and HVSEN can survive input currents as high as ±10 mA from high voltage sources.

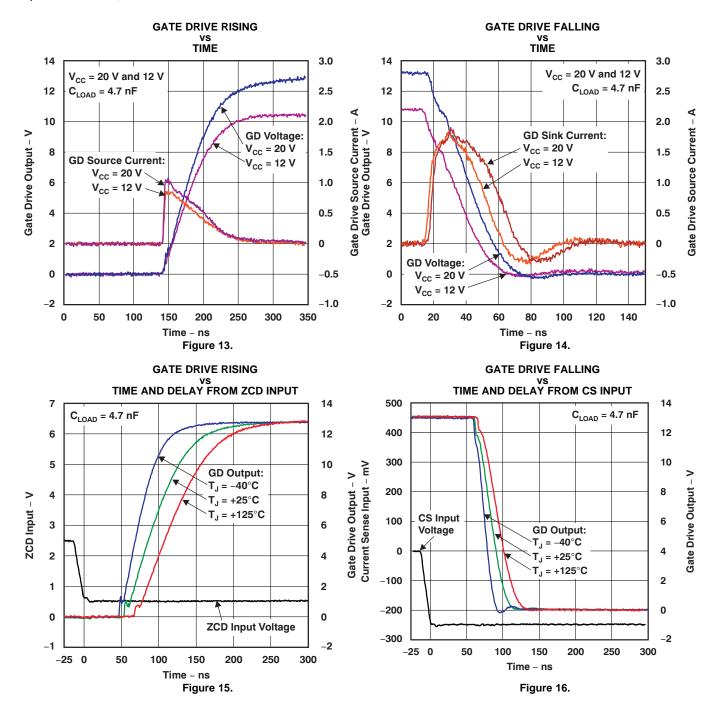

- (5) No GDA or GDB current limiting is required when driving a power MOSFET gate. However, a small series resistor may be required to damp ringing due to stray inductance. See Figure 13 and Figure 14 for details.

## **DISSIPATION RATINGS**

| PACKAGE         | THERMAL IMPEDANCE PACKAGE JUNCTION-TO-AMBIENT |                       | T <sub>A</sub> = +85°C POWER RATING |

|-----------------|-----------------------------------------------|-----------------------|-------------------------------------|

| SOIC 16-Pin (D) | 140°C/W <sup>(1)</sup>                        | 890 mW <sup>(1)</sup> | 460 mW <sup>(1)</sup>               |

<sup>(1)</sup> Tested per JEDEC EIA/JESD 51-1. Thermal resistance is a strong function of board construction and layout. Air flow will reduce thermal resistance. This number is only a general guide; see TI document SPRA953 device Thermal Metrics.

## RECOMMENDED OPERATING CONDITIONS

All voltages are with respect to GND,  $-40^{\circ}$ C <  $T_J = T_A < +125^{\circ}$ C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                                                | MIN  | MAX | UNIT |

|------------------------------------------------|------|-----|------|

| VCC input voltage from a low-impedance source  | 14   | 21  | V    |

| VCC input current from a high-impedance source | 8    | 18  | mA   |

| VREF load current                              | 0    | -2  | mA   |

| VINAC Input voltage                            | 0    | 6   | V    |

| ZCDA, ZCDB series resistor                     | 20   | 80  | kΩ   |

| TSET resistor to program PWM on-time           | 66.5 | 270 | kΩ   |

| HVSEN input voltage                            | 0.8  | 4.5 | V    |

| PWMCNTL pull-up resistor to VREF               | 1    | 10  | kΩ   |

## **ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

|                            | RATING | UNIT |

|----------------------------|--------|------|

| Human body model (HBM)     | 2000   | V    |

| Charged device model (CDM) | 500    | V    |

Copyright © 2007–2008, Texas Instruments Incorporated

## **ELECTRICAL CHARACTERISTICS**

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $-40^{\circ}$ C <  $T_J$  =  $T_A$  < +125 $^{\circ}$ C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                        | PARAMETER                                                    | TEST CONDITIONS                            | MIN  | TYP   | MAX   | UNIT |

|------------------------|--------------------------------------------------------------|--------------------------------------------|------|-------|-------|------|

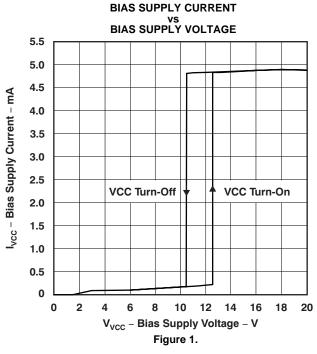

| VCC BIAS S             | SUPPLY                                                       | 1                                          |      |       |       |      |

| VCC <sub>(shunt)</sub> | VCC shunt voltage <sup>(1)</sup>                             | I <sub>VCC</sub> = 10 mA                   | 22   | 24    | 26    | V    |

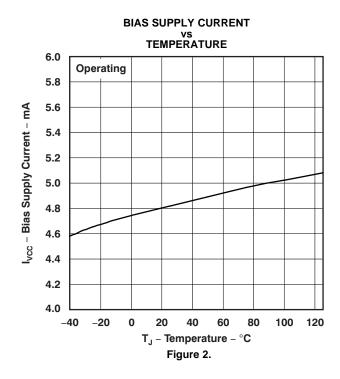

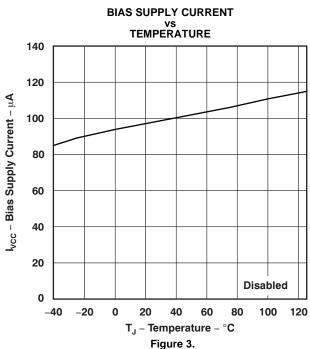

| I <sub>VCC(stby)</sub> | VCC current, disabled                                        | VSENSE = 0 V                               |      | 100   | 200   | μΑ   |

| I <sub>VCC(on)</sub>   | VCC current, enabled                                         | VSENSE = 6 V                               |      | 5     | 8     | mA   |

| UNDERVOL               | TAGE LOCKOUT (UVLO)                                          |                                            |      |       |       |      |

| VCC <sub>(on)</sub>    | VCC turn-on threshold                                        |                                            | 11.5 | 12.6  | 13.5  | V    |

| VCC <sub>(off)</sub>   | VCC turn-off threshold                                       |                                            | 9.5  | 10.35 | 11.5  | V    |

|                        | UVLO Hysteresis                                              |                                            | 1.85 | 2.25  | 2.65  | V    |

| REFERENC               | E                                                            | 1                                          |      |       |       |      |

| $V_{REF}$              | VREF output voltage, no load                                 | I <sub>VREF</sub> = 0 mA                   | 5.82 | 6.00  | 6.18  | V    |

|                        | VREF change with load                                        | 0 mA ≤ I <sub>VREF</sub> ≤ -2 mA           |      | 1     | 6     | mV   |

|                        | VREF change with VCC                                         | 12 V ≤ VCC ≤ 20 V                          |      | 1     | 10    | mV   |

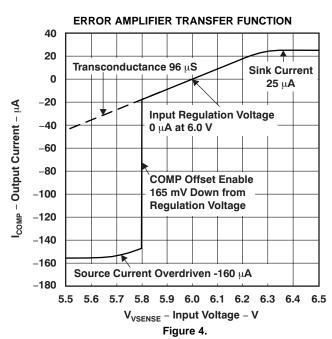

| ERROR AM               | PLIFIER                                                      | 1                                          |      |       |       |      |

|                        | VSENSE input regulation voltage                              | T <sub>A</sub> = +25°C                     | 5.85 | 6.00  | 6.15  | V    |

|                        | VSENSE input regulation voltage                              |                                            | 5.82 | 6.00  | 6.18  | V    |

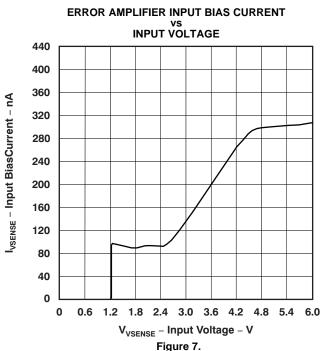

|                        | VSENSE input bias current                                    | In regulation                              | 125  | 300   | 800   | nA   |

|                        | COMP high voltage, clamped                                   | VSENSE = 5.8 V                             | 4.70 | 4.95  | 5.10  | V    |

|                        | COMP low voltage, saturated                                  | VSENSE = 6.2 V                             |      | 0.03  | 0.125 | V    |

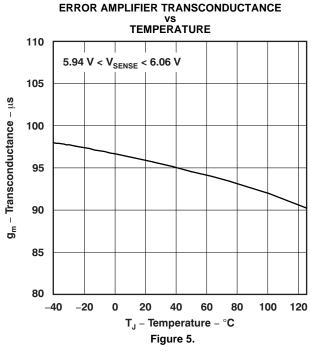

| g <sub>m</sub>         | VSENSE to COMP transconductance                              | COMP = 3 V,<br>5.94 V < VSENSE < 6.06 V    | 75   | 96    | 110   | μS   |

|                        | COMP source current, overdriven                              | VSENSE = 5 V, COMP = 3 V                   | -120 | -160  | -190  | μΑ   |

|                        | COMP sink current                                            | VSENSE = 6.4 V, COMP = 3 V                 | 18   | 25    | 32    | μΑ   |

|                        | VSENSE threshold for COMP offset enable, down from $V_{REF}$ | Voltage below V <sub>REF</sub>             | 135  | 185   | 235   | mV   |

| V <sub>OVP</sub>       | VSENSE over-voltage threshold, rising                        |                                            | 6.25 | 6.45  | 6.7   | V    |

|                        | VSENSE over-voltage hysteresis                               |                                            | 0.1  | 0.2   | 0.4   | V    |

|                        | VSENSE enable threshold, rising                              |                                            | 1.15 | 1.25  | 1.35  | V    |

|                        | VSENSE enable hysteresis                                     |                                            | 0.02 | 0.05  | 0.2   | V    |

| OUTPUT MO              | ONITORING                                                    |                                            |      |       | '     |      |

| V <sub>PWMCNTL</sub>   | HVSEN threshold to PWMCNTL                                   | HVSEN rising                               | 2.35 | 2.50  | 2.65  | V    |

|                        | HVSEN input bias current, high                               | HVSEN = 3 V                                | -0.5 |       | 0.5   | μΑ   |

|                        | HVSEN input bias current, low                                | HVSEN = 2 V                                | 28   | 36    | 41    | μΑ   |

|                        | HVSEN rising threshold to over-voltage fault                 |                                            | 4.64 | 4.87  | 5.1   | V    |

|                        | HVSEN falling threshold to over-voltage fault                |                                            | 4.45 | 4.67  | 4.80  | V    |

|                        | Phase Fail filter time to PWMCNTL high                       | PHB = 5 V,<br>ZCDA switching, ZCDB = 0.5 V | 8    | 14    | 20    | ms   |

|                        | PWMCNTL leakage current high                                 | HVSEN = 2 V, PWMCNTL = 15 V                | -1   |       | 1     | μΑ   |

|                        | PWMCNTL output voltage low                                   | HVSENS = 3 V, IPWMCNTL = 5 mA              |      | 0.2   | 0.5   | V    |

<sup>(1)</sup> Excessive VCC input voltage and current will damage the device. This clamp does not protect the device from an unregulated supply. If an unregulated supply is used, a Fixed Positive Voltage Regulator such as the UA78L15A is recommended. See the Absolute Maximum Ratings table for the limits on VCC voltage and current.

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $-40^{\circ}$ C <  $T_{J}$  =  $T_{A}$  < +125 $^{\circ}$ C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|          | PARAMETER                                       | TEST CONDITIONS                                                                 | MIN    | TYP    | MAX                                   | UNIT |

|----------|-------------------------------------------------|---------------------------------------------------------------------------------|--------|--------|---------------------------------------|------|

| GATE DR  | RIVE <sup>(2)</sup>                             | ,                                                                               |        |        | "                                     |      |

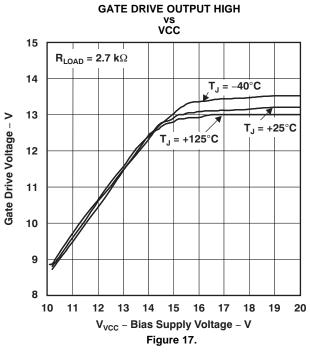

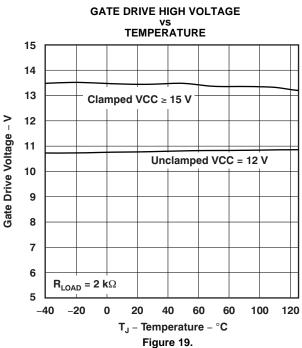

|          | GDA, GDB output voltage high                    | I <sub>GDA</sub> , I <sub>GDB</sub> = −100 mA                                   | 11.5   | 13     | 15                                    | V    |

|          | GDA, GDB output voltage high, clamped           | VCC = 20 V, I <sub>GDA</sub> , I <sub>GDB</sub> = -5 mA                         | 12     | 13.5   | 15                                    | V    |

|          | GDA, GDB output voltage high, low VCC           | VCC = 12 V, I <sub>GDA</sub> , I <sub>GDB</sub> = -5 mA                         | 10     | 10.5   | 11.5                                  | V    |

|          | GDA, GDB on-resistance high                     | I <sub>GDA</sub> , I <sub>GDB</sub> = -100 mA                                   |        | 8      | 14                                    | Ω    |

|          | GDA, GDB output voltage low                     | I <sub>GDA</sub> , I <sub>GDB</sub> = 100 mA                                    |        | 0.15   | 0.3                                   | V    |

|          | GDA, GDB on-resistance low                      | I <sub>GDA</sub> , I <sub>GDB</sub> = 100 mA                                    |        | 2      | 3                                     | Ω    |

|          | Rise time                                       | 1 V to 9 V, C <sub>LOAD</sub> = 1 nF                                            |        | 18     | 30                                    | ns   |

|          | Fall time                                       | 9 V to 1 V, C <sub>LOAD</sub> = 1 nF                                            |        | 12     | 25                                    | ns   |

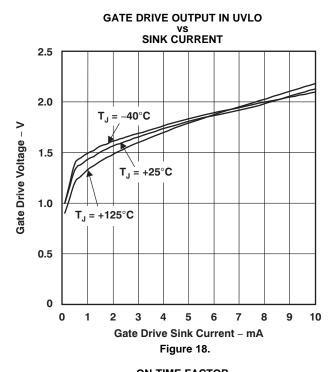

|          | GDA, GDB output voltage UV                      | I <sub>GDA</sub> , I <sub>GDB</sub> = 2.5 mA                                    |        | 1.6    | 2                                     | V    |

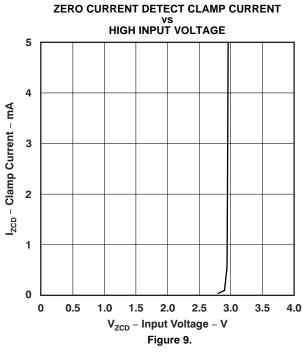

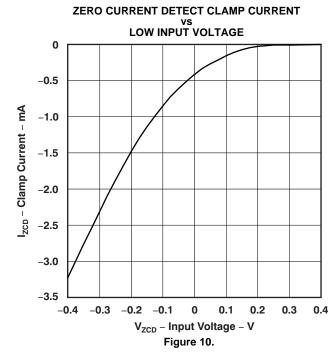

| ZERO CU  | IRRENT DETECTOR                                 |                                                                                 | ·      |        |                                       |      |

|          | ZCDA, ZCDB voltage threshold, falling           |                                                                                 | 0.8    | 1.0    | 1.2                                   | V    |

|          | ZCDA, ZCDB voltage threshold, rising            |                                                                                 | 1.5    | 1.68   | 1.88                                  | V    |

|          | ZCDA, ZCDB clamp, high                          | $I_{ZCDA} = +2 \text{ mA}, I_{ZCDB} = +2 \text{ mA}$                            | 2.6    | 3.0    | 3.4                                   | V    |

|          | ZCDA, ZCDB input bias current                   | ZCDA = 1.4 V, ZCDB = 1.4 V                                                      | -0.5   |        | 0.5                                   | μΑ   |

|          | ZCDA, ZCDB clamp, low                           | $I_{ZCDA} = -2 \text{ mA}, I_{ZCDB} = -2 \text{ mA}$                            | -0.4   | -0.2   | 0                                     | V    |

|          | ZCDA, ZCDB delay to GDA, GDB outputs (2)        | Respective gate drive output rising 10% from zero crossing input falling to 1 V |        | 45     | 100                                   | ns   |

| CURREN   | T SENSE                                         |                                                                                 |        |        |                                       |      |

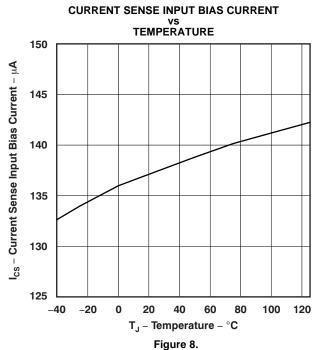

|          | CS input bias current                           | At rising threshold                                                             |        | -150   | -250                                  | μΑ   |

|          | CS current limit rising threshold               |                                                                                 | -0.18  | -0.20  | -0.22                                 | V    |

|          | CS current limit falling threshold              |                                                                                 | -0.005 | -0.015 | -0.029                                | V    |

|          | CS current limit response time <sup>(2)</sup>   | From CS exceeding threshold –0.05 V to GDx dropping 10%                         |        | 60     | 100                                   | ns   |

| MAINS IN | IPUT                                            |                                                                                 |        |        |                                       |      |

|          | VINAC input bias current                        | VINAC = 2 V                                                                     | -0.5   |        | 0.5                                   | μΑ   |

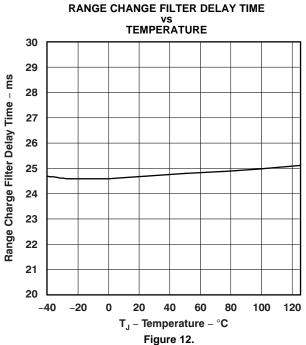

|          | VINAC line range threshold, rising              | To PWM on-time change                                                           | 3.25   | 3.45   | 3.60                                  | V    |

|          | VINAC line range threshold, falling             |                                                                                 | 3.05   | 3.20   | 3.35                                  | V    |

|          | VINAC line falling range change filter time (2) | VINAC line changes for less than the range change filter time                   | 18     | 26     | 36                                    | ms   |

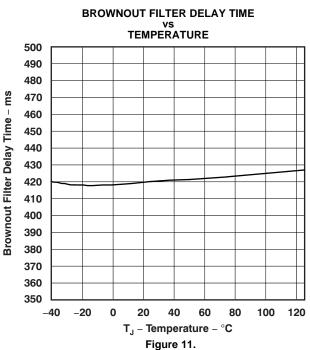

| BROWNC   | DUT                                             |                                                                                 |        |        | , , , , , , , , , , , , , , , , , , , |      |

|          | VINAC brownout threshold                        | VINAC falling                                                                   | 1.34   | 1.39   | 1.44                                  | V    |

|          | VINAC brownout current                          | VINAC = 1 V                                                                     | 5      | 7      | 9                                     | μΑ   |

|          | VINAC brownout filter time                      | VINAC fails to exceed the brownout threshold for the brownout filter time       | 340    | 440    | 540                                   | ms   |

<sup>(2)</sup> Refer to Figure 13, Figure 14, Figure 15, and Figure 16 in the Typical Characteristics for typical gate drive waveforms.

Copyright © 2007–2008, Texas Instruments Incorporated

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $-40^{\circ}$ C <  $T_J$  =  $T_A$  < +125 $^{\circ}$ C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                    | PARAMETER                                                         | TEST CONDITIONS                                             | MIN      | TYP   | MAX   | UNIT |

|--------------------|-------------------------------------------------------------------|-------------------------------------------------------------|----------|-------|-------|------|

| PULSE-WI           | DTH MODULATOR                                                     |                                                             | <u> </u> |       | •     |      |

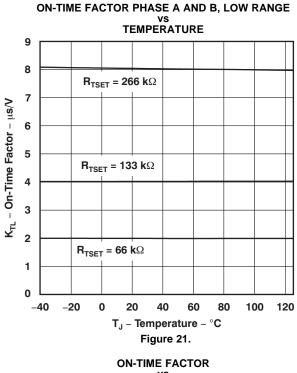

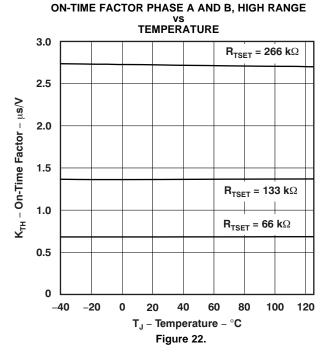

| K <sub>TH</sub>    | On-time factor, phases A and B, high range                        | VINAC = 3.75 V, VSENSE = 5.8 V <sup>(3)</sup>               | 1.25     | 1.35  | 1.5   | μs/V |

| K <sub>THS</sub>   | On-time factor, single-phase, A, high range                       | VINAC = 3.75 V, VSENSE = 5.8 V,<br>PHB = 0 V <sup>(3)</sup> | 2.4      | 2.7   | 3.0   | μs/V |

| K <sub>TL</sub>    | On-time factor, phases A and B, low range                         | VINAC = 3.2 V, VSENSE = 5.8 V <sup>(3)</sup>                | 3.6      | 4.0   | 4.4   | μs/V |

| K <sub>TLS</sub>   | On-time factor, single-phase, A, low range                        | VINAC = 3.2 V, VSENSE = 5.8 V,<br>PHB = 0 V <sup>(3)</sup>  | 7.2      | 8     | 8.9   | μs/V |

|                    | Phase B to phase A on-time matching, low line range               | VSENSE = 5.8 V, VINAC = 3.2 V                               | -6       |       | 6     | %    |

|                    | Phase B to phase A on-time matching, high line range              | VSENSE = 5.8V, VINAC = 3.75 V                               | -6       |       | 6     | %    |

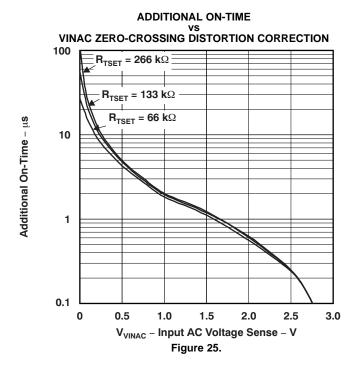

|                    | Zero-crossing distortion correction additional on                 | COMP = 0.25 V, VINAC = 1 V                                  |          | 2     |       | μs   |

|                    | time                                                              | COMP = 0.25 V, VINAC = 0.1 V                                |          | 20    |       | μs   |

|                    | PHB threshold falling, to single-phase operation, low line range  | To GDB output shutdown VINAC = 1.5 V                        | 0.7      | 0.8   | 0.9   | V    |

|                    | PHB threshold rising, to two-phase operation, low line range      | To GDB output running VINAC = 1.5 V                         | 0.9      | 1.0   | 1.1   | V    |

|                    | PHB threshold falling, to single-phase operation, high line range | To GDB output shutdown VINAC = 4.0 V                        | 1.0      | 1.1   | 1.2   | V    |

|                    | PHB threshold rising, to two-phase operation, high line range     | To GDB output running VINAC = 4.0 V                         | 1.2      | 1.3   | 1.4   | V    |

|                    | COMP threshold falling to shutdown                                | GDA and GDB outputs shutdown                                | 0.125    | 0.150 | 0.175 | V    |

|                    | COMP threshold rising to run                                      | GDA and GDB outputs running                                 | 0.17     | 0.20  | 0.23  | V    |

| T <sub>(min)</sub> | Minimum switching period                                          | $R_{TSET} = 133 \text{ k}\Omega^{(3)}$                      | 1.7      | 2.2   | 2.5   | μs   |

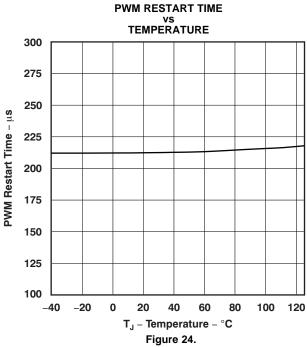

|                    | PWM restart time                                                  | ZCDA = ZCDB = 2 V <sup>(4)</sup>                            | 165      | 200   | 265   | μs   |

| THERMAL            | SHUTDOWN                                                          |                                                             | ·        |       |       |      |

|                    | Thermal shutdown temperature                                      | T <sub>J</sub> , temperature rising <sup>(5)</sup>          |          | +160  |       | °C   |

|                    | Thermal restart temperature                                       | T <sub>J</sub> , temperature falling <sup>(5)</sup>         |          | +140  |       | °C   |

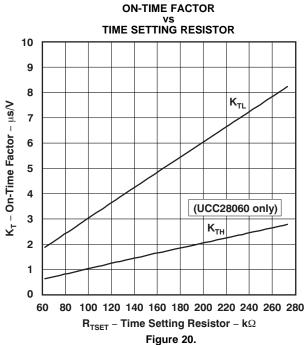

<sup>(3)</sup> Gate drive on-time is proportional to V<sub>COMP</sub> – 125 mV. The on-time proportionality factor, K<sub>T</sub>, is different in high and low ranges and also different in two-phase and single-phase modes. The on-time factor, K<sub>T</sub>, scales linearly with the value of R<sub>TSET</sub>. The minimum switching period is proportional to R<sub>TSET</sub>.

<sup>(4)</sup> An output on-time is generated at both GDA and GDB if both ZCDA and ZCDB negative-going edges are not detected for the restart time. In single-phase mode, the restart time applies for the ZCDA input and the GDA output.

<sup>(5)</sup> Thermal shutdown occurs at temperatures higher than the normal operating range. Device performance above the normal operating temperature is not specified or assured.

## **DEVICE INFORMATION**

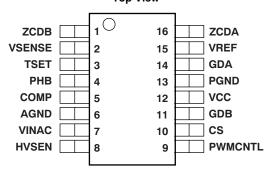

UCC28060D SOIC 16-Pin (D) Top View

## **TERMINAL FUNCTIONS**

| TERI  | TERMINAL |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME  | NO.      | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| AGND  | 6        | _   | <b>Analog ground:</b> Connect analog signal bypass capacitors, compensation components, and analog signal returns to this pin. Connect the analog and power grounds at a single point to isolate high-curoise signals of the power components from interference with the low-current analog circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| COMP  | 5        | 0   | <b>Error amplifier output:</b> The error amplifier is a transconductance amplifier, so this output is a high-impedance current source. Connect voltage regulation loop compensation components from this pin to AGND. The on-time seen at the gate drive outputs is proportional to the voltage at this pin minus an offset of approximately 125 mV. During soft-start events (undervoltage, brownout, or disable), COMP is pulled low. Normal operation only resumes after the soft-start event clears and COMP has been discharged below 0.5 V, making sure that the circuit restarts with a low COMP voltage and a short on-time. Do not connect COMP to a low-impedance source that would interfere with COMP falling below 0.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| cs    | 10       | I   | Current sense input: Connect the current sense resistor and the negative terminal of the diode bridge to this pin. Connect the return of the current sense resistor to the AGND pin with a separate trace. As input current increases, the voltage on CS goes more negative. This cycle-by-cycle over-current protection limits input current by turning off both gate driver (GDx) outputs when CS is more negative than the CS rising threshold (approximately –200 mV). The GD outputs remain low until CS falls to the CS falling threshold (approximately –15 mV). Current sense is blanked for approximately 100 ns following the falling edge of either GD output. This blanking filters noise that occurs when current switches from a power FET to a boost diode. In most cases, no additional current sense filtering is required. If filtering is required, the filter series resistance must be under 100 $\Omega$ to maintain accuracy. To prevent excessive negative voltage on the CS pin during inrush conditions, connect the current sensing resistor to the CS pin through a low value external resistor. As with the filter series resistance, this external resistor needs to be under 100 $\Omega$ to maintain accuracy. |  |  |  |

| GDA   | 14       | 0   | Channel A and channel B gate drive output: Connect these pins to the gate of the power FET for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| GDB   | 11       | 0   | each phase through the shortest connection practical. If it is necessary to use a trace longer than 0.5 in (12.6 mm) for this connection, some ringing may occur due to trace series inductance. This ringing can be reduced by adding a $5-\Omega$ to $10-\Omega$ resistor in series with GDA and GDB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| HVSEN | 8        | ı   | High voltage output sense: The UCC28060 incorporates FailSafe OVP so that any single failure does not allow the output to boost above safe levels. Output over-voltage is monitored by both VSENSE and HVSEN and shuts down the PWM if either pin exceeds the appropriate over-voltage threshold. Using two pins to monitor for over-voltage provides redundant protection and fault tolerance. HVSEN can also be used to enable a downstream power converter when the voltage on HVSEN is within the operating region. Select the HVSEN divider ratio for the desired over-voltage and power-good thresholds. Select the HVSEN divider impedance for the desired power-good hysteresis. During operation, HVSEN must never fall below 0.8 V. Dropping HVSEN below 0.8 V puts the UCC28060 into a special test mode, used only for factory testing. A bypass capacitor from HVSEN to AGND is recommended to filter noise and prevent false over-voltage shutdown.                                                                                                                                                                                                                                                                              |  |  |  |

| PGND  | 13       | _   | <b>Power ground for the integrated circuit:</b> Connect this pin to AGND through a separate short trace to isolate gate driver noise from analog signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

Copyright © 2007–2008, Texas Instruments Incorporated

## **TERMINAL FUNCTIONS (continued)**

| TERMINAL |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| РНВ      | 4   | I   | Phase B enable: This pin turns on/off channel B of the boost converter. The commanded on-time for channel A is immediately doubled when channel B is disabled, which helps to keep COMP voltage constant during the phase management transient. The PHB thresholds change with line range for the best efficiency when PHB is connected to COMP. PHB can also be driven by external logic signals to allow customized phase management. To disable phase management, connect the PHB pin to the VREF pin.                                                                                                                                                                                                                                                                         |

| PWMCNTL  | 9   | 0   | <b>PWM enable logic output:</b> This open-drain output goes low when HVSEN is within the HVSEN good region and the ZCDA and ZCDB inputs are switching correctly if operating in two-phase mode (see PHB Pin). Otherwise, PWMCNTL is high impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TSET     | 3   | I   | <b>Timing set:</b> PWM on-time programming input. Connect a resistor from TSET to AGND to set the on-time versus COMP voltage and the minimum period at the gate drive outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VCC      | 12  | _   | Bias supply input: Connect this pin to a controlled bias supply of between 14 V and 21 V. Also connect a 0.1-μF ceramic bypass capacitor from this pin to PGND. This supply powers all circuits in the device and must be capable of delivering 6 mA dc plus the transient power MOSFET gate charging current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VINAC    | 7   | I   | Input ac voltage sense: For normal operation, connect this pin to a voltage divider across the rectified input power mains. This input senses input voltage range to set the ramp rate and senses brownout. Input voltage range changes when the peak voltage on VINAC becomes and stays below the range change threshold for the range change filter time or the peak voltage on VINAC becomes above the range change threshold. When the voltage on VINAC remains below the brownout threshold for more than the brownout filter time, the device enters a brownout mode and both output drives are disabled. Select the input voltage divider ratio for the desired brownout threshold and power line range. Select the divider impedance for the desired brownout hysteresis. |

| VREF     | 15  | 0   | Voltage reference output: Connect a 0.1-μF ceramic bypass capacitor from this pin to AGND. This 6 VDC reference can be used to bias other circuits requiring less than 2 mA of total supply current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VSENSE   | 2   | I   | Output dc voltage sense: Connect this pin to a voltage divider across the output of the power converter. The error amplifier reference voltage is 6 V. Select the output voltage divider ratio for the desired output voltage. Connect the ground side of this divider to ground through a separate short trace for best output regulation accuracy and noise immunity. VSENSE can be pulled low by an open-drain logic output or 6-V logic output in series with a low-leakage diode to disable the outputs and reduce VCC current. If VSENSE is disconnected, open-loop protection provides an internal current source to pull VSENSE low, turning off the gate drivers.                                                                                                        |

| ZCDA     | 16  | I   | <b>Zero current detection inputs:</b> These inputs expect to see a negative edge when the inductor current in the respective phases go to zero. The inputs are clamped at 0 V and 3 V. Signals should be coupled through a series resistor that limits the clamping current to less than ±3 mA. Connect these pins through a current limiting resistor to the zero crossing detection windings of the appropriate boost                                                                                                                                                                                                                                                                                                                                                           |

| ZCDB     | 1   | I   | inductor. The inductor winding must be connected so that this voltage drops when inductor current decays to zero. When the inductor current drops to zero, the ZCD input must drop below the falling threshold, approximately 1 V, to cause the gate drive output to rise. When the power MOSFET turns off, the ZCD input must rise above the rising threshold, approximately 1.7 V, to arm the logic for another falling ZCD edge.                                                                                                                                                                                                                                                                                                                                               |

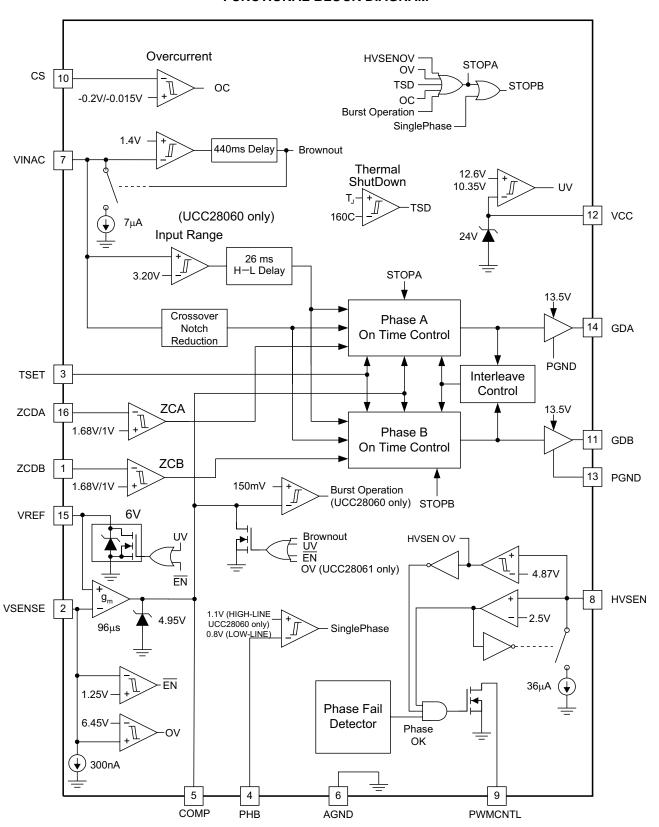

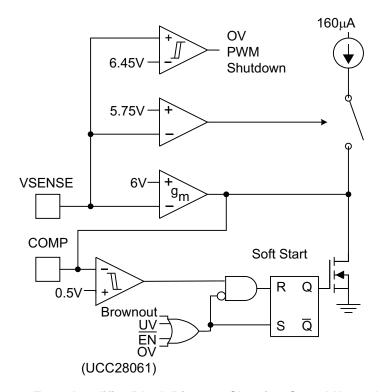

#### **FUNCTIONAL BLOCK DIAGRAM**

## TYPICAL CHARACTERISTICS

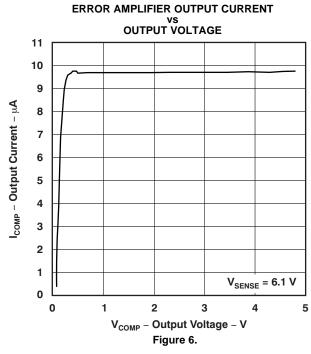

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = T_A = +25$ °C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = T_A = +25$ °C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = T_A = +25$ °C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = T_A = +25$ °C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = T_A = +25$ °C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

Submit Documentation Feedback

Copyright © 2007–2008, Texas Instruments Incorporated

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = T_A = +25$ °C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J$  =  $T_A$  = +25°C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

## **APPLICATION INFORMATION**

## **Theory of Operation**

The UCC28060 contains the control circuits for two boost pulse-width modulation (PWM) power converters. The boost PWM power converters ramp current in the boost inductors for a time period proportional to the voltage on the error amplifier output. Each power converter then turns off the power MOSFET until current in the boost inductor decays to 0, as sensed on the zero current detection inputs (ZCDA and ZCDB). Once the inductor current decays to 0, the power converter starts another cycle. This on/off cycling produces a triangle wave of current, with peak current set by the on-time and power mains input voltage, as shown in Equation 1.

$$I_{PEAK}(t) = \frac{VINAC(t) \times T_{ON}}{L}$$

(1)

The average line current is exactly equal to half of the peak line current, as shown in Equation 2.

$$I_{AVG}(t) = \frac{VINAC(t) \times T_{ON}}{2 \times L}$$

(2)

With  $T_{ON}$  and L being essentially constant during an ac line period, the resulting triangular current waveform during each switching cycle has an average value proportional to the instantaneous value of the rectified ac line voltage. This architecture results in a resistive input impedance characteristic at the line frequency and a near-unity power factor.

The outputs of the two PWMs operate 180° out-of-phase so that power-line ripple current for the two PWMs is greatly reduced from the ripple current of each individual PWM. This design reduces ripple current at the input and output, allowing the reduction in size and cost of input and output filters.

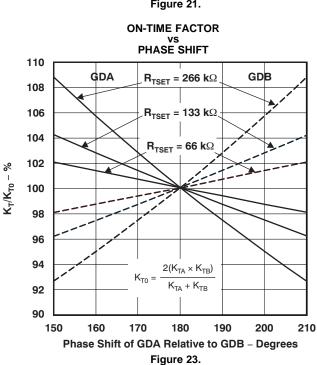

Optimal phase balance occurs if the individual power stages and the on-times are well-matched. Mismatches in inductor values do not affect the phase relationship.

## On-Time Control, Maximum Frequency Limiting, and Restart Timer

Gate drive on-time varies with the error amplifier output voltage by a factor called  $K_T$ , as shown in Equation 3.

$$T_{ON} = K_T (V_{COMP} - 125 \text{ mV})$$

(3)

Where:

V<sub>COMP</sub> is the output of the error amplifier, and 125 mV is a modulator offset.

To compensate for the effects of line voltage changes on loop gain,  $K_T$  is three times larger in low-line range than in high-line range, as shown in Equation 4.

$$K_{TL} = 3 \times K_{TH}$$

To provide smooth transition between two-phase and single-phase operation,  $K_T$  increases by a factor of two in single-phase mode:

- $K_{THS} = 2 \times K_{TH}$ ; active in high-line range and single-phase operation

- $K_{TLS} = 2 \times K_{TL}$ ; active in low-line range and single-phase operation

The clamped maximum output of the error amplifier is limited to 4.95 V. This value, less the 125 mV modulator offset, limits on-time to Equation 5.

$$T_{ON(max)} = K_T \times 4.825 \text{ V}$$

(5)

This on-time limit sets the maximum power that can be delivered by the converter at a given input voltage level.

The switching frequency of each phase is limited by minimum period timers. If the current decays to 0 before the minimum period timer elapses, turn-on is delayed, resulting in discontinuous phase current.

The restart timer ensures starting under all circumstances by restarting both phases if either phase ZCD input has not transitioned high-to-low for approximately 200 µs. To prevent the circuit from operating in continuous conduction mode (CCM), the restart time does not trigger turn-on until both phase currents return to 0.

Copyright © 2007–2008, Texas Instruments Incorporated

The on-time factors ( $K_{TH}$ ,  $K_{THS}$ ,  $K_{TL}$ ,  $K_{TLS}$ ) and the minimum switching period  $T_{MIN}$  are proportional to the time setting resistor  $R_{TSET}$ , the resistor from the TSET pin to ground, and they can be calculated by Equation 6 through Equation 8:

$$K_{TH} = \frac{R_{TSET}}{133 \text{ k}\Omega} \times 1.35 \frac{\mu \text{s}}{\text{V}} \text{ ; Active in High-Line Range (UCC28060 only)}$$

(6)

$$K_{TL} = \frac{R_{TSET}}{133 \text{ k}\Omega} \times 4.0 \frac{\mu \text{s}}{\text{V}}$$

; Active in Low-Line Range (7)

$$T_{MIN} = \frac{R_{TSET}}{133 \text{ k}\Omega} \times 2.2 \mu \text{s}$$

; Minimum Switching Period (8)

The proper value of  $R_{TSET}$  results in the clamped maximum on-time,  $T_{ON(max)}$ , required by the converter operating at the minimum input line and maximum load.

## **Natural Interleaving**

Under normal operating conditions, the UCC28060 regulates the relative phasing of the channel A and channel B inductor currents to be very close to 180°, minimizing the ripple currents seen at the line source and output capacitor. The phase control function differentially modulates the on-times of the A and B channels based on the phase and frequency relationship. This natural interleaving method allows the converter to achieve 180° phase shift and transition mode operation for both phases without the requirements on boost inductor tolerance. As a result, the current sharing of the A and B channels are proportional to the inductor tolerance. The best current sharing is achieved when both inductors are exactly the same value.

## **Easy Phase Management**

At light load conditions, because of the small conduction losses resulting from small load current and large switching losses caused by the discharging of the MOSFET junction capacitors, shutting down one of the power stages reduces switching loss and increases conduction loss. At certain power levels, the reduction of switching losses is greater than the increase in conduction losses; better efficiency can be realized. This feature is one of the major benefits of interleaved power factor correction (PFC) and it is especially valuable for meeting light-load efficient standards design requirements.

The easy phase management function allows the user to shut down one of the power stages to achieve higher efficiency at light load conditions by connecting the COMP pin to the PHB pin. Based on theoretical analysis and experimental results, the UCC28060 preset phase management thresholds can achieve maximum efficiency improvement. According to the COMP pin voltage, easy phase management shuts down phase B at corresponding power levels. The thresholds and corresponding power levels are listed in Table 1.

Table 1. PHB Management Performance with PHB Connected to COMP

|                    |                            | PHB THRESHOLDS |             |                              |                             |  |

|--------------------|----------------------------|----------------|-------------|------------------------------|-----------------------------|--|

|                    |                            | PHB THRESH     | OLD VOLTAGE | PERCENTAGE C                 | F FULL POWER                |  |

| VAC <sub>RMS</sub> | COMP VOLTAGE AT FULL POWER | HIGH TO LOW    | LOW TO HIGH | HIGH TO LOW<br>(PHASE B OFF) | LOW TO HIGH<br>(PHASE B ON) |  |

| 85                 | 4.85 V                     | 0.8 V          | 1.0 V       | 14%                          | 19%                         |  |

| 115                | 2.7 V                      | 0.8 V          | 1.0 V       | 26%                          | 34%                         |  |

| 133                | 2.1 V                      | 0.8 V          | 1.0 V       | 35%                          | 45%                         |  |

| 187                | 3.1 V                      | 1.1 V          | 1.3 V       | 33%                          | 40%                         |  |

| 230                | 2.1 V                      | 1.1 V          | 1.3 V       | 50%                          | 61%                         |  |

| 265                | 1.6 V                      | 1.1 V          | 1.3 V       | 67%                          | 81%                         |  |

The PHB pin can also be driven by an external logic signal to allow customized phase management. To disable phase management, connect the PHB pin to the VREF pin.

## **Zero Crossing Detection and Valley Switching**

In transition-mode PFC circuits, the MOSFET turns on when the boost inductor current crosses 0. Because of the resonance between the boost inductor and the parasitic capacitor at the MOSFET drain node, part of the energy stored in the MOSFET junction capacitor can be recovered, reducing switching losses. Furthermore, when the rectified input voltage is less than half of the output voltage, all the energy stored in the MOSFET junction capacitor can be recovered and zero-voltage switching (ZVS) can be realized. By adding an appropriate delay, the MOSFET can be turned on at the valley of its resonating drain voltage (valley switching). In this way, the energy recovery can be maximized and switching loss is minimized.

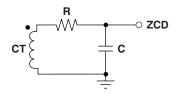

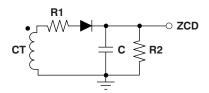

The RC time constant is generally derived empirically, but a good starting point is a value equal to 25% of the resonant period of the drain circuit. The delay can be realized by a simple RC filter, as shown in Figure 26. Because the ZCD pin is internally clamped, a more accurate delay can also be realized by using Figure 27.

Figure 26. Simple RC Delay Circuit

Figure 27. More Accurate Time Delay Circuit

#### **Brownout Protection**

As the power line RMS voltage decreases, RMS input current increases to maintain the output voltage constant for a specific load. Brownout protection prevents the RMS input current from exceeding a safe operating level. Power line RMS voltage is sensed at VINAC. When the voltage applied to VINAC fails to exceed the brownout threshold for the brownout filter time, a brownout condition is detected and both gate drive outputs immediately pull low. During brownout, COMP is actively pulled low. Gate drive outputs remain low until the voltage on VINAC rises above the brownout threshold. After a brownout, the power stage soft-starts as COMP rises.

The brownout detection threshold and its hysteresis are set by the voltage divider ratio and resistor values. This pin also detects the input line range to set the corresponding on-time factors. Both the brownout protection and line range detection are based on VINAC peak voltage; the threshold and hysteresis are also based on line peak voltage. The peak VINAC voltage can be easily translated into RMS value. Suggested resistor values for the voltage divider are 3 M $\Omega$  ±1% from the rectified input voltage to VINAC and 46.4 k $\Omega$  ±1% from VINAC to ground. These resistors set the typical thresholds for RMS line voltages, as shown in Table 2.

**Table 2. Brownout and Range Change Thresholds**

| THRESHOLD | BROWNOUT (RMS) | MAINS SELECT (RMS) |

|-----------|----------------|--------------------|

| Falling   | 65 V           | 150.9 V            |

| Rising    | 79.8 V         | 161.2 V            |

## Failsafe OVP—Output Over-Voltage Protection

FailSafe OVP prevents any single failure from allowing the output to boost above safe levels. Redundant paths for output voltage sensing provide additional protection against output over-voltage. Over-voltage protection is implemented through two independent paths: VSENSE and HVSEN. The converter shuts down if either input senses an over-voltage condition. The output voltage can still maintain a safe level with either loop failure. The device is re-enabled when both sense inputs fall back into the normal range. At that time, the gate drive outputs resume switching under PWM control. Output over-voltage does not cause soft-start and the COMP pin is not discharged during an output over-voltage event.

Copyright © 2007–2008, Texas Instruments Incorporated

#### **Over-Current Protection**

Under certain conditions (such as inrush, brownout recovery, and output overload), the PFC power stage sees large currents. It is critical that the power devices be protected from switching during these conditions.

The conventional current sensing method uses a shunt resistor in series with the MOSFET source to sense the converter current, resulting in multiple ground points and high power dissipation. Furthermore, since no current information is available when the MOSFETs are off, the source resistor current sensing method requires repeated turn-ons of the MOSFETs during over-current conditions. As a result, the converter may temporarily operate in continuous current mode (CCM) and experience failures induced by excessive reverse recovery currents in the boost diode.

The UCC28060 uses a single resistor to continuously sense the total inductor (input) current. This way, turn-on of the MOSFETs is completely avoided when the inductor currents are excessive. The drive to the MOSFETs is inhibited until total inductor current drops to near zero, precluding reverse recovery induced failures (these failures are most likely to occur when the ac line recovers from a brownout condition).

Following an over-current condition, both MOSFETs are turned on in phase when the input current drops to near 0. Because two phase currents are temporarily operating in phase, set the over-current protection threshold to more than twice of each phase maximum current ripple value in order to allow a return to normal operation after an over-current event.

#### **Phase Fail Protection**

The UCC28060 detects failure of one phase by monitoring the sequence of ZCD pulses. During normal two-phase operation, if one ZCD input remains idle for longer than approximately 14 ms while the other ZCD input switches normally, PWMCNTL goes high, indicating that the power stage is not operating correctly. During normal single-phase operation, phase failure is not monitored.

#### **Distortion Reduction**

Because of the resonance between the capacitance present across the drain-source of the switching MOSFET and the boost inductor, conventional transition mode power factor correction circuits may not be able to absorb power from the input line when the input voltage is around 0 V. This limitation results in waveform distortion and increased harmonic distortion. To reduce line current distortion to the lowest possible level, the UCC28060 increases switching MOSFET on-time when input voltage is around 0 V to increase the power absorption and compensate for this effect.

## **Improved Error Amplifier**

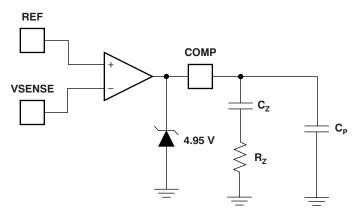

The voltage error amplifier is a transconductance amplifier. Voltage loop compensation is connected from the error amplifier output, COMP, to analog ground, AGND. The recommended compensation network is shown in Figure 28.

Figure 28. Typical Error Amplifier Compensation

To improve the transient response, the error amplifier output current is increased by 100  $\mu$ A when the error ampliput is below 5.815 V, as shown in Figure 29. This increase allows faster charging of the compensation components following sudden load current increases (also refer to Figure 4 in the Typical Characteristics).

Figure 29. Error Amplifier Block Diagram Showing Speed-Up and Latched Soft-Start

## **Open-Loop Protection**

If the feedback loop is disconnected from the device, a current source internal to the UCC28060 pulls the VSENSE pin voltage towards ground. When VSENSE falls below 1.20 V, the device is disabled. When disabled, supply current decreases, and both gate drive outputs and COMP are actively pulled low. The device is re-enabled when VSENSE rises above 1.25 V. At that time, the gate drive outputs begin switching under PWM control.

The device can be externally disabled by grounding the VSENSE pin with an open-drain or open-collector driver. When disabled, device supply current drops and COMP is actively pulled low. When VSENSE is released, the device soft-starts. This disable method forces the device into standby mode and minimizes its power consumption. This feature is particularly useful when standby power is a key design aspect.

If the feedback loop is disconnected from ground, the VSENSE voltage goes high. When VSENSE rises above the over-voltage protection threshold, both gate drive outputs go low, and COMP is actively pulled low. The device is re-enabled when VSENSE falls back into range. At that time, the gate drive outputs begin switching under PWM control. The VSENSE pin is internally clamped to protect the device from damage under this condition.

#### **Soft-Start**

The PWM gradually ramps from zero on-time to normal on-time as the compensation capacitor from COMP to AGND charges from a low level to the final value. This process implements a soft-start, with a time constant set by the output current of the error amplifier and the value of the compensation capacitors. In the event of a brownout, logic disable, or VCC undervoltage fault, COMP is actively pulled low so the PWM soft-starts after this event is cleared. Even if a fault event happens very briefly, soft-start fully discharges the compensation components before resuming operation, ensuring soft-starting. See Figure 29 for details.

## **Light-Load Operation**

As load current decreases, the error amplifier commands less input current by lowering the COMP voltage. If PHB (normally connected to COMP) falls below 0.8 V at low input line (or 1.1 V at high input line), channel B stops switching and channel A on-time doubles to compensate. If COMP falls below 150 mV, channel A also stops switching and the loop enters a hysteretic control mode. The PWM skips cycles to maintain regulation.

#### Command for the Downstream Converter

In the UCC28060, the PWMCNTL pin is used to coordinate the PFC stage with a downstream converter. Through the HVSEN pin, the output voltage is sensed. When the output voltage is within the desired range, the PWMCNTL pin is pulled to ground internally and can be used to enable a downstream converter. The enable threshold and hysteresis can be adjusted independently through the voltage divider ratio and resistor values. The HVSEN pin is also used for the FailSafe over-voltage protection. When designing the voltage divider, make sure this FailSafe over-voltage protection level is set above normal operating levels.

#### **VCC Undervoltage Protection**

VCC must rise above the undervoltage threshold for the PWM to begin functioning. If VCC drops below the threshold during operation, both gate drive outputs and COMP are actively pulled low. VCC must rise above the threshold for PWM function to restart.

## **VCC**

VCC is connected to a bias supply of between 13 V and 21 V. When powered from a poorly-regulated supply, an external zener diode is recommended to prevent excessive current into VCC.

## **DESIGN EXAMPLE**

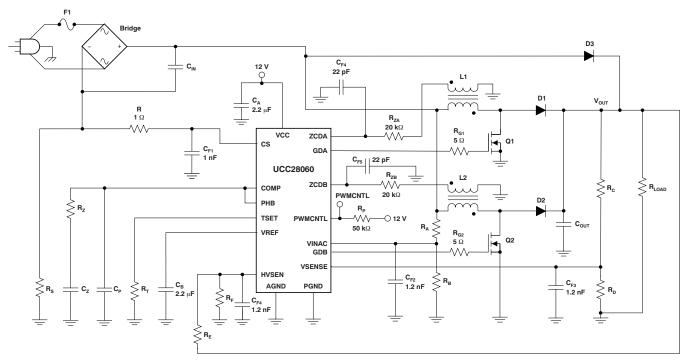

An example of the UCC28060 PFC controller in a two-phase transition mode interleaved PFC pre-regulator is shown in Figure 30.

Figure 30. Typical Transition Mode Interleaved PFC Pre-Regulator

## **Design Goals**

The specifications for this design were chosen based on the power requirements of a 300 W LCD TV. These specifications are shown in Table 3.

**Table 3. Design Specifications**

|                   | PARAMETER                    | MIN                       | TYP | MAX                        | UNIT             |

|-------------------|------------------------------|---------------------------|-----|----------------------------|------------------|

| V <sub>IN</sub>   | RMS input voltage            | 85 (V <sub>IN_MIN</sub> ) |     | 265 (V <sub>IN_MAX</sub> ) | V <sub>RMS</sub> |

| $V_{OUT}$         | Output voltage               |                           | 390 |                            | V                |

| f <sub>LINE</sub> | Line frequency               | 47                        |     | 63                         | Hz               |

| PF                | Power factor at maximum load | 0.90                      |     |                            |                  |

| P <sub>OUT</sub>  |                              |                           |     | 300                        | W                |

| η                 | Full load efficiency         | 0.92                      |     |                            |                  |

| f <sub>MIN</sub>  | Minimum switching frequency  | 45                        |     |                            | kHz              |

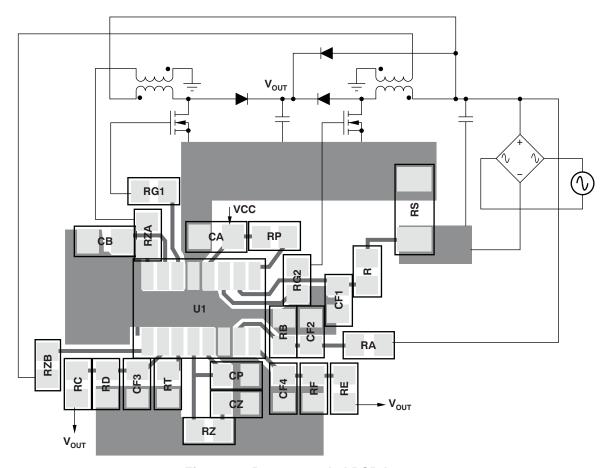

## **Recommended PCB Device Layout**

Interleaved transition-mode PFC system architecture dramatically reduces input and output ripple current, allowing the circuit to use smaller and less expensive filters. To maximize the benefits of interleaving, the input and output filter capacitors should be located after the two phase currents are combined together. Similar to other power management devices, when laying out the printed circuit board (PCB) it is important to use star grounding techniques and keep filter capacitors as close to device ground as possible. To minimize the interference caused by capacitive coupling from the boost inductor, the device should be located at least 1 in (25.4 mm) away from the boost inductor. It is also recommended that the device not be placed underneath magnetic elements. Because of the precise timing requirement, the timing setting resistor  $R_T$  should be put as close as possible to the TSET pin and returned to the analog ground. See Figure 31 for a recommended component layout and placement.

Figure 31. Recommended PCB Layout

#### **Inductor Selection**

The boost inductor is selected based on the inductor ripple current requirements at the peak of low line. Selecting the inductor requires calculating the boost converter duty cycle at the peak of low line (D<sub>PEAK\_LOW\_LINE</sub>), as shown in Equation 9.

as shown in Equation 9.

$$D_{PEAK\_LOW\_LINE} = \frac{V_{OUT} - V_{IN\_MIN} \sqrt{2}}{V_{OUT}} = \frac{390 \text{ V} - 85 \text{ V} \sqrt{2}}{390 \text{ V}} \approx 0.69$$

(9)

The minimum switching frequency of the converter ( $f_{MIN}$ ) occurs at the peak of low line and is set between 25 kHz and 50 kHz to avoid audible noise. For this design example,  $f_{MIN}$  was set to 45 kHz:

$$L1 = L2 = \frac{\eta \times V_{\text{IN\_MIN}}^2 \times D_{\text{PEAK\_LOW\_LINE}}}{P_{\text{OUT}} \times f_{\text{MIN}}} = \frac{0.92(85 \text{ V})^2 \ 0.69}{300 \ \text{W} \times 45 \ \text{kHz}} \approx 340 \ \mu\text{H} \tag{10}$$

The inductor for this design would have a peak current ( $I_{LPEAK}$ ) of 5.4 A, as shown in Equation 11, and an RMS current ( $I_{LRMS}$ ) of 2.2 A, as shown in Equation 12.

$$I_{LPEAK} = \frac{P_{OUT}\sqrt{2}}{V_{IN\_MIN} \times \eta} = \frac{300 \text{ W}\sqrt{2}}{85 \text{ V} \times 0.92} \approx 5.4 \text{ A}$$

(11)

$$I_{LRMS} = \frac{I_{LPEAK}}{\sqrt{6}} = \frac{5.4 \text{ A}}{\sqrt{6}} \approx 2.2 \text{ A}$$

(12)

This converter uses constant on-time  $(T_{ON})$  and zero-current switching (ZCS) to set up the converter timing. Auxiliary windings off of L1 and L2 detect when the inductor currents are 0. Selecting the turns ratio in Equation 13 ensures that there is at least 2 V at the peak of high line to reset the ZCD comparator after every switching cycle.

The turns-ratio of each auxiliary winding is:

$$\frac{N_{P}}{N_{S}} = \frac{V_{OUT} - V_{IN\_MAX}\sqrt{2}}{2 V} = \frac{390 V - 265 V\sqrt{2}}{2 V} \approx 8$$

(13)

## ZCD Resistor Selection (R<sub>ZA</sub>, R<sub>ZB</sub>)

The minimum value of the ZCD resistors is selected based on the internal zener clamp maximum current rating of 3 mA, as shown in Equation 14.

$$R_{ZA} = R_{ZB} \ge \frac{V_{OUT} N_S}{N_P \times 3 \text{ mA}} = \frac{390 \text{ V}}{8 \times 3 \text{ mA}} \approx 16.3 \text{ k}\Omega$$

(14)

In this design the ZCD resistors were set to 20 k $\Omega$ , as shown in Equation 15.

$$R_{ZA} = R_{ZB} = 20 \text{ k}\Omega \tag{15}$$

#### **HVSENSE**

The HVSENSE pin programs the PWMCNTL output of the UCC28060. The PWMCNTL open-drain output can be used to disable a downstream converter while the PFC output capacitor is charging. PWMCNTL starts in high impedance and pulls to ground when the HVSENSE increases above 2.5 V. Setting the point where PWMCNTL becomes active requires a voltage divider from the boost voltage to the HVSEN pin to ground. Equation 16 to Equation 20 show how to set the PWMCNTL pin to activate when the output voltage is within 90% of its nominal value.

$$V_{OUT\_OK} = V_{OUT} \times 0.90 \approx 351 \text{ V}$$

(16)

Resistor  $R_E$  sets up the high side of the voltage divider and programs the hysteresis of the PWMCNTL signal. For this example,  $R_E$  was selected to provide 108 V of hysteresis, as shown in Equation 17.

$$R_{E} = \frac{\text{Hysteresis}}{36 \,\mu\text{A}} = \frac{108 \,\text{V}}{36 \,\mu\text{A}} = 3 \,\text{M}\Omega \tag{17}$$

Resistor R<sub>F</sub> is used to program the PWMCNTL active threshold, as shown in Equation 18.

$$R_{F} = \left( \frac{2.5 \text{ V}}{\frac{\text{V}_{\text{OUT\_OK}} - 2.5 \text{ V}}{\text{R}_{\text{E}}}} - 36 \,\mu\text{A} \right) = \frac{2.5 \text{ V}}{\frac{351 \text{ V} - 2.5 \text{ V}}{3 \text{ M}\Omega}} = 31.185 \,\text{k}\Omega \approx 31.6 \,\text{k}\Omega$$

(18)