# UC1840 UC2840 UC3840

# PROGRAMMABLE, OFF-LINE, PWM CONTROLLER

- ALL CONTROL. DRIVING, MONITORING, AND PROTECTION FUNCTIONS INCLUDED

- LOW-CURRENT, OFF-LINE START CIRCUIT

- FEED-FORWARD LINE REGULATION OVER 4 TO 1 INPUT RANGE

- PWM LATCH FOR SINGLE PULSE PER PE-RIOD

- PULSE-BY-PULSE CURRENT LIMITING PLUS SHUTDOWN FOR OVER-CURRENT FAULT

- NO START-UP OR SHUTDOWN TRANSIENTS

- SLOW TURN-ON AND MAXIMUM DUTY-CY-CLE CLAMP

- SHUTDOWN UPON OVER-OR UNDERVOL-TAGE SENSING

- LATCH OFF OR CONTINUOUS RETRY AFTER

FAULT

- REMOTE. PULSE-COMMANDABLE START/ STOP

- PWM OUTPUT SWITCH USABLE TO 1A PEAK CURRENT

- 1% REFERENCE ACCURACY

- 500 kHz OPERATION

### DESCRIPTION

Although containing most of the features required by all types of switching power supply controllers. the UC1840 family has been optimized for highlyefficient boot-strapped primaryside operation in forward or flyback power converters. Two important features for this mode are a starting circuit which requires little current from the primary input voltage and feed-forward control for constant volt-second operation over a wide input voltage range.

In addition to startup and normal regulating PWM functions, these devices ofter built-in protection from over-voltage, under-voltage, and over-current fault conditions. This monitoring circuitry contains the added features that any fault will initiate a complete shutdown with provisions for either latch off or automatic restart. In the latch-off mode, the controller may be started and stopped with external pulsed or steady-state commands.

Other performance features of these devices include a 1% accurate reference, provision for slowturn-on and duty-cycle limiting, and highspeed pulse-by-pulse current limiting in addition to current fault shutdown.

The UC1840's PWM output stage includes a latch to insure only a single pulse per period and is designed to optimize the turn off of an external switching device by conducting during the "OFF" time with a capability for both high peak current and low saturation voltage. These devices are available in an 18pin dual-in-line plastic or ceramic package.

The UC1840 is characterized for operation over the full military temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C. The UC2840 and UC3840 are designed for operation from  $-25^{\circ}$ C to  $+85^{\circ}$ C and 0 C to  $+70^{\circ}$ C, respectively.

### PIN CONNECTION AND ORDER CODES

| COMPENSATION         | [] ' | 18 ] N  | TURNI VAL AC |

|----------------------|------|---------|--------------|

| START/ UV            | ( )  | · 7 ]   | INV INPUT    |

| OV SENSE             | []]  | 16 ]    | SV REF       |

| STOP                 | [] . | 15]     | •∀; \$UPPLY  |

| RESET                | [ 5  | 14]     | DRIVER BIAS  |

| CURRENT<br>THRESHOLD | [ a. | [ د י   | GROUND       |

| CURRENT SENS         | € [  | 12] 1   | WM OUTPUT    |

| SLOW-START           | ( e  | 11      | V, SENSE     |

| Reda .               | 64   | 10]     | RAMP         |

|                      |      | 1.44.00 |              |

| Туре   | Plastic | Ceramio |

|--------|---------|---------|

| UC1840 | -       | UC1840J |

| UC2840 | UC2840N | UC2840J |

| UC3840 | UC3840N | UC3840. |

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol              | Parameter                                                                                                                                                                           | Test Conditions                                    | Unit                     |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------|

| V,                  | Supply Voltage + V, (pin 15)<br>Voltage Driven<br>Current Driven 100 mA Maximum                                                                                                     | 32<br>Self Limiting                                | V                        |

| Vo                  | PWM Output Volage (pin 12)                                                                                                                                                          | 40                                                 | V                        |

| l <sub>o</sub>      | PWM Output Current, Steady-state (pin 12)                                                                                                                                           | 400                                                | mA                       |

| E <sub>op</sub>     | PWM Output Peak Energy Discharge<br>Driver Bias Current (pin 14)                                                                                                                    | 20<br>–200                                         | μJ<br>mA                 |

| I <sub>o(REF)</sub> | Reference Output Current (pin 16)<br>Slow Start Sink Current (pin 8)<br>V, Sense Current (pin 11)<br>Current Limit Inputs (pin 6, 7)<br>Comparator Inputs (pins 2, 3, 4, 5, 17, 18) | - 50<br>20<br>10<br>- 0.5 to + 55<br>- 0.3 to + 32 | mA<br>mA<br>mA<br>V<br>V |

| Ptot                | Power Dissipation at Tamb = 70 °C                                                                                                                                                   | 1000                                               | mW                       |

| T,                  | Junction Temperature Range                                                                                                                                                          | - 55 to + 150                                      | °C                       |

| T <sub>op</sub>     | Operating Ambient Temperature Range : UC1840<br>UC2840<br>UC3840                                                                                                                    | - 55 to + 125<br>- 25 to + 85<br>0 to + 70         | 2°<br>⊃°<br>2°           |

| Tstg                | Storage Temperature                                                                                                                                                                 | - 65 to + 150                                      | °C                       |

# THERMAL DATA

| Rth j-amb | Thermal Resistance Junction-ambient | Max | 80 | °C/W |

|-----------|-------------------------------------|-----|----|------|

|-----------|-------------------------------------|-----|----|------|

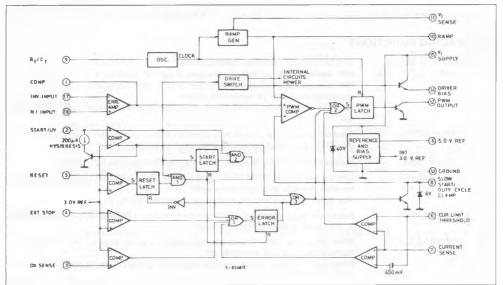

### BLOCK DIAGRAM

### FUNCTIONAL DESCRIPTION

| Name | Function |

|------|----------|

|      |          |

### **PWM CONTROL**

| OSCILLATOR          | Generates a fixed-frequency internal clock from an external $R_{\rm T}$ and $C_{\rm T}$                                                                                                                                        |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | Frequency = $\frac{K_c}{R_T C_T}$ where $K_c$ is a first-order correction factor =                                                                                                                                             |

|                     | 0.3 log (C <sub>T</sub> x 10 <sup>12</sup> ).                                                                                                                                                                                  |

| RAMP GENERATOR      | Develops a linear ramp with a slope defined externally by                                                                                                                                                                      |

|                     | $\frac{dv}{dt} = \frac{\text{sense voltage}}{R_R C_R} , C_R \text{ is normally selected} \leq C_T \text{ and}$                                                                                                                 |

|                     | its value will have some effect upon valley voltage. $C_{R}$ terminal can be used as an input port for current mode control.                                                                                                   |

| ERROR AMPLIFIER     | Conventional operational amplifier for closed-loop gain and phase compensation<br>Low output impedance : unity-gain stable.                                                                                                    |

| REFERENCE GENERATOR | Precision 5.0 V for internal and external usage to 50 mA. Tracking 3.0 V reference for internal usage only with nominal accuracy of $\pm$ 2 % 40 V clamp zener for chip 0. V. protection, 100 mA maximum current.              |

| PWM COMPARATOR      | Generates output pulse wich starts at termination of clock pulse and ends when<br>the ramp input crosses the lowest of two positive inputs.                                                                                    |

| PWM LATCH           | Terminates the PWM output pulse when set by inputs for either the PWM comparator, the pulse-by-pulse current limit comparator, or the error latch. Resets wich each internal clock pulse.                                      |

| PWM OUTPUT SWITCH   | Transistor capable of sinking current to ground wich is off during the PWM<br>on-time and turns on to terminate the power pulse. Current capacity is 400 mA<br>saturated with peak capacitance discharge in excess of one amp. |

### FUNCTIONAL DESCRIPTION (continued)

#### Name

#### Function

# SEQUENCING FUNCTIONS

| START/U. V. SENSE | This comparator performs three functions.<br>With an increasing voltage, it generates a turn-on signal at a start threshold<br>With a decreasing voltage, it generates a U. V. fault signal at a lower level<br>separated by a 200 $\mu$ A hysteresis current.<br>At the U. V. threshold, it also resets the Error Latch if the Reset Latch has been<br>set. |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRIVE SWITCH      | Disables most of the chip to hold internal current consumption low, and Driver<br>Bias OFF, until input voltage reaches start threshold.                                                                                                                                                                                                                     |

| DRIVE BIAS        | Supplies drive current to external power switch to provide turn-on bias.                                                                                                                                                                                                                                                                                     |

| SLOW START        | Clamps low to hold PWM OFF. Upon release, rises with rate controlled by $R_sC_s$ for slow increase of output pulse width.<br>Also used to clamp maximum duty cycle with divider $R_s$ $R_{DC}$ .                                                                                                                                                             |

| START LATCH       | Keeps low input voltage at initial turn-on from being defined as a U. V. fault. Sets at start level to monitor for U. V. fault.                                                                                                                                                                                                                              |

| RESET LATCH       | When reset, this latch insures no reset signal to either Start or Error latches so that first fault will lock the PWM off.<br>When set, this latch resets the Start and Error latches at the U. V. low threshold, allowing a restart.                                                                                                                        |

# **PROTECTION FUNCTIONS**

| ERROR LATCH      | <ul> <li>When set by momentary input, this latch insures immediate PWM shutdown and hold off until reset.</li> <li>Inputs to Error Latch are :</li> <li>a. U. V. low (after turn-on)</li> <li>b. O. V. high</li> <li>c. Step low</li> <li>d. Current Sense 400 mV over threshold</li> <li>Error Latch resets at U. V. threshold if Reset Latch is set.</li> </ul> |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CURRENT LIMITING | Differential input comparator terminates individual output pulses each time sense voltage rises above threshold.<br>When sense voltage rises to 400 mV above threshold, a shutdown signal it sent to Error Latch.                                                                                                                                                 |

# UC1840-UC2840-UC3840

**ELECTRICAL CHARACTERISTICS** (refer to the test circuit. Unless otherwise stated, these specifications apply for T<sub>1</sub> = -55 to + 125 °C for the UC1840. - 25 °C to + 85 °C for the UC2840 and 0 to + 70 °C for the UC3840; V<sub>1</sub> = 20 V, R<sub>T</sub> = 20 KΩ, C<sub>T</sub> = 0.001µF, C<sub>R</sub> = 0.001 µF, current limit threshold = 200 mV)

| Symbol | Parameter | Test Conditions |      | JC184<br>JC284 | -    | l    | JC384 | 0    | Unit |  |

|--------|-----------|-----------------|------|----------------|------|------|-------|------|------|--|

|        |           |                 | Min. | Typ.           | Max. | Min. | Typ.  | Max. |      |  |

#### POWER INPUTS

| IST   | Start-up Current       | $V_1 = 30 \text{ V}$ . Pin 2 = 2.5 V.<br>T <sub>1</sub> = 25 °C |    | 4     | 5.5   |    | 4     | 5.5   | mA   |

|-------|------------------------|-----------------------------------------------------------------|----|-------|-------|----|-------|-------|------|

|       | *Start-up Current T.C. | V <sub>1</sub> = 30 V, Pin 2 = 2.5 V                            |    | - 0.1 | - 0.2 |    | - 0.1 | - 0.2 | %/°C |

| li li | Operating Current      | $V_i$ = 30 V, Pin 2 = 3.5 V                                     | 5  | 10    | 15    | 5  | 10    | 15    | mA   |

| Vsov  | Supply O.V. Clamp      | I, = 20 m A                                                     | 33 | 40    | 45    | 33 | 40    | 48    | V    |

#### **REFERENCE SECTION**

| VREF                        | Reference Voltage   | T <sub>1</sub> = 25 °C                       | 4.95 | 5    | 5.05  | 4.9 | 5    | 5.1   | V     |

|-----------------------------|---------------------|----------------------------------------------|------|------|-------|-----|------|-------|-------|

| AVREF                       | Line Regulation     | V, = 8 to 30 V                               |      | 10   | 15    |     | 10   | 20    | mV    |

| AVREF                       | Load Regulation     | $I_L = 0$ to 20mA                            |      | 10   | 20    |     | 10   | 30    | mV    |

| $\Delta V_{REF}/\Delta T^*$ | Temperature Coeff.  | Over Op. Temp. Range                         |      |      | ± 0.4 |     |      | ± 0.4 | mV/°C |

| Isc                         | Short Circuit Curr. | V <sub>REF</sub> = 0, T <sub>j</sub> = 25 °C |      | - 80 | - 100 |     | - 80 | - 100 | mA    |

### OSCILLATOR

| fs                  | Nominal Frequency   | T <sub>1</sub> = 25 °C                         | 47  | 50  | 53    | 45  | 50  | 55    | KHz  |

|---------------------|---------------------|------------------------------------------------|-----|-----|-------|-----|-----|-------|------|

|                     | Voltage Stability   | V, = 8 to 30 V                                 |     | 0.5 | 1     |     | 0.5 | 1     | %    |

|                     | *Temperature Coeff. | Over Op. Temp. Range                           |     |     | ± 0.8 |     |     | ± 0.8 | %/°C |

| f <sub>s(max)</sub> | Maxim. Frequency    | R <sub>T</sub> = 2 KΩ, C <sub>T</sub> = 330 pF | 500 |     |       | 500 |     |       | KHz  |

### RAMP GENERATOR

| Ramp Current Min. | I <sub>SENSE</sub> = - 10 μA |       | - 11   | - 14 |      | - 11  | -14 | μA |

|-------------------|------------------------------|-------|--------|------|------|-------|-----|----|

| Ramp Current Max. | ISENSE = 1 mA                | - 0.9 | - 0.95 |      | -0.9 | -0.95 |     | mA |

| Ramp Valley       |                              | 0.3   | 0.5    | 0.7  | 0.3  | 0.5   | 0.7 | V  |

| Ramp Peak         | Clamping Level               | 3.9   | 4.2    | 4.5  | 3.9  | 4.2   | 4.5 | V  |

# ELECTRICAL CHARACTERISTICS (continued)

| Symbol | Parameter | Test Conditions |      | JC184<br>JC284 |      | l    | JC384 | 0    | Unit |

|--------|-----------|-----------------|------|----------------|------|------|-------|------|------|

|        |           |                 | Min. | Тур.           | Max. | Min. | Тур.  | Max. |      |

### ERROR AMPLIFIER

| Vos | Input Offset Voltage                              | V <sub>CM</sub> = 5 V                  |     | 0.5 | 5    |     | 2   | 10   | mV   |

|-----|---------------------------------------------------|----------------------------------------|-----|-----|------|-----|-----|------|------|

| Гb  | Input Bias Current                                |                                        |     | 0.5 | 2    |     | 1   | 5    | μA   |

| los | Input Offset Current                              |                                        |     |     | 0.5  |     |     | 0.5  | μA   |

| Gv  | Open Loop Gain                                    | $\Delta V_o = 1$ to 3 V                | 60  | 66  |      | 60  | 66  |      | dB   |

|     | Output Swing (max<br>Out < Ramp Peak –<br>100 mV) | Minimum Total Range                    | 0.3 |     | 3.5  | 0.3 |     | 3.5  | V    |

| CMR | Common Mode<br>Rejection                          | $V_{CM} = 1.5$ to 5.5 V                | 70  | 80  |      | 70  | 80  |      | dB   |

| SVR | Supply Voltage<br>Rejection                       | V <sub>1</sub> = 8 to 30 V             | 40  | 50  |      | 40  | 50  |      | dB   |

| Isc | Short Circuit Current                             | V <sub>comp</sub> = 0V                 |     | - 4 | - 10 |     | - 4 | - 10 | mA   |

| B*  | Gain Bandwidth                                    | $T_1 = 25 \ ^{\circ}C, \ G_V = 0 \ dB$ | 1   | 2   |      | 1   | 2   |      | MHz  |

| SR* | Slew Rate                                         | $T_1 = 25 ^{\circ}C, G_V = 0  dB$      |     | 0.8 |      |     | 0.8 |      | V/µs |

# **PWM SECTION**

|                     | *Continuous Duty<br>Cycle Range<br>(other than zero) | Min. Total Cont. Range<br>Ramp Peak < 4.2 V                              | 5 |     | 95  | 5 |     | 95  | %  |

|---------------------|------------------------------------------------------|--------------------------------------------------------------------------|---|-----|-----|---|-----|-----|----|

| V <sub>o(sat)</sub> | Output Saturation                                    | I <sub>0</sub> = 20 mA                                                   |   | 0.2 | 0.4 |   | 0.2 | 0.4 | V  |

| V <sub>o(sat)</sub> | Output Saturation                                    | l <sub>o</sub> = 200 mA                                                  |   | 1.7 | 2.2 |   | 1.7 | 2.2 | V  |

| IOL                 | Output Leakage                                       | $V_{0} = 40 V$                                                           |   | 0.1 | 10  |   | 0.1 | 10  | μA |

| τ <sub>d</sub>      | *Comparator Delay                                    | Pin 8 to pin 12<br>T <sub>1</sub> = 25 °C, R <sub>L</sub> = 1 K $\Omega$ |   | 300 | 500 |   | 300 | 500 | ns |

### SEQUENCING FUNCTIONS

| VT             | Comparator<br>Threshold                      | Pins 2, 3, 4, 5                       | 2.8 | 3     | 3.2  | 2.8 | 3     | 3.2  | V  |

|----------------|----------------------------------------------|---------------------------------------|-----|-------|------|-----|-------|------|----|

| I <sub>b</sub> | Input Bias Current                           | Pins 3, 4, 5 = 0V                     |     | - 1   | - 3  |     | -1    | -3   | μA |

|                | Start/UV Hysteresis<br>Current               | Pin 2 = 2.5 V, $T_j = 25 \ ^{\circ}C$ | 120 | 180   | 240  | 120 | 180   | 240  | μA |

|                | Input Leakage                                | V. = 20 V                             |     | 0.1   | 10   |     | 0.1   | 10   | μA |

|                | Driver Bias Saturation<br>Voltage<br>VIN-VOH | I <sub>B</sub> = - 50 mA              |     | 2     | 3    |     | 2     | 3    | V  |

|                | Driver Bias Leakage                          | $V_B = 0V$                            |     | - 0.1 | - 10 |     | - 0.1 | - 10 | μA |

|                | Slow-start Saturation                        | $I_s = 2 \text{ mA}$                  |     | 0.2   | 0.5  |     | 0.2   | 0.5  | V  |

|                | Slow-start Leakage                           | $V_{s} = 4.5 V$                       |     | 0.1   | 2    |     | 0.1   | 2    | μA |

### ELECTRICAL CHARACTERISTICS (continued)

| s | ymbol | Parameter | Test Conditions |      | JC184<br>JC284 |      | ι    | JC384 | 0    | Unit |  |

|---|-------|-----------|-----------------|------|----------------|------|------|-------|------|------|--|

|   | -     |           |                 | Min. | Typ.           | Max. | Min. | Тур.  | Max. |      |  |

### CURRENT CONTROL

|                  | Current Limit Offset       |                                                                  |       | 0   | 5   |       | 0   | 10  | mV |

|------------------|----------------------------|------------------------------------------------------------------|-------|-----|-----|-------|-----|-----|----|

|                  | Current Shutdown<br>Offset |                                                                  | 340   | 400 | 440 | 340   | 400 | 440 | mV |

| l <sub>b</sub>   | Input Bias Current         | Pin 7 = 0V                                                       |       | - 2 | - 5 |       | - 2 | - 5 | μA |

|                  | *Common mode<br>Range      |                                                                  | - 0.3 |     | 3   | - 0.3 |     | 3   | V  |

| τ <sub>d</sub> ° | Current Limit Delay        | $T_j = 25 \text{ °C. Pin 7 to } 12$<br>$R_L = 1 \text{ K}\Omega$ |       | 200 | 400 |       | 200 | 400 | ns |

\* Guaranteed by design. Not 100 % tested in production.

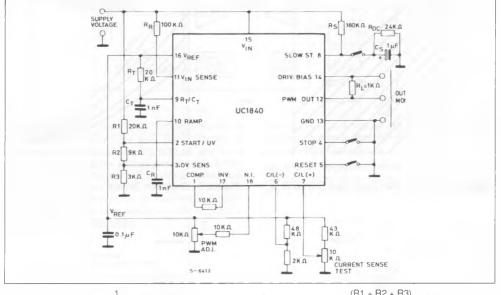

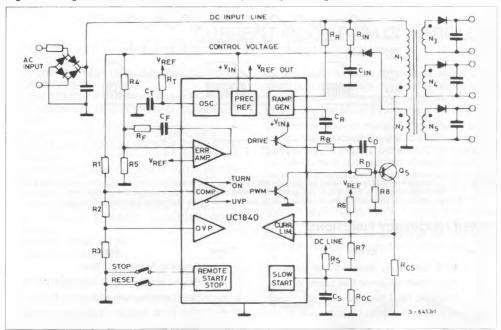

#### Figure 1 : Open Loop Test Circuit.

Nominal frequency =  $\frac{1}{R_T C_T}$  = 50 kHz Start voltage = 3  $\frac{(R1 + R2 + R3)}{R2 + R3}$  + 0.2 R1 = 12 V U.V. fault voltage = 3  $\frac{(R1 + R2 + R3)}{R2 + R3}$  = 8 V O.V. fault voltage = 3  $\frac{(R1 + R2 + R3)}{R3}$  = 32 V Current limit = 200mV Current fault voltage = 600mV Duty cycle clamp = 50%

### UC1840-UC2840-UC3840

Figure 2 : Start U.V. Hysteresis Current.

Figure 4 : Oscillator Frequency.

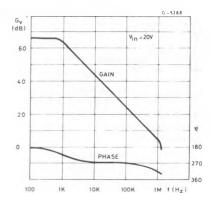

Figure 6 : Error Amplifier Open-loop Gain and Phase.

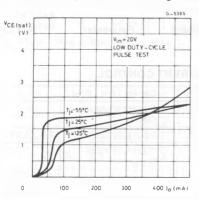

Figure 3 : PWM Output Saturation Voltage.

Figure 5 : PWM Output Minimum Pulse Width.

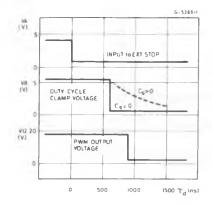

Figure 7 : Shutdown Timing.

### **APPLICATION INFORMATION**

Figure 8 : Programmable PWM Controller in a Simplified Flyback Regulator.

In this application [see Fig.8] complete control is maintained on the primary side. Control power is provided by  $R_{IN}$  and  $C_{IN}$  during start-up, and by a primary-referenced low voltage winding. N2, for efficient operation after start. The error amplifier loop is closed to regulate the DC voltage from N2 with other outputs following through their magnetic coupling - a task made even easier with the UC1840's feed-forward line regulation.

The UC1840 will readily accept digital start/stop commands transmitted from the secondary side by means of optical couplers.

Not shown are protective snubbers or additional interface circuitry which may be required by the choice of the high-voltage switch. Qs. or the application

# UC1840-UC2840-UC3840

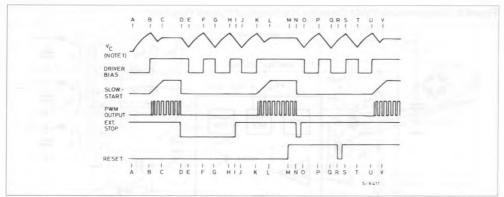

Figure 9 : Power Sequencing Functions.

Notes: 1. VC represents an analog of the output voltage generated by a primary-referenced secondary winding of the power transformer. It is the voltage monitored by the start/U.V. comparator and, in most cases, is the supply voltage. Vi. for the UC1840

2. Although input to External Stop, Pin 4, is shown, results are the same for any fault input which sets the Error Latch.

| Time   | Event                                                |

|--------|------------------------------------------------------|

| А      | Initial Turn-on, Vc Rises with Light Load            |

| В      | Start Threshold. Driver Bias Loads Vc                |

| С      | Operating PWM Regulates V <sub>c</sub>               |

| D      | Stop Input Sets Error Latch Turning off<br>PWM       |

| E      | U. V. Low Threshold. Error Latch Remain Set          |

| F      | Start Turns on Driver Bias Bus Error Latch Still Set |

| G<br>H | $\rm V_{c}$ and Driver Bias Continue to Cycle        |

| 1      | Stop Command Removed                                 |

| J      | Error Latch Reset at U. V. Low Threshold             |

| К      | Start Threshold Now Removes Slow-start Clam          |

#### POWER FREQUENCY FUNCTIONS

| Time   | Event                                                 |

|--------|-------------------------------------------------------|

| L      | Return to Normal Run State                            |

| М      | Reset Latch Set Signal Removed                        |

| N      | Error Latch Set with Momentary Fault                  |

| 0      | Error Latch does not reset as Reset Latch is reset    |

| P<br>Q | $V_{\rm c}$ and Driver Bias Recycle with no Turn-on   |

| R      | Reset Latch Set is Set with Momentary<br>Reset Signal |

| S      | Vc must Complete Cycle to Turn-on                     |

| Т      | Start and Error Latches Reset                         |

| U      | Normal Start Initiated                                |

| V      | Return to Normal Run State                            |