### National Semiconductor

# DP117-X/DP117-XR/ $\mu$ A117-X/ $\mu$ A117-XR Series Winchester Disk Read/Write Preamplifiers

#### **General Description**

The DP117-X/DP117-XR,  $\mu$ A117-X/ $\mu$ A117-XR Series High Performance Read/Write Preamplifiers are intended for use in Winchester disk drives which employ center tapped ferrite or manganese-zinc read/write heads. The circuit can interface with up to eight read/write heads which makes it ideal for multi-platter disk drive designs. Designed to reside in the Head/Disk Assembly (HDA) of Winchester disk drives, the Read/Write Preamplifiers provide termination, gain, and output buffering for the disk heads as well as switched write current. Certain write fault conditions are detected and reported to protect recording integrity. The parts are available with internal damping resistor (DP117-R) and without internal damping resistor (DP117).

#### Features

- Wide bandwidth, high gain, low noise

- Up to eight read/write channels

- Internal write fault condition detection

- 5.0V and 12V power supply voltages

- Independent read and write data lines

- TTL control and data logic levels

- Externally programmable write current

- Available with internal damping resistor

- Compatible with SSI 117 family

#### Part Selection

| Device Code | Channels |

|-------------|----------|

| μA117-2     | 2        |

| μA117-4     | 4        |

| μA117-6     | 6        |

#### Absolute Maximum Ratings All voltages referenced to GND

| If Military/Aerospace specified      | ••••••                           | DC Supply Voltage                         |                                 |

|--------------------------------------|----------------------------------|-------------------------------------------|---------------------------------|

| please contact the National          |                                  | (V <sub>DD1</sub> )                       | -0.3V to +14V                   |

| Office/Distributors for availability | y and specifications.            | (V <sub>DD2</sub> )                       | -0.3V to +14V                   |

| Storage Temperature Range            |                                  | (V <sub>CC</sub> )                        | -0.3V to +6.0V                  |

| Ceramic                              | -65°C to +175°C                  | Digital Input Voltage Range               |                                 |

| Plastic                              | -65°C to +150°C                  | (V <sub>IN</sub> )                        | -0.3V to V <sub>CC</sub> + 0.3V |

| Operating Junction Temperature Ra    | inge +25°C to +135°C             | Head Port Voltage Range                   |                                 |

| Lead Temperature                     |                                  | (V <sub>H</sub> )                         | -0.3V to V <sub>DD</sub> + 0.3V |

| Ceramic (Soldering, 60 seconds)      | 300°C                            | WUS Port Voltage Range                    |                                 |

| Plastic (Soldering, 10 seconds)      | 265°C                            | (V <sub>WUS</sub> )                       | -0.3V to +14V                   |

| Internal Power Dissipation (Notes 1  | & 2)                             | Write Current (I <sub>W</sub> )           | 60 mA                           |

| 28L-Ceramic DIP                      | 2.50W                            | Output Current (In)                       |                                 |

| 24L-Ceramic DIP                      | 1.95W                            | RDX, RDY                                  | — 10 mA                         |

| 18L-Ceramic DIP                      | 1.58W                            | VCT                                       | —60 mA                          |

| 24L-Brazed Flatpak                   | 0.97W                            | WUS                                       | + 12 mA                         |

| 24L-Ceramic Flatpak                  | 0.90W                            |                                           |                                 |

| 28L-PLCC                             | 1.39W                            | Recommended Opera                         | nting                           |

| Supply Voltage (V <sub>CC1</sub> )   | 6.0V                             | Conditions                                |                                 |

| Supply Voltage (V <sub>CC2</sub> )   | 15V                              | DC Supply Voltage                         |                                 |

| Write Current (IWC)                  | 70 mA                            | (V <sub>DD1</sub> )                       | 12V ±10%                        |

| Input Voltage Range                  |                                  | (V <sub>DD2</sub> )                       | 6.5V to VDD1                    |

| Head Select (HS0, HS1, HS2)          | -0.4V to V <sub>CC1</sub> + 0.3V | (V <sub>CC</sub> )                        | 5.0V ± 10%                      |

| Write Current (WC)                   |                                  | Head Inductance (Lh)                      | 5.0 μH to 15 μH                 |

| Voltage in read and idle modes.      |                                  | Damping Resistor (External) (RD)          | 500Ω to 2000Ω                   |

| (Write mode must be current          |                                  | RCT Resistor (RCT)                        | $90\Omega \pm 5.05 (1/2W)$      |

| limited to -70 mA)                   | -0.3V to V <sub>CC1</sub> + 0.3V | . ,                                       |                                 |

| Chip Select (CS)                     | -0.4V to V <sub>CC1</sub> + 0.3V | Write Current (I <sub>W</sub> )           | 25 mA to 50 mA                  |

| Read/Write (R/W)                     | -0.4V to V <sub>CC1</sub> + 0.3V | RDX, RDY Output Current (I <sub>O</sub> ) | 0 μA to 100 μA                  |

|                                      |                                  |                                           |                                 |

Note 2: Ratings apply to ambient temperature at 25°C. Above this temperature, derate the 28L-Ceramic DIP at 16.7 mW/°C, the 24L-Ceramic DIP at 13 mW/°C, the 18L-Ceramic DIP at 10.5 mW/°C, the 24L-Brazed Flatpak at 6.5 mW/°C, the 24L-Ceramic Flatpak at 6.0 mW/°C, and the 28L-PLCC at 11.2 mW/°C.

#### DC Characteristics $25^{\circ}C \le T_J < 125^{\circ}C$ , $V_{DD1} = 12V$ , $V_{CC} = 5.0V$ , unless otherwise specified

| Symbol          |            | Parameter          | Con                       | ditions                                                                       | Min  | Max                 | Unite   |

|-----------------|------------|--------------------|---------------------------|-------------------------------------------------------------------------------|------|---------------------|---------|

| lcc             | C Supply C | urrent             | Read/Idle Mod             | Read/Idle Mode                                                                |      | 25                  | mA      |

|                 |            |                    | Write Mode                |                                                                               |      | 30                  | - The v |

| IDD             | Supply Cu  | urrent             | idle Mode                 |                                                                               |      | 25                  |         |

|                 |            |                    | Read Mode                 |                                                                               |      | 50                  | mA      |

|                 |            |                    | Write Mode                | Write Mode                                                                    |      | 30 + I <sub>W</sub> |         |

| PC              | Power Co   | Power Consumption  |                           | Idle Mode                                                                     |      | 400                 |         |

|                 |            |                    |                           | Read Mode                                                                     |      | 600                 |         |

|                 |            |                    |                           | Write Mode,<br>$I_W = 50 \text{ mA}$<br>RCT = 90 $\Omega$<br>RCT = 0 $\Omega$ |      | 850<br>1050         | mW      |

| VIL             | Digital    | Input Voltage LOW  |                           |                                                                               | -0.3 | 0.8                 | V       |

| VIH             | Inputs     | Input Voltage HIGH |                           |                                                                               | 2.0  | $V_{\rm CC}$ + 0.3  | V       |

| կլ              | ]          | Input Current LOW  | $V_{IL} = 0.8V$           |                                                                               | -0.4 |                     | mA      |

| кн              |            | Input Current HIGH | V <sub>IH</sub> = 2.0V    |                                                                               |      | 100                 | μΑ      |

| V <sub>OL</sub> | WUS Out    | put                | $I_{OL} = 8.0 \text{ mA}$ |                                                                               |      | 0.5                 | V       |

| юн              | ]          |                    | V <sub>OH</sub> = 5.0V    |                                                                               |      | 100                 | μA      |

| V <sub>CT</sub> | Center Ta  | Center Tap Voltage |                           |                                                                               | 4    | l.0 (typ)           | V       |

|                 |            |                    | Write Mode                |                                                                               | 6    | 6.0 (typ)           | v       |

| Write Characteristics $v_{DD1} = 12V$ , $v_{CC} = 5.0V$ , $I_W = 45$ mA, Lh = 10 $\mu$ H, f (I     | Data) = 5.0 MHz, CL (RDX, RDY) |

|----------------------------------------------------------------------------------------------------|--------------------------------|

| $\leq$ 20 pF, R <sub>D EXT</sub> = 750 $\Omega$ or R <sub>D INT</sub> , unless otherwise specified | ÷.                             |

| Parameter                               | Conditions                 | Min | Max   | Units   |

|-----------------------------------------|----------------------------|-----|-------|---------|

| Write Current Range                     |                            | 10  | 50    | mA      |

| Write Current Constant "K"              |                            | 133 | 147   | v       |

| Differential Head Voltage Swing         |                            | 5.7 |       | V (pk)  |

| Unselected Differential<br>Head Current |                            |     | 2.0   | mA (pk) |

| Differential Output Capacitance         |                            |     | 15    | pF      |

| Differential Output Resistance          | Without Internal Resistors | 10k |       | Ω       |

| - <u>-</u> -                            | With Internal Resistors    | 538 | 1.0k  | 46      |

| WDI Transition Frequency                | WUS = LOW                  | 400 | (typ) | kHz     |

| Iwc to Head Current Gain                |                            | 18  | (typ) | mA/mA   |

## **Read Characteristics** $V_{DD1} = 12V$ , $V_{CC} = 5.0V$ , $Lh = 10 \mu$ H, f (Data) = 5.0 MHz, CL (RDX, RDY) $\leq 20 p$ F, (V<sub>in</sub> is referenced to V<sub>CT</sub>), R<sub>D EXT</sub> = 750 $\Omega$ or R<sub>D INT</sub>, unless otherwise specified

| Parameter                      | Conditions                                                                                                                      |                            | Min  | Max  | Unit   |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|------|--------|

| Differential Voltage Gain      | $V_{IN} = 1.0 \text{ mV}_{p-p}$ at 300 kHz<br>RL (RDX), RL (RDY) = 1.0 k $\Omega$                                               |                            | 80   | 120  | v/v    |

| Dynamic Range                  | Input Voltage, V <sub>I</sub> , where gain falls by 10%.<br>V <sub>IN</sub> = V <sub>I</sub> + 0.5 mV <sub>p-p</sub> at 300 kHz |                            | -2.0 | 2.0  | mV     |

| Bandwidth (-3 dB)              | Zs  < 5.0Ω, V <sub>IN</sub>                                                                                                     | $= 1.0 \text{ mV}_{p-p}$   | 30   |      | MHz    |

| Input Noise Voltage            | BW = 15 MHz, Lh = 0, Rh = 0                                                                                                     |                            |      | 2.1  | nV/√H: |

| Differential Input Capacitance | f = 5.0 MHz                                                                                                                     |                            |      | 23   | рF     |

| Differential Input Resistance  | f = 5.0 MHz                                                                                                                     | Without Internal Resistors | 2k   |      | Ω      |

| 11                             |                                                                                                                                 | With Internal Resistors    | 440  | 850  | 32     |

| Input Bias Current             |                                                                                                                                 |                            |      | 45   | μΑ     |

| Common Mode Rejection Ratio    | $V_{CM} = V_{CT} + 100 \text{ mV}_{p-p} \text{ at } 5.0 \text{ MHz}$                                                            |                            | 50   |      | dB     |

| Power Supply Rejection Ratio   | 100 mV <sub>p-p</sub> at 5.0 MHz on V <sub>DD1</sub> , V <sub>DD2</sub> or V <sub>CC</sub>                                      |                            | 45   |      | dB     |

| Channel Separation             | Unselected Channels: $V_{IN} = 100 \text{ mV}_{p-p}$ at 5.0 MHz and Selected Channel: $V_{IN} = 0 \text{ mV}_{p-p}$             |                            | 45   |      | dB     |

| Output Offset Voltage          |                                                                                                                                 |                            | -480 | 480  | m۷     |

| Common Mode Output Voltage     |                                                                                                                                 |                            | 5.0  | 7.0  | V      |

| Single Ended Output Resistance | f = 5.0 MHz                                                                                                                     |                            |      | 35   | Ω      |

| Internal Damping Resistor      |                                                                                                                                 |                            | 560  | 1070 | Ω      |

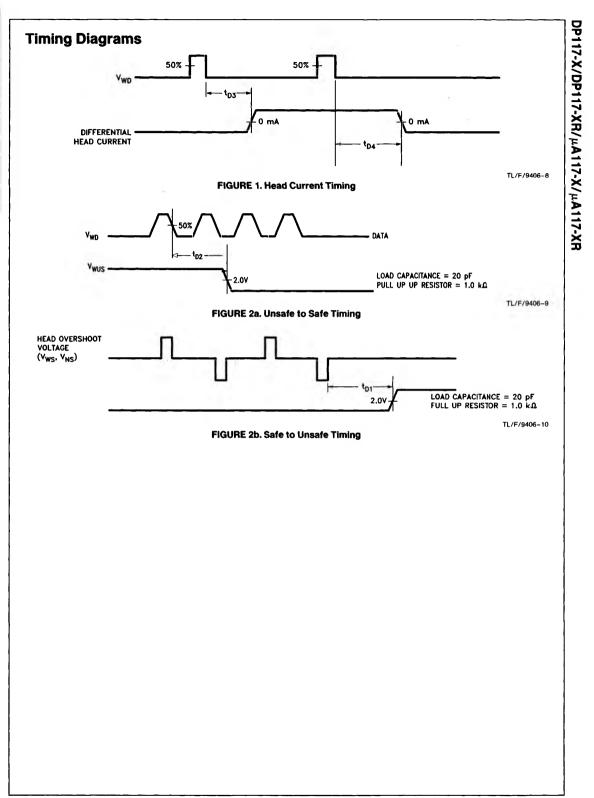

| Symbol            | Parameter                  | Conditions                                                                              | Min | Max | Units |  |

|-------------------|----------------------------|-----------------------------------------------------------------------------------------|-----|-----|-------|--|

| R/W               | R/W to Write               | Delay to 90% of Write Current                                                           |     | 1.0 | ( ·   |  |

|                   | R/W to Read                | Delay to 90% of 100 mV, 10 MHz Read Signal<br>Envelope or to 90% Decay of Write Current |     | 1.0 | .0 μs |  |

| CS                | CS to Select               | Delay to 90% of Write Current or to 90% of<br>100 mV, 10 MHz Read Signal Envelope       |     | 1.0 | μs    |  |

|                   | CS to Unselect             | Delay to 90% Decay of Write Current                                                     |     | 1.0 |       |  |

| HS0<br>HS1<br>HS2 | to Any Head                | Delay to 90% of 100 mV, 10 MHz Read<br>Signal Envelope                                  |     | 1.0 | μs    |  |

| wus               | Safe to Unsafe—TD1         | $I_W = 50 \text{ mA}$                                                                   | 1.6 | 8.0 | μs    |  |

|                   | Unsafe to Safe—TD2         | $I_W = 20 \text{ mA}$                                                                   |     | 1.0 | μ0    |  |

| Head<br>Current   | Propagation Delay—TD3, TD4 | D4 Lh = 0 $\mu$ H, Rh = 0 $\Omega$<br>from 50% Points                                   |     | 25  |       |  |

|                   | Asymmetry                  | WDI has 50% Duty Cycle and<br>1 ns Rise/Fall Time                                       | 2   |     | ns    |  |

|                   | Rise/Fall Time             | 10%-90% Points                                                                          | 20  |     | 1     |  |

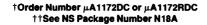

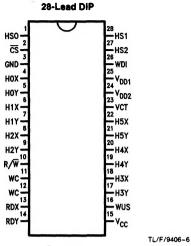

#### **Connection Diagrams**

#### Top View

TL/F/9406-1

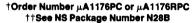

#### 22-Lead Molded DIP

#### **Top View**

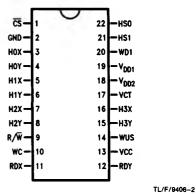

†Order Number μA1174PC or μA1174RPC ††See NS Package Number N22A

†For most current order information, contact your local sales office. ††For most current package information, contact product marketing.

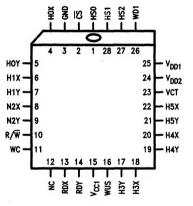

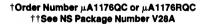

#### Connection Diagrams (Continued)

**Top View**

28-Lead PLCC

Top View

+For most current order information, contact your local sales office. ++For most current package information, contact product marketing. TL/F/9406-5

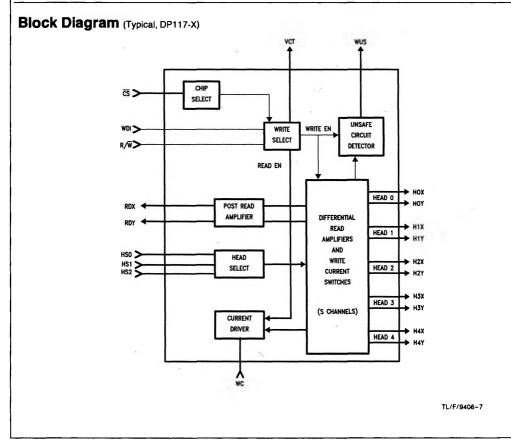

#### **Functional Description**

In the Write mode, the DP117-X/DP117-XR,  $\mu$ A117-X/  $\mu$ A117-XR Series accepts TTL compatible write data pulses on the WDI lead. On the falling edge of each write data pulse, a current transition is made in the selected head. Head selection is accomplished via TTL input signals: HS0, HS1, HS2 (see Table II). Internal circuitry senses the following conditions:

- 1. Absence of data transitions.

- 2. Open circuit head connection.

- 3. Absence of write current.

- 4. Short circuit head connection.

- 5. Idle or read mode.

#### **Pin Descriptions**

Any or all of the above conditions would result in a high level on the write unsafe (WUS) output signal.

During read operations, the DP117-X amplifies the differential voltages appearing across the selected R/W head lead and applies the amplified signal differentially to data lines RDX and RDY.

| Lead                     | Name                           | Function                                                                                                                                                                                                                                                                            |

|--------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS                       | Chip Select                    | Chip Select High disables the read/write function of the device and forces idle mode. (TTL)                                                                                                                                                                                         |

| R/W                      | Read/Write Select              | A Logic High places the devices in read mode and a Logic Low forces write<br>mode. Refer to Table I. (TTL)                                                                                                                                                                          |

| H0X, Y<br>through H5X, Y | Read/Write Head<br>Connections | The DP117 has five pairs of read/write connections. The X and Y phases are made consistent with the read output, RDX and RDY, phases. (Differential)                                                                                                                                |

| RDX, Y                   | Read Data Outputs              | The chip has one pair of read data outputs which is multiplexed to the appropriate head connections. (Differential)                                                                                                                                                                 |

| HS0<br>through HS2       | Head Select Inputs             | The eight read/write heads are addressed with the head select inputs. Refer to Table II. (TTL)                                                                                                                                                                                      |

| WC                       | Write Current Input            | This lead sets the current level for the write mode. An external resistor is<br>connected from this lead to ground, and write current is determined by the value<br>of this resistor divided into the write current constant K, which is typically 140V.                            |

| WDI                      | Write Data Input               | The write data input toggles the write current between the X and Y selected head<br>connections. Write current is switched on the negative edge of WDI. The initial<br>direction for write current is the X side of the switch and is set upon entering read<br>or idle mode. (TTL) |

| V <sub>DD2</sub>         | Resistor Center Tap            | In some versions (determined by lead availability) of the DP117-X series, a resistor may be connected between RCT and $V_{DD1}$ to reduce internal power dissipation. If this resistor is not used, RCT must be connected externally to $V_{DD1}$ .                                 |

| VCT                      | Center Tap Voltage             | The center tap output provides bias voltage for the head inputs in read and write<br>mode. It should be connected to the center tap of the read/write heads.                                                                                                                        |

| WUS                      | Write Unsafe                   | A high logic level at the write unsafe output indicates a fault condition during<br>write. Write unsafe will also be high during read and idle mode. (Open collector)                                                                                                               |

#### TABLE I. Read/Write Select

| Operating Modes |                |       |  |

|-----------------|----------------|-------|--|

| Chip Select CS  | Read/Write R/W | Mode  |  |

| 1               | X              | idle  |  |

| 0               | 1              | Read  |  |

| 0               | 0              | Write |  |

#### **TABLE II. Head Select Inputs**

|     | Head Selection |     |                        |  |  |  |

|-----|----------------|-----|------------------------|--|--|--|

| HS0 | HS1            | HS2 | Head Selected (Note 1) |  |  |  |

| 0   | 0              | 0   | 0                      |  |  |  |

| 1   | 0              | 0   | 1                      |  |  |  |

| 0   | 1              | 0   | 2                      |  |  |  |

| 1   | 1              | 0   | 3                      |  |  |  |

| 0   | 0              | 1   | 4                      |  |  |  |

| 1   | 0              | 1   | 5                      |  |  |  |

Note 1: If selected head is beyond the capacity of the DP117-X model, the open input condition on the selected input will be reported as an unsafe level at the WUS output.