SLVS082A - APRIL 1994 - REVISED SEPTEMBER 1994

| <ul> <li>Single-Chip Switching-Power-Supply<br/>Control With Limited External Components</li> </ul>                                 | N PACKAGE<br>(TOP VIEW)                                            |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|

| Built-In PWM Control Circuit                                                                                                        |                                                                    |  |  |  |  |

| <ul> <li>Open-Collector Output for Direct Drive of<br/>Transformer</li> </ul>                                                       | REF [ 1 20] CPG<br>PGO [ 2 19] PGI                                 |  |  |  |  |

| Variable Dead-Time Control                                                                                                          | SVP5 3 18 EA+<br>SVP12 4 17 EA-                                    |  |  |  |  |

| <ul> <li>Overvoltage and Undervoltage Detection<br/>and Latch-Up for Each Supply Voltage:<br/>5 V, 12 V, -5 V, and -12 V</li> </ul> | CPR [ 5 16 ] EAO<br>DT [ 6 15 ] V <sub>CC</sub><br>CUV [ 7 14 ] SC |  |  |  |  |

| System Overcurrent Protection                                                                                                       | SVN5 8 13 CT                                                       |  |  |  |  |

| • Wide Supply Range From 7 V to 40 V                                                                                                | SVN12 🛛 9 12 🗋 D2                                                  |  |  |  |  |

| Power-Good Indicator Function                                                                                                       | D1 [ 10 11] GND                                                    |  |  |  |  |

## description

The TPS5206CN is a bipolar monolithic integrated circuit designed for push-pull-type switching-power-supply (SPS) control in desktop PC applications. It offers pulse-width-modulation (PWM) control and power-supply supervisor functions, including detection of undervoltage and overvoltage conditions on  $\pm 5$  V and  $\pm 12$  V system supplies. It also detects overcurrent conditions on the SPS system output. This single chip reduces the total component count and provides additional design flexibility, which minimizes cost and printed-circuit-board (PCB) space requirements in present and new SPS designs.

## overvoltage-protection lockout feature

The overvoltage-protection lockout feature monitors four different supply voltages. When an overvoltage (OV) condition is detected, the power-good output (PGO) is set low and the PWM function is disabled. The OV condition is detected on the SVP5, SVP12, SVN5, and SVN12 inputs. Threshold voltages are typically 5.9 V, 14.1 V, -8.4 V, and -15.3 V, respectively.

## undervoltage-protection lockout feature

The undervoltage-protection lockout feature monitors four different supply voltages. When an undervoltage (UV) condition is detected, the power-good output (PGO) is set low and the PWM function is disabled. The UV condition is detected on the SVP5, SVP12, SVN5, and SVN12 inputs. Threshold voltages are typically 3.9 V, 9.5 V, -3.4 V, and -9.3 V, respectively.

## overcurrent-protection lockout feature

The overcurrent (OC) protection lockout feature is designed to protect the SPS from excessive load or short-circuit conditions. The circuit converts the output current of the SPS to a voltage, which is then monitored at SC. It sets PG low and shuts down the PWM circuit when the sensed voltage is higher than 5 V.

## reference regulator

The internal 5-V reference regulator is designed primarily to provide the internal circuitry with a stable supply rail for varying input voltages. The regulator employs a band-gap circuit as its primary reference to maintain thermal stability of less than 100-mV variation over the operating free-air temperature range of 0°C to 70°C. In addition to supplying an internal reference, the regulator provides a precision 5-V reference that can support 5 mA of load current for external bias circuits. The regulated voltage has a margin of error of 2%. Short-circuit protection is provided to protect the internal circuit from overload or short-circuit conditions.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1994, Texas Instruments Incorporated

SLVS082A - APRIL 1994 - REVISED SEPTEMBER 1994

#### oscillator

The timing capacitor (CT) is charged by the oscillator with a  $350-\mu$ A current source set by the timing resistor (RT) (10 k $\Omega$ ), internally. This produces a linear-ramp voltage waveform across CT. When the voltage across CT reaches 3 V, it is discharged by the oscillator circuit and the charging cycle is reinitiated. The frequency of the oscillator is programmable over a range of 1 kHz to 300 kHz by the selection of CT. The programmed frequency of the oscillator can be calculated with the equation f = 1/(10<sup>4</sup> × CT). The PWM output frequency is one-half of the oscillator frequency.

## dead-time (DT) control

The DT input provides control of minimum dead time (off time). An input offset of 110 mV ensures a minimum dead time of 3% with the DT input grounded. Additional dead time can be imposed by applying voltage to the DT input. This provides a linear control of the dead time from its minimum of 3% to its maximum of 100% as the DT input voltage varies from 0 V to 3.3 V. The DT input is a relatively high-impedance input and is used where additional control of the output duty cycle is required. The input must be terminated; leaving this terminal open causes an undefined condition.

## pulse-width modulation

The ramp voltage across CT is compared to the output of the error amplifier. The CT input incorporates a series diode, which is omitted from the DT control input. This requires the error-amplifier output to be 0.7-V greater than the voltage across CT to inhibit the PWM output. This also ensures PWM maximum-duty-cycle operation without requiring the control voltage to sink to true ground potential. The output pulse width varies from 97% of the period to 0 as the voltage at the error-amplifier output varies from 0.5 V to 3.5 V.

#### error amplifier

The high-gain error amplifier receives bias from the V<sub>CC</sub> power rail. The inverting input, EA–, is biased by V<sub>ref</sub>/2 internally. The amplifier output is biased low by a current sink to provide PWM maximum duty cycle when the amplifier is off. Since the amplifier output is biased low only through  $I_{O(sink)}$  of 300 µA (see functional block diagram), bias current required by external circuitry into the amplifier output for feedback must not exceed the capability of  $I_{O(sink)}$ ; otherwise, the PWM maximum duty cycle is limited.

SLVS082A - APRIL 1994 - REVISED SEPTEMBER 1994

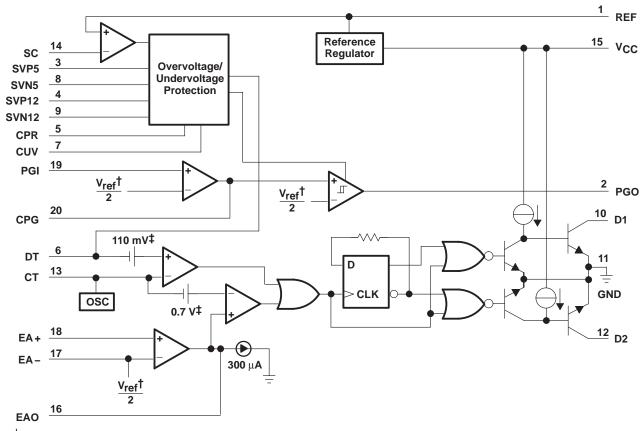

## functional block diagram

† Internally generated voltage ‡ Fixed-voltage offset

## **Terminal Functions**

| TERMINAL |     | 1/0 | DECODIDITION                                                                                                            |

|----------|-----|-----|-------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                             |

| CPG      | 20  | 0   | Power-good-capacitor connection. Connects a capacitor to power-good signal delay.                                       |

| CPR      | 5   | 0   | Protection-delay-capacitor connection. Connects a capacitor to protection-delay circuit to bypass high-frequency noise. |

| СТ       | 13  | 0   | Timing capacitor. Connects a capacitor to sawtooth oscillator circuit for programming the operating frequency.          |

| CUV      | 7   | 0   | UV capacitor connection. Connects a capacitor to UV power-on delay circuit to avoid malfunction in the initial state.   |

| D1       | 10  | 0   | PWM driver-1 output                                                                                                     |

| D2       | 12  | 0   | PWM driver-2 output                                                                                                     |

| DT       | 6   | Ι   | Dead time. Control input to control the PWM minimum dead time (off time).                                               |

| EA-      | 17  | Ι   | Error-amplifier inverting input                                                                                         |

| EA+      | 18  | Ι   | Error-amplifier noninverting input                                                                                      |

| EAO      | 16  | I/O | Error-amplifier output                                                                                                  |

| GND      | 11  |     | Ground                                                                                                                  |

| PGI      | 19  | Ι   | Power-good input                                                                                                        |

| PGO      | 2   | 0   | Power-good output                                                                                                       |

| REF      | 1   | 0   | 5-V reference voltage output                                                                                            |

| SC       | 14  | Ι   | Overcurrent sense input. When an OV/UV condition is sensed, the TLS1206 output is locked and PGO is set to low.         |

SLVS082A - APRIL 1994 - REVISED SEPTEMBER 1994

## **Terminal Functions (Continued)**

| TERMINAL |     |     | DESCRIPTION                                                                                                         |  |  |  |  |

|----------|-----|-----|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                         |  |  |  |  |

| SVN5     | 8   | Ι   | -5-V OV/UV detection input. When an OV/UV condition is sensed, the TLS1206 output is locked and PGO is set to low.  |  |  |  |  |

| SVN12    | 9   | I   | -12-V OV/UV detection input. When an OV/UV condition is sensed, the TLS1206 output is locked and PGO is set to low. |  |  |  |  |

| SVP5     | 3   | I   | 5-V OV/UV detection input. When an OV/UV condition is sensed, the TLS1206 output is locked and PGO is set to low.   |  |  |  |  |

| SVP12    | 4   | I   | 12-V OV/UV detection input. When an OV/UV condition is sensed, the TLS1206 output is locked and PGO is set to low.  |  |  |  |  |

| VCC      | 15  |     | Supply voltage                                                                                                      |  |  |  |  |

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>CC</sub>                                 | 41 V                    |

|-----------------------------------------------------------------|-------------------------|

| Amplifier input voltage, V <sub>I</sub>                         | V <sub>CC</sub> + 0.3 V |

| Collector output voltage, VO                                    | 41 V                    |

| Collector output current, IO                                    |                         |

| Total power dissipation at (or below) 25°C free-air temperature | 1 W                     |

| Operating free-air temperature range, T <sub>A</sub>            | 0°C to 70°C             |

| Storage temperature range                                       | 65°C to 70°C            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### DISSIPATION RATING TABLE

| PACKAGE | T <sub>A</sub> ≤ 25°C | OPERATING FACTOR            | T <sub>A</sub> = 70°C |

|---------|-----------------------|-----------------------------|-----------------------|

|         | POWER RATING          | ABOVE T <sub>A</sub> = 25°C | POWER RATING          |

| N       | 1150 mW               | 9.2 mW/°C                   | 736 mW                |

## recommended operating conditions

|                                                                   | MIN  | MAX   | UNIT |

|-------------------------------------------------------------------|------|-------|------|

| Supply voltage, V <sub>CC</sub>                                   | 7    | 40    | V    |

| Collector output voltage, V <sub>O(D1)</sub> , V <sub>O(D2)</sub> |      | 40    | V    |

| Collector output current, I <sub>O(D1)</sub> , I <sub>O(D2)</sub> |      | 150   | mA   |

| Timing capacitor, CT                                              | 0.47 | 10000 | nF   |

| Operating free-air temperature, T <sub>A</sub>                    | 0    | 70    | °C   |

SLVS082A - APRIL 1994 - REVISED SEPTEMBER 1994

| PARAMETER                       |                                               |           | TEST CONDITIONS                                                                                                                      |                                                                    | MIN  | TYP   | MAX        | UNIT |

|---------------------------------|-----------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------|-------|------------|------|

| V <sub>ref</sub>                | Reference output voltage                      |           | I <sub>O</sub> = 5 mA                                                                                                                |                                                                    | 4.9  | 5     | 5.1        | V    |

| VIH(SC)                         | High-level input voltage, SC over protection  | ercurrent | $\begin{array}{l} \text{SVP5} = 5 \text{ V},\\ \text{SVN5} = -5 \text{ V},\\ \text{V}_{O(\text{DT})} \geq 3.5 \text{ V} \end{array}$ | SVP12 = 12 V,<br>SVN12 = -12 V,                                    | 5.1  |       |            | V    |

| VIL(SC)                         | Low-level input voltage, SC over protection   | ercurrent | $\begin{array}{l} SVP5=5 \ V,\\ SVN5=-5 \ V,\\ V_O(DT) \leq 0.4 \ V \end{array}$                                                     | SVP12 = 12 V,<br>SVN12 = -12 V,                                    |      |       | 4.9        | V    |

|                                 |                                               | SVP5      | SVP12 = 12 V,<br>SVN12 = -12 V,                                                                                                      | SVN5 = $-5 \text{ V}$ ,<br>V <sub>O(DT)</sub> $\leq 0.4 \text{ V}$ | 3.5  | 3.9   | 4.5        |      |

|                                 | Input threshold voltage,                      | SVP12     | SVP5 = 5 V,<br>SVN12 = -12 V,                                                                                                        | SVN5 = $-5 \text{ V}$ ,<br>V <sub>O(DT)</sub> $\leq 0.4 \text{ V}$ | 9    | 9.5   | 10.5       |      |

| VIT(UV)                         | undervoltage sense                            | SVN5      | SVP5 = 5 V,<br>SVN12 = -12 V,                                                                                                        | SVP12 = 12 V,<br>V <sub>O(DT)</sub> ≤ 0.4 V                        | -3   | -3.4  | -4         | V    |

|                                 |                                               | SVN12     | SVP5 = 5 V,<br>SVN5 = -5 V,                                                                                                          | SVP12 = 12 V, $V_{O(DT)} \leq 0.4 \text{ V}$                       | -8   | -9.3  | -10        |      |

| Vit(ov)                         | Input threshold voltage,<br>overvoltage sense | SVP5      | SVP12 = 12 V,<br>SVN12 = -12 V,                                                                                                      | SVN5 = $-5 \text{ V}$ ,<br>V <sub>O(DT)</sub> $\leq 0.4 \text{ V}$ | 5.5  | 5.9   | 6.3        | V    |

|                                 |                                               | SVP12     | SVP5 = 5 V,<br>SVN12 = -12 V,                                                                                                        | SVN5 = −5 V,<br>V <sub>O(DT)</sub> ≤ 0.4 V                         | 13.5 | 14.1  | 14.8       |      |

|                                 |                                               | SVN5      | SVP5 = 5 V,<br>SVN12 = -12 V,                                                                                                        | SVP12 = 12 V,<br>V <sub>O(DT)</sub> ≤ 0.4 V                        | -7   | -8.4  | -9         |      |

|                                 |                                               | SVN12     | SVP5 = 5 V,<br>SVN5 = -5 V,                                                                                                          | SVP12 = 12 V,<br>V <sub>O(DT)</sub> ≤ 0.4 V                        | -14  | -15.3 | -16        |      |

| VOL(D1) <sup>,</sup><br>VOL(D2) | Low-level output voltage, output drivers      |           | V <sub>O(DT)</sub> ≥ 3.5 V                                                                                                           | I <sub>OL</sub> = 0<br>I <sub>OL</sub> = 150 mA                    |      | 1.6   | 0.4<br>2.5 | V    |

| VO(DT)                          | Dead-time output voltage                      |           | SVP5 = 7 V,                                                                                                                          | I <sub>O(DT)</sub> = -250 μA                                       | 3.5  |       |            | V    |

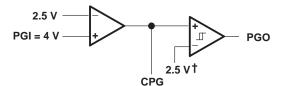

| VIH(PGI)                        | High-level input voltage, PGI                 |           | $V_{O(PGO)} \ge 4 V,$                                                                                                                | See Figure 3                                                       | 2.8  |       |            | V    |

| VIL(PGI)                        | Low-level input voltage, PGI                  |           | V <sub>O(PGO)</sub> ≤ 0.4 V,                                                                                                         | See Figure 3                                                       |      |       | 2.42       | V    |

| VIH(CPG)                        | High-level input voltage, CPG                 |           | VI(PGI) = 4 V,<br>See Figure 4                                                                                                       | $V_{O}(PGO) \ge 4 V,$                                              | 2.95 |       |            | V    |

| VIL(CPG)                        | Low-level input voltage, CPG                  |           | VI(PGI) = 4 V,<br>See Figure 4                                                                                                       | $V_{O}(PGO) \le 0.4 V,$                                            |      |       | 2.6        | V    |

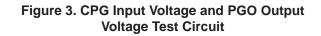

| VOH(PGO)                        | High-level output voltage, PGO                |           | V <sub>CPG</sub> = 4 V,<br>See Figure 5                                                                                              | I <sub>O(PGO)</sub> = -240 μA,                                     | 4.75 |       |            | V    |

| V <sub>OL(PGO)</sub>            | Low-level output voltage, PGO                 |           | V <sub>CPG</sub> = 0 V,<br>See Figure 6                                                                                              | I <sub>O(PGO)</sub> = 9.6 mA,                                      |      |       | 0.4        | V    |

| ICC                             | Standby supply current                        |           | All other inputs and                                                                                                                 | outputs open                                                       |      |       | 32         | mA   |

| f <sub>osc</sub>                | Oscillator frequency                          |           | C <sub>T</sub> = 1200 pF                                                                                                             |                                                                    |      | 80    |            | kHz  |

## electrical characteristics over recommended operating free-air temperature range, V<sub>CC</sub> = 15 V

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature

|    | PARAMETER                | TEST CONDITIONS                                                                                                                                                                | MIN | TYP | MAX | UNIT |

|----|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

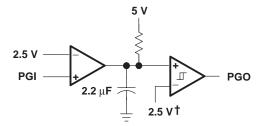

| tr | Rise time of power good  | $V_{CPG} L \rightarrow H$ , $V_{O(PGO)} L \rightarrow H$ , See Figures 4 and 6                                                                                                 |     |     | 100 | ns   |

| td | Delay time of power good | $ \begin{array}{ll} R_L = 150 \ \mathrm{k}\Omega, & CPG = 2.2 \ \muF, \\ V_I(PGI) \ H \rightarrow L, \ V_O(PGO) \ H \rightarrow L, & See \ Figures \ 4 \ and \ 6 \end{array} $ |     | 500 | 600 | μs   |

SLVS082A - APRIL 1994 - REVISED SEPTEMBER 1994

## APPLICATION INFORMATION

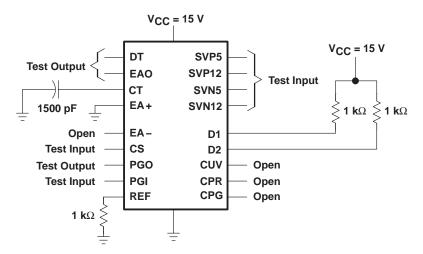

(open)

Figure 2. PGI Input Voltage Test Circuit

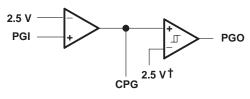

Figure 4. PG Delay Time and Rise Time Test Circuit

<sup>†</sup> Internally biased at  $V_{ref}/2$  or 2.5 V

Figure 5. PG Output Voltage Waveform

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DLP® Products               | www.dlp.com            | Broadband          | www.ti.com/broadband      |

| DSP                         | dsp.ti.com             | Digital Control    | www.ti.com/digitalcontrol |

| Clocks and Timers           | www.ti.com/clocks      | Medical            | www.ti.com/medical        |

| Interface                   | interface.ti.com       | Military           | www.ti.com/military       |

| Logic                       | logic.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Power Mgmt                  | power.ti.com           | Security           | www.ti.com/security       |

| Microcontrollers            | microcontroller.ti.com | Telephony          | www.ti.com/telephony      |

| RFID                        | www.ti-rfid.com        | Video & Imaging    | www.ti.com/video          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated