- Advanced LinCMOS™ Technology

- 8-Bit Analog-to-Digital Converter

- 8-Bit Digital-to-Analog Converter

- Monotonic Over Entire Analog-to-Digital and Digital-to-Analog Conversion Range

- 8-Input Analog Multiplexer With Latched Channel Select

- Programmable Input Range on Two Input Amplifiers

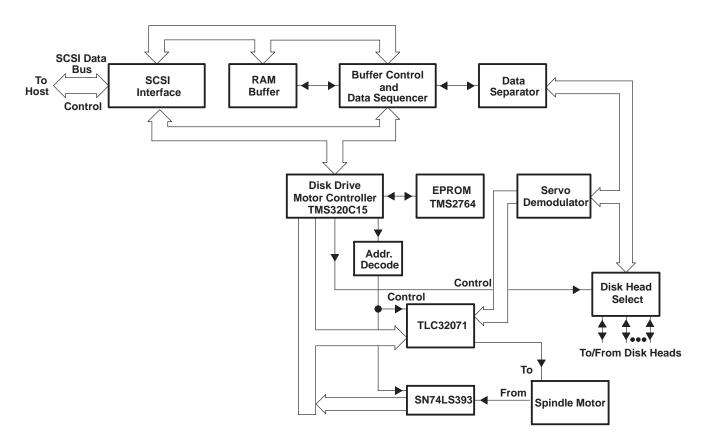

- Interfaces Directly to Many Digital Signal Processors Including the TMS320 Family

- Low-Glitch Impulse at DAC Output

- Built-In Scaling and Level Shifting on Six of the Analog Inputs

- Designed for Servo-Loop Control Systems Including Disk Drives

#### description

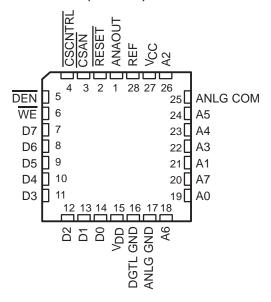

The TLC32071 is an analog interface integrated circuit that converts between the analog and digital domains. The device includes an 8-bit voltage-output digital-to-analog converter (DAC), an 8-bit analog-to-digital converter (ADC), an analog input multiplexer with eight analog inputs, an output reference MUX, and a high-speed 8-bit bidirectional data bus that interfaces directly to the TMS320 family of digital signal processors. The reset input (RESET) is used to clear the DAC and control registers. The 8-bit DAC converts digital signals to the equivalent analog values. The DAC is followed by a level shifter, which adjusts the center of the DAC output range to the voltage externally applied to the ANLG COM input. One of three output ranges can be selected by an internal register.

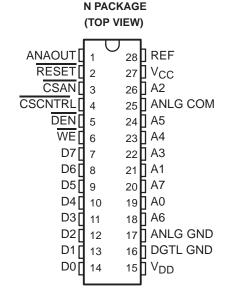

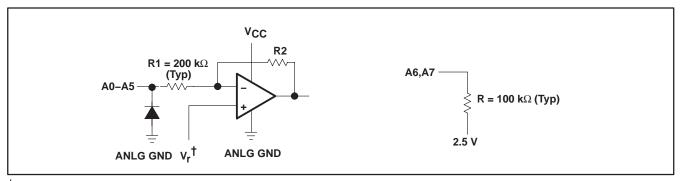

### FN PACKAGE (TOP VIEW)

The 8-bit ADC converts any one of eight analog inputs selected by a programmable internal register through an input multiplexer. Six of these have inverting inputs with built-in level shifting so that these six output ranges are centered at the ADC input voltage midpoint. Two of the six inputs have register selectable gains. The first conversion result after selection of one of the six inverting inputs should be discarded as invalid. The two remaining inputs are direct inputs to the ADC multiplexer with output ranges centered at the internal 2.5-V reference ( $V_{ref}$ ). After reset, this reference is available at the REF output. The REF output can also be programmed by an internal control register to provide access to other internal references, any of the analog inputs after scaling and shifting, or the unscaled output of the DAC.

LinCMOS is a trademark of Texas Instruments Incorporated.

### functional block diagram

All resistor values shown are nominal.

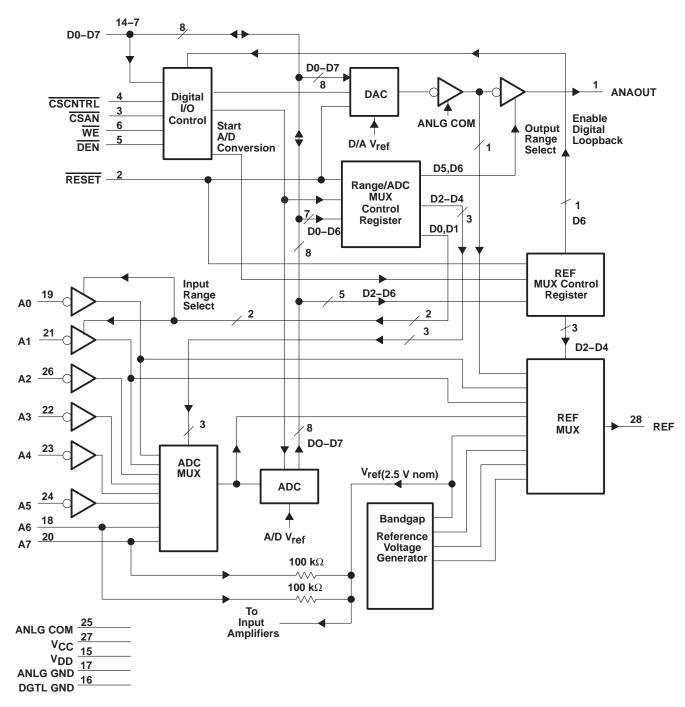

### equivalents of analog input circuit

$<sup>^{\</sup>dagger}$  V<sub>r</sub> is an internally generated voltage with the following typical values: at range = 1, V<sub>r</sub> = 3.33 V; at range = 1/2, V<sub>r</sub> = 3.75; at range = 1/4, V<sub>r</sub> = 4.167 V.

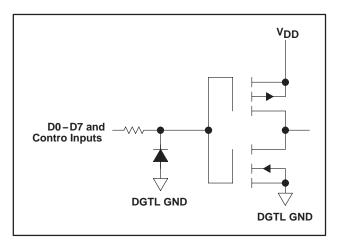

### equivalent of digital input circuit

# TLC32071 HIGH-SPEED 8-BIT A/D AND D/A CONVERTER WITH 8-CHANNEL MULTIPLEXER SLAS051-D3973, DECEMBER 1991

### **Terminal Functions**

| PIN      |          |     |                                                                                                                                                                                                                                                |

|----------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.      | I/O | DESCRIPTION                                                                                                                                                                                                                                    |

| ANAOUT   | 1        | 0   | Analog output. The DAC output with selectable ranges.                                                                                                                                                                                          |

| ANLG COM | 25       | ı   | Analog common. Input for reference voltage for inverting analog inputs.                                                                                                                                                                        |

| ANLG GND | 17       |     | Analog ground. Ground connection associated with ADC, DAC, and other analog circuits.                                                                                                                                                          |

| A0       | 19       | ı   |                                                                                                                                                                                                                                                |

| A1       | 21       | ı   | Inverting analog input with range programmable to 8, 4, or 2 V. This input uses ANLG COM as a signal ground.                                                                                                                                   |

| A2       | 26       | ı   |                                                                                                                                                                                                                                                |

| A3       | 22       | ı   | <del></del>                                                                                                                                                                                                                                    |

| A4       | 23       | ı   | Inverting analog Input. This input uses ANLG COM as a signal ground.                                                                                                                                                                           |

| A5       | 24       | I   |                                                                                                                                                                                                                                                |

| A6       | 18       | ı   | Auxiliary noninverting analog input with input range of 0.5 to 4.5 V. This input uses the internal reference VR2.5                                                                                                                             |

| A7       | 20       | ı   | as a signal ground.                                                                                                                                                                                                                            |

| CSAN     | 3        | ı   | Chip select for writing to the D/A converter and reading the results of an A/D conversion.                                                                                                                                                     |

| CSCNTRL  | 4        | ı   | Chip select for the control register, which selects DAC and ADC ranges and the analog input channel.                                                                                                                                           |

| DEN      | 5        | ı   | Read strobe for the A/D converter output. Output buffers are enabled when this signal is held low.                                                                                                                                             |

| DGTL GND | 16       |     | Digital ground. Ground connection associated with digital data-bus signals and other digital circuits.                                                                                                                                         |

| D7-D0    | 7–1<br>4 | I/O | Bidirectional data bus. This bus is used for writing conversion data to the DAC, writing data to the range/ADC MUX control register or to the REF MUX control register, and for reading the ADC conversion result.                             |

| RESET    | 2        | I   | Reset. This strobe, when low, clears the range/ADC MUX control register, the REF MUX control register, and the DAC input register. CSCNTRL and CSAN should be held high during a reset operation.                                              |

| REF      | 28       | 0   | 2.5-V reference output. The signal routed to this pin is determined by the contents of an internal register (see CSCNTRL data word description). The internally generated 2.5-V reference may be selected for use in biasing inputs A6 and A7. |

| $V_{DD}$ | 15       |     | 5-V (digital) supply                                                                                                                                                                                                                           |

| VCC      | 27       |     | 10-V (analog) supply                                                                                                                                                                                                                           |

| WE       | 6        | I   | Write enable. This input is a write strobe for the control registers and the DAC input register. Data is latched on the rising edge of this signal.                                                                                            |

#### PRINCIPLES OF OPERATION

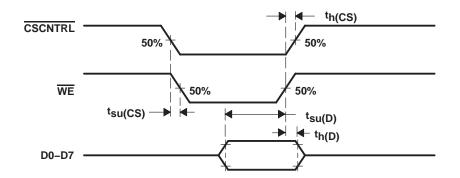

### writing control words to the TLC32071

With the CSCNTRL input low, a control word is written to the TLC32071 by placing data on the D7–D0 inputs and applying a low-going pulse to the write enable input (WE). Data is latched on the rising edge of the WE pulse. The values of D0 and D1 of the control word determine whether the data is latched in the range/ADC MUX control register or the REF MUX register. See Tables 1, 2, 3, and 4 for data-bit formats.

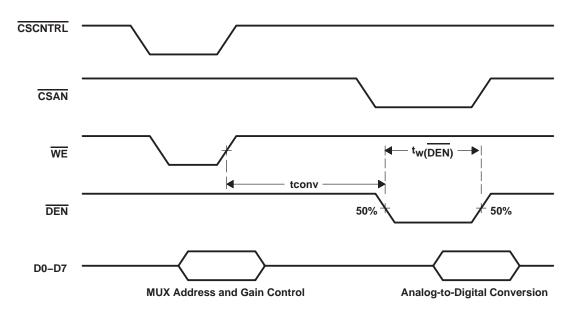

### operation of the ADC channel

Analog-to-digital conversion begins when gain-select and channel-select data word is latched in the range/ADC MUX control register by the rising edge of the WE pulse. This data word controls the state of the range/ADC input multiplexer. After the conversion time, the conversion result may be read by taking the DEN input low while the CSAN input is low. Writing of data to the REF MUX control register (using CSCNTRL and WE with D0 and D1 both 0) does not start a conversion. Each time one of the A0 through A5 signal channels is selected, the first conversion result after selection should be ignored due to internal input amplifier settling time. If this channel remains selected, subsequent conversions are valid.

### operation of the DAC channel

When the  $\overline{\text{CSAN}}$  input is low, digital-to-analog conversion is performed by placing input data on data bus DB7–DB0 and applying a low-going pulse to  $\overline{\text{WE}}$ . The data word is latched on the rising edge of the  $\overline{\text{WE}}$  pulse and is decoded to an equivalent analog voltage. The conversion occurs internally in approximately 100 ns with the D/A conversion result available at the ANAOUT output after a specified settling time.

### digital loopback mode

Digital loopback enables the simultaneous testing of the A/D and D/A channels. When digital loopback is enabled, the A/D conversion result is transferred to the D/A input latches on the next rising edge of  $\overline{\text{DEN}}$ . The analog signal from the input pin at the A/D converter is transferred through the D/A converter to the analog output ANAOUT. To enable digital loopback, write to the REF MUX control register (see data word format in Table 3) to set bit D6. Then, perform A/D conversion (as in normal operation) by writing channel select and range select information to the range/ADC MUX control register. This is done by strobing  $\overline{\text{WE}}$  while  $\overline{\text{CSCTRL}}$  is low. Read the conversion result by strobing  $\overline{\text{DEN}}$  while holding  $\overline{\text{CSAN}}$  low when digital loopback is enabled. The A/D conversion result is transferred to the DAC on the rising edge of  $\overline{\text{DEN}}$  (See Tables 1, 2, 3, and 4).

#### reset operation

CSAN and CSCNTRL should be held high during a reset operation. When the RESET input is taken low, the internal reset signal clears the range/ADC MUX control register, the REF MUX control register, and the DAC input register. The following conditions exist after reset:

- 1. The DAC output is set to the voltage at the ANLG COM input.

- 2. The DAC range is set to ANLG COM  $\pm 4$  V.

- 3. The A0 analog channel is selected and the A0 and A1 amplifier ranges are set to ANLG COM  $\pm 4$  V.

- 4. The 2.5 V reference is selected at the REF output.

- 5. Digital loopback is disabled.

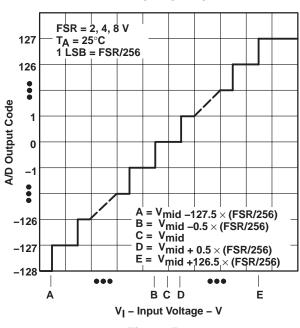

#### analog inputs

The ANLG COM voltage establishes the operating midpoint of the input amplifiers, A0 through A5. When the input signal voltage equals this voltage, the ADC output is ideally digital count zero. These amplifiers level shift to the ADC midpoint of 2.5 V and scale the input voltage range to the ADC range of 0.5 to 4.5 V. The A6 and A7 noninverting inputs are centered at the 2.5 V internally generated voltage reference and are connected directly to the input MUX. Table 5 gives the full scale input range and the midpoint voltages applicable for the individual analog inputs.

**Table 1. Data Word Formats (Channel Range Selection)**

|    |                   | A0/A1 CHANNEL       |                                                           |               | LE RAI | NGE |

|----|-------------------|---------------------|-----------------------------------------------------------|---------------|--------|-----|

| D1 | PROGRAMMABLE GAIN |                     | DATA DESTINATION                                          | (ANLG COM=5)  | MIN    | MAX |

| L  | L                 | No range selection  | Higher-order bits are sent to REF-MUX register            |               |        |     |

| L  | Н                 | Range is set to 1   |                                                           | ANLG COM ±4 V | 1 V    | 9 V |

| Н  | L                 | Range is set to 1/2 | Higher-order bits are sent to ADC channel-select register | ANLG COM ±2 V | 3 V    | 7 V |

| Н  | Н                 | Range is set to 1/4 |                                                           | ANLG COM ±1 V | 4 V    | 6 V |

Table 2. Data Word Formats (RANGE/ADC-Multiplexer Channel Selection) (Data chosen from this table is only valid when data bits D1 and D0 are not both low)

| SELECTED CHANNEL | D7 | D6 | D5 | D4 | D3 | D2 |

|------------------|----|----|----|----|----|----|

| A0               | Х  | Х  | Х  | L  | L  | L  |

| A1               | Х  | X  | X  | L  | L  | Н  |

| A2               | Х  | Χ  | Χ  | L  | Н  | L  |

| А3               | Х  | Χ  | Χ  | L  | Н  | Н  |

| A4               | Х  | Χ  | Χ  | Н  | L  | L  |

| A5               | Х  | Χ  | Χ  | Н  | L  | Н  |

| A6               | Х  | Χ  | Χ  | Н  | Н  | L  |

| A7               | Х  | Χ  | Χ  | Н  | Н  | Н  |

Table 3. Data Word Formats (DAC Output Range Selection)

(Data chosen from this table is only valid when data bits D1 and D0 are not both low)

|       |   |                     | OUTPUT FULL SCALE RANGE |     |     |  |  |

|-------|---|---------------------|-------------------------|-----|-----|--|--|

| D6 D5 |   | DAC OUTPUT RANGE    | (ANLG COM=5)            | MIN | MAX |  |  |

| L     | Χ | Range is set to 1   | ANLG COM ±4 V           | 1 V | 9 V |  |  |

| Н     | L | Range is set to 1/2 | ANLG COM ±2 V           | 3 V | 7 V |  |  |

| Н     | Н | Range is set to 1/4 | ANLG COM ±1 V           | 4 V | 6 V |  |  |

Table 4. Data Word Formats (REF-Multiplexer Channel Selection)

(Data chosen from this table is valid only when data bits D1 and D0 are both low)

| SELECTED CHANNEL                    | D6 | D5 | D4 | D3 | D2 |

|-------------------------------------|----|----|----|----|----|

| Vref (2.5 V nom)                    | Х  | Χ  | L  | L  | L  |

| Bandgap (ACOM + 1.25 V)             | Х  | Χ  | L  | L  | Н  |

| A/D reference (approximately 4.6 V) | Х  | Χ  | L  | Н  | L  |

| D/A reference (ANLG COM -3 V)       | Х  | Χ  | L  | Н  | Н  |

| A0 amp output <sup>†</sup>          | Х  | Χ  | Н  | L  | L  |

| A1 amp output <sup>†</sup>          | Х  | Χ  | Н  | L  | Н  |

| ADC MUX output <sup>†</sup>         | Х  | Χ  | Н  | Н  | L  |

| DAC level shift output‡             | Х  | Χ  | Н  | Н  | Н  |

| Enable digital loopback             | Н  | Χ  | Χ  | Χ  | Х  |

$<sup>\</sup>dagger$  These signals are outputs of scaling/level-shifting amplifiers. The range of these signals is V  $_{ref}$   $\pm 2$  V.

$<sup>\</sup>ddagger$  The unscaled output of the DAC. This analog output is proportional to the DAC value with a fixed range of ANLG COM  $\pm 1$  V, but inverted relative to the twos-complement code written to the DAC.

### **Table 5. Analog Input Characteristics**

| INPUT       | v <sub>mid</sub> † | NOMINAL<br>FSR‡ | INPUT VOLTAGE RANGE<br>(ANLG COM=5) |       |  |

|-------------|--------------------|-----------------|-------------------------------------|-------|--|

|             |                    | FSK+            | MIN                                 | MAX   |  |

| A0, A1§ (1) | ANLG COM           | ±4 V            | 1 V                                 | 9 V   |  |

| (1/2)       | ANLG COM           | ±4 V            | 3 V                                 | 7 V   |  |

| (1/4)       | ANLG COM           | ±4 V            | 4 V                                 | 6 V   |  |

| A2 thru A5§ | ANLG COM           | ±4 V            | 1 V                                 | 9 V   |  |

| A6, A7      | $v_{ref}\P$        | ±2 V            | 0.5 V                               | 4.5 V |  |

T V<sub>mid</sub> is (VP127-VM127)•127.5/254+VM127 where VP127 is the minimum input voltage to produce an output code of +127, and VM127 is the minimum input voltage to produce an output code of –127.

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub> (analog supply) (see Note 1)      |

|-------------------------------------------------------------------------|

| Supply voltage range, VDD (digital supply) (see Note 2)0.5 V to 7 V     |

| Digital ground voltage range, DGTL GND                                  |

| Analog output voltage range (see Note 1) −0.5 V to V10 + 0.5 V          |

| Analog input voltage range (see Note 1)0.5 V to 14 V                    |

| Digital output voltage range (see Note 2)0.5 V to V5 + 0.5 V            |

| Digital input voltage range (see Note 2)                                |

| Operating free-air temperature range, T <sub>A</sub> 0°C to 70°C        |

| Storage temperature range –65°C to 150°C                                |

| Case temperature for 10 seconds: FN package                             |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: N package |

NOTES: 1. All voltage values are given with respect to ANLG GND unless otherwise noted.

7

<sup>‡</sup> Full-scale range is (VP127–VM127)•256/254 where VP127 is the minimum input voltage to produce an output code of +127, and VM127 is the minimum input voltage to produce an output code of –127.

<sup>§</sup> Inverting inputs

<sup>¶</sup> V<sub>ref</sub> is an internally generated reference voltage that can be available at the REF output. The inputs A6 and A7 are connected to V<sub>ref</sub> through an on-chip resistor.

<sup>2.</sup> All voltage values are with respect to DGTL GND.

### TLC32071 HIGH-SPEED 8-BIT A/D AND D/A CONVERTER WITH 8-CHANNEL MULTIPLEXER

SLAS051-D3973, DECEMBER 1991

### recommended operating conditions

|                                                                          | MIN              | NOM | MAX | UNIT |

|--------------------------------------------------------------------------|------------------|-----|-----|------|

| Supply voltage, V <sub>CC</sub>                                          | 9                | 10  | 12  | V    |

| Supply voltage, V <sub>DD</sub>                                          | 4.5              | 5   | 5.5 | V    |

| High-level input voltage, V <sub>IH</sub> (digital inputs)               | 2.4              |     |     | V    |

| Low-level input voltage, V <sub>IL</sub> (digital inputs)                |                  |     | 0.5 | V    |

| Reference voltage input at ANLG COM <sup>†</sup> input, V <sub>ref</sub> | 3.5              | 5   | 6   | V    |

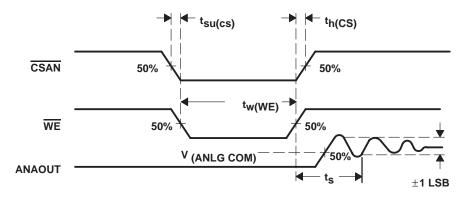

| Setup time, CSCNTRL low before WE low, t <sub>SU(CS)</sub>               | 0                |     |     | ns   |

| Hold time, CSCNTRL high after WE high, th(CS)                            | 0                |     |     | ns   |

| Setup time, data bus before CSCNTRL high, t <sub>SU(D)</sub>             | 15               |     |     | ns   |

| Hold time, data bus after CSCNTRL high, th(D)                            | 15               |     |     | ns   |

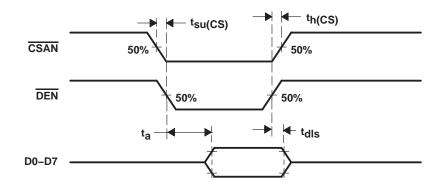

| Pulse duration, DEN, t <sub>W</sub> (DEN)                                | t <sub>a</sub> ‡ |     |     | ns   |

| Setup time, CSAN low before DEN low, t <sub>Su(CS)</sub>                 | 0                |     |     | ns   |

| Hold time, CSAN high after DEN high, th(CS)                              | 0                |     |     | ns   |

| Setup time, CSAN low before WE low, t <sub>Su(CS)</sub>                  | 0                |     |     | ns   |

| Hold time, CSAN high after WE high, th(CS)                               | 0                |     |     | ns   |

| Pulse duration, RESET, tw(RE)                                            | 25               |     |     | ns   |

| Pulse duration, WE, t <sub>W(WE)</sub>                                   | 30               |     |     | ns   |

| Operating free-air temperature, TA                                       | 0                |     | 70  | °C   |

<sup>†</sup> For a DAC range of R = (1, 1/2, 1/4), ANLG COM should be chosen so that ANLG COM  $\pm 4R$  is greater than 0.5 V and less then  $V_{CC} = 0.5 \text{ V}$  or the DAC output may not be able to deliver the specified maximum current without voltage limiting occurring.

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                       | TEST CONDITIONS                             | MIN  | TYP§ | MAX  | UNIT |

|---------------------|-------------------------------------------------|---------------------------------------------|------|------|------|------|

| Vон                 | High-level output voltage                       | $V_{DD}$ at 4.5 V, $I_{OH} = -360 \mu A$    | 2.4  |      |      | V    |

| VOL                 | Low-level output voltage                        | $V_{DD}$ at 4.5 V, $I_{OL} = 1.6$ mA        |      |      | 0.4  | V    |

| V <sub>ref</sub>    | Reference voltage output (see Note 3)           | ANLG COM = 5 V                              | 2.42 | 2.5  | 2.58 | V    |

| R <sub>O(ref)</sub> | Reference output resistance                     | ANLG COM = 5 V                              |      | 0.8  | 1.2  | kΩ   |

| lіН                 | High-level input current                        | V <sub>IH</sub> = 5 V                       |      |      | 10   | μΑ   |

| I <sub>I</sub> L    | Low-level input current                         | V <sub>IL</sub> = 0                         |      |      | - 10 | μΑ   |

| I <sub>DD</sub>     | Supply current, digital                         | D0-D7 at V <sub>IH</sub> or V <sub>IL</sub> |      |      | 20   | mA   |

| Icc                 | Supply current, analog                          |                                             |      |      | 22   | mA   |

| loz                 | Off-state output current (high-impedance state) | V <sub>O</sub> = 5 V                        |      |      | 3    | μА   |

| loz                 | On-state output current (high-impedance state)  | V <sub>O</sub> = 0                          |      |      | -3   | μΑ   |

| loo                 | Short-circuit output current                    | V <sub>O</sub> = 5 V                        | 25   | 40   |      | A    |

| los                 | Short-circuit output current                    | V <sub>O</sub> = 0                          | -45  | -60  |      | mA   |

| Co                  | Output capacitance (digital outputs)            |                                             |      |      | 5    | pF   |

§ All typical values are at  $T_A = 25$ °C.

NOTE 3: This voltage is an internal reference voltage (2.5 V) that is available at the output-multiplexer output.

<sup>‡</sup>Access time

### ADC operating characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER            |                                                                                     | TEST CONDITIONS |                          | MIN                    | MAX                    | UNIT |

|----------------------|-------------------------------------------------------------------------------------|-----------------|--------------------------|------------------------|------------------------|------|

|                      | Linearity error                                                                     |                 |                          |                        | ±1                     | LSB  |

| V <sub>I(FS)</sub> † | Input voltage for full-scale output code (Input channel = A6 or A7)                 |                 |                          | 3.92                   | 4.08                   | V    |

| V <sub>mid</sub> ‡   | ADC input offset voltage (Input channel = A6 or A7)                                 |                 |                          | V <sub>ref</sub> -0.06 | V <sub>ref</sub> +0.06 | V    |

| t <sub>conv</sub>    | Conversion time                                                                     | See Figure 2    |                          |                        | 2.5                    | μs   |

|                      |                                                                                     |                 | C <sub>L</sub> = 100 pF§ |                        | 50                     |      |

| ta                   | Access time (delay from falling edge of DEN to data output)                         | See Figure 3    | $C_L = 50 pF$            |                        | 41                     | ns   |

|                      |                                                                                     |                 | C <sub>L</sub> = 25 pF§  |                        | 37                     |      |

| t <sub>dis</sub>     | Disable time (delay from rising edge of DEN to high-impedance state of data output) | See Figure 3    | C <sub>L</sub> = 100 pF  |                        | 35                     | ns   |

<sup>†</sup> Full-scale range is (VP127–VM127) • 256/254 where VP127 is the minimum input voltage to produce an output code of +127, and VM127 is the minimum input voltage to produce an output code of -127.

### DAC operating characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER       |                                                                              | TEST CONDITIO                                            | MIN                                              | TYP¶             | MAX | UNIT             |     |

|-----------------|------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------|------------------|-----|------------------|-----|

| t <sub>S</sub>  | Settling time (to 1 LSB)                                                     | LSB) Load on ANAOUT = 20 pF + 5 k $\Omega$ (to ANLG COM) |                                                  |                  | 8   | 15               | μs  |

| EL              | Linearity error                                                              |                                                          |                                                  |                  |     | ±1               | LSB |

|                 | Code width                                                                   |                                                          |                                                  | 0.25             |     | 1.75             | LSB |

|                 | Output voltage swing <sup>#</sup> ,                                          |                                                          | Range = 1                                        | 7.84             | 8   | 8.16             |     |

| VO(FS)          | full scale                                                                   | DAC input = $-128$ to $+127$                             | Range = 1/2                                      | 3.92             | 4   | 4.08             | V   |

| , ,             | (VP127-VM128) • 256/255                                                      |                                                          | Range = 1/4                                      | 1.96             | 2   | 2.04             |     |

|                 |                                                                              |                                                          | Range = 1                                        | ANLG<br>COM-0.08 |     | ANLG<br>COM+0.08 |     |

|                 | Output bias level <sup>#</sup> , full scale<br>(VP127–VM128) • 128/255+VM128 | DAC input = 0                                            | Range = 1/2                                      | ANLG<br>COM-0.06 |     | ANLG<br>COM+0.06 | V   |

|                 |                                                                              |                                                          | Range = 1/4                                      | ANLG<br>COM-0.05 |     | ANLG<br>COM+0.05 |     |

|                 | Glitch energy                                                                | Sample rate = 30 kHz                                     | Sample rate = 30 kHz                             |                  |     | 1.2              | mV  |

| I <sub>OM</sub> | Maximum output current, ANAOUT                                               | Source from V <sub>CC</sub> – 0.5 V or 0.5 V             | Source from V <sub>CC</sub> – 0.5 V or sink from |                  |     |                  | mA  |

<sup>¶</sup> Typical values are at  $T_A = 25$ °C.

<sup>&</sup>lt;sup>‡</sup> V<sub>mid</sub> is (VP127–VM127) • 127.5/254 + VM127 where VP127 is the minimum input voltage to produce an output code of +127, and VM127 is the minimum input voltage to produce an output code of −127.

<sup>§</sup> C<sub>I</sub> is in addition to the internal capacitance of the digital output.

<sup>#</sup>VP127 is the voltage output for an input code of +127. VM128 is the voltage output for an input code of -128.

### TLC32071 HIGH-SPEED 8-BIT A/D AND D/A CONVERTER WITH 8-CHANNEL MULTIPLEXER

SLAS051-D3973, DECEMBER 1991

## ADC electrical characteristics for inputs A0 and A1 over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER         |                                                                      | TEST CONDITIONS               |             | MIN  | TYP | MAX   | UNIT |

|-------------------|----------------------------------------------------------------------|-------------------------------|-------------|------|-----|-------|------|

| A <sub>V</sub> 1  | Voltage amplification                                                | Range = 1                     |             | 0.99 | 1   | 1.01  | V/V  |

| A <sub>V</sub> 2  | Voltage amplification                                                | Range = 1/2                   |             | 1.98 | 2   | 2.02  | V/V  |

| A <sub>V</sub> 4  | Voltage amplification                                                | Range = 1/4                   |             | 3.96 | 4   | 4.04  | V/V  |

| V <sub>OB</sub> 1 | Output bias voltage at input of ADC with respect to V <sub>ref</sub> | V <sub>I</sub> = V(ANLG COM), | Range = 1   |      | 0   | ±0.02 | V    |

| V <sub>OB</sub> 2 | Output bias voltage at input of ADC with respect to V <sub>ref</sub> | VI = V(ANLG COM),             | Range = 1/2 |      | 0   | ±0.03 | V    |

| V <sub>OB</sub> 4 | Output bias voltage at input of ADC with respect to V <sub>ref</sub> | VI = V(ANLG COM),             | Range = 1/4 |      | 0   | ±0.05 | V    |

| rį                | Input resistance                                                     |                               |             | 140  | 200 | 260   | kΩ   |

### ADC electrical characteristics for inputs A2, A3, A4 and A5 over recommended operating free-air temperature range (unless otherwise noted)

|       | PARAMETER                                                                    | TEST CONDITIONS              | MIN    | TYP  | MAX    | UNIT |

|-------|------------------------------------------------------------------------------|------------------------------|--------|------|--------|------|

| $A_V$ | Voltage amplification to ADC                                                 |                              | -0.495 | -0.5 | -0.505 | V/V  |

| VOB   | Output bias voltage at the input of the ADC with respect to V <sub>ref</sub> | V <sub>I</sub> = V(ANLG COM) | -0.02  | 0    | +0.02  | V    |

| rį    | Input resistance                                                             |                              | 140    | 200  | 260    | kΩ   |

### ADC electrical characteristics for inputs A6 and A7 (direct inputs) over recommended free-air temperature range (unless otherwise noted)

|       | PARAMETER                    | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------|------------------------------|-----------------|-----|-----|-----|------|

| $A_V$ | Voltage amplification to ADC |                 |     | 1   |     | V/V  |

| rį    | Input resistance (to REF)    |                 | 70  | 100 | 130 | kΩ   |

### PARAMETER MEASUREMENT INFORMATION

Figure 1. Write Operation

Figure 2. A/D Conversion Cycle

Figure 3. A/D Read Operation

### PARAMETER MEASUREMENT INFORMATION

Figure 4. D/A Conversion Operation

#### IDEAL A/D OUTPUT CODE vs INPUT VOLTAGE

Figure 5

### PARAMETER MEASUREMENT INFORMATION

### **IDEAL D/A OUTPUT VOLTAGE INPUT CODE** ANLG COM + 127 × (FSR/256) FSR = 2, 4, 8 V T<sub>A</sub> = 25°C ANLG COM + $126 \times (FSR/256)$ 1 LSB = FSR/256 Output Voltage - V ANLG COM +1 × (FSR/256) **ACOM** ANLG COM $-1 \times (FSR/256)$ ANLG COM $-126 \times (FSR/256)$ ANLG COM $-127 \times (FSR/256)$ ANLG COM -128 × (FSR/256) -128 -127 ••• -1 0 126 127 **Input Code**

Figure 6

### **APPLICATION INFORMATION**

Figure 7. Simplified Disk-Drive Controller

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |

|--------------------|---------------------------|

| Audio              | www.ti.com/audio          |

| Automotive         | www.ti.com/automotive     |

| Broadband          | www.ti.com/broadband      |

| Digital Control    | www.ti.com/digitalcontrol |

| Medical            | www.ti.com/medical        |

| Military           | www.ti.com/military       |

| Optical Networking | www.ti.com/opticalnetwork |

| Security           | www.ti.com/security       |

| Telephony          | www.ti.com/telephony      |

| Video & Imaging    | www.ti.com/video          |

| Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated