## INTEGRATED CIRCUITS

Product specification Supersedes data of 1995 Mar 22 File under Integrated Circuits, IC02 1996 Jan 12

## TDA8753A

### FEATURES

- Triple analog-to-digital converter

- 8-bit resolution

- Sampling rate up to 20 MHz

- Power dissipation of 500 mW (typical)

- Internal clamp functions

- 4 : 1 : 1 output data encoder

- Y binary output

- U, V two's complement outputs

- Sample rate converter permits programmable horizontal compression factors from 1 to 2

- Serial microcontroller interface

- TTL compatible inputs.

### QUICK REFERENCE DATA

### APPLICATIONS

- High-speed analog-to-digital conversion for video signal digitizing in 4 : 1 : 1 format

- 100 Hz improved definition TV for all formats (4/3, 16/9, 14/9 etc.).

### **GENERAL DESCRIPTION**

The TDA8753A is a monolithic CMOS 8-bit video low-power analog-to-digital conversion interface for YUV signals. It converts the YUV analog input signal into 8-bit binary coded digital words in format 4 : 1 : 1 at a sampling rate of 20 MHz. All analog signal inputs are clamped. The device includes a digital sample rate converter for variable compression with a factor 1 to 2.

| SYMBOL           | PARAMETER                                  | CONDITIONS                               | MIN. | TYP.  | MAX. | UNIT |

|------------------|--------------------------------------------|------------------------------------------|------|-------|------|------|

| V <sub>DDA</sub> | analog supply voltage                      |                                          | 4.75 | 5.0   | 5.25 | V    |

| V <sub>DDD</sub> | digital supply voltage                     |                                          | 4.75 | 5.0   | 5.25 | V    |

| I <sub>DDA</sub> | analog supply current                      |                                          | -    | 55    | 63   | mA   |

| I <sub>DDD</sub> | digital supply current                     |                                          | -    | 45    | 55   | mA   |

| INL              | integral non-linearity                     | f <sub>clk</sub> = 16 MHz; ramp input    | -    | ±0.75 | -    | LSB  |

| DLE              | differential non-linearity                 | f <sub>clk</sub> = 16 MHz; ramp input; Y | -    | ±0.5  | 0.75 | LSB  |

|                  |                                            | $f_{clk}$ = 16 MHz; ramp input; U and V  | -    | ±0.6  | ±0.9 | LSB  |

| SNR              | signal-to-noise ratio<br>without harmonics | note 1                                   | 43   | -     | -    | dB   |

| f <sub>clk</sub> | maximum conversion rate                    |                                          | 20   | -     | -    | MHz  |

| P <sub>tot</sub> | total power dissipation                    | note 2                                   | -    | 500   | 650  | mW   |

### Notes

- 1. The signal-to-noise ratio without harmonics is measured using a 16 MHz clock frequency. This value is given for a 4.43 MHz input frequency on the Y channel (1.5 MHz on the U and V channels).

- The external resistor (between V<sub>DDA</sub> and I<sub>ref</sub>) fixing internal static currents influences P<sub>tot</sub>. The value of the resistor should be 5.6 kΩ (5%).

### **ORDERING INFORMATION**

| TYPE     | PACKAGE |                                                         |          |  |

|----------|---------|---------------------------------------------------------|----------|--|

| NUMBER   | NAME    | DESCRIPTION                                             | VERSION  |  |

| TDA8753A | SDIP42  | plastic shrink dual in-line package; 42 leads (600 mil) | SOT270-1 |  |

TDA8753A

3

### PINNING

| SYMBOL                | PIN | DESCRIPTION                             |  |

|-----------------------|-----|-----------------------------------------|--|

| Y7                    | 1   | Y data output, bit 7 (MSB)              |  |

| Y6                    | 2   | Y data output, bit 6                    |  |

| Y5                    | 3   | Y data output, bit 5                    |  |

| Y4                    | 4   | Y data output, bit 4                    |  |

| Y3                    | 5   | Y data output, bit 3                    |  |

| Y2                    | 6   | Y data output, bit 2                    |  |

| Y1                    | 7   | Y data output, bit 1                    |  |

| Y0                    | 8   | Y data output, bit 0 (LSB)              |  |

| V <sub>DDD2</sub>     | 9   | digital supply voltage 2, (+5 V)        |  |

| V <sub>SSD2</sub>     | 10  | digital ground 2                        |  |

| U1                    | 11  | U data output, bit 1 (n)                |  |

| U0                    | 12  | U data output, bit 0 (n – 1)            |  |

| V1                    | 13  | V data output, bit 1 (n)                |  |

| V0                    | 14  | V data output, bit 0 (n – 1)            |  |

| V <sub>SSD3</sub>     | 15  | digital ground 3                        |  |

| CLK                   | 16  | clock input                             |  |

| WEO                   | 17  | write enable output                     |  |

| WEI                   | 18  | write enable input                      |  |

| H <sub>ref</sub>      | 19  | horizontal reference signal input       |  |

| CLAMP                 | 20  | clamp control input                     |  |

| MODE1                 | 21  | test mode select                        |  |

| MODE0                 | 22  | test mode select                        |  |

| MSCAN                 | 23  | test pin                                |  |

| V <sub>SSD1</sub>     | 24  | digital ground 1                        |  |

| V <sub>DDD1</sub>     | 25  | digital supply voltage 1 (+5 V)         |  |

| V <sub>SSA5</sub>     | 26  | analog ground 5                         |  |

| I <sub>ref</sub>      | 27  | current level reference                 |  |

| DEC <sub>ref(L)</sub> | 28  | decoupling output from reference<br>LOW |  |

| V <sub>ref(H)</sub>   | 29  | reference voltage input (HIGH)          |  |

| V <sub>SSA4</sub>     | 30  | analog ground 4                         |  |

| V <sub>DDA3</sub>     | 31  | analog supply voltage 3, (+5 V)         |  |

| INV                   | 32  | V analog voltage input                  |  |

| V <sub>SSA3</sub>     | 33  | analog ground 3                         |  |

| V <sub>DDA2</sub>     | 34  | analog supply voltage 2 (+5 V)          |  |

| INU                   | 35  | U analog voltage input                  |  |

| V <sub>SSA2</sub>     | 36  | analog ground 2                         |  |

| V <sub>DDA1</sub>     | 37  | analog supply voltage 1 (+5 V)          |  |

| INY                   | 38  | Y analog voltage input                  |  |

| V <sub>SSA1</sub>     | 39  | analog ground 1                         |  |

|              |                                                                                                                                                                                           | _            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL       | PIN                                                                                                                                                                                       |              | ESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| UPCL<br>UPDA | 40<br>41                                                                                                                                                                                  | control clos | ck input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V50          | 41                                                                                                                                                                                        | data execu   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 12                                                                                                                                                                                        |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ,<br>C       | Y7 1<br>Y6 2<br>Y5 3<br>Y4 4<br>Y3 5<br>Y2 6<br>Y1 7<br>Y0 8<br>/SSD2 10<br>U1 11<br>U0 12<br>V1 13<br>V0 14<br>/SSD3 15<br>CLK 16<br>WEO 17<br>WEI 18<br>Href 19<br>SLAMP 20<br>IODE1 21 | TDA8753A     | 42 $\vee$ 50<br>41 $\cup$ PDA<br>40 $\cup$ PCL<br>39 $\vee$ SSA1<br>38 $\mid$ NY<br>37 $\vee$ DDA1<br>36 $\vee$ SSA2<br>35 $\mid$ NU<br>34 $\vee$ DDA2<br>33 $\vee$ SSA3<br>32 $\mid$ NV<br>31 $\vee$ DDA3<br>30 $\vee$ SSA4<br>29 $\vee$ ref(H)<br>28 $DEC_{ref(L)}$<br>27 $\mid$ ref<br>26 $\vee$ SSA5<br>25 $\vee$ DDD1<br>24 $\vee$ SSD1<br>23 $\mid$ SSA1<br>23 $\mid$ SSA1<br>23 $\mid$ SSA5<br>25 $\mid$ DDD1<br>24 $\vee$ SSD1<br>23 $\mid$ SSA1<br>23 $\mid$ SSA1<br>24 $\vee$ SSD1<br>23 $\mid$ SSA1<br>25 $\mid$ DDD2 |

|              | Fig.2                                                                                                                                                                                     | Pin configu  | uration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### TDA8753A

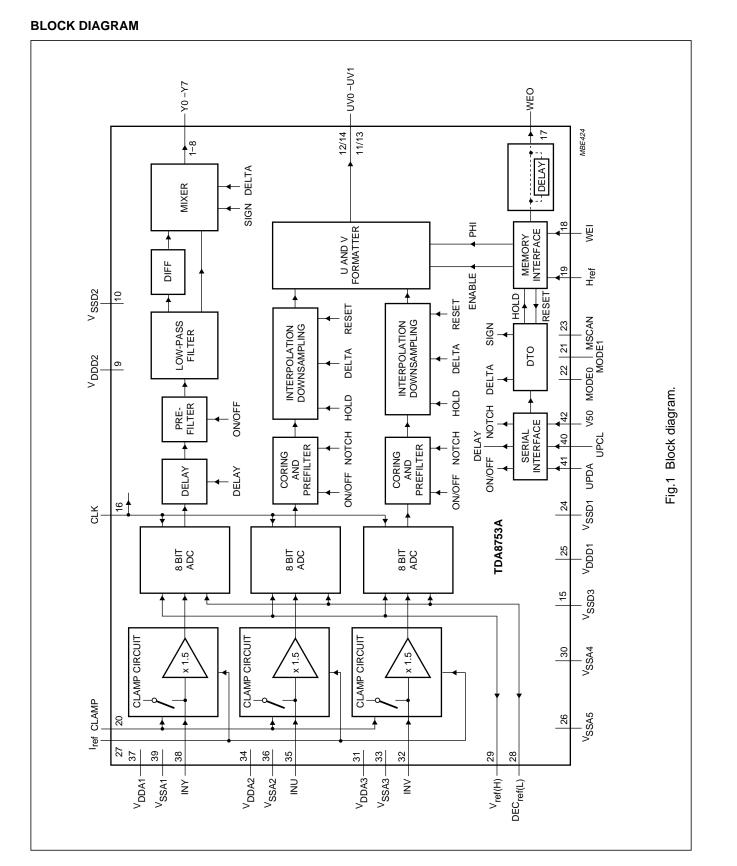

### FUNCTIONAL DESCRIPTION

#### Analog-to-digital converter

The TDA8753 implements 3 independent CMOS 8-bit analog-to-digital converters. The converters use a multi-step approach with offset compensated comparators.

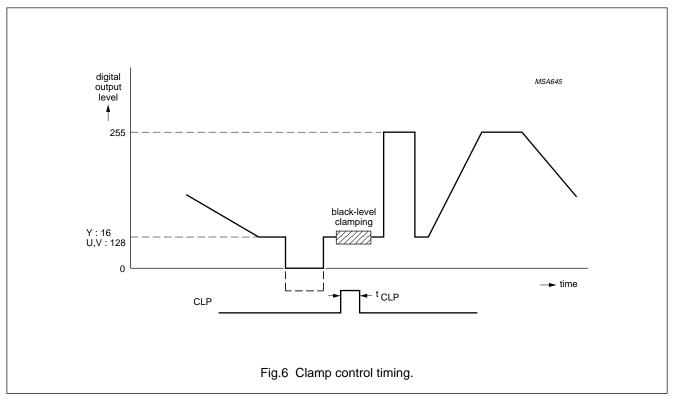

### Clamping

An internal clamping circuit is provided in each of the 3 analog channels. The analog pins INY, INV and INU are switched to on-chip clamping levels during an active pulse on the clamp input CLP. The clamping level in the Y channel is code level 16. The clamping level in the U/V channel is code level 128 (output code 0 in the 2's complement description) see Tables 3 and 4.

#### Sample rate converter

A sample rate converter is integrated in the TDA8753A to facilitate programming of the horizontal aspect ratio which can be varied from a factor 1 to 2.

This includes conversion from 16/9 to 14/9 and 4/3. In the U/V channel a linear interpolation is sufficient because of the four times oversampling.

#### Discrete time oscillator (DTO)

A discrete time oscillator is used to calculate for every sample of the phase delay that is needed for a given compression factor.

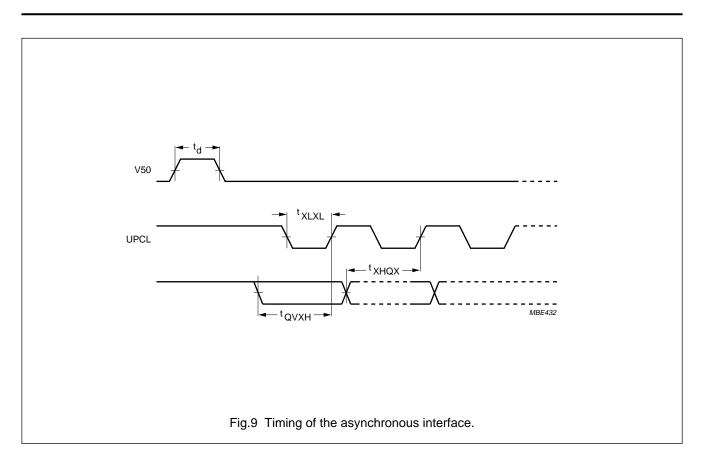

#### Serial interface (SIO)

All controls are sent to the TDA8753A via a serial microprocessor interface. Data from this interface will be made active at the vertical input pulse V50.

The TDA8753A has three addressable control registers which can be loaded via the signals UPDA and UPCL. The format of this bus is fixed according to mode 0 of the 8051 family UART at 1 Mbaud (8 bits are transmitted, LSB first).

### Serial interface protocol

#### POWER-ON STATE

When powered up the SIO is in an unknown state and all data in the registers is random. When signals are applied to UPCL and UPDA in this state, the behaviour is unpredictable. The only way to exit from this state to a known state is apply a V50 signal to the TDA8753A.

#### **INITIALIZATION STATE**

From power-on or any other state, the INIT state is entered (at the latest) one TDA8753A clock period after the end of the V50 HIGH state. In this state the F0, F1 and F2 TDA8753A registers are loaded with the values that are in the corresponding line buffers BF0, BF1 and BF2. The first time V50 is issued after power-on, this data is unknown. After a rising UPCL edge has been detected, the address reception state is entered.

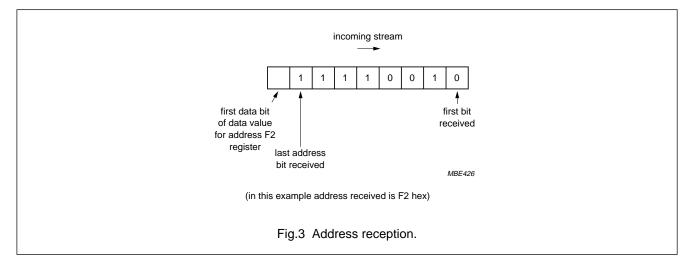

#### ADDRESS RECEPTION STATE

Bits are counted at each rising UPCL edge. The next 8 bits received on UPDA line are considered as address bits. The address reception is illustrated in Fig.3.

### TDA8753A

The TDA8753A registers have address F0, F1 and F2 hexadecimal notation. Whenever the received address (decoded on the first 8 bits received) is one of these, the event is recorded in such a way that the next data received by the TDA8753A will be captured in the line buffer BF0, BF1 and BF2 respectively.

When 8 bits have been received, the data reception state is entered. The address reception state can also be exited at any time when V50 goes HIGH. The F0, F1 and F2 registers may not be loaded properly if there is some activity in progress on the incoming line.

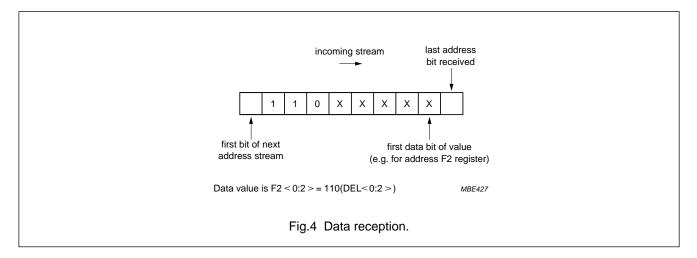

#### DATA RECEPTION STATE

The next 8 bits are considered as data bits according to the format of Fig.4.

When 8 data bits have been received, the data is recorded in the BF0, BF1 or BF2 line buffers if the previous address recorded was F0 hex, F1 hex or F2 hex respectively. The bit count is then reset to zero and the address reception state is entered. This state may be ended any time when V50 goes HIGH but in that condition F0, F1 and F2 registers may not be loaded properly.

| Table 1         Data allocation |

|---------------------------------|

|---------------------------------|

| ADDRESS | PARAMETER      | FUNCTION                                                                              | NUMBER<br>OF BITS | BIT<br>POSITION |

|---------|----------------|---------------------------------------------------------------------------------------|-------------------|-----------------|

| F0H     | CF             | compression factor value will be (1 + cf/255)<br>which results in a range from 1 to 2 | 8                 | 7:0             |

| F1H     | UV_CORING      | coring definition in U and V channels; see Table 5                                    | 2                 | 1:0             |

|         | UV_FILTER_TYPE | notch filter selection in U and V channels $(0 = 4 \text{ MHz}; 1 = 2 \text{ MHz})$   | 1                 | 2               |

|         | PRE_ON         | luminance prefilter active                                                            | 1                 | 3               |

|         | NOTCH_ON       | notch prefilter active                                                                | 1                 | 4               |

|         | DTO_ON         | DTO control                                                                           | 1                 | 5               |

|         | SEL_DTO_RES    | select DTO reset (0 = WE; 1 = $H_{ref}$ )                                             | 1                 | 6               |

|         | WEO_DEL_SEL    | select delay in WEO                                                                   |                   |                 |

| F2H     | Y_VAR_DELAY    | luminance delay compression (see Table 5)                                             |                   |                 |

|         |                | not used; load 0                                                                      | 5                 | 7:2             |

### TDA8753A

### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL                              | PARAMETER                                           | CONDITIONS         | MIN. | MAX.             | UNIT |

|-------------------------------------|-----------------------------------------------------|--------------------|------|------------------|------|

| V <sub>DDD</sub>                    | digital supply voltage                              |                    | -0.3 | 6.5              | V    |

| V <sub>DDA</sub>                    | analog supply voltage                               |                    | -0.3 | 6.5              | V    |

| V <sub>DDA</sub> – V <sub>DDD</sub> | supply voltage difference                           |                    | -0.5 | +0.5             | V    |

| VI                                  | input voltage                                       | referenced to AGND | _    | V <sub>DDA</sub> | V    |

| V <sub>clk(p-p)</sub>               | AC input voltage for switching (peak-to-peak value) | referenced to DGND | -    | V <sub>DDD</sub> | V    |

| T <sub>stg</sub>                    | storage temperature                                 |                    | -55  | +150             | °C   |

| T <sub>amb</sub>                    | operating ambient temperature                       |                    | 0    | +70              | °C   |

#### THERMAL RESISTANCE

| SYMBOL              | PARAMETER                                               | VALUE | UNIT |

|---------------------|---------------------------------------------------------|-------|------|

| R <sub>th j-a</sub> | thermal resistance from junction to ambient in free air | 45    | K/W  |

#### HANDLING

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling integrated circuits.

### CHARACTERISTICS

$V_{DDA} = V_{DDD} = 4.75$  to 5.25 V;  $V_{SSA}$  and  $V_{SSD}$  shorted together;  $V_{DDA} - V_{DDD} = -0.1$  to +0.1 V (see note 1);  $V_{ref(H)} = 2.38$  V;  $f_{clk} = 20$  MHz with 50% duty cycle; 5.6 k $\Omega$  (5%) connected between I<sub>ref</sub> and V<sub>DDA</sub>; CL = 15 pF;  $T_{amb} = 0$  to 70 °C; typical values measured at  $V_{DDA} = V_{DDD} = 5$  V; unless otherwise specified.

| SYMBOL           | PARAMETER                                                                                             | CONDITIONS                                   | MIN. | TYP. | MAX.             | UNIT |  |

|------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------|------|------|------------------|------|--|

| Supply           |                                                                                                       |                                              |      |      | ł                |      |  |

| V <sub>DDA</sub> | analog supply voltage                                                                                 |                                              | 4.75 | 5.0  | 5.25             | V    |  |

| V <sub>DDD</sub> | digital supply voltage                                                                                |                                              | 4.75 | 5.0  | 5.25             | V    |  |

| I <sub>DDA</sub> | analog supply current                                                                                 |                                              | _    | 55   | 63               | mA   |  |

| I <sub>DDD</sub> | digital supply current                                                                                |                                              | -    | 45   | 55               | mA   |  |

| Digital inputs a | Digital inputs and clock input (WE, H <sub>ref</sub> , CLAMP, MODE1, MODE0, SCCL, UPCL, UPDA and V50) |                                              |      |      |                  |      |  |

| V <sub>IL</sub>  | LOW level input voltage                                                                               |                                              | 0    | -    | 0.8              | V    |  |

| V <sub>IH</sub>  | HIGH level input voltage                                                                              |                                              | 2.0  | -    | V <sub>DDD</sub> | V    |  |

| Cl               | input capacitance                                                                                     |                                              | _    | 7    | 15               | pF   |  |

| 1L <sub>1</sub>  | input leakage current                                                                                 | V <sub>I</sub> = 0 V; V <sub>DDD</sub> = 5 V | -10  | -    | +10              | μA   |  |

| SYMBOL                 | PARAMETER                                                                   | CONDITIONS                           | MIN.  | TYP.  | MAX.             | UNIT |

|------------------------|-----------------------------------------------------------------------------|--------------------------------------|-------|-------|------------------|------|

| Clamp and ref          | erences [I <sub>ref</sub> , DEC <sub>ref(L)</sub> and V <sub>ref(H)</sub> ] |                                      |       | 1     | - I              | _!   |

| A <sub>CL</sub>        | clamping accuracy                                                           | Y                                    | -4    | -     | +1               | LSB  |

|                        |                                                                             | U and V                              | -1    | -     | +1               | LSB  |

| C <sub>clamp</sub>     | serial clamp capacitor                                                      |                                      | 10    | 22    | _                | nF   |

| Z <sub>ADC</sub>       | internal impedance between pin 29 and V <sub>SSA</sub>                      |                                      | _     | 420   | -                | Ω    |

| V <sub>ref(H)</sub>    | converter reference HIGH, applied to pin 29                                 |                                      | _     | 2.38  | -                | V    |

| V <sub>DECref(L)</sub> | converter reference voltage LOW, applied to pin 28                          | V <sub>ref(H)</sub> = 2.38 V         | _     | 0.39  | -                | V    |

| Y analog input         | t (INY); V <sub>ref(H)</sub> = 2.38 V, V <sub>ref(L)</sub> = 0.39           | V; see Table 4                       |       |       |                  |      |

| V <sub>i(p-p)</sub>    | input voltage, full range<br>(peak-to-peak value)                           | ramp input                           | _     | 1.26  | -                | V    |

| li                     | input current                                                               | clamp non-active                     | -     | 5     | 100              | nA   |

| CI                     | input capacitance                                                           |                                      | -     | _     | 15               | pF   |

| U,V analog inp         | outs (INU and INV); V <sub>ref(H)</sub> = 2.38 V, V                         | / <sub>ref(L)</sub> = 0.39 V; see Ta | ble 4 | 1     |                  |      |

| V <sub>i(p-p)</sub>    | input voltage (peak-to-peak value)                                          | ramp input                           | -     | 1.26  | _                | V    |

| i                      | input current                                                               | clamp non-active                     | _     | 5     | 100              | nA   |

| CI                     | input capacitance                                                           |                                      | -     | -     | 15               | pF   |

| Inputs isolatio        | 'n                                                                          | 1                                    |       |       |                  |      |

| α <sub>act</sub>       | crosstalk between INY, INU and INV                                          |                                      | _     | -     | -50              | dB   |

| Digital outputs        | s (Y0 to Y7, U1, U0, V1 and V0); see                                        | Table 3                              |       | 1     | -                |      |

| V <sub>OL</sub>        | LOW level output voltage                                                    | I <sub>OL</sub> = 1.6 mA             | 0     | _     | 0.5              | V    |

| V <sub>он</sub>        | HIGH level output voltage                                                   | I <sub>OH</sub> = 0.4 mA             | 2.4   | _     | V <sub>DDD</sub> | V    |

|                        | processing (f <sub>CLK</sub> = 20 MHz)                                      | 1                                    | Į     | -1    | -                |      |

| G <sub>diff</sub>      | differential gain                                                           | note 2                               | _     | 1.5   | _                | %    |

| $\Phi_{diff}$          | differential phase                                                          | note 2                               | _     | 1.0   | _                | deg  |

| f <sub>all</sub>       | harmonics (full scale) all                                                  | note 3; Y                            | _     | -53   | _                | dB   |

|                        | components                                                                  | U and V                              | _     | -55   | _                | dB   |

| SVR                    | supply voltage ripple rejection                                             | note 4                               | _     | 2     | _                | %/V  |

| В                      | bandwidth                                                                   | –1 dB; note 5                        | _     | 6     | _                | MHz  |

| Transfer funct         | ion (f <sub>cik</sub> = 16 MHz)                                             |                                      |       |       |                  | _    |

| INL                    | integral non-linearity                                                      | ramp input                           | _     | ±0.75 | _                | LSB  |

| DNL                    | differential non-linearity                                                  | ramp input; Y                        | _     | ±0.5  | ±0.75            | LSB  |

|                        |                                                                             | ramp input; U and V                  | _     | ±0.6  | ±0.9             | LSB  |

| SNR                    | signal-to-noise ratio without                                               | note 6; Y                            | 41    | 44.5  | _                | dB   |

|                        | harmonics                                                                   | U and V                              | 42    | 46    | _                | dB   |

| SYMBOL                       | PARAMETER                                        | CONDITIONS                 | MIN. | TYP. | MAX. | UNIT |

|------------------------------|--------------------------------------------------|----------------------------|------|------|------|------|

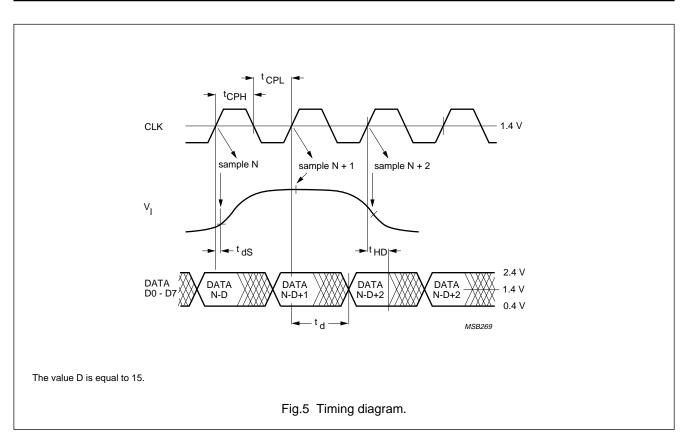

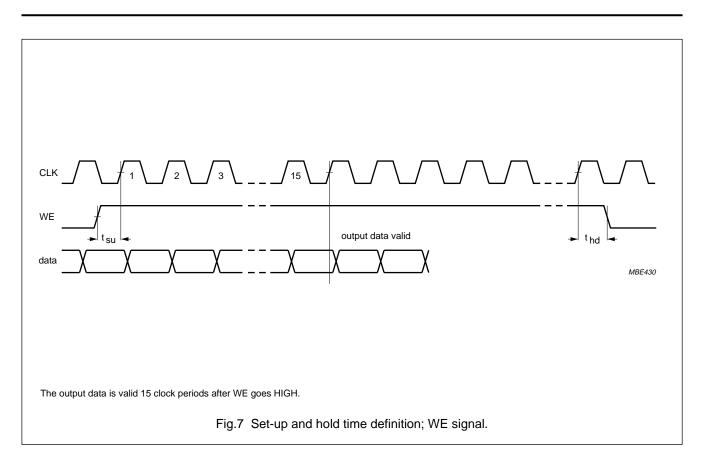

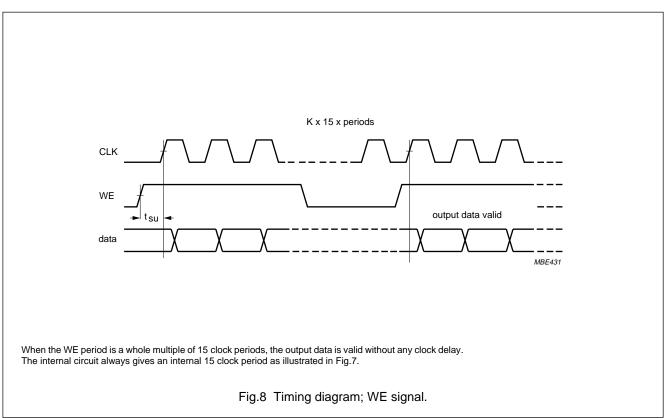

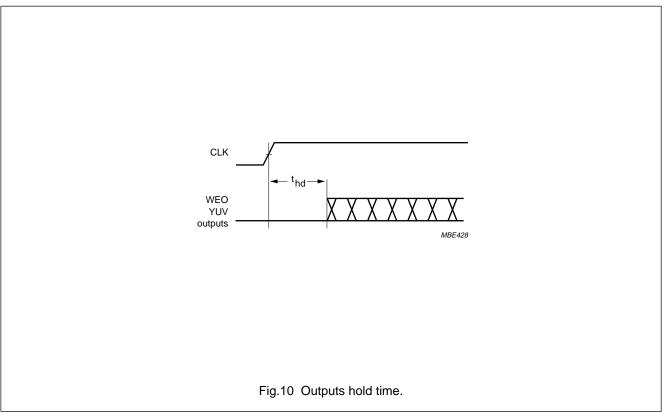

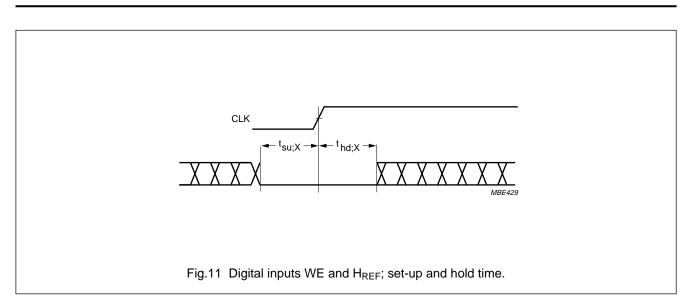

| Timing (f <sub>clk</sub> = 2 | 20 MHz; C <sub>L</sub> = 15 pF); see Figs 7 and  | 10; note 7                 | 1    | 1    | 1    |      |

| f <sub>clk</sub>             | maximum input clock frequency                    |                            | 20   | -    | -    | MHz  |

| t <sub>CP(H)</sub>           | clock pulse width HIGH                           |                            | 22   | -    | _    | ns   |

| t <sub>CP(L)</sub>           | clock pulse width LOW                            |                            | 22   | _    | _    | ns   |

| t <sub>ds</sub>              | sampling delay                                   |                            | -    | 4    | _    | ns   |

| t <sub>hd</sub>              | output hold time                                 |                            | 7    | -    | _    | ns   |

| t <sub>d</sub>               | output delay time                                |                            | _    | -    | 32   | ns   |

| t <sub>CLKr</sub>            | clock rise time                                  |                            | 3    | 5    | _    | ns   |

| t <sub>CLKf</sub>            | clock fall time                                  |                            | 3    | 5    | _    | ns   |

| t <sub>su;Href</sub>         | HREF set-up time                                 |                            | 7    | -    | _    | ns   |

| t <sub>hd;Href</sub>         | HREF hold time                                   |                            | 3    | -    | _    | ns   |

| tr                           | data output rise time                            |                            | _    | 10   | _    | ns   |

| t <sub>f</sub>               | data output fall time                            |                            | -    | 10   | _    | ns   |

| t <sub>CLP</sub>             | minimum time for active clamp pulse width        |                            | 2.3  | 2.5  | -    | μs   |

| t <sub>su;WE</sub>           | WE set-up time                                   |                            | 7    | -    | _    | ns   |

| t <sub>hd;WE</sub>           | WE hold time                                     |                            | 3    | -    | _    | ns   |

| t <sub>XLXL</sub>            | serial port clock cycle time                     | f <sub>xtal</sub> = 12 MHz | 1    | _    | _    | μs   |

| t <sub>QVXH</sub>            | output data set-up to rising edge of clock       |                            | 700  | -    | -    | ns   |

| t <sub>XHQH</sub>            | output data hold time after rising edge of clock |                            | 50   | -    | -    | ns   |

| t <sub>W</sub>               | V50 pulse duration                               |                            | 2    | _    | _    | ms   |

| t <sub>VC</sub>              | V50 to clock time                                |                            | 2    | -    | _    | ms   |

| Sample rate co               | onverter (f <sub>clk</sub> = 20 MHz)             |                            |      | -    | -    |      |

| ΦΥ                           | Y phase accuracy                                 | $f_{iY} = 0$ to 5 MHz      | _    | ±1   | _    | ns   |

| FUV                          | UV phase accuracy                                | $f_{iUV} = 0$ to 1.5 MHz   | _    | ±4   | _    | ns   |

| Y <sub>fr</sub>              | Y frequency response                             | $f_{iY} = 0$ to 5 MHz      | _    | ±0.5 | _    | dB   |

| UV <sub>fr</sub>             | UV frequency response                            | $f_{iUV} = 0$ to 1.5 MHz   | _    | ±0.5 | _    | dB   |

| Y <sub>step</sub>            | Y step size                                      |                            | _    | 1    | _    | ns   |

| UV <sub>step</sub>           | UV step size                                     |                            | -    | 4    | _    | ns   |

### TDA8753A

### Notes to the Characteristics

- 1. V<sub>DDA</sub> and V<sub>DDD</sub> should be supplied from the same power supply and decoupled separately.

- 2. Measurement carried out using video amplifier type VM700A, where the video analog signal (Y channel) is reconstructed via the DAC.

- 3. The input conditions are related as follows:

$$\begin{split} Y - V_{i(p-p)} &= 1.26 \text{ V}, \text{ } \text{f}_i = 4.43 \text{ MHz} \\ \text{U and } V - V_{i(p-p)} &= 1.26 \text{ V}, \text{ } \text{f}_i = 1.5 \text{ MHz}. \end{split}$$

- 4. Supply voltage ripple rejection: SVR; relative variation of the full-scale range of analog input for a supply voltage variation of 0.5 V. SVR =  $[\Delta (V_{I(0)} V_{I(255)})/[V_{I(0)} V_{I(255)}]/\Delta V_{DDA}$ .

- 5. The –1 dB bandwidth is the frequency value for which the analog reconstructed (glitch-free) output signal is compressed in term of number of codes, by –1 dB (respectively for –3 dB bandwidth).

- The signal-to-noise ratio without harmonics is measured under a 16 MHz clock frequency. This value is given for a 4.43 MHz input frequency on the Y channel (1.5 MHz on the U and V channels).

- 7. Output data acquisition: Output data is available after the maximum delay of t<sub>d</sub>.

#### Table 2Mode selection

| MODE1 | MODE0 | MODE                 |

|-------|-------|----------------------|

| 0     | 0     | normal configuration |

Table 3

Output data coding

| OUTPUT PORT | BIT | OUTPUT DATA        |                  |                  |                  |

|-------------|-----|--------------------|------------------|------------------|------------------|

| Y           | Y7  | Y <sub>0</sub> 7   | Y <sub>1</sub> 7 | Y <sub>2</sub> 7 | Y <sub>3</sub> 7 |

|             | Y6  | Y <sub>0</sub> 6   | Y <sub>1</sub> 6 | Y <sub>2</sub> 6 | Y <sub>3</sub> 6 |

|             | Y5  | Y <sub>0</sub> 5   | Y <sub>1</sub> 5 | Y <sub>2</sub> 5 | Y <sub>3</sub> 5 |

|             | Y4  | Y <sub>0</sub> 4   | Y <sub>1</sub> 4 | Y <sub>2</sub> 4 | Y <sub>3</sub> 4 |

|             | Y3  | Y <sub>0</sub> 3   | Y <sub>1</sub> 3 | Y <sub>2</sub> 3 | Y <sub>3</sub> 3 |

|             | Y2  | Y <sub>0</sub> 2   | Y <sub>1</sub> 2 | Y <sub>2</sub> 2 | Y <sub>3</sub> 2 |

|             | Y1  | Y <sub>0</sub> 1   | Y <sub>1</sub> 1 | Y <sub>2</sub> 1 | Y <sub>3</sub> 1 |

|             | Y0  | Y <sub>0</sub> 0   | Y <sub>1</sub> 0 | Y <sub>2</sub> 0 | Y <sub>3</sub> 0 |

| U           | U1  | $\overline{U}_07$  | U <sub>0</sub> 5 | U <sub>0</sub> 3 | U <sub>0</sub> 1 |

|             | U0  | U <sub>0</sub> 6   | U <sub>0</sub> 4 | U <sub>0</sub> 2 | U <sub>0</sub> 0 |

| V           | V1  | $\overline{V}_0$ 7 | V <sub>0</sub> 5 | V <sub>0</sub> 3 | V <sub>0</sub> 1 |

|             | V0  | V <sub>0</sub> 6   | V <sub>0</sub> 4 | V <sub>0</sub> 2 | V <sub>0</sub> 0 |

| STEP      | INPUT VOLTAGE | INTERNAL BINARY OUTPUTS | REMARKS                         |

|-----------|---------------|-------------------------|---------------------------------|

| Underflow | <0.26         | 0000000                 |                                 |

| 0         | 0.26          | 0000000                 | V <sub>DECref(L)</sub> /1.5     |

| 1         | -             | 0000001                 |                                 |

|           |               |                         |                                 |

| 16        | 0.34          | 00010000                | clamp level of Y channel        |

|           |               |                         |                                 |

| 128       | 0.89          | 1000000                 | clamp level of U and V channels |

|           |               |                         |                                 |

| 254       | _             | 1111110                 |                                 |

| 255       | 1.52          | 1111111                 | V <sub>ref(H)</sub> - 0.1 V/1.5 |

| Overflow  | >1.52         | 1111111                 |                                 |

Table 4

Internal ADC data coding as a function of the analog input

Table 5 Coring and luminance delay

| UV_CORING |      | INTERNAL CORING CORRECTION                     | Y_VAR_DELAY |      | INTERNAL DELAY FOR Y PATH           |  |

|-----------|------|------------------------------------------------|-------------|------|-------------------------------------|--|

| F1:1      | F1:0 | IN U AND V CHANNELS<br>(AROUND CODE 128 LEVEL) | F2:1        | F2:0 | AT PREFILTER INPUT<br>(CLOCK PULSE) |  |

| 0         | 0    | coring off                                     | 0           | 0    | 0                                   |  |

| 0         | 1    | +1/-1                                          | 0           | 1    | 1                                   |  |

| 1         | 0    | +1/-0                                          | 1           | 0    | 2                                   |  |

| 1         | 1    | +2/-1                                          | 1           | 1    | 3                                   |  |

## TDA8753A

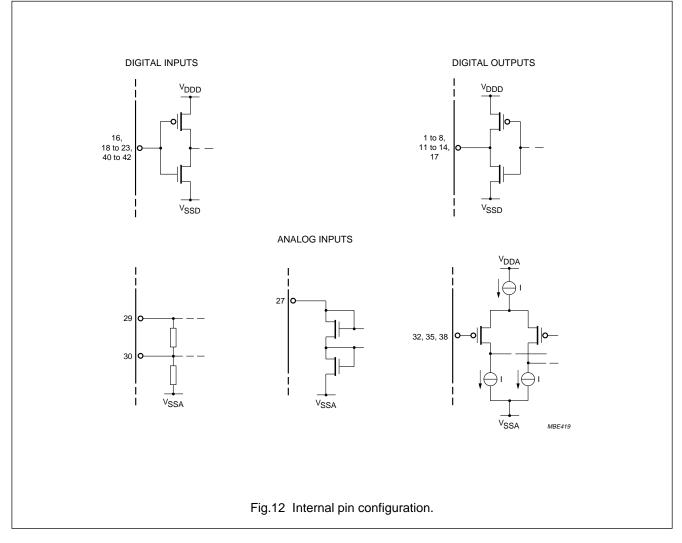

### INTERNAL PIN CONFIGURATION

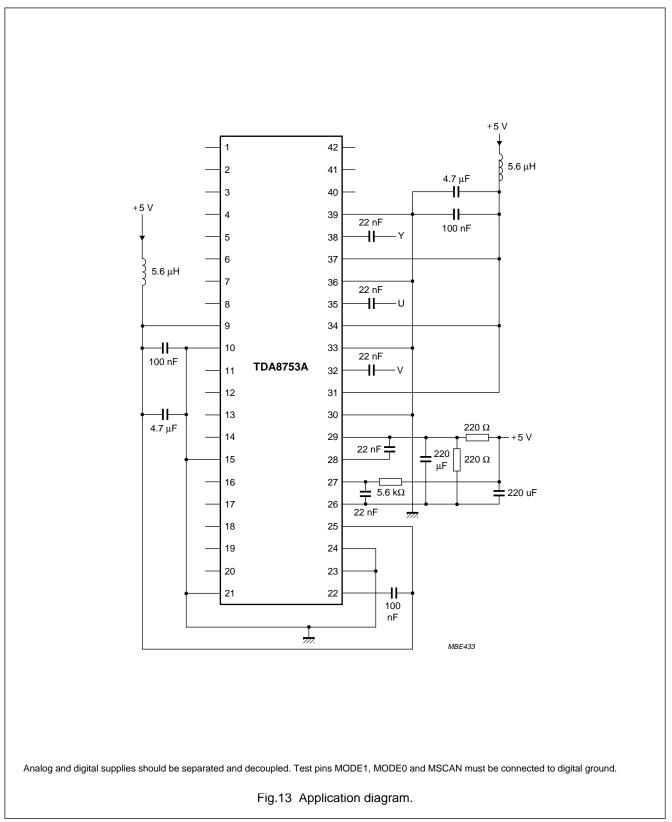

### APPLICATION INFORMATION

**Philips Semiconductors**

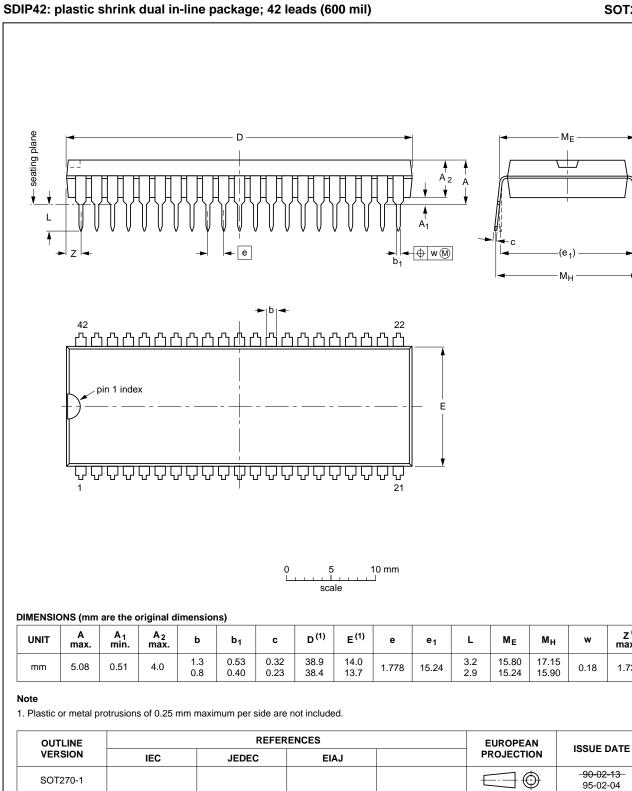

### PACKAGE OUTLINE

TDA8753A

SOT270-1

Z <sup>(1)</sup> max.

1.73

### TDA8753A

### SOLDERING

### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our *"IC Package Databook"* (order code 9398 652 90011).

#### Soldering by dipping or by wave

The maximum permissible temperature of the solder is 260 °C; solder at this temperature must not be in contact with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature ( $T_{stg max}$ ). If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

#### **Repairing soldered joints**

Apply a low voltage soldering iron (less than 24 V) to the lead(s) of the package, below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300 °C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400 °C, contact may be up to 5 seconds.

### DEFINITIONS

| Data sheet status         |                                                                                       |

|---------------------------|---------------------------------------------------------------------------------------|

| Objective specification   | This data sheet contains target or goal specifications for product development.       |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later. |

| Product specification     | This data sheet contains final product specifications.                                |

| Limiting values           |                                                                                       |

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### Application information

Where application information is given, it is advisory and does not form part of the specification.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.