INTEGRATED CIRCUITS

Product specification Supersedes data of November 1992 File under Integrated Circuits, IC02 1995 Mar 07

# **Philips Semiconductors**

#### FEATURES

- Two RGB/YUV selectable clamped inputs with associated synchronization

- RGB/YUV matrix

- 3-state switching with an OFF-state

- Selectable gain

- I<sup>2</sup>C-bus or non-I<sup>2</sup>C-bus mode

- Address selection for 7 devices

- Fast switching.

### **GENERAL DESCRIPTION**

The TDA8443A is a general purpose two-channel switch for YUV or RGB signals. One channel provides matrixing from RGB to YUV, which can be bypassed.

The IC is controlled via  $I^2C$ -bus by seven different addresses or can be used in a non- $I^2C$ -bus mode. In the non- $I^2C$ -bus mode, control of the circuit is achieved by DC voltages.

#### QUICK REFERENCE DATA

| SYMBOL              | PARAMETER                       | CONDITIONS         | MIN. | TYP. | MAX. | UNIT |

|---------------------|---------------------------------|--------------------|------|------|------|------|

| V <sub>P</sub>      | supply voltage (pin 18)         |                    | 10.8 | 12.0 | 13.2 | V    |

| I <sub>P</sub>      | supply current                  |                    | -    | 65   | 90   | mA   |

| RGB/YUV cha         | annels                          |                    |      |      |      |      |

| Z <sub>19-22</sub>  | output impedance (pin 19)       |                    | -    | 7    | 30   | Ω    |

| Z <sub>20-22</sub>  | output impedance (pin 20)       |                    | _    | 7    | 30   | Ω    |

| Z <sub>21-22</sub>  | output impedance (pin 21)       |                    | -    | 7    | 30   | Ω    |

| В                   | bandwidth                       | -3 dB; mode 0 or 2 | -    | 25   | -    | MHz  |

|                     |                                 | +3 dB; mode 0 or 2 | -    | 12   | -    | MHz  |

|                     |                                 | ±3 dB; mode 1      | -    | 10   | -    | MHz  |

| V <sub>O(p-p)</sub> | maximum output amplitude of YUV | gain × 1           | 2.1  | _    | -    | V    |

|                     | signals (peak-to-peak value)    | gain × 2           | 4.2  | -    | -    | V    |

| T <sub>amb</sub>    | operating ambient temperature   |                    | 0    | -    | +70  | °C   |

#### ORDERING INFORMATION

| TYPE     | PACKAGE |                                                  |          |  |  |

|----------|---------|--------------------------------------------------|----------|--|--|

| NUMBER   | NAME    | DESCRIPTION                                      | VERSION  |  |  |

| TDA8443A | DIP24   | plastic dual in-line package; 24 leads (600 mil) | SOT101-1 |  |  |

### TDA8443A

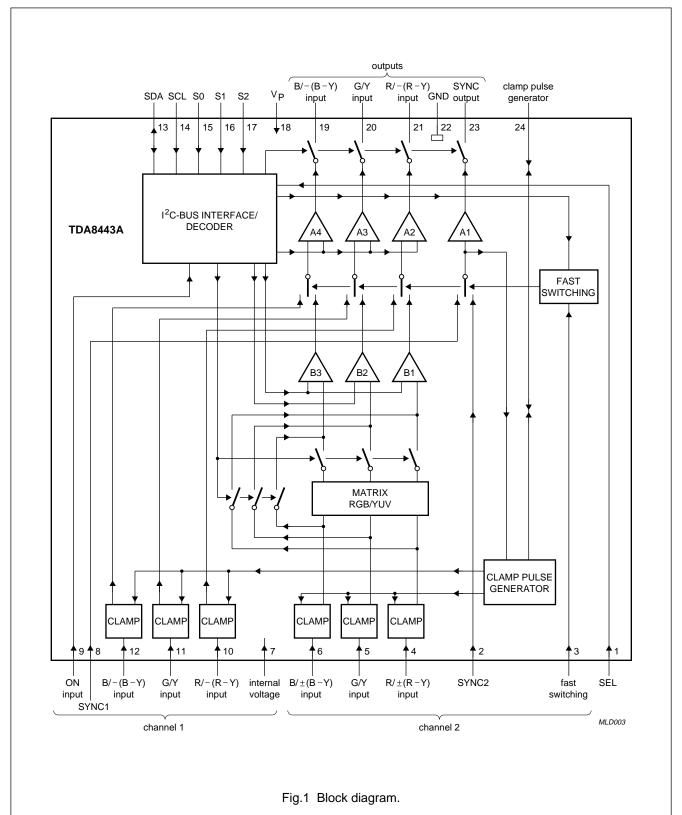

#### **BLOCK DIAGRAM**

TDA8443A

## I<sup>2</sup>C-bus controlled YUV/RGB switch

#### PINNING

| FINNING     |     |                                                      |                 |                 |

|-------------|-----|------------------------------------------------------|-----------------|-----------------|

| SYMBOL      | PIN | DESCRIPTION                                          |                 |                 |

| SEL         | 1   | select input<br>(non-I <sup>2</sup> C-bus mode only) |                 |                 |

| SYNC2       | 2   | synchronization input for<br>Channel 2               |                 |                 |

| FS          | 3   | fast switching input                                 |                 | <b>1</b>        |

| R/±(R–Y)IN  | 4   | R or (R-Y) signal input                              | SEL 1           | 24 CLAMP        |

| G/Y IN      | 5   | G or Y signal input                                  | SYNC2 2         | 23 SYNC         |

| B/±(B–Y)IN  | 6   | B or (B–Y) signal input                              | FS 3            | 22 GND          |

| VINT        | 7   | internal voltage supply                              | R/±(R - Y) IN 4 | 21] R/-(R-Y) OI |

| SYNC1       | 8   | synchronization input for<br>Channel 1               | G/Y IN 5        | 20 G/Y OUT      |

| ON          | 9   | ON input                                             |                 | 19 B/-(B-Y) OL  |

| R/-(R-Y)IN  | 10  | R or –(R–Y) signal input                             | V INT 7         | 18 VP           |

| G/Y IN      | 11  | G or Y signal input                                  | SYNC1 8         | 17 S2           |

| B/-(B-Y)IN  | 12  | B or –(B–Y) signal input                             | ON 9            | 16 S1           |

| SDA         | 13  | serial data input/output; l <sup>2</sup> C-bus       | R/-(R-Y) IN 10  | 15 S0           |

| SCL         | 14  | serial clock input; I <sup>2</sup> C-bus             | G/Y IN 11       |                 |

| S0          | 15  | address selection input 0                            |                 | 14 SCL          |

| S1          | 16  | address selection input 1                            | B/- (B-Y) IN 12 | 13 SDA          |

| S2          | 17  | address selection input 2                            |                 | MLD004          |

| VP          | 18  | supply voltage                                       |                 |                 |

| B/-(B-Y)OUT | 19  | B or –(B–Y) signal output                            |                 |                 |

| G/Y OUT     | 20  | G or Y signal output                                 |                 |                 |

| R/-(R-Y)OUT | 21  | R or –(R–Y) signal output                            |                 |                 |

| GND         | 22  | ground                                               |                 |                 |

| SYNC        | 23  | synchronization output                               |                 |                 |

| CLAMP       | 24  | clamping pulse generator<br>input/output             | Fig.2 Pin c     | configuration.  |

### TDA8443A

#### FUNCTIONAL DESCRIPTION

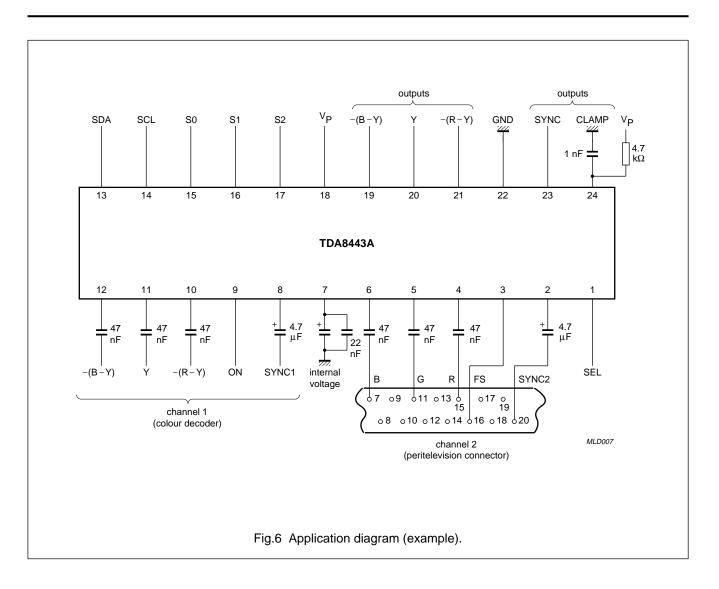

The circuit contains two sets of inputs (see Fig.1). Both channels can receive RGB or YUV signals. Each set of inputs has its own synchronization input, which internally generates a pulse to clamp the inputs. The internal clamping pulse can also be controlled by a signal (e.g. a sandcastle pulse) applied to pin 24. The pulse will occur during the time that the signal at pin 24 is between 5.5 and 6.5 V. If both a sync signal and a pin 24 signal are used the signal should be applied to pin 24 via a 1 k $\Omega$  resistor.

RGB signals of Channel 2 can be matrixed to YUV signals.

The outputs can be set in a high impedance OFF state, which allows the use of seven devices in parallel  $(I^2C$ -bus mode).

The circuit can be controlled by an I<sup>2</sup>C-bus compatible microcontroller or directly by DC voltages. The fast switching input can be operated via pin 16 of the peritelevision connector.

### I<sup>2</sup>C-bus mode

The protocol for the devices in  $I^2C$ -bus mode is shown in Fig.3.

| Table 1 | Protocol bit description |

|---------|--------------------------|

|---------|--------------------------|

| BIT        | DESCRIPTION                              |

|------------|------------------------------------------|

| STA        | start condition                          |

| MA2 to MA0 | address selection bits; see Table 2      |

| ACK        | acknowledge bit                          |

| D7         | channel selection bit; see Table 3       |

| D6         | matrix selection bit; see Table 3        |

| D5 to D3   | gain control bits; see Table 4           |

| D2         | fast switching priority bit; see Table 5 |

| D1 and D0  | output state control bits; see Table 6   |

| STO        | stop condition                           |

### TDA8443A

| Table 2 Address selection | Table 2 | Address selection |

|---------------------------|---------|-------------------|

|---------------------------|---------|-------------------|

| ADD         | ADDRESS SELECT PINS <sup>(1)(2)</sup> |             |      | DDRESS SELECT B | ITS  |

|-------------|---------------------------------------|-------------|------|-----------------|------|

| S2 (PIN 17) | S1 (PIN 16)                           | S0 (PIN 15) | MA2  | MA1             | MAO  |

| L           | L                                     | L           | *(3) | *(3)            | *(3) |

| L           | L                                     | Н           | 0    | 0               | 1    |

| L           | Н                                     | L           | 0    | 1               | 0    |

| L           | Н                                     | н           | 0    | 1               | 1    |

| Н           | L                                     | L           | 1    | 0               | 0    |

| Н           | L                                     | н           | 1    | 0               | 1    |

| Н           | н                                     | L           | 1    | 1               | 0    |

| Н           | н                                     | н           | 1    | 1               | 1    |

#### Notes

1. L = LOW level input voltage.

2. H = HIGH level input voltage.

3.  $* = \text{non-I}^2\text{C-bus operation.}$

#### Table 3 Mode control bits D7 and D6

| MODE | D7 | D6 | FUNCTION                          |

|------|----|----|-----------------------------------|

| 0    | 0  | 0  | Channel 2 selected, no matrix     |

| 1    | 0  | 1  | Channel 2 selected, matrix active |

| 2    | 1  | 0  | Channel 1 selected                |

| _    | 1  | 1  | not allowed                       |

Table 4

Gain setting (see also Table 9)

| D5 | D4 | D3 | A1     | A2, A3, A4 | B1, B3 | B2   |

|----|----|----|--------|------------|--------|------|

| 0  | 0  | 0  | 1      | 1          | -1     | 0.45 |

| 0  | 0  | 1  | 1      | 1          | 1      | 1    |

| 0  | 1  | 0  | not al | lowed      | —      | _    |

| 0  | 1  | 1  | 1      | 1          | -1     | 0.45 |

| 1  | 0  | 0  | 2      | 2          | -1     | 0.45 |

| 1  | 0  | 1  | 2      | 1          | 1      | 1    |

| 1  | 1  | 0  | 2      | 2          | 1      | 1    |

| 1  | 1  | 1  | 2      | 1          | -1     | 0.45 |

#### **Matrix equations**

The relationship between output and input signals of the matrix is as follows:

Y = 0.3R + 0.59G + 0.11B

R-Y = 0.7R - 0.59G - 0.11B

B-Y = -0.3R - 0.59G + 0.89B

### TDA8443A

Table 5

Priority/fast switching bit D2

| D2 | FAST SWITCHING<br>(PIN 3) | MODE                        |

|----|---------------------------|-----------------------------|

| 0  | X <sup>(1)</sup>          | 0 to 2, depending on D7, D6 |

| 1  | 0.4 V                     | 2                           |

#### Note

1. X = don't care.

#### Table 6 Output state control bits

| D1 | D0               | PIN 9            | FUNCTION |

|----|------------------|------------------|----------|

| 0  | X <sup>(1)</sup> | X <sup>(1)</sup> | OFF      |

| 1  | 0                | L                | OFF      |

| 1  | 0                | Н                | ON       |

| 1  | 1                | X <sup>(1)</sup> | ON       |

#### Note

1. X = don't care.

#### Power-on reset

If the circuit is switched on in the  $l^2C$ -bus mode, all bits of D0 to D7 are set to zero.

| Table 7 | Non-I <sup>2</sup> C-bus mode | (S2 = S1 = S0 = L) |

|---------|-------------------------------|--------------------|

|---------|-------------------------------|--------------------|

| CONTROL MODE SWITCHEI |               | MODE SWITCHED BY | GAIN                     | SETTINGS | B1, B3 | B2 |      |

|-----------------------|---------------|------------------|--------------------------|----------|--------|----|------|

| PIN 13                | <b>PIN 14</b> | PIN 1            | FS (PIN 3) A1 A4, A3, A2 |          | DZ     |    |      |

| L                     | L             | L                | 2 or 0                   | 1        | 1      | 1  | 1    |

| L                     | L             | Н                | 2 or 0                   | 1        | 2      | 1  | 1    |

| L                     | Н             | L                | 2 or 1                   | 1        | 1      | -1 | 0.45 |

| L                     | Н             | Н                | 2 or 0                   | 1        | 1      | -1 | 0.45 |

| Н                     | L             | L                | 2 or 0                   | 2        | 1      | 1  | 1    |

| Н                     | L             | Н                | 2 or 0                   | 2        | 2      | 1  | 1    |

| Н                     | Н             | L                | 2 or 1                   | 2        | 1      | -1 | 0.45 |

| Н                     | Н             | Н                | 2 or 0                   | 2        | 1      | -1 | 0.45 |

#### **Table 8**Fast switching input (pin 3)

| FS       | MODE SELECTED                      |

|----------|------------------------------------|

| ≤0.4 V   | mode 2                             |

| 1 to 3 V | mode 0 or mode 1 as set by control |

| Table 9 | ON  | input ( | pin 9)  |

|---------|-----|---------|---------|

| 10010 0 | 011 | mpary   | piii 0) |

| ON | FUNCTION                                           |

|----|----------------------------------------------------|

| L  | OFF; no output signal; high impedance<br>OFF-state |

| Н  | function is determined in Table 7                  |

### TDA8443A

#### LIMITING VALUES

In accordance with the Absolute Maximum System (IEC 134).

| SYMBOL              | PARAMETER                     |      | MAX.                 | UNIT |

|---------------------|-------------------------------|------|----------------------|------|

| VP                  | supply voltage (pin 18)       | _    | 14                   | V    |

| V <sub>I(SDA)</sub> | input voltage (pin 13)        | -0.3 | 14                   | V    |

| V <sub>I(SCL)</sub> | input voltage (pin 14)        | -0.3 | 14                   | V    |

| V <sub>n</sub>      | input voltage any other pin   | -0.3 | V <sub>P</sub> + 0.3 | V    |

| I <sub>O(max)</sub> | maximum output current        | -    | 20                   | mA   |

| T <sub>amb</sub>    | operating ambient temperature | 0    | +70                  | °C   |

| T <sub>stg</sub>    | IC storage temperature range  | -55  | +125                 | °C   |

| Tj                  | maximum junction temperature  | -    | +125                 | °C   |

### CHARACTERISTICS

$V_P$  = 12 V;  $T_{amb}$  = 25 °C; unless otherwise specified.

| SYMBOL              | PARAMETER                                      | CONDITIONS                                               | MIN. | TYP. | MAX. | UNIT |

|---------------------|------------------------------------------------|----------------------------------------------------------|------|------|------|------|

| Supply              | 1                                              |                                                          | 1    |      |      |      |

| V <sub>P</sub>      | supply voltage (pin 18)                        |                                                          | 10.8 | 12.0 | 13.2 | V    |

| Ι <sub>Ρ</sub>      | supply current                                 |                                                          | _    | 65   | 90   | mA   |

| RGB/YUV             | channels                                       |                                                          |      |      | •    |      |

| G <sub>abs</sub>    | absolute gain difference<br>(programmed value) |                                                          | _    | 0    | 10   | %    |

| G <sub>rel</sub>    | relative gain difference                       | between Y output and the (R–Y) and (B–Y) channel outputs | -    | 0    | 10   | %    |

|                     |                                                | between any other two channels                           | -    | 0    | 5    | %    |

| l <sub>l</sub>      | input current                                  |                                                          | -    | 0.5  | 1.0  | μA   |

| Z <sub>19-22</sub>  | output impedance (pin 19)                      |                                                          | -    | 7    | 30   | Ω    |

| Z <sub>20-22</sub>  | output impedance (pin 20)                      |                                                          | -    | 7    | 30   | Ω    |

| Z <sub>21-22</sub>  | output impedance (pin 21)                      |                                                          | -    | 7    | 30   | Ω    |

| В                   | bandwidth                                      | -3 dB; mode 0 or 2                                       | -    | 25   | -    | MHz  |

|                     |                                                | +3 dB; mode 0 or 2                                       | -    | 12   | -    | MHz  |

|                     |                                                | ±3 dB; mode 1                                            | _    | 10   | -    | MHz  |

| t <sub>diff</sub>   | mutual time difference at output               | all inputs of one source connected together              | _    | _    | 25   | ns   |

| V <sub>o(p-p)</sub> | maximum output amplitude of YUV                | gain × 1                                                 | 2.1  | -    | -    | V    |

|                     | signals (peak-to-peak value)                   | gain × 2                                                 | 4.2  | -    | -    | V    |

| $\alpha_{ct}$       | crosstalk                                      | note 1; $f_i = 5$ MHz; between<br>inputs of same source  | _    | -    | -30  | dB   |

|                     |                                                | note 1; between same source                              | _    | -    | -40  | dB   |

| $\alpha_{off}$      | isolation (OFF state)                          | f <sub>i</sub> = 10 MHz                                  | 50   | -    | -    | dB   |

| SYMBOL                   | PARAMETER                                                                                                | CONDITIONS                                | MIN. | TYP. | MAX.           | UNIT |

|--------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------|------|------|----------------|------|

| G <sub>diff(p-p)</sub>   | differential gain at nominal output                                                                      | R-Y = 1.05 V (p-p)                        | -    | -    | 10             | %    |

| (F F)                    | signals (peak-to-peak value)                                                                             | B–Y = 1.33 V (p-p)                        | -    | _    | 10             | %    |

|                          |                                                                                                          | Y = 0.34 V (p-p)                          | -    | _    | 10             | %    |

| S/N                      | signal-to-noise ratio                                                                                    | nominal input; B = 5 MHz;<br>note 2       | 50   | -    | -              | dB   |

| SVRR                     | supply voltage ripple rejection                                                                          | note 3                                    | 30   | -    | -              | dB   |

| Vo                       | DC output levels during clamping                                                                         |                                           | -    | 5.3  | -              | V    |

| Synchroniz               | zation channels                                                                                          |                                           |      |      |                |      |

| G <sub>diff</sub>        | gain difference (programmed value)                                                                       |                                           | _    | _    | 10             | %    |

| В                        | bandwidth                                                                                                | –3 dB                                     | _    | 50   | _              | MHz  |

|                          |                                                                                                          | +3 dB; gain × 1                           | _    | 20   | _              | MHz  |

|                          |                                                                                                          | $\pm 3 \text{ dB}; \text{ gain} \times 2$ | _    | 13   | _              | MHz  |

| V <sub>i(p-p)</sub>      | input amplitude of sync signal for<br>correct operation of clamp pulse<br>generator (peak-to-peak value) |                                           | 0.2  | -    | 2.5            | V    |

| Z <sub>23-22</sub>       | output impedance (pin 23)                                                                                |                                           | -    | 20   | 30             | Ω    |

| V <sub>o(p-p)</sub>      | maximum undistorted output<br>amplitude (pin 23)<br>(peak-to-peak value)                                 |                                           | 2.5  | _    | _              | V    |

| Vo                       | DC output level on top of sync pulse                                                                     |                                           | 1.5  | 1.9  | 2.4            | V    |

| I <sup>2</sup> C-bus inp | buts for SDA, SCL                                                                                        | •                                         |      |      |                |      |

| V <sub>IH</sub>          | HIGH level input voltage                                                                                 |                                           | 3    | _    | V <sub>P</sub> | V    |

| V <sub>IL</sub>          | LOW level input voltage                                                                                  |                                           | -0.3 | _    | 1.5            | V    |

| I <sub>IH</sub>          | HIGH level input current                                                                                 |                                           | _    | _    | 10             | μA   |

| IIL                      | LOW level input current                                                                                  |                                           | -    | -    | 10             | μA   |

| I <sup>2</sup> C-bus ou  | tput for SDA (open collector)                                                                            |                                           |      |      | •              | -    |

| V <sub>OL</sub>          | LOW level output voltage                                                                                 | I <sub>OL</sub> = 3 mA                    | -    | -    | 0.4            | V    |

| Address s                | election inputs for S0, S1, S2                                                                           | •                                         | ŀ    | 1    | •              | -    |

| VIH                      | HIGH level input voltage                                                                                 |                                           | 3    | _    | VP             | V    |

| V <sub>IL</sub>          | LOW level input voltage                                                                                  |                                           | -0.3 | _    | 0.4            | V    |

| I <sub>IH</sub>          | HIGH level input current                                                                                 |                                           | _    | 0    | 10             | μA   |

| IIL                      | LOW level input current                                                                                  |                                           | -50  | -10  | 0              | μA   |

| Fast switcl              | hing input                                                                                               |                                           |      |      | •              | -    |

| VIH                      | HIGH level input voltage                                                                                 |                                           | 1    | _    | 3              | V    |

| V <sub>IL</sub>          | LOW level input voltage                                                                                  |                                           | -0.3 | _    | 0.4            | V    |

| I <sub>IH</sub>          | HIGH level input current                                                                                 |                                           | _    | 0    | 500            | μA   |

| IIL                      | LOW level input current                                                                                  |                                           | -100 | _    | _              | μA   |

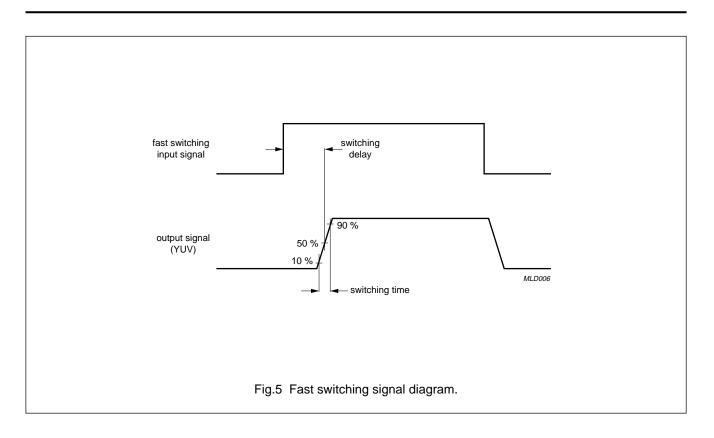

| t <sub>sw</sub>          | switching time                                                                                           | see Fig.5                                 | -    | 10   | _              | ns   |

| t <sub>d</sub>           | switching delay                                                                                          | see Fig.5                                 | _    | 20   | _              | ns   |

### TDA8443A

| SYMBOL          | PARAMETER                | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|-----------------|--------------------------|------------|------|------|------|------|

| Select inpu     | ıt                       |            |      | •    |      | •    |

| V <sub>IH</sub> | HIGH level input voltage |            | 3    | _    | VP   | V    |

| V <sub>IL</sub> | LOW level input voltage  |            | -0.3 | _    | 0.4  | V    |

| I <sub>IH</sub> | HIGH level input current |            | -    | 0    | 10   | μA   |

| IIL             | LOW level input current  |            | -50  | -10  | 0    | μA   |

| ON input        |                          |            | •    |      | •    | -    |

| V <sub>IH</sub> | HIGH level input voltage |            | 3    | -    | VP   | V    |

| V <sub>IL</sub> | LOW level input voltage  |            | -0.3 | _    | 1.5  | V    |

| I <sub>IH</sub> | HIGH level input current |            | _    | _    | 10   | μA   |

| IIL             | LOW level input current  |            | _    | -    | 10   | μA   |

#### Notes

1. Crosstalk is defined as the unwanted data transfer from an output, driven at nominal level, to other inputs and outputs on the IC and is expressed as a ratio in dBs.

2. Signal-to-noise ratio =

$$20\log \frac{V_{o(p-p)}}{V_{no(rms)}}$$

(B = 5 MHz)

3. Supply voltage ripple rejection =  $20\log \frac{V_{RR(supply)}}{V_{RR(at the output)}}$

### TDA8443A

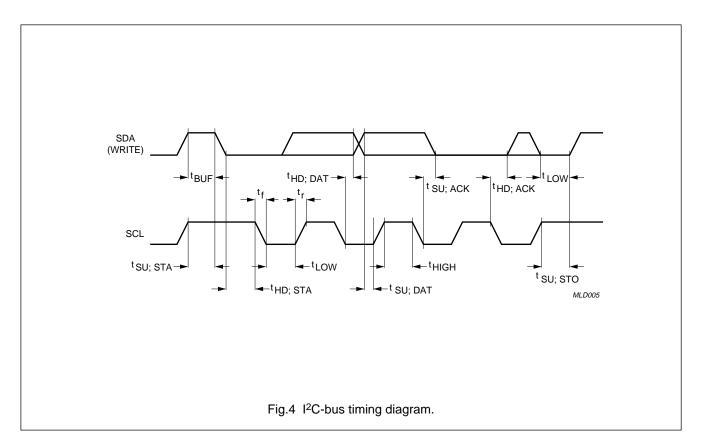

#### TIMING CHARACTERISTICS

$I^2C$ -bus load conditions: 4 k $\Omega$  pull-up resistor to +5 V; 200 pF capacitor to GND; all values are referenced to V<sub>IH</sub> = 3 V and V<sub>IL</sub> = 1.5 V; see Fig.4.

| SYMBOL              | PARAMETER                          | CONDITIONS | MIN. | TYP. | MAX. |

|---------------------|------------------------------------|------------|------|------|------|

| t <sub>BUF</sub>    | time bus must be free before start |            | 4.7  | -    | μs   |

| t <sub>SU;STA</sub> | set-up time for start condition    |            | 4.7  | -    | μs   |

| t <sub>HD;STA</sub> | hold time for start condition      |            | 4.0  | -    | μs   |

| t <sub>LOW</sub>    | SCL and SDA LOW time               |            | 4.7  | -    | μs   |

| t <sub>HIGH</sub>   | SCL HIGH time                      |            | 4.0  | -    | μs   |

| tr                  | SCL and SDA rise time              |            | -    | 1.0  | μs   |

| t <sub>f</sub>      | SCL and SDA fall time              |            | -    | 0.3  | μs   |

| t <sub>SU;DAT</sub> | data set-up time (write)           |            | 250  | -    | ns   |

| t <sub>HD;DAT</sub> | data hold time (write)             | note 1     | 1.0  | -    | μs   |

| t <sub>SU;ACK</sub> | acknowledge set-up time            |            | -    | 2    | μs   |

| t <sub>HD;ACK</sub> | acknowledge hold time              |            | 0    | -    | μs   |

| t <sub>SU;STO</sub> | set-up time for stop condition     |            | 4.7  | -    | μs   |

#### Note

Timing t<sub>HD;DAT</sub> deviates from the I<sup>2</sup>C-bus specification. After reset has been activated, a delay of 50 μs must occur before transmission may be resumed.

### TDA8443A

### **APPLICATION INFORMATION**

| Table 10 | Channel | input/output | information |

|----------|---------|--------------|-------------|

|----------|---------|--------------|-------------|

| INPUT 1     | INPUT 2     | OUTPUT      | MODE | D5 | D4 | D3 |

|-------------|-------------|-------------|------|----|----|----|

| Y = 0.34 V  |             | Y = 0.34 V  |      |    |    |    |

| U = -1.33 V |             | U = -1.33 V | 2    |    | 1  | 1  |

| V = -1.05 V | _           | V = -1.05 V | 2    | 1  |    | 1  |

| S = 0.3 V   |             | S = 0.6 V   |      |    |    |    |

|             | R = 0.75 V  | Y = 0.34 V  |      |    |    |    |

|             | G = 0.75 V  | U = -1.33 V | 1    | 1  | 1  | 1  |

| _           | B = 0.75 V  | V = -1.05 V | 1    | 1  | 1  | 1  |

|             | S = 0.3 V   | S = 0.6 V   |      |    |    |    |

| Y = 0.34 V  |             | Y = 0.68 V  |      |    |    |    |

| U = -1.33 V |             | U = -2.66 V | 2    | 1  | 0  | 0  |

| V = -1.05 V | _           | V = -2.10 V | 2    | 1  | 0  | 0  |

| S = 0.3 V   |             | S = 0.6 V   |      |    |    |    |

|             | R = 0.75 V  | Y = 0.68 V  |      |    |    |    |

|             | G = 0.75 V  | U = -2.66 V | 1    | 1  | 0  | 0  |

| _           | B = 0.75 V  | V = -2.10 V | 1    |    |    | 0  |

|             | S = 0.3 V   | S = 0.6 V   |      |    |    |    |

| Y = 0.34 V  |             | Y = 0.34 V  |      |    |    |    |

| U = -1.33 V |             | U = -1.33 V |      | 1  | 0  | 1  |

| V = -1.05 V | _           | V = -1.05 V | 2    | 1  | 0  | 1  |

| S = 0.3 V   |             | S = 0.6 V   |      |    |    |    |

|             | Y = 0.34 V  | Y = 0.34 V  |      |    |    |    |

|             | U = -1.33 V | U = -1.33 V |      |    | 0  | 4  |

| _           | V = -1.05 V | V = -1.05 V | 0    | 1  | 0  | 1  |

|             | S = 0.3 V   | S = 0.6 V   |      |    |    |    |

| Y = 0.34 V  |             | Y = 0.68 V  |      |    |    |    |

| U = -1.33 V |             | U = -2.66 V |      |    |    | 0  |

| V = -1.05 V | _           | V = -2.10 V | 2    | 1  | 1  | 0  |

| S = 0.3 V   |             | S = 0.6 V   |      |    |    |    |

|             | Y = 0.34 V  | Y = 0.68 V  |      |    |    |    |

|             | U = -1.33 V | U = -2.66 V |      |    |    |    |

| _           | V = -1.05 V | V = -2.10 V | 0    | 1  | 1  | 0  |

|             | S = 0.3 V   | S = 0.6 V   |      |    |    |    |

#### Input clamps

The R, G, B respectively (R–Y), Y and (B–Y) video signals are AC-coupled to the IC where they are clamped on the black level. The timing information for this clamping action is derived from the associated synchronization signal SYNC, which could also consist of the composite video information signal CVBS. The syncsignal is AC-coupled to the IC where it is clamped on top-sync level, information obtained from this action is used to generate the clamp pulses.

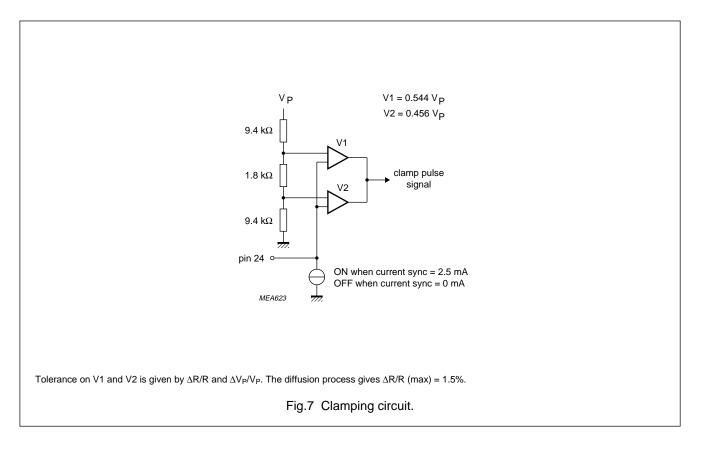

The clamp pulses can be generated in two ways:

1. Using the sync information (internal clamping)

The sync information is clamped on top-sync and the information obtained from this action is used to switch an internal current source at pin 24.

Pin 24 should be connected to V<sub>P</sub> via a 4.7 k $\Omega$  resistor, and a 1 nF capacitor to ground. During video scan the voltage at pin 24 will be HIGH (equals positive supply voltage). During the synchronization pulses the voltage at pin 24 will drop to zero because of the current sink (2.5 mA). When the synchronization pulse is over, the current source is switched off and the voltage at pin 24 will rise to its higher level. Because of the time constant at pin 24, the restoration will take some microseconds. The voltage at pin 24 is also sensed internally and at the time it is between  $0.456V_P$  and  $0.544V_P$ , a time pulse is generated and used for the clamping action.

2. Using a sandcastle pulse (external clamping)

If an associated sandcastle pulse is available, it can also be used as a clamping pulse. In this event the sandcastle pulse should be connected to pin 24, the top of the clamping pulse should be between 0.544V<sub>P</sub> and 0.456V<sub>P</sub>. The timing of the internal clamping pulse will be equal to the timing of the higher part of the sandcastle pulse. If the sync signal is also connected, the current sink will also become active during the synchronization pulses. This means that the sandcastle pulse should be connected to pin 24 via a 1 k $\Omega$  dropping resistor. In this event only the sandcastle pulse, but the sandcastle pulse at pin 24 will be influenced during sync pulses, but the sandcastle pulse at the sandcastle pulse should be connected.

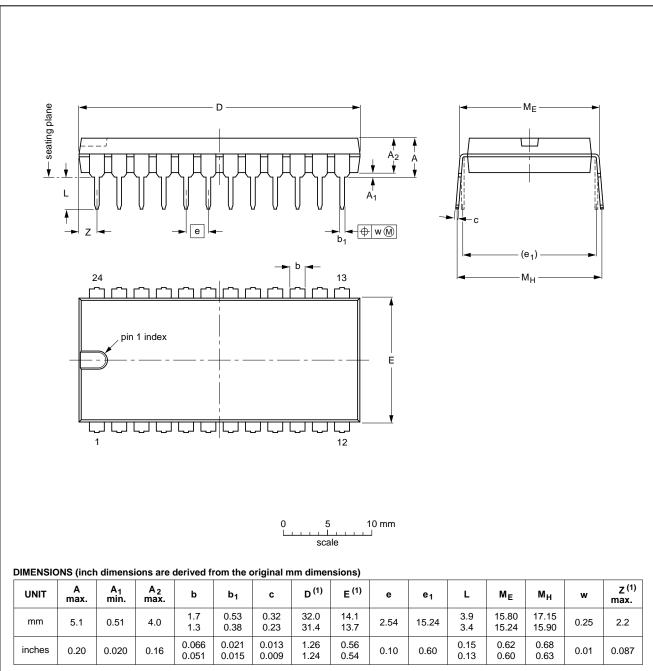

#### PACKAGE OUTLINE

### DIP24: plastic dual in-line package; 24 leads (600 mil)

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE<br>VERSION | REFERENCES |          |      |  | EUROPEAN   | ISSUE DATE                      |

|--------------------|------------|----------|------|--|------------|---------------------------------|

|                    | IEC        | JEDEC    | EIAJ |  | PROJECTION | ISSUE DATE                      |

| SOT101-1           | 051G02     | MO-015AD |      |  |            | <del>92-11-17</del><br>95-01-23 |

# TDA8443A

SOT101-1

### TDA8443A

#### SOLDERING

#### Plastic dual in-line packages

BY DIP OR WAVE

The maximum permissible temperature of the solder is 260 °C; this temperature must not be in contact with the joint for more than 5 s. The total contact time of successive solder waves must not exceed 5 s.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified storage maximum. If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit. REPAIRING SOLDERED JOINTS

Apply a low voltage soldering iron below the seating plane (or not more than 2 mm above it). If its temperature is below 300  $^{\circ}$ C, it must not be in contact for more than 10 s; if between 300 and 400  $^{\circ}$ C, for not more than 5 s.

#### DEFINITIONS

| Data sheet status         |                                                                                       |

|---------------------------|---------------------------------------------------------------------------------------|

| Objective specification   | This data sheet contains target or goal specifications for product development.       |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later. |

| Product specification     | This data sheet contains final product specifications.                                |

#### Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### Application information

Where application information is given, it is advisory and does not form part of the specification.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.