INTEGRATED CIRCUITS

Preliminary specification File under Integrated Circuits, IC02 September 1991

### FEATURES

- Gain controlled vision IF amplifier

- Synchronous demodulator for negative and positive demodulation

- AGC detector operating on peak sync amplitude for negative demodulation and on vision peak white level for positive demodulation

- Tuner AGC

- AFC circuit with on/off-switch

- Video preamplifier

- Video switch to select either the internal video signal or an external video signal

- Horizontal oscillator and synchronization circuit with two control loops

- Vertical synchronization (divider system), ramp generator and driver with automatic amplitude adjustment for 50 and 60 Hz

- Transmitter identification (mute)

- Sandcastle pulse generation

- · Auto VCR switch

- 50/60 Hz identification

#### **GENERAL DESCRIPTION**

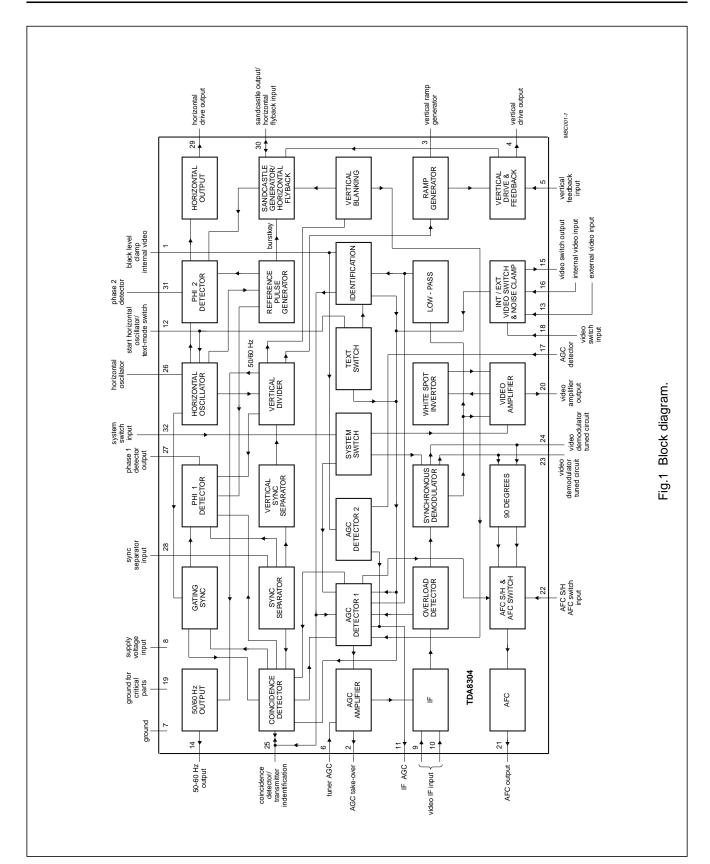

The TDA8304 possesses the capability to demodulate IF signals having either positive or negative-going video information. It is housed within a 32-pin encapsulation. The device includes a three-stage video IF amplifier, AFC and AGC circuitry, integral three-level sandcastle pulse generator, fully synchronized horizontal and vertical time bases with drive circuits, a video switch and a transmitter identification/mute circuit. A functional colour TV receiver can thus be realised with the addition of a tuner, audio demodulator and amplifier, chrominance decoder and respective line and field deflection circuitry.

### FUNCTIONAL DESCRIPTION

# Video IF amplifier, demodulator and video amplifier

Each of the three AC-coupled IF stages permits the omission of DC feedback and possesses a control range in excess of 20 dB.

The IF amplifier is followed by a passive synchronous demodulator providing a regenerated carrier signal. This is limited by a logarithmic limiter circuit prior to its application to the demodulator. Improved picture synchronization is provided by a wider bandwidth together with improved video amplifier linearity. The video amplifier contains also a white spot inverter and a noise clamp which limits interference pulses to a point below the peak sync level.

#### AFC-circuit

The reference signal for the AFC quadrature demodulator can also be acquired from the tuned circuit of the IF synchronous demodulator because an accurate 90° phase shift is realised internally. In this way only one tuned circuit needs to be applied and only one adjustment has to be carried out. The AFC output is affected by the asymmetrical frequency spectrum of the signal fed to the quadrature demodulator, which is determined by the SAW filter characteristic. To overcome this video frequency dependency of the AFC output, the demodulator output is followed by a sample-and-hold circuit.

For the reception of negative-going signals, the output is sampled only during peak sync (where a non-modulated carrier is present). When receiving signals with positive modulation the AFC is continuously active but extensively filtered. Substantial noise will be present on the quadrature demodulator input signal during reception of very weak signals. This noise has an asymmetrical frequency spectrum (with respect to the IF carrier) causing an offset in the AFC output voltage. This effect can be minimized by applying a notch in the demodulator tuned circuit. The sample-and-hold circuit is followed by an amplifier with high output impedance. The steepness of the AFC control voltage can be lowered by applying load resistors from the output to the supply and to ground. The AFC output is switched off when the AFC sample pin (22) is connected to ground.

#### **ORDERING INFORMATION**

| EXTENDED TYPE | PACKAGE |                                 |         |                       |  |  |  |

|---------------|---------|---------------------------------|---------|-----------------------|--|--|--|

| NUMBER        | PINS    | PINS PIN POSITION MATERIAL CODE |         |                       |  |  |  |

| TDA8304       | 32      | DIL                             | plastic | SOT201 <sup>(1)</sup> |  |  |  |

#### Note

1. SOT201-1; 1996 December 2.

### TDA8304

### QUICK REFERENCE DATA

| SYMBOL                 | PARAMETER                                             | CONDITIONS                  | MIN. | TYP. | MAX. | UNIT |

|------------------------|-------------------------------------------------------|-----------------------------|------|------|------|------|

| Supply                 | -                                                     |                             |      |      |      | 1    |

| V <sub>P</sub>         | supply voltage (pin 8)                                |                             | 10   | 12   | 13.2 | V    |

| I <sub>P</sub>         | supply current (pin 8)                                |                             | 90   | 115  | 140  | mA   |

| I <sub>start</sub>     | start current (pin 12)                                | note 1                      | _    | 6.5  | 9    | mA   |

| Video                  | •                                                     |                             | •    |      |      |      |

| V <sub>9-10(rms)</sub> | IF sensitivity (RMS value)                            | note 2                      | 25   | 40   | 65   | μV   |

| G <sub>9-10</sub>      | IF gain control range                                 |                             | _    | 74   | -    | dB   |

| S/N                    | signal-to-noise ratio                                 | input signal = 10 mV        | 52   | 58   | -    | dB   |

| V <sub>21</sub>        | AFC output voltage swing                              |                             | 10.5 | _    | 11.5 | V    |

| Video switch           | ·                                                     |                             | •    |      |      |      |

| V <sub>16(p-p)</sub>   | internal video input (peak-to-peak value)             | V <sub>O</sub> = 2.5 V(p-p) | -    | 2    | -    | V    |

| V <sub>13(p-p)</sub>   | external video input (peak-to-peak value)             | V <sub>O</sub> = 2.5 V(p-p) | _    | 1    | -    | V    |

| V <sub>15(p-p)</sub>   | video output signal (peak-to-peak value)              |                             | 2.3  | 2.5  | 2.7  | V    |

| Sync                   |                                                       |                             | ·    |      |      |      |

| V <sub>28</sub>        | required sync pulse amplitude                         | note 3                      | 200  | 750  | _    | mV   |

| I <sub>30</sub>        | required input current during flyback pulse           |                             | 0.1  | _    | 2    | mA   |

| V <sub>30</sub>        | sandcastle output during                              |                             |      |      |      |      |

|                        | burstkey                                              |                             | 8    | -    | -    | V    |

|                        | horizontal blanking                                   |                             | 4    | 4.4  | 5    | V    |

|                        | vertical blanking                                     |                             | 2.1  | 2.5  | 2.9  | V    |

| V <sub>25</sub>        | video transmitter identification output               |                             |      |      |      |      |

|                        | no signal condition                                   |                             | -    | 0.3  | -    | V    |

|                        | signal condition                                      |                             | -    | 9.8  | -    | V    |

| V <sub>5</sub>         | vertical feedback for DC voltage                      |                             | 2.9  | 3.3  | 3.7  | V    |

| V <sub>5(p-p)</sub>    | vertical feedback for AC voltage (peak-to-peak value) |                             | -    | 1    | -    | V    |

### Notes to the quick reference data

Supplying a current of 9 mA to pin 12 starts the horizontal oscillator. This current can be obtained via a bleed circuit from the mains rectifier whilst the main supply for the device (V<sub>cc</sub>) is obtained from the horizontal output stage. The load current of the driver must be added to the value given.

2. On set AGC.

The minimum value is obtained by connecting a 1.8 kΩ resistor between pins 15 and 28. The slicing level can be varied by changing the value of this resistor (higher resistor value results in larger value of the minimum sync pulse amplitude). The slicing level is independent of the video information.

### September 1991

## Small signal combination IC for colour TV

#### PINNING

| PIN | DESCRIPTION                                     |

|-----|-------------------------------------------------|

| 1   | black level clamp internal video                |

| 2   | tuner take-over                                 |

| 3   | vertical ramp generator                         |

| 4   | vertical drive                                  |

| 5   | vertical feedback                               |

| 6   | tuner AGC                                       |

| 7   | ground                                          |

| 8   | supply voltage input                            |

| 9   | video IF input                                  |

| 10  | video IF input                                  |

| 11  | IF AGC                                          |

| 12  | start horizontal oscillator/text-mode switch    |

| 13  | external video input                            |

| 14  | 50 - 60 Hz output                               |

| 15  | video switch output                             |

| 16  | internal video input                            |

| 17  | AGC detector                                    |

| 18  | video switch input                              |

| 19  | ground for some critical parts                  |

| 20  | video amplifier output                          |

| 21  | AFC output                                      |

| 22  | AFC S/H, AFC switch input                       |

| 23  | video demodulator tuned circuit                 |

| 24  | video demodulator tuned circuit                 |

| 25  | coincidence detector/transmitter identification |

| 26  | horizontal oscillator                           |

| 27  | phase 1 detector                                |

| 28  | sync separator input                            |

| 29  | horizontal drive output                         |

| 30  | sandcastle output/horizontal flyback input      |

| 31  | phase 2 detector                                |

| 32  | system switch input                             |

### AGC circuit

For signals employing negative modulation the AGC detector operates on peak sync level and on peak white level with those having positive modulation. Selection is facilitated by the system switch (pin 32), see Table 1. The charge current at positive modulation (see Table 2) is only present during the vertical sync or when the level at pin 1 drops 200 mV below the level of pin 17 as a result of input signal variations. To obtain rapid AGC action when executing a search tuning operation when the circuit is set for peak white AGC, the charge current is increased to 55  $\mu$ A until the detection of a transmitted signal. With an AGC capacitor of 6.8  $\mu$ F the video tilt will be < 2% for positive and for negative modulated signals.

### VCR switch

The TDA8304 has an auto VCR-switch facility. Due to the inherent instability of signals from a VCR, the horizontal time constant should be shorter to prevent loss of horizontal synchronization in the early part of the scan. Provision is therefore incorporated (in the internal video mode) to automatically switch the short time constant such that a strong signal instigates the 'VCR' mode and a weak signal triggers the 'TV' mode. The phase detector is gated during the 'TV mode' and operates with a long time constant. The phase detector is not gated in the 'VCR' mode and operates with a short time constant. The TDA8304 is active in the 'VCR' mode only at reception of an external video signal.

### Video-switch

Selection between internal video (pin 16) and external video (pin 13) is made by applying a switching potential to pin 18 (see Table 3). Video output (pin 20) from the device is filtered to remove the audio carrier and DC-coupled to pin 16. The TDA8304 provides the opportunity for a direct video connection (e.g. via a peritel connector) to be made to the device at pin 13. The AGC detector is not gated during the external video mode, the first phase detector is also not gated and operates with a short time constant. The gain of the IF amplifier (in the external video mode) is reduced to prevent crosstalk of the video amplifier to the horizontal oscillator during the no-signal condition.

### TDA8304

#### Horizontal synchronization

The horizontal synchronization circuit of the TDA8304 provides the drive pulse for a horizontal deflection stage.

- The phase of the control loop will be adapted automatically to the level of the input signal in order to achieve an optimum performance

- The control gradient of the control loop will be low at reception of weak signals to reduce the noise bandwidth.

- The phase detector control current is increased during strong or no-signal reception to obtain a short catching time and a good performance during VCR playback.

#### Vertical synchronization

The TDA8304 embodies a synchronized divider system for generating the vertical sawtooth at pin 3 having several advantages and features such as:

- The vertical frequency is alignment free. The divider automatically adapts to a vertical frequency of 50 Hz or 60 Hz including automatic amplitude correction and its operating modes offer maximum interference/disturbance protection.

- A discriminator-window checks the accuracy of the vertical trigger pulse. Internally clockpulses are generated by doubling the line frequency. The divider operates in the 60 Hz mode when the trigger pulse appears before count 576, otherwise the 50 Hz mode will be active.

- The divider system operates with a number of different reset windows. The windows are activated via an up/down counter. The counter increases its counter-value by 1 for each time the separated vertical sync pulse appears within the selected window, otherwise the counter value is lowered by 1.

### Modes of operation

Large search window (divider ratio between 488 and 722). This mode is valid for the following conditions:

- · Divider is looking for a new transmitter

- Divider ratio found does not comply with the narrow window specification limits

- Up/down counter value of the divider system, operating in the narrow window mode, drops below count 10

Narrow window mode: divider ratio between 522 - 528 (60 Hz) or 622 - 628 (50 Hz)

- The divider system switches over to narrow window mode when the up/down counter has reached his maximum value of 15 vertical sync pulses.

- When the divider operates in the narrow window mode and a vertical sync pulse is missing in the window, the divider is reset at the end of that window and the counter value is lowered by 1.

- At a counter value below 10 the divider system switches over to the large window mode.

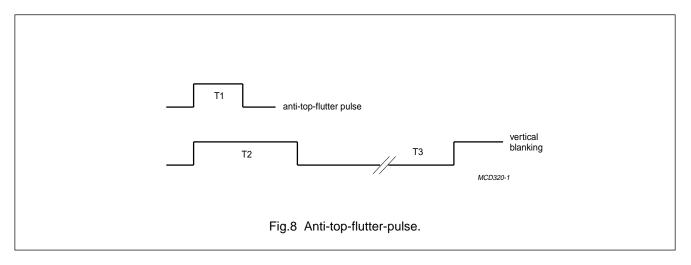

- The divider system generate also the so-called anti-top-flutter pulse which inhibits the phase 1 detector during the vertical sync pulse. The width of this pulse depends on the divider mode. For the large window mode the start is generated at the reset of the divider. In the narrow window mode the anti-top-flutter pulse starts at the beginning of the first equalizing pulse. The anti-top-flutter pulse ends at count 10 for 50 Hz and at count 12 for 60 Hz.

- The divider is switched to count 625 when out of sync is detected by the coincidence detector. This results in a stable amplitude when no input signal is available.

- The divider is switched to the large window mode when enlarged vertical sync pulses are detected.

### TDA8304

### Table 1 AGC circuit operation

| STATE POSITIVE MODULATION |           | NEGATIVE MODULATION |  |  |  |

|---------------------------|-----------|---------------------|--|--|--|

| input pin 32              | HIGH/open | LOW                 |  |  |  |

#### Table 2 AGC detector currents

| STATE     | POSITIVE MODULATION |               | NEGATIVE MODULATION |               |  |

|-----------|---------------------|---------------|---------------------|---------------|--|

| action    | current             | condition     | current             | condition     |  |

| charge    | 10 μΑ               | V-sync signal | 55 μΑ               | _             |  |

| charge    | 55 μΑ               | pin 25 = LOW  | -                   | _             |  |

| discharge | 3 mA                | VITS signal   | 1.5 mA              | H-sync signal |  |

#### Table 3 Video switch operation

| STATE        | INTERNAL VIDEO | EXTERNAL VIDEO |

|--------------|----------------|----------------|

| input pin 18 | LOW            | HIGH           |

### QUALITY SPECIFICATION

Quality level according to UZW-BQ/FQ-601.

| SYMBOL | PARAMETER                                 |      | RANGE<br>B | UNIT |

|--------|-------------------------------------------|------|------------|------|

| ESD    | protection circuit specification (note 1) | 2000 | 500        | V    |

|        |                                           | 100  | 200        | pF   |

|        |                                           | 1500 | 0          | Ω    |

### Note to the Quality specification

1. All pins of the IC are protected against ESD by means of the internal clamping diodes. Range A represents the human body model and range B represents the charge device model.

### LIMITING VALUES

In accordance with the Absolute Maximum System (IEC 134)

| SYMBOL           | PARAMETER                           |     | MAX. | UNIT |

|------------------|-------------------------------------|-----|------|------|

| VP               | supply voltage (pin 8)              | _   | 13.2 | V    |

| P <sub>tot</sub> | total power dissipation             | _   | 2.3  | W    |

| T <sub>stg</sub> | storage temperature range           | -55 | +150 | °C   |

| T <sub>amb</sub> | operating ambient temperature range | -25 | +65  | °C   |

### THERMAL RESISTANCE

| SYMBOL              | PARAMETER                            | TYP. | MAX. | UNIT |

|---------------------|--------------------------------------|------|------|------|

| R <sub>th j-a</sub> | from junction to ambient in free air | 30   | 35   | K/W  |

### TDA8304

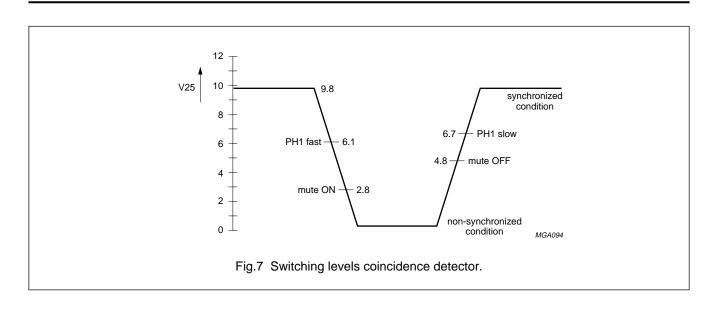

# The transmitter identification/coincidence detector

Pin 25 of the TDA8304 serves as the transmitter identification and/or coincidence detector (see Table 4). Pin 25 is HIGH (= 9.8 V) when a transmitter is present and LOW (= 0.3 V) when no transmitter signal is detected. When the video switch is in the internal mode, the signal at the sync separator input (pin 28) is the demodulated IF signal, pin 25 will act as a coincidence detector. Pin 25 is HIGH when the horizontal oscillator loop is synchronized with the video signal and LOW in case of no synchronization. In the external video mode and in the text mode, pin 25 will be active as transmitter identification. The system relies upon the detection of sync pulses on the incoming IF signal. Pin 25 is charged with a current of 125  $\mu$ A by the separated

horizontal sync pulse and discharged continuously with a current of 4  $\mu$ A. The high impedance of pin 25 should be taken into account in the application concept.

### The 50/60 Hz identification

The 50/60 Hz information (see Table 5) derived from the divider system is available at the open collector output pin 14.

| STATE                         | INTERNAL VIDEO |        |                 |          | EXTERNAL VIDEO |            |            |

|-------------------------------|----------------|--------|-----------------|----------|----------------|------------|------------|

| input pin 18                  | LOW            |        |                 | HIGH     |                |            |            |

| input pin 12                  | TV mode =      | = HIGH | Text mode = LOW |          |                |            |            |

| Input signal<br>pins 9 and 10 | yes            | none   | yes             | none     | none           | yes        | none       |

| input pin 28                  | 50/60 Hz       | none   | 50/60 Hz        | VCS text | none           | don't care | don't care |

| output pin 25                 | 9.8 V          | 0.3 V  | 9.8 V           | 0.3 V    | 0.3 V          | 9.8 V      | 0.3 V      |

### Table 550/60 Hz identification

| INPUT/OUTPUT                  | STATUS     | STATUS     | STATUS     |

|-------------------------------|------------|------------|------------|

| Input signal<br>pins 9 and 10 | don't care | don't care | don't care |

| input pin 28                  | 50 Hz      | 60 Hz      | none       |

| output pin 14                 | 0.3 V      | 12 V       | 0.3 V      |

### TDA8304

### CHARACTERISTICS

$T_{amb}$  = 25 °C;V<sub>p</sub> = 12 V; carrier 38.9 MHz negative modulation, unless otherwise specified

| SYMBOL                 | PARAMETER                                                       | CONDITIONS              | MIN. | TYP. | MAX. | UNIT |

|------------------------|-----------------------------------------------------------------|-------------------------|------|------|------|------|

| Supply (pir            | 1 8)                                                            |                         |      | •    |      |      |

| V <sub>8</sub>         | supply voltage range                                            |                         | 10   | 12   | 13.2 | V    |

| l <sub>8</sub>         | supply current                                                  | no input                | 90   | 115  | 140  | mA   |

| I <sub>12</sub>        | start current (pin 12)                                          | note 1                  | _    | 6.5  | 9    | mA   |

| V <sub>12</sub>        | start protection level                                          | I <sub>12</sub> = 12 mA | -    | -    | 16.5 | V    |

| IF Amplifie            | r                                                               |                         |      | •    | •    |      |

| V <sub>9-10(rms)</sub> | input sensitivity (RMS value)                                   | note 2                  | 25   | 40   | 65   | μV   |

| R <sub>9-10</sub>      | differential input resistance                                   | note 3                  | -    | 1300 | -    | Ω    |

| C <sub>9-10</sub>      | differential input capacitance                                  | note 3                  | _    | 5    | _    | pF   |

| G <sub>9-10</sub>      | gain control range                                              |                         | _    | 74   | -    | dB   |

| $\Delta V_{20}$        | output signal expansion for 46 dB input signal variation        | note 4                  | -    | 1    | -    | dB   |

| V <sub>9-10</sub>      | maximum input signal                                            |                         | 100  | 170  | _    | mV   |

| V <sub>9-10(rms)</sub> | input sensitivity in external mode (RMS value)                  | note 2                  | 250  | 400  | 650  | μV   |

|                        | lifier (notes 5 and 6)                                          |                         |      |      |      |      |

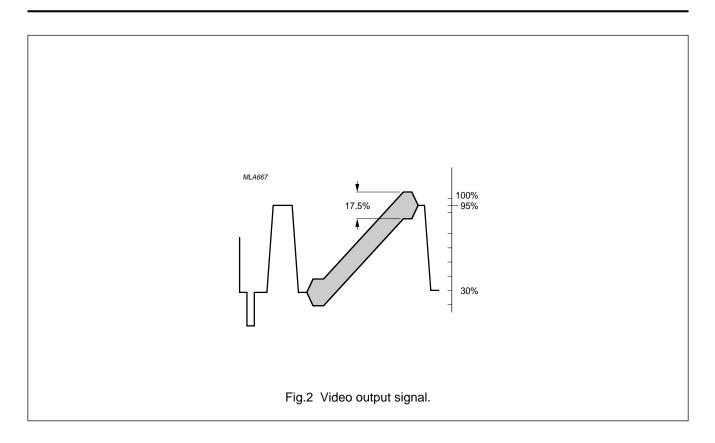

| V <sub>20</sub>        | negative modulation, zero signal level                          |                         | 4.7  | 4.9  | 5.1  | V    |

| V <sub>20</sub>        | positive modulation, zero signal level                          |                         | 2.5  | 2.7  | 2.9  | V    |

| V <sub>20</sub>        | peak sync (negative modulation)                                 | note 7                  | 2.5  | 2.75 | 3.0  | V    |

| V <sub>20</sub>        | white level (positive modulation)                               | note 7                  | 4.7  | 4.9  | 5.1  | V    |

| V <sub>20</sub>        | white spot threshold level                                      |                         | _    | 5.7  | _    | V    |

| V <sub>20</sub>        | white spot insertion level                                      |                         | _    | 4    | -    | V    |

| Z <sub>20</sub>        | video output impedance                                          |                         | -    | 25   | -    | Ω    |

| I <sub>20</sub>        | internal bias current of npn emitter follower output transistor |                         | 1.4  | 1.8  | -    | mA   |

| I <sub>source</sub>    | maximum source current (pin 20)                                 |                         | 10   | -    | -    | mA   |

| В                      | bandwidth of demodulated output signal                          |                         | 5    | 6    | _    | MHz  |

| G <sub>20</sub>        | differential gain                                               | note 8                  | -    | 2    | 5    | %    |

| φ                      | differential phase                                              | note 8                  | -    | 2    | 5    | deg  |

| NL                     | video non-linearity                                             | note 9                  | -    | 2    | 5    | %    |

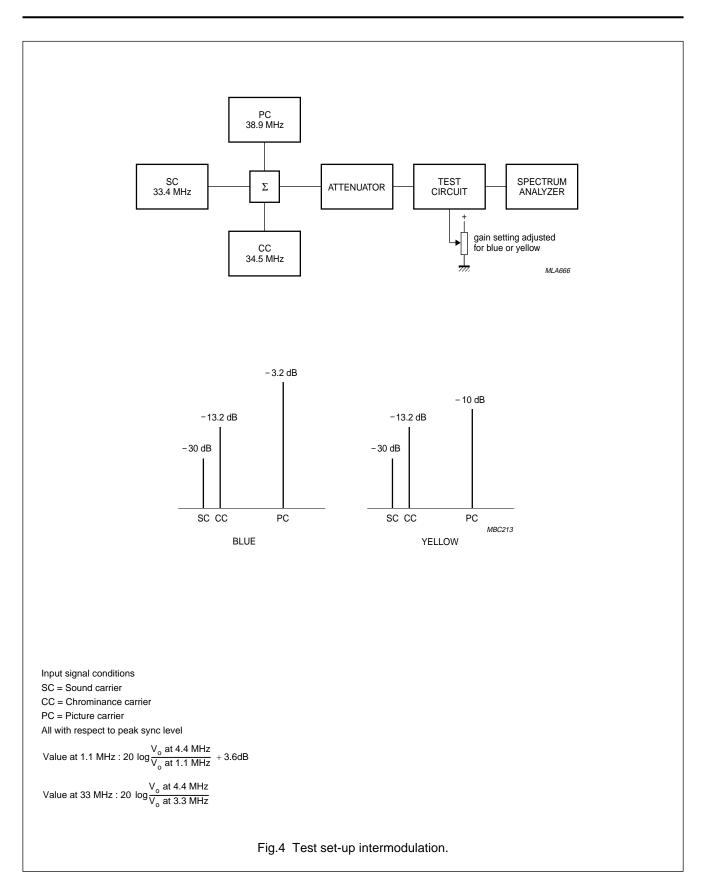

|                        | intermodulation                                                 | note 10                 |      |      |      |      |

|                        | 1.1 MHz; blue                                                   |                         | 50   | 60   | -    | dB   |

|                        | 1.1 MHz; yellow                                                 |                         | 50   | 60   | -    | dB   |

|                        | 3.3 MHz; blue                                                   |                         | 55   | 65   | _    | dB   |

|                        | 3.3 MHz; yellow                                                 |                         | 55   | 65   | -    | dB   |

| SYMBOL                 | PARAMETER                                              | CONDITIONS                                             | MIN. | TYP. | MAX. | UNIT |

|------------------------|--------------------------------------------------------|--------------------------------------------------------|------|------|------|------|

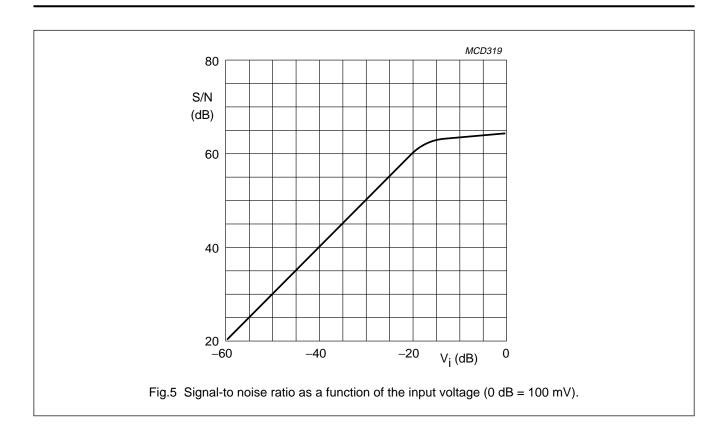

| S/N                    | signal-to-noise ratio                                  | 10 mV input<br>signal                                  | 52   | 58   | _    | dB   |

|                        |                                                        | end of gain<br>control range;<br>note 11;<br>see Fig.5 | 57   | 62   | -    | dB   |

| V <sub>20</sub>        | residual carrier signal                                |                                                        | _    | 2    | 10   | mV   |

| V <sub>20</sub>        | residual 2nd harmonic of carrier signal                |                                                        | _    | 2    | 10   | mV   |

| System sw              | /<br>/itch (note 12)                                   |                                                        |      |      |      |      |

| AGC ON PE              | AK SYNC LEVEL FOR NEGATIVE MODULATION SIGNALS          |                                                        |      |      |      |      |

| V <sub>32</sub>        | control voltage                                        |                                                        | 0    | -    | 0.8  | V    |

| I <sub>32</sub>        | input current                                          |                                                        | -100 | _    | -500 | μA   |

|                        | ITE LEVEL FOR POSITIVE MODULATION SIGNALS              | 1                                                      |      |      |      |      |

| V <sub>32</sub>        | control voltage                                        |                                                        | 2    | -    | 12   | V    |

| I <sub>32</sub>        | input current                                          |                                                        | 0    | -    | 1    | mA   |

| IF sync se             | parator                                                | 1                                                      |      |      |      | 1    |

| lı                     | input current                                          |                                                        | 0.4  | 0.6  | 0.8  | mA   |

| lo                     | output current (pin 1)                                 |                                                        | 22   | 27   | 32   | μA   |

| V <sub>1</sub>         | clamp level                                            |                                                        | _    | 3.3  | -    | V    |

| Tuner AGC              |                                                        |                                                        | -    |      | -    |      |

| V <sub>9-10(rms)</sub> | minimum starting point for tuner take-over (RMS value) |                                                        | -    | -    | 0.2  | mV   |

| V <sub>9-10(rms)</sub> | maximum starting point for tuner take-over (RMS value) |                                                        | 100  | 150  | -    | mV   |

| I <sub>6</sub>         | maximum tuner AGC output swing                         | V <sub>6</sub> = 3 V                                   | 4    | -    | _    | mA   |

| V <sub>6</sub>         | output saturation voltage                              | I <sub>6</sub> = 2 mA                                  | _    | _    | 300  | mV   |

| I <sub>6</sub>         | leakage current                                        |                                                        | _    | -    | 1    | μA   |

|                        | input signal variation complete tuner control          | $\Delta I_6 = 2 \text{ mA}$                            | 0.2  | 2    | 4    | dB   |

| V <sub>2</sub>         | minimum voltage tuner take-over                        |                                                        | -    | -    | 1    | V    |

| AGC detec              | tion level                                             |                                                        |      |      |      |      |

| I <sub>17</sub>        | charge current                                         |                                                        | -    | 200  | _    | μA   |

| I <sub>17</sub>        | discharge current                                      |                                                        | -    | 20   | _    | μA   |

| V <sub>17</sub>        | clamp level                                            |                                                        | _    | 2.9  | _    | V    |

| Video swit             | ching circuit (note 13)                                |                                                        |      |      |      |      |

| EXTERNAL F             | POSITIVE VIDEO INPUT                                   |                                                        |      |      |      |      |

| V <sub>13(p-p)</sub>   | input signal (peak-to-peak value)                      | V <sub>O</sub> = 2.5 V(p-p)                            | -    | 1    | -    | V    |

| I <sub>13</sub>        | input current                                          |                                                        | -    | 1.5  | 5    | μA   |

| V <sub>13</sub>        | peak sync clamping level                               | I <sub>13</sub> = 1 mA                                 | 1.65 | 1.85 | 2.05 | V    |

| SYMBOL               | PARAMETER                                                              | CONDITIONS                  | MIN. | TYP. | MAX. | UNIT   |

|----------------------|------------------------------------------------------------------------|-----------------------------|------|------|------|--------|

| INTERNAL VI          |                                                                        |                             | 1    | -1   | 1    | 1      |

| V <sub>16(p-p)</sub> | Internal video input signal (peak-to-peak value)                       | V <sub>O</sub> = 2.5 V(p-p) | _    | 2    | _    | V      |

| I <sub>16</sub>      | input current                                                          |                             | _    | 1.5  | 5    | μA     |

| V <sub>16</sub>      | noise clamping level                                                   | I <sub>16</sub> = 1 mA      | 2.2  | 2.4  | 2.6  | V      |

| VIDEO OUTF           | PUT (POSITIVE VIDEO)                                                   | 1                           |      | -1   | 1    | 4      |

| V <sub>15(p-p)</sub> | video output signal (peak-to-peak value)                               |                             | 2.3  | 2.5  | 2.7  | V      |

| V <sub>15</sub>      | peak sync signal                                                       |                             | _    | 3    | _    | V      |

| I <sub>bias</sub>    | internal bias current (pin 15)                                         |                             | 1    | 1.5  | _    | mA     |

| lo                   | maximum output current (pin 15)                                        |                             | 5    | _    | -    | mA     |

| α                    | crosstalk external to internal                                         | notes 14 and 24             | _    | 55   | _    | dB     |

| α                    | crosstalk internal to external                                         | notes 14 and 24             | _    | 55   | _    | dB     |

| Video swit           | ch                                                                     |                             |      |      |      | •      |

| V <sub>18</sub>      | input voltage for internal video                                       |                             | _    | _    | 0.8  | V      |

| V <sub>18</sub>      | input voltage for external video                                       |                             | 2    | _    | VP   | V      |

| I <sub>18</sub>      | maximum current                                                        | V <sub>18</sub> = 0 V       | _    | 0.05 | 0.2  | mA     |

|                      |                                                                        | V <sub>18</sub> = 12 V      | -    | 0.25 | 1    | mA     |

| Text/TV sw           | /itch                                                                  |                             |      |      |      |        |

| V <sub>12</sub>      | input voltage for text mode                                            |                             | -    | _    | 0.8  | V      |

| V <sub>12</sub>      | input voltage for TV mode                                              |                             | 2    | _    | VP   | V      |

| I <sub>12</sub>      | maximum current                                                        | V <sub>12</sub> = 0 V       | -    | _    | 0.3  | mA     |

|                      |                                                                        | V <sub>12</sub> = 11.5 V    | -    | _    | 1.5  | mA     |

| AFC-circui           | it (note 15)                                                           |                             |      |      |      | ·      |

| I <sub>22</sub>      | AFC sample and hold switch-off current                                 |                             | 0.1  | _    | -    | mA     |

| lo                   | output current (pin 22)                                                | V <sub>22</sub> = 0 V       | 0.2  | 0.4  | 0.8  | mA     |

| ILI                  | leakage current (pin 22)                                               |                             | _    | _    | 1    | μA     |

| V <sub>21</sub>      | AFC output voltage swing                                               |                             | 10.5 | _    | 11.5 | V      |

| I <sub>21</sub>      | available output current                                               |                             | ±0.2 | _    | _    | mA     |

|                      | control slope                                                          |                             | _    | 100  | _    | mV/kHz |

| Vo                   | output voltage (pin 21)                                                | AFC off                     | 5.5  | 6    | 6.5  | V      |

| R <sub>O</sub>       | AFC output resistance                                                  |                             | _    | 40   | _    | kΩ     |

| V <sub>21(p-p)</sub> | output voltage swing                                                   | notes 16 and 24             | _    | 11   | _    | V      |

|                      | control slope                                                          | notes 16 and 24             | _    | 80   | -    | mV/kHz |

| V <sub>21</sub>      | output voltage shift with respect to $V_I = 10 \text{ mV}(\text{RMS})$ | notes 16 and 24             | -    | -2   | -    | V      |

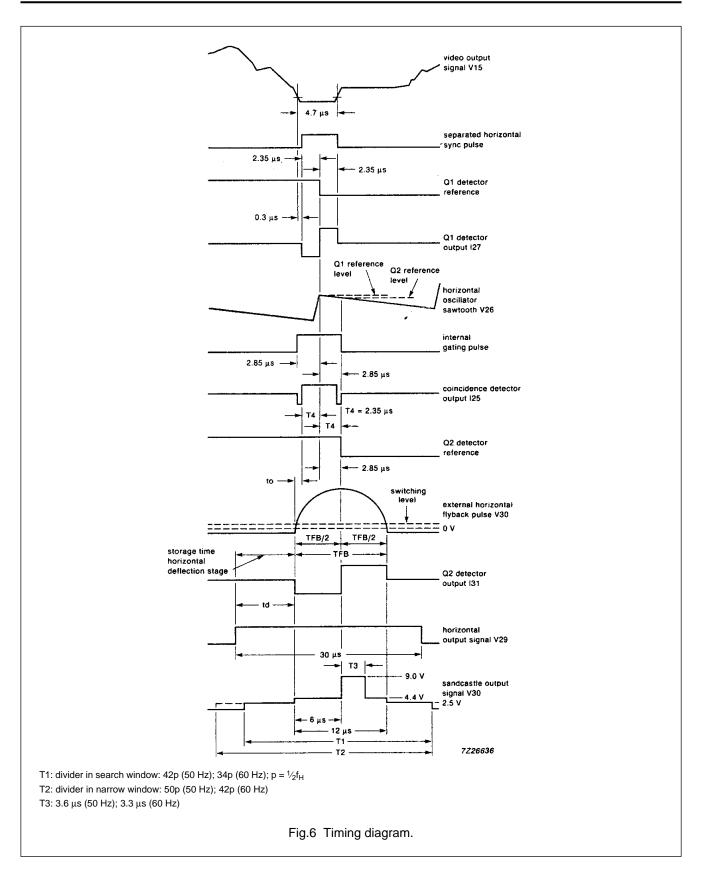

| Sync sepa            | rator (see Fig.6)                                                      |                             |      |      |      | •      |

| V <sub>28</sub>      | required sync pulse amplitude                                          | note 17                     | 200  | 750  | _    | mV     |

| I <sub>28</sub>      | input current                                                          | $V_{28} > 5 V$              | -    | 8    | -    | μA     |

|                      |                                                                        | V <sub>28</sub> = 0 V       | _    | -10  | _    | mA     |

| SYMBOL                              | PARAMETER                                                   | CONDITIONS                 | MIN.      | TYP.  | MAX.  | UNIT  |

|-------------------------------------|-------------------------------------------------------------|----------------------------|-----------|-------|-------|-------|

| First contr                         | ol loop                                                     | 1                          |           |       |       |       |

| Δf                                  | PLL holding range                                           |                            | _         | ±1500 | ±2000 | Hz    |

| Δf                                  | PLL catching range                                          |                            | ±600      | ±1500 | _     | Hz    |

|                                     | control sensitivity to oscillator                           | note 18                    | see Fig.7 |       | 1     |       |

| V <sub>9-10(rms)</sub>              | IF input signal for switching from fast to slow (RMS value) |                            | -         | 2.2   | -     | mV    |

| Second co                           | ntrol loop (positive edge)                                  | •                          |           | •     |       |       |

| $\frac{\delta t_{d}}{\delta t_{o}}$ | control sensitivity, see Fig.6                              | note 19                    | -         | 100   | -     |       |

| t <sub>d</sub>                      | control range                                               |                            | -         | 25    | -     | μs    |

| Phase adju                          | ustment (via second control loop)                           | •                          | -         |       |       |       |

|                                     | control sensitivity                                         |                            | -         | 25    | _     | μA/μs |

| α                                   | maximum allowed phase shift                                 |                            | -         | ±2    | -     | μs    |

| Horizontal                          | oscillator                                                  |                            | •         | •     | •     | •     |

|                                     | free running frequency                                      | R = 34.3 kΩ;<br>C = 2.7 nF | -         | 15625 | -     | Hz    |

| Δf                                  | spread with fixed external components                       |                            | _         | -     | 4     | %     |

| Δf                                  | frequency variations with supply voltage from 10 to 13.2 V  |                            | -         | -     | 2     | %     |

| $\Delta f_T$                        | frequency variation with temperature                        | note 24                    | _         | -1.6  | -     | Hz/°C |

| $\Delta f_{fr}$                     | maximum frequency deviation at start of horizontal output   |                            | -         | -     | 10    | %     |

| Δf                                  | frequency variation when only noise is received             | note 24                    | -         | -     | 500   | Hz    |

| Horizontal                          | output (open collector; pin 29)                             |                            |           | ·     |       |       |

| V <sub>29</sub>                     | output limiting voltage                                     |                            | _         | -     | 16.5  | V     |

| V <sub>OL</sub>                     | output voltage LOW                                          | I <sub>sink</sub> = 10 mA  | _         | 0.3   | 0.5   | V     |

| l <sub>sink</sub>                   | maximum sink current                                        |                            | 10        | _     | _     | mA    |

|                                     | duty factor of output signal                                |                            | _         | 46    | -     | %     |

| t <sub>r</sub>                      | rise time output pulse                                      |                            | _         | 260   | -     | ns    |

| t <sub>f</sub>                      | fall time output pulse                                      |                            | -         | 100   | -     | ns    |

| Flyback in                          | put and sandcastle output (note 20)                         |                            |           |       |       |       |

| I <sub>30</sub>                     | required input current during flyback pulse                 |                            | 0.1       | _     | 2     | mA    |

| V <sub>30</sub>                     | output voltage during                                       |                            |           |       |       |       |

|                                     | burstkey                                                    |                            | 8         | -     | -     | V     |

|                                     | horizontal blanking                                         |                            | 4         | 4.4   | 5     | V     |

|                                     | vertical blanking                                           |                            | 2.1       | 2.5   | 2.9   | V     |

| t <sub>W</sub>                      | pulse width of burstkey                                     |                            |           |       |       |       |

|                                     | at 60 Hz signals                                            |                            | 2.9       | 3.3   | 3.7   | μs    |

|                                     | at 50 Hz signals                                            |                            | 3.2       | 3.6   | 4     | μs    |

| SYMBOL              | PARAMETER                                                                            | CONDITIONS                          | MIN.    | TYP.     | MAX. | UNIT  |

|---------------------|--------------------------------------------------------------------------------------|-------------------------------------|---------|----------|------|-------|

| Flyback in          | put and sandcastle output (note 20)                                                  | I                                   |         | 1        | 1    |       |

|                     | width of horizontal blanking pulse                                                   |                                     | flyback | pulse wi | dth  |       |

|                     | width of vertical blanking pulse                                                     |                                     |         |          |      |       |

|                     | divider in search window                                                             | 50 Hz                               | _       | 21       | _    | lines |

|                     |                                                                                      | 60 Hz                               | _       | 17       | _    | lines |

|                     | divider in narrow window                                                             | 50 Hz                               | _       | 25       | _    | lines |

|                     |                                                                                      | 60 Hz                               | _       | 21       | _    | lines |

| t <sub>d</sub>      | delay between the start of the sync pulse at the video output and the burstkey pulse | 60 Hz                               |         |          |      |       |

|                     | trailing edge                                                                        |                                     | _       | _        | 9.3  | μs    |

|                     | rising edge                                                                          |                                     | 4.7     | 5.4      | 6.1  | μs    |

| Vertical rai        | mp generator (note 22)                                                               | 1                                   | -       |          | •    |       |

| l <sub>3</sub>      | input current during scan                                                            |                                     | _       | _        | 2    | μA    |

| l <sub>3</sub>      | discharge current during retrace                                                     |                                     | -       | 0.8      | -    | mA    |

| V <sub>3(p-p)</sub> | sawtooth amplitude (peak-to-peak value)                                              |                                     | _       | 1.9      | -    | V     |

| t                   | interlace timing of the internal pulses                                              | note 24                             | 30      | 32       | 34   | μs    |

| Vertical ou         | itput                                                                                | 1                                   |         |          | 4    |       |

| I <sub>4</sub>      | available output current                                                             | V <sub>4</sub> = 4 V                | _       | _        | 3    | mA    |

| V <sub>4</sub>      | maximum available output voltage                                                     | I <sub>4</sub> = 0.1 mA             | 4.4     | 5        | _    | V     |

| Vertical fee        | edback input                                                                         | 1                                   | -       |          | 4    |       |

| V <sub>5</sub>      | DC input voltage                                                                     |                                     | 2.9     | 3.3      | 3.7  | V     |

| V <sub>5(p-p)</sub> | AC input voltage (peak-to-peak value)                                                |                                     | _       | 1        | _    | V     |

| I <sub>5</sub>      | input current                                                                        |                                     | _       | -        | 12   | μA    |

|                     | internal pre-correction to sawtooth                                                  |                                     | _       | 3        | -    | %     |

|                     | deviation amplitude 50/60 Hz                                                         |                                     | _       | -        | 2    | %     |

|                     | temperature dependency of the amplitude                                              | note 24<br>ΔT = 45 °C               | -       | -        | 2    | %     |

| Vertical gu         | lard                                                                                 | •                                   |         |          |      | ,     |

| $\Delta V_5$        | active switch level at a deviation with respect to the DC feedback level             | note 23;<br>V <sub>30</sub> = 2.5 V |         |          |      |       |

|                     | guard level LOW                                                                      |                                     | -       | 1.5      | -    | V     |

|                     | guard level HIGH                                                                     |                                     | _       | 2        | _    | V     |

### TDA8304

| SYMBOL          | PARAMETER                                                                  | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|-----------------|----------------------------------------------------------------------------|------------|------|------|------|------|

| Coincidend      | ce detector/transmitter identification (note 21)                           | •          |      |      |      | •    |

| V <sub>25</sub> | voltage for in-sync condition                                              |            | _    | 9.8  | -    | V    |

| V <sub>25</sub> | voltage for no-sync condition                                              | no signal  | -    | 0.3  | -    | V    |

| V <sub>25</sub> | switching level to switch the phase detector from fast to slow             |            | 6.2  | 6.7  | 7.2  | V    |

| V <sub>25</sub> | hysteresis slow to fast                                                    |            | -    | 0.6  | -    | V    |

| V <sub>25</sub> | switching level to activate the mute function (transmitter identification) |            | 2.5  | 2.8  | 3.1  | V    |

| V <sub>25</sub> | hysteresis mute function                                                   |            | -    | 2.0  | -    | V    |

| I <sub>25</sub> | load (allowed) at pin 25                                                   |            | -2   | -    | 2    | μA   |

| 50/60 Hz id     | entification (open collector output)                                       |            | ,    |      |      |      |

| V <sub>14</sub> | output voltage at 50 Hz (no signal)                                        |            | -    | 0.3  | 0.5  | V    |

| V <sub>14</sub> | output voltage at 60 Hz                                                    |            | -    | Vp   | -    | V    |

| I <sub>14</sub> | sink current active                                                        |            | -    | -    | 5    | mA   |

| I <sub>14</sub> | output current inactive (transmitter present)                              |            | -    | -    | 1    | μA   |

### Notes to the characteristics

- Supplying a current of 9 mA to pin 12 starts the horizontal oscillator. This current can be obtained via a bleed circuit from the mains rectifier whilst the main supply for the device (V<sub>cc</sub>) is obtained from the horizontal output stage. The load current of the driver must be added to the value given.

- 2. On set AGC.

- 3. The input impedance has been chosen such that a SAW filter can be employed.

- 4. Measured with 0 dB = 450  $\mu$ V.

- 5. Measured at 10 mV RMS 100% input signal.

- 6. Projected zero point; i.e. with switched demodulator.

- 7. The output signal amplitude is determined by the AGC detector. For negative modulation the peak sync level is used as reference. With positive modulation the white level is stabilized.

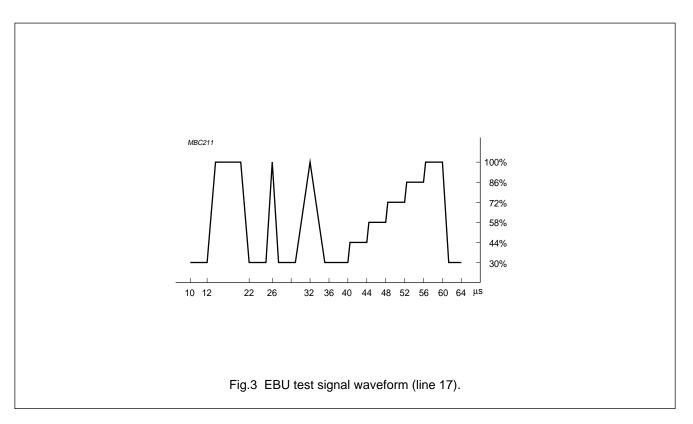

- 8. Measured according to the test line given in Fig.3. The differential gain is expressed as a percentage of the difference in peak amplitudes between the largest and smallest value relative to the subcarrier amplitude at blanking level. The differential phase is defined as the difference in degrees between the largest and smallest phase angle. The differential gain and phase are measured with a DSB signal.

- 9. This figure is valid for the complete video signal amplitude (peak white-to-black). The non-linearity is expressed as a percentage of the maximum deviation of a luminance step from the mean step, with respect to the mean step.

- 10. The test set-up and input conditions are given in Fig.5. The figures are measured at an input signal of 10 mV RMS.

- 11. Measured with a source impedance of 75  $\Omega$ .

The signal-to-noise ratio = 20  $\log \frac{V_o \text{ black-to-white}}{V_{n \text{ (rms)}} \text{ at } B = 5 \text{ MHz}}$

- 12. By means of the system switch 2 conditions can be obtained. Negative modulation with peak sync level AGC. This is obtained with pin 32 connected to ground. Positive modulation with peak white AGC. This is obtained with pin 32 connected to the positive supply.

- 13. When the video switch is in the external mode the first control loop in the synchronization circuit is not switched to a long time constant when weak signals are received.

### TDA8304

14. Defined as 20 log  $\frac{V_o \text{ unwanted video black-to-white}}{V_o \text{ wanted video-black-to-white}}$ ; measured at 4.4 MHz.

- 15. The indicated figures are measured at an input signal of 10 mV RMS. The unloaded Q-factor of the reference tuned circuit is 70. With very weak input signals the drive signal for the AFC circuit will have a high noise content. This noise input has a asymmetrical frequency spectrum which will cause an offset of the AFC output voltage. To avoid problems due to this effect a notch filter can be built into the demodulator tuned circuit. The characteristics given for weak signals are measured without a notch circuit, with a SAW filter connected in front of the IC input signal such that the input signal of the IC is 150 μV (RMS value).

- 16. Measured at an input signal amplitude of 150  $\mu$ V(RMS) (pin 21).

- 17. The minimum value is obtained by connecting a 1.8 kΩ resistor between pins 15 and 28. The slicing level can be varied by changing the value of this resistor (higher resistor value results in larger value of the minimum sync pulse amplitude). The slicing level is independent of the video information.

- 18. Frequency control is obtained by supplying a correction current to the oscillator RC network via a resistor connected between the phase 1 detector output and the oscillator network. The oscillator can be adjusted to the correct frequency by short circuiting the sync separator bias network (pin 28) to +V<sub>p</sub>. To avoid the need of a VCR switch the time constant of the phase detector at strong input signals is sufficiently short to get a stable picture during VCR playback. During the vertical retrace period the time constant is even shorter so that the head-errors of the VCR are compensated at the beginning of scan. During conditions of weak signal (information derived from the AGC circuit) the time constant is increased to obtain a better noise immunity.

- 19. This figure is valid for an external load impedance of 82 k $\Omega$  from pin 31 to the phase adjustment potentiometer (of H-shift).

- 20. The flyback input and sandcastle output have been combined on one pin. The flyback pulse is clamped to a level of 4.5 V. The minimum current to drive the second control loop is 0.1 mA.

- 21. The functions in-sync/out-of-sync and transmitter identification have been combined on this pin. The capacitor is charged during the sync pulse and discharged during the time difference between gating (6.5 μs) and the sync pulse in the internal video mode. When the circuit is in the external mode the capacitor is charged by the horizontal sync pulse and discharged continuously with a small current.

- 22. The vertical scan is synchronized by means of a divider system. Therefore no adjustment is required for the ramp generator. The divider detects whether the incoming signal has a vertical frequency of 50 or 60 Hz and corrects the vertical amplitude.

- 23. To avoid screen burn due to a collapse of the vertical deflection a continuous blanking level ( $V_{30}$  = 2.5 V) is inserted in the sandcastle pulse when the feedback voltage of the vertical deflection is not within the specified limits.

- 24. These figures are based on test samples.

| CONDITION<br>PIN 18                   | CONDITION                      | CONTROL SENSITIVITY<br>HOR.OSCILLATOR kHz / μs |           |  |

|---------------------------------------|--------------------------------|------------------------------------------------|-----------|--|

| VIDEO SWITCH                          | V <sub>25</sub>                | T2 - T1                                        | T3 = SCAN |  |

|                                       | V <sub>25</sub> > 6.7 V<br>and |                                                |           |  |

|                                       | strong signal                  | 11.3                                           | 7.6       |  |

| Low internal video                    | weak signal                    | 1.3                                            | 1.3       |  |

| Low internal video                    | V <sub>25</sub> < 6.1 V<br>and |                                                |           |  |

|                                       | strong signal                  | 11.3                                           | 7.6       |  |

|                                       | weak signal                    | 11.3                                           | 7.6       |  |

| HIGH or<br>floating<br>external video | don't care                     | 11.3                                           | 7.6       |  |

#### – 3.3 V 220 kΩ ◀ 68 nF 47 kΩ 32 system switch 3 ╢ 1 + -ᅮ 82 kΩ 4.7 kΩ 47 kΩ 47 kΩ 100 nF 8 31 ╢ 2 1 mA horizontal flyback input 390 kΩ 30 sandcastle output 3 -∟\_\_\_⊢ 220 nF 2.7 kΩ 3 –Iŀ-ᢇ horizontal drive 4 29 output vertical drive output Ĩ 150 pF 470 nF vertical feedback input 1.8 kΩ 5 28 ╢ 68 nF ╢ 4.7 μF 1.5 kΩ \_**||** tuner AGC 🔸 27 6 82 kΩ 2.7 nF + -11 $27 \ \text{k}\Omega$ 5.6 kΩ 1 7 26 10 kΩ 47 nF supply voltage input (+) 8 25 ╢ transmitter identification TDA8304 1.2 nF IF input -╢ 9 24 100 pF 1.2 nF ╢ 10 23 6.8 μF 22 nF ╢┼ 11 22 ╢ + + start/text switch 1.2 kΩ 12 21 ► AFC 220 Ω external video input 13 20 15 kΩ 1.2 kΩ + \_ 50 Hz/60 Hz 14 19 4 -16 video output video output 🗲 15 18 video switch - + 330 kΩ + 47 μF 16 17 MBC002-1 Fig.9 Application diagram.

## Small signal combination IC for colour TV

TDA8304

### Small signal combination IC for colour TV

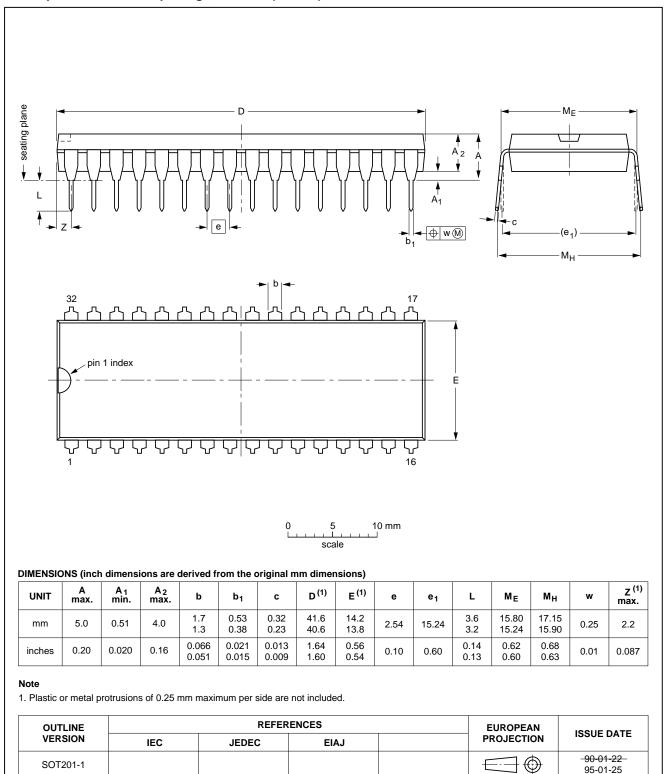

### PACKAGE OUTLINE

DIP32: plastic dual in-line package; 32 leads (600 mil)

SOT201-1

### TDA8304

### SOLDERING

### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "IC Package Databook" (order code 9398 652 90011).

### Soldering by dipping or by wave

The maximum permissible temperature of the solder is 260 °C; solder at this temperature must not be in contact with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature (Tstg max). If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

#### Repairing soldered joints

Apply a low voltage soldering iron (less than 24 V) to the lead(s) of the package, below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300 °C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400 °C, contact may be up to 5 seconds.

### DEFINITIONS

| Data sheet status         |                                                                                       |

|---------------------------|---------------------------------------------------------------------------------------|

| Objective specification   | This data sheet contains target or goal specifications for product development.       |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later. |

| Product specification     | This data sheet contains final product specifications.                                |

| Limiting values           |                                                                                       |

#### limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

### Application information

Where application information is given, it is advisory and does not form part of the specification.

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.