# **IN-CAR REMOTE AMPLIFIER DSP**

- 24-Bit FIXED-POINT DSP CORE DELIVERING UP TO 50 MIPS

- 2 x 1024 x 24 Bit OF RAM FOR X AND Y DATA MEMORY.

- 3072 x 24 Bit OF RAM FOR PROGRAM ALSO USABLE FOR DELAY

- SERIAL AUDIO INTERFACE.

- DEBUG PORT.

- CONTROL INTERFACE FOR EXTERNAL GPIOs, INTERRUPTS, AND RESET.

- SPI AND I<sup>2</sup>C FOR COMMUNICATION BETWEEN EXTERNAL MICRO AND DSP. BOTH MASTER AND SLAVE OPERATING MODES.

- PLL CLOCK OSCILLATOR

- 5V-TOLERANT 3.3V I/O INTERFACE

#### DESCRIPTION

This device is a high-performance, fully programmable DSP, suitable for a wide range of applications and particularly for Audio and Sound Processing. It contains a 24-bit 50 MIPS DSP core, several interfaces

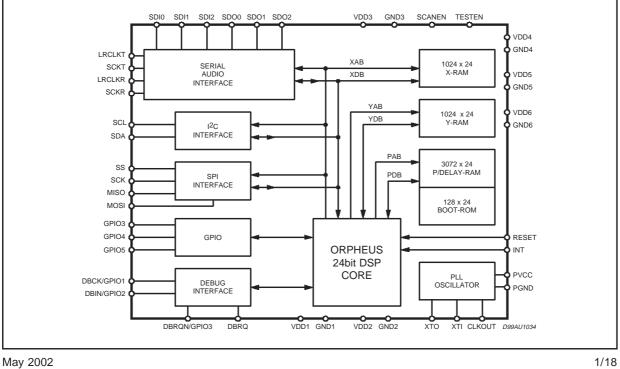

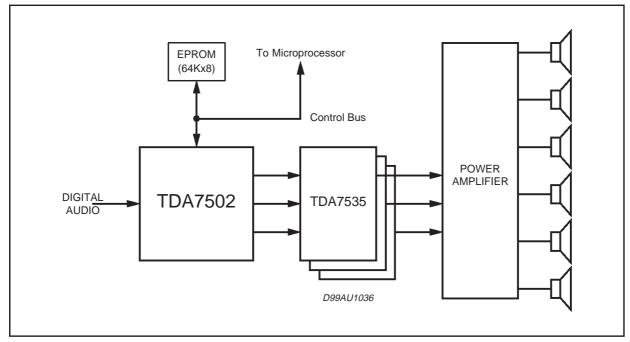

#### **BLOCK DIAGRAM**

for control and data, plus a configurable PLL.

The computational power and the memory configuration make this device particularly suitable for in car equalisation. This device will offer the best trade-off between performance and cost when coupled with the TDA7535, or other devices of the same family. A library of sound processing functions is available for this device: some of these functions are: parametric equaliser, cross over filters, acoustic delay, dynamic compression, Vol/Bass/Treble/Fader, active equalisation, Stereo Spatial Enhancement and more.

#### ABSOLUTE MAXIMUM RATINGS

| Symbol           | Parameter                                | Value                          | Unit |

|------------------|------------------------------------------|--------------------------------|------|

| V <sub>dd</sub>  | DC Supply voltage                        | -0.5 to 4.6                    | V    |

| V <sub>in</sub>  | Digital input voltage (XTI and XTO only) | -0.5 to (V <sub>DD</sub> +0.5) | V    |

| V <sub>in</sub>  | Digital input voltage (*)                | 6.5                            | V    |

| Тј               | Operating junction temperature range     | -40 to 125                     | °C   |

| T <sub>stg</sub> | Storage temperature                      | -55 to 150                     | °C   |

(\*) When the IC is powered.

Warning: Operation at or beyond these limit may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

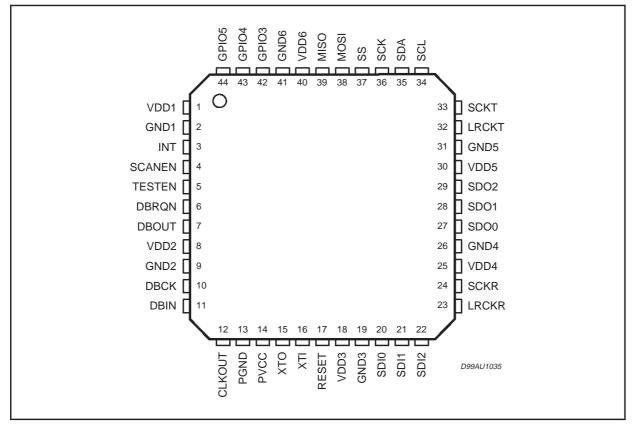

# PIN CONNECTION (Top view)

#### THERMAL DATA

| R <sub>th j-amb (*)</sub> Thermal Resistance Junction to Ambient | 68 | °C/W |

|------------------------------------------------------------------|----|------|

57

(\*) In still air.

# **PIN DESCRIPTION**

| N. | Name               | Туре | Reset<br>Status | Function                                                                                                                                                                                                           |

|----|--------------------|------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | VDD1               | Р    | -               | 3.3V core supply.                                                                                                                                                                                                  |

| 2  | GND1               | G    | -               | Core ground.                                                                                                                                                                                                       |

| 3  | INT                | I/O  | -               | External interrupt line (Input/Output). When this line is asserted low, the DSP may be interrupted. Acts as IRQA line of DSP core.                                                                                 |

| 4  | SCANEN             | I    | -               | SCAN Enable When active with TESTEN also active, controls theshifting of the internal scan chains.                                                                                                                 |

| 5  | TESTEN             | I    | -               | Test Enable. When active, puts the chip into test mode and muxes the XTI clock to all flip-flops. When SCANEN is also active, the scan chain shifting                                                              |

| 6  | DBRQN              | I    | -               | Debug Port Request Input. Means of entering the Debug mode of operation.                                                                                                                                           |

| 7  | DBOUT/GPIO2        | I/O  | I               | The serial data output for the Debug Port. Can also be used as a GPIO.                                                                                                                                             |

| 8  | VDD2               | I    | -               | 3.3V core supply.                                                                                                                                                                                                  |

| 9  | GND2               | I    | -               | Core ground.                                                                                                                                                                                                       |

| 10 | DBCK/GPIO0         | I/O  | I               | Debug Port Bit Clock/Chip Status 1. The serial clock for the Debug<br>Port is provided when an input. When an output, provides<br>information about the chip status. Can also be used as GPIO                      |

| 11 | DBIN/GPIO1         | I/O  | I               | Debug Port Serial Input/Chip Status 0. The serial data input for the<br>Debug Port is provided when an input. When an output, provides<br>information about the chip status. Can also be used as GPIO.             |

| 12 | CLKOUT             | 0    | -               | Output Clock.                                                                                                                                                                                                      |

| 13 | PGND               | G    | -               | PLL Clock Ground Input. Ground connection for oscillator circuit.                                                                                                                                                  |

| 14 | PVCC               | Р    | -               | PLL Clock Power Supply. Positive supply for PLL Clock Oscillator.                                                                                                                                                  |

| 15 | XTO <sup>(1)</sup> | 0    | High            | Crystal Oscillator Output. Crystal Oscillator output drive.                                                                                                                                                        |

| 16 | XTI <sup>(1)</sup> | I    | -               | Crystal Oscillator Input. External Clock Input or crystal connection.                                                                                                                                              |

| 17 | RESET              | I/O  | I               | System Reset. A logic low level applied to RESET input initializes DSPs. During Debug Mode if this pin is pulled low in while the DBRQN line is pulled low then the DSP pointed to by the DBSEL pin will be reset. |

| 18 | VDD3               | Р    | -               | 3.3V Supply.                                                                                                                                                                                                       |

| 19 | GND3               | G    | -               | Ground.                                                                                                                                                                                                            |

| 20 | SDI0               | I    | -               | SDI0 is a stereo digital audio data input pin channel 0.                                                                                                                                                           |

| 21 | SDI1               | I    | -               | SDI1 is a stereo digital audio data input pin channel 1.                                                                                                                                                           |

| 22 | SDI2               | I    | -               | SDI2 is a stereo digital audio data input pin channel 2.                                                                                                                                                           |

| 23 | LRCKR              | I/O  | -               | Left-Right clock for SAI Receiver. Master or slave.                                                                                                                                                                |

| 24 | SCKR               | I/O  | -               | SAI receive bit clock. Master or slave.                                                                                                                                                                            |

# **PIN DESCRIPTION** (continued)

| N. | Name  | Туре | Reset<br>Status | Function                                                                                                           |

|----|-------|------|-----------------|--------------------------------------------------------------------------------------------------------------------|

| 25 | VDD4  | Р    | -               | 3.3V Supply.                                                                                                       |

| 26 | GND4  | G    | -               | Ground.                                                                                                            |

| 27 | SDO0  | 0    | High            | SDO0 is a stereo digital audio data output pin channel 0.                                                          |

| 28 | SDO1  | 0    | High            | SDO1 is a stereo digital audio data output pin channel 1.                                                          |

| 29 | SDO2  | 0    | High            | SDO2 is a stereo digital audio data pin channel 2.                                                                 |

| 30 | VDD5  | Р    | -               | 3.3V Supply.                                                                                                       |

| 31 | GND5  | G    | -               | Ground.                                                                                                            |

| 32 | LRCKT | I/O  | -               | SAI transmit left/right clock. Master or slave.                                                                    |

| 33 | SCKT  | I/O  | -               | SAI transmit bit clock. Master or slave.                                                                           |

| 34 | SCL   | I/O  | -               | Clock line for I <sup>2</sup> C bus. Schmitt trigger input.                                                        |

| 35 | SDA   | I/O  | -               | Data line for I <sup>2</sup> C bus. Schmitt trigger input.                                                         |

| 36 | SCK   | 1    | -               | Bit clock for SPI control interface.                                                                               |

| 37 | SS    | 1    | -               | Slave select input pin for SPI control interface.                                                                  |

| 38 | MOSI  | I/O  | -               | Serial Data Output for SPI type serial port when in SPI Master Mode and Serial Data Input when in SPI Slave Mode.  |

| 39 | MISO  | I/O  | -               | Serial Data Input for SPI style serial port when in SPI Master Mode and Serial Data Output when in SPI Slave Mode. |

| 40 | VDD6  | Р    | -               | 3.3V Supply.                                                                                                       |

| 41 | GND6  | G    | -               | Ground.                                                                                                            |

| 42 | GPIO3 | I/O  | -               | This pin is dedicated as general I/O.                                                                              |

| 43 | GPIO4 | I/O  | -               | This pin is dedicated as general I/O.                                                                              |

| 44 | GPIO5 | I/O  | -               | This pin is dedicated as general I/O.                                                                              |

57

Notes: 1. XTI and XTO are not 5V tolerant

#### **RECOMMENDED DC OPERATING CONDITIONS**

| Symbol          | Parameter                 | Test Condition | Min. | Тур. | Max. | Unit |

|-----------------|---------------------------|----------------|------|------|------|------|

| V <sub>dd</sub> | 3.3V Power Supply Voltage |                | 3.15 | 3.3  | 3.45 | V    |

#### **POWER CONSUMPTION**

| Symbol          | Parameter       | Test Condition                  | Min. | Тур. | Max. | Unit |

|-----------------|-----------------|---------------------------------|------|------|------|------|

| I <sub>dd</sub> | Maximum current | @3.3V and T <sub>j</sub> =125°C |      |      | 250  | mA   |

Note: 50MHz internal DSP clock

#### PLL CHARACTERISTICS

| Symbol           | Parameter              | Test Condition                   | Min. | Тур. | Max. | Unit |

|------------------|------------------------|----------------------------------|------|------|------|------|

|                  | Lock Time (note1)      | @3.3V and T <sub>j</sub> = 125°C |      |      | 3    | ms   |

| F <sub>vco</sub> | VCO Frequency (note 2) |                                  | 70   |      | 140  | MHz  |

Note: 1. Depending on VCO output frequency.

2.  $F_{dsp} = F_{vco}/2$  when PLL is running

# **OSCILLATOR CHARACTERISTICS**

| Symbol           | Parameter                      | Test Condition                    | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------|-----------------------------------|------|------|------|------|

| F <sub>osc</sub> | Max Oscillator Frequency (XTI) | @ 3.3V and T <sub>j</sub> = 125°C | 8    |      | 12.5 | MHz  |

#### **GENERAL INTERFACE ELECTRICAL CHARACTERISTICS**

| Symbol            | Parameter                                               | Test Condition                                 | Min. | Тур. | Max. | Unit |

|-------------------|---------------------------------------------------------|------------------------------------------------|------|------|------|------|

| lii               | Low LevelInput Current without<br>pullup device         | V <sub>i</sub> = 0V (note 1)                   |      |      | 1    | μA   |

| l <sub>ih</sub>   | High Level Input Current without<br>pullup device       | $V_i = V_{dd}$ (note 1)                        |      |      | 1    | μA   |

| l <sub>oz</sub>   | Tri-state Output leakage without<br>pull up/down device | $V_o = 0V \text{ or } V_{dd} \text{ (note 1)}$ |      |      | 1    | μA   |

| I <sub>ozFT</sub> | 5V Tolerant Tri-state Output                            | $V_o = 0V \text{ or } V_{dd} \text{ (note 1)}$ |      |      | 1    | μΑ   |

|                   | leakage without pull up/down device                     | $V_0 = 5.5V$                                   |      | 1    | 3    | μA   |

| Ilatchup          | I/O latch-up current                                    | $V < 0V, V > V_{dd}$                           | 200  |      |      | mA   |

| V <sub>esd</sub>  | Electrostatic Protection                                | Leakage , 1µA (note 2)                         | 1500 |      |      | V    |

Note: 1. The leakage currents are generally very small, <1nA. The value given here, 1mA, ia amaximum that can occur after an Electrostatic Stress on the pin.

2. Human Body Model.

#### LOW VOLTAGE TTL INTERFACE DC ELECTRICAL CHARACTERISTICS

| Symbol              | Parameter                         | Test Condition | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------|----------------|------|------|------|------|

| Vil                 | Low Level Input Voltage           | (note 1)       |      |      | 0.8  | V    |

| V <sub>ih</sub>     | High Level Input Voltage          | (note 1)       | 2    |      |      | V    |

| V <sub>ilhyst</sub> | Low level threshold input falling | (note 1)       | 0.9  |      | 1.35 | V    |

| V <sub>ihhyst</sub> | Low level threshold input falling | (note 1)       | 1.3  |      | 1.9  | V    |

| V <sub>hyst</sub>   | Schmitt trigger hysteresis        | (note 1)       | 0.4  |      | 0.7  | V    |

| Symbol          | Parameter                 | Test Condition                         | Min. | Тур. | Max. | Unit |

|-----------------|---------------------------|----------------------------------------|------|------|------|------|

| V <sub>ol</sub> | Low level output Voltage  | I <sub>ol</sub> = XmA (notes 1, 2 & 3) |      |      | 0.4  | V    |

| V <sub>oh</sub> | High level output Voltage |                                        | 2.4  |      |      | V    |

Note:

1. TTL specifications only apply to the supply voltage range Vdd = 3.0V to 3.6V

2. Takes into account 200mV voltage drop in both supply lines.

3. X is the source/sink current under worst case conditions and is reflected in the name of the I/O cell according to the drive capability.

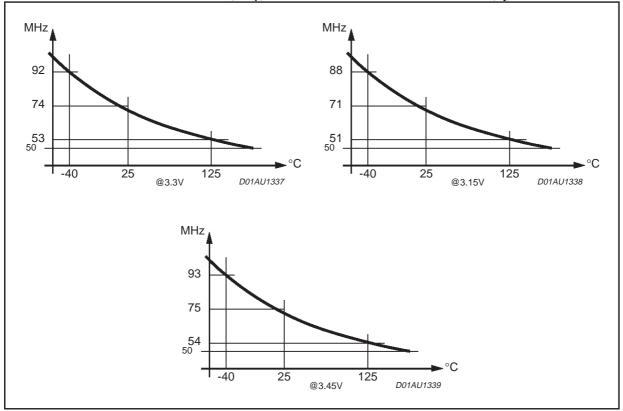

#### **DSP CORE**

| Symbol           | Parameter                   | Test Condition                    | Min. | Тур. | Max. | Unit |

|------------------|-----------------------------|-----------------------------------|------|------|------|------|

| F <sub>dsp</sub> | Maximum DSP clock frequency | @3.15V and T <sub>j</sub> = 125°C | 50   |      |      | MHz  |

# MAXIMUM DSP CLOCK FREQUENCY (Fdsp) VERSUS JUNCTION TEMPERATURE (Tj)

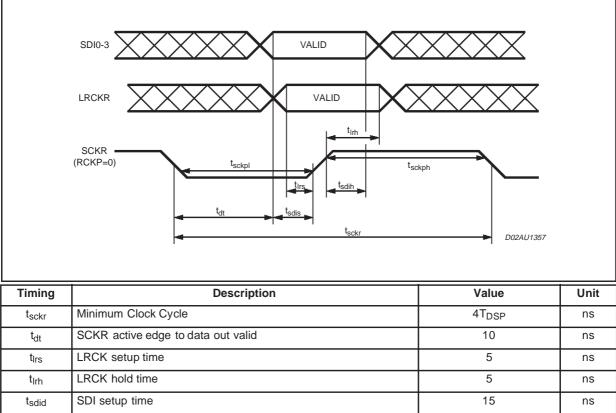

# SAI INTERFACE

# Figure 1. SAI Timings

| -                  |                       |                        |    |

|--------------------|-----------------------|------------------------|----|

| t <sub>lrh</sub>   | LRCK hold time        | 5                      | ns |

| t <sub>sdid</sub>  | SDI setup time        | 15                     | ns |

| t <sub>sdih</sub>  | SDI hold time         | 15                     | ns |

| t <sub>sckph</sub> | Minimum SCK high time | 0.35 t <sub>sckr</sub> | ns |

| t <sub>sckpl</sub> | Minimum SCK low time  | 0.35 t <sub>sckr</sub> | ns |

Note  $T_{DSP}$  = dsp master clock cycle time =  $1/F_{DSP}$

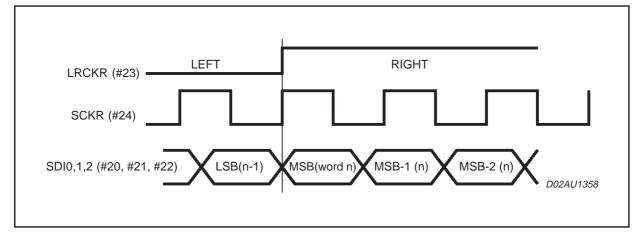

# Figure 2. SAI protocol when RLRS=0; RREL=0; RCKP=1; RDIR=0

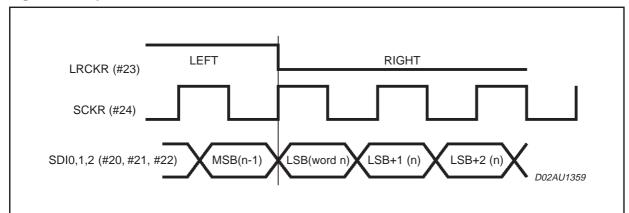

#### Figure 3. SAI protocol when RLRS=1; RREL=0; RCKP=1; RDIR=1.

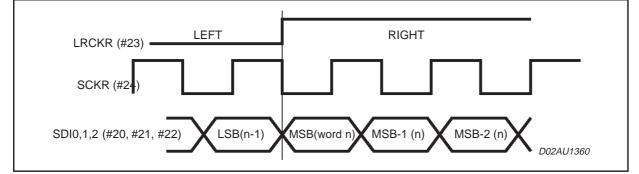

Figure 4. SAI protocol when RLRS=0; RREL=0; RCKP=0; RDIR=0.

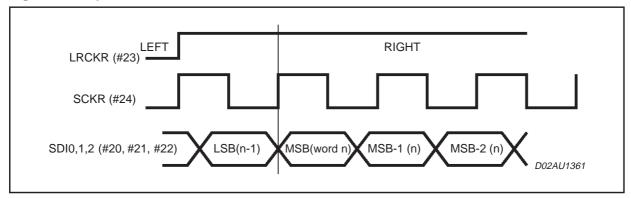

Figure 5. SAI protocol when RLRS=0; RREL=1; RCKP=1; RDIR=0.

57

Note: some timing is used for transmitter and receiver

8/18

# **SPI INTERFACES**

| Symbol                 | Description             | Min Value            | Unit |

|------------------------|-------------------------|----------------------|------|

|                        | MASTER                  |                      | •    |

| t <sub>sclk</sub>      | Clock Cycle             | 12T <sub>DSP</sub>   | ns   |

| t <sub>dtr</sub>       | Sclk edge to MOSI valid | 40                   | ns   |

| tmisosetup             | MISO setup time         | 16                   | ns   |

| t <sub>misohold</sub>  | MISO hold time          | 4                    | ns   |

| t <sub>sclkh</sub>     | SCK high time           | 0.5t <sub>sclk</sub> | ns   |

| t <sub>sclkl</sub>     | SCK high low            | 0.5t <sub>sclk</sub> | ns   |

|                        | SLAVE                   | 1                    | -    |

| t <sub>sclk</sub>      | Clock Cycle             | 12T <sub>DSP</sub>   | ns   |

| t <sub>dtr</sub>       | Sclk edge to MOSI valid | 40                   | ns   |

| t <sub>mosisetup</sub> | MOSI setup time         | 16                   | ns   |

| t <sub>mosihold</sub>  | MOSI hold time          | 4                    | ns   |

| t <sub>sclkh</sub>     | SCK high time           | 0.5t <sub>sclk</sub> | ns   |

| t <sub>sclkl</sub>     | SCK high low            | 0.5t <sub>sclk</sub> | ns   |

# Figure 6. SPI Clocking scheme.

| SS (#37)         |                                                |

|------------------|------------------------------------------------|

| SCK (#36)        | (CPOL=0, CPHA=0)                               |

| SCK (#36)        | (CPOL=0, CPHA=1)                               |

| SCK (#36)        | (CPOL=1, CPHA=0)                               |

| SCK (#36)        | (CPOL=1, CPHA=1)                               |

| MISO, MOSI (#38, | #39) MSB 6 5 4 3 2 1 LSB                       |

|                  |                                                |

|                  | INTERNAL STROBE FOR INTERNAL CAPTURE D02AU1362 |

|                  |                                                |

# **Debug Port Interface**

| No. | Characteristics                                                   | dclk =       | Unit       |    |

|-----|-------------------------------------------------------------------|--------------|------------|----|

| NO. |                                                                   | Min.         | Max.       |    |

| 1   | DBCK rise time                                                    |              | 3          | ns |

| 2   | DBCK fall time                                                    |              | 3          | ns |

| 3   | DBCK Low                                                          | 40           |            | ns |

| 4   | DBCK High                                                         | 40           |            | ns |

| 5   | DBCK Cycle Time                                                   | 200          |            | ns |

| 6   | DBRQN Asserted to DBOUT (ACK) Asserted                            | 5 TDSP       |            | ns |

| 7   | DBCK High to DBOUT Valid                                          |              | 42         | ns |

| 8   | DBCK High to DBOUT Invalid                                        | 3            |            | ns |

| 9   | DBIN Valid to DBCK Low (Set-up)                                   | 15           |            | ns |

| 10  | DBCK Low to DBIN Invalid (Hold)                                   | 3            |            | ns |

|     | DBOUT (ACK) Asserted to First DBCK High                           | 2 Tc         |            | ns |

|     | DBOUT (ACK) Assertion Width                                       | 4.5 TDSP - 3 | 5 TDSP + 7 | ns |

| 11  | Last DBCK Low of Read Register to First DBCK High of Next Command | 7 TDSP + 10  |            | ns |

| 12  | Last DBCK Low to DBOUT Invalid (Hold)                             | 3            |            | ns |

|     | DBSEL setup to DBCK                                               | TDSP         |            | ns |

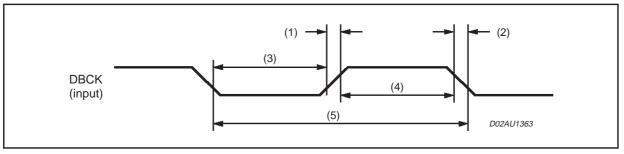

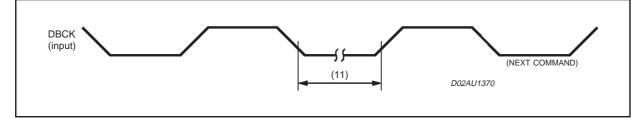

# Figure 7. Debug Port Serial Clock Timing.

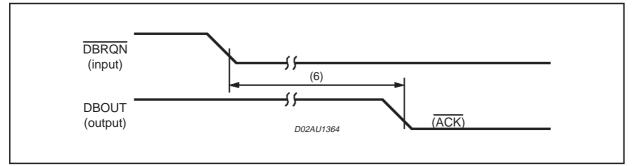

# Figure 8. Debug Port Acknowledge Timing.

57

10/18

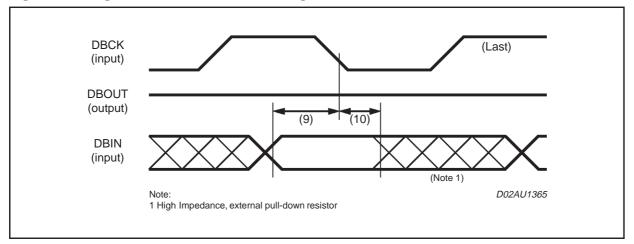

Figure 9. Debug Port Data I/O to Status Timing.

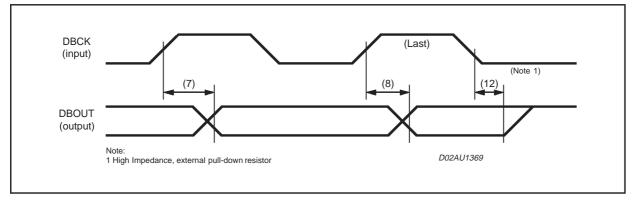

Figure 10. Debug Port Read Timing.

Figure 11. Debug Port DBCK Next Command After Read Register Timing.

57

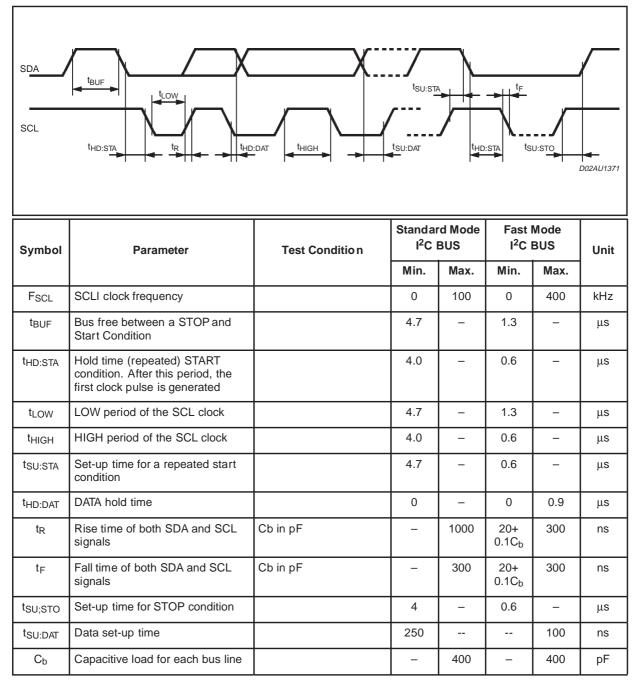

# I<sup>2</sup>C TIMING

# Figure 12. Definition of Timing for the fC BUS.

### FUNCTIONAL DESCRIPTION

The TDA7502 contains one DSP Core and associated peripherals.

#### 24-BIT DSP CORE.

The DSP core is used to process the converted analog audio data coming from the CODEC chip via the SAI and return it for analog conversion. Functions such as volume, tone, balance, and fader control, as well as spatial enhancement and general purpose signal processing may be performed by the DSP.

Some capabilities of the DSPs are listed below:

Single cycle multiply and accumulate with convergent rounding and condition code generation

- 2 x 56-bit Accumulators

- Double precision multiply

- Scaling and saturation arithmetic

- 48-bit or 2 x 24-bit parallel moves

- 64 interrupt vector locations

- Fast or long interrupts possible

- Programmable interrupt priorities and masking

- 8 each of Address Registers, Address Offset Registers and Address Modulo Registers

- Linear, Reverse Carry, Multiple Buffer Modulo, Multiple Wrap-around Moduloaddress arithmetic

- Post-increment or decrement by 1 or by offset, Index by offset, predecrement address

- Repeat instruction and zero overhead DO loops

- Hardware stack capable of nesting combinations of 7 DO loops or 15 interrupts/ subroutines

- Bit manipulation instructions possible on all registers and memory locations. Also Jump on bit test.

- 4 pin serial debug interface

- Debug access to all internal registers, buses and memory locations

- 5 word deep program address history FIFO

- Hardware and software breakpoints for both program and data memory accesses

- Debug Single stepping, Instruction injection and Disassembly of program memory

#### **DSP PERIPHERALS**

There are a number of peripherals that are tightly coupled to the DSP Core. Each of the peripherals are

listed below and described in the following sections.

- 1024 x 24-Bit X-RAM.

- 1024 x 24-Bit Y-RAM.

- 3072 x 24-Bit Program RAM

- 512 x 24-Bit Boot ROM.

- Serial Audio Interface (SAI)

- Single Debug Port

- Programmable Control Interface (SPI/I2C)

- GPIO

#### DATA AND PROGRAM MEMORY

Each of the memories are described below.

#### 1024 x 24-Bit X-RAM (XRAM)

This is a 1024 x 24-Bit Single Port SRAM used for storing coefficients. The 16-Bit XRAM address, XABx(15:0) is generated by the Address Generation Unit of the DSP core. The 24-Bit XRAM Data, XD-Bx(23:0), may be written to and read from the Data ALU of the DSP core. The XDBx Bus is also connected to the Internal Bus Switch so that it can be routed to and from all peripheral blocks.

#### 1024 x 24 Bit Y-RAM (YRAM)

This is a 1024 x 24-Bit Single Port SRAM used for storing coefficients. The 16-Bit address, YABx(15:0) is generated by the Address Generation Unit of the DSP core. The 24-Bit Data, YDBx(23:0), is written to and read from the Data ALU of the DSP core. The YDBx Bus is also connected to the Internal Bus Switch so that it can be routed to and from other blocks.

#### 3072 X 24-Bit Program RAM

This is a 3072 x 24-Bit Single Port SRAM used for storing and executing program code. The 16-Bit PRAM Address, PABx(15:0) is generated by the Program Address Generator of the DSP core for Instruction Fetching, and by the AGU in the case of the Move Program Memory (MOVEM) Instruction. The 24-Bit PRAM Data (Program Code), PDBx(23:0), can only be written to using the MOVEM instruction.

During instruction fetching the PDBx Bus is routed to the Program Decode Controller of the DSP core for instruction decoding.

Spare space in the Program area may be used as data memory to implement delay lines for example.

### 512 x 24-Bit Bootstrap ROM (Boot ROM)

This is a 512 x 24-Bit factory programmed Boot ROM used for storing the program sequence for initializing the DSP.

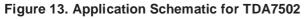

Essentially this consists of a routine that is called when the DSP comes out of reset. There are four different boot modes supported by the boot ROM. The first mode loads the application program via SPI interface where Casper's SPI is in Master Mode. The second boot mode enables the Debug Port and waits. The third and fourth modes load the application program via the  $I^2C$  interface, one with Casper's  $I^2C$  Interface configured in slave mode and the other in master mode. Which boot mode to enter is configured by sampling the states of the GPIO4 and GPIO3 pins at reset as shown in the table below.

| Modes                     | Description                                       | GPIO3 | GPIO4 |

|---------------------------|---------------------------------------------------|-------|-------|

| 0-SPI Master              | load PRAM, XRAM<br>and YRAM from SPI              | 0     | 0     |

| 1-Debug                   | enable Debug Port                                 | 0     | 1     |

| 2-I <sup>2</sup> C Master | load PRAM, XRAM<br>and YRAM from I <sup>2</sup> C | 1     | 0     |

| 3-I <sup>2</sup> C Slave  | oad PRAM, XRAM<br>and YRAM from I <sup>2</sup> C  | 1     | 1     |

Table 1. Casper IC Boot Modes

### Serial Audio Interface (SAI)

The SAI is used to deliver digital audio to the DSPs from an external source. Once processed by the DSPs, it can be returned through this interface. The features of the SAI are listed below.

- Three Synchronized Stereo Data Transmission Lines

- Three Synchronized Stereo Data Reception Lines

- Master/Slave operating modes

- Transmit and Receive Interrupt Logic triggers on Left/Right data pairs

- Receive and Transmit Data Registers have two locations to hold left and right data.

### **Serial Peripheral Interface**

The DSP core requires a serial interface to receive commands and data over the LAN. During an SPI transfer, data is transmitted and received simultaneously. A serial clock line synchronizes shifting and sampling of the information on the two serial data lines. A slave select line allows individual selection of a slave SPI device.

When an SPI transfer occurs an 8-bit word is shifted out one data pin while another 8-bit character is simultaneously shifted in a second data pin.The central element in the SPI system is the shift register and the read data buffer. The system is single buffered in the transfer direction and double buffered in the receive direction.

# I<sup>2</sup>C Interface

The inter Integrated Circuit bus is a single bidirectional two-wire bus used for efficient inter IC control. All  $I^2C$  bus compatible devices incorporate an on-chip interface which allows them communicate directly with each other via the  $I^2C$  bus.

Every component hooked up to the  $I^2C$  bus has its own unique address whether it is a CPU, memory or some other complex function chip. Each of these chips can act as a receiver and /or transmitter on its functionality.

#### **General Purpose Input/Output**

The DSP requires a set of external general purpose input/output lines, and a reset line. These signals are used by external devices to signal events to the DSP. The GPIO lines are implemented as DSP 's peripherals.

### **PLL Clock Oscillator**

The PLL Clock Oscillator can accept an external clock at XTI or it can be configured to run an internal oscillator when a crystal is connected across pins XTI & XTO. There is an input divide block IDF (1 -> 32) at the XTI clock input and a multiply block MF (9 -> 128) in the PLL loop. Hence the PLL can multiply the external input clock by a ratio MF/IDF to generate the internal clock. This allows the internal clock to be within 2 MHz of any desired frequency even when XTI is much greater than 1 MHz. It is recommended that the input clock is not divided down to less than 1 MHz as this reduces the Phase Detector's update rate.

The clocks to the DSP can be selected to be either the VCO output divided by 2 to 16, or be driven by the XTI pin directly.

The crystal oscillator and the PLL will be gated off when entering the power-down mode (by setting a register on DSP0).

# **Application Scheme**

57

15/18

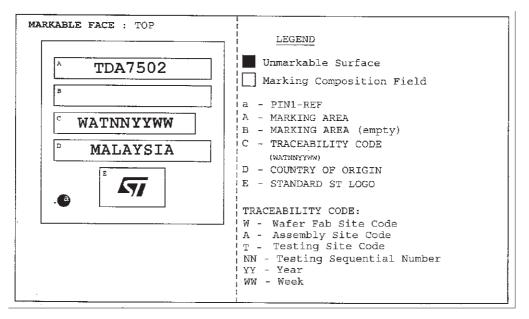

# **PACKAGE MARKING**

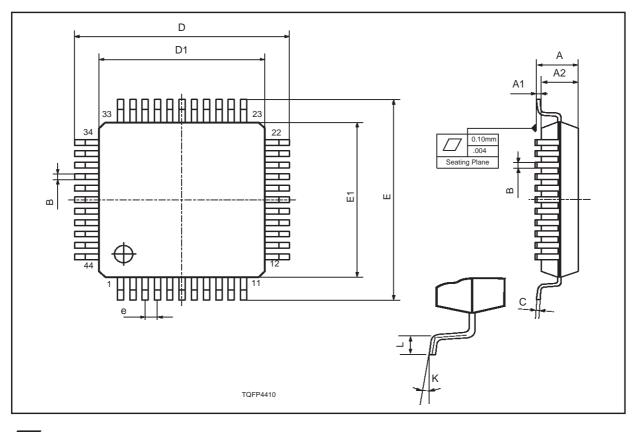

| DIM. |                                | mm    |      |       | inch  |       |

|------|--------------------------------|-------|------|-------|-------|-------|

|      | MIN.                           | TYP.  | MAX. | MIN.  | TYP.  | MAX.  |

| Α    |                                |       | 1.60 |       |       | 0.063 |

| A1   | 0.05                           |       | 0.15 | 0.002 |       | 0.006 |

| A2   | 1.35                           | 1.40  | 1.45 | 0.053 | 0.055 | 0.057 |

| В    | 0.30                           | 0.37  | 0.45 | 0.012 | 0.014 | 0.018 |

| С    | 0.09                           |       | 0.20 | 0.004 |       | 0.008 |

| D    |                                | 12.00 |      |       | 0.472 |       |

| D1   |                                | 10.00 |      |       | 0.394 |       |

| D3   |                                | 8.00  |      |       | 0.315 |       |

| е    |                                | 0.80  |      |       | 0.031 |       |

| E    |                                | 12.00 |      |       | 0.472 |       |

| E1   |                                | 10.00 |      |       | 0.394 |       |

| E3   |                                | 8.00  |      |       | 0.315 |       |

| L    | 0.45                           | 0.60  | 0.75 | 0.018 | 0.024 | 0.030 |

| L1   |                                | 1.00  |      |       | 0.039 |       |

| к    | 0°(min.), 3.5°(typ.), 7°(max.) |       |      |       |       |       |

# OUTLINE AND MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics ® 2002 STMicroelectronics - All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco -Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

http://www.st.com