### INTEGRATED CIRCUITS

### DATA SHEET

# **TDA4685**Video processor with automatic cut-off control

Preliminary specification

File under Integrated Circuits, IC02

May 1993

**TDA4685**

#### **FEATURES**

- · Operates from an 8 V DC supply

- Black level clamping of the colour difference, luminance and RGB input signals with coupling-capacitor DC level storage

- Two analog RGB inputs, selected either by fast switch signals or the I<sup>2</sup>C-bus; brightness and contrast control of these RGB inputs

- Saturation, contrast, brightness and white adjustment via I<sup>2</sup>C-bus

- Same RGB output black levels for Y/CD and RGB input signals

- Timing pulse generation from either a 2- or 3-level sandcastle pulse for clamping, vertical synchronization and cut-off timing pulses

- Automatic cut-off control or clamped output selectable via I<sup>2</sup>C-bus

- Automatic cut-off control with picture tube leakage current compensation

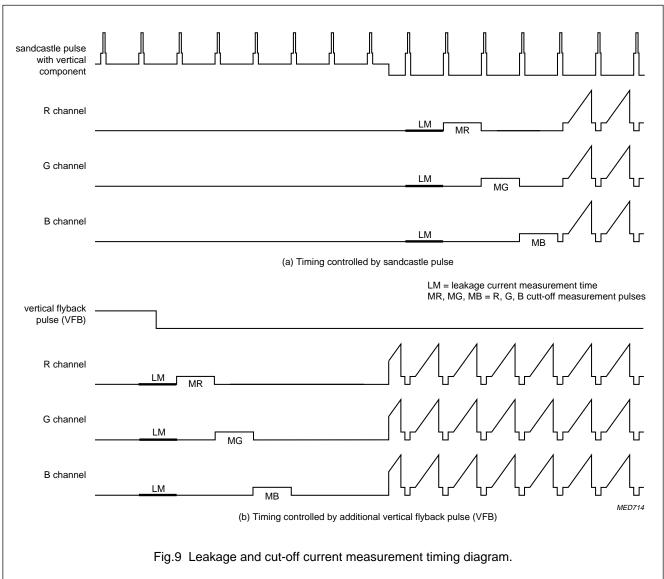

- Cut-off measurement pulses after end of the vertical blanking pulse or end of an extra vertical flyback pulse

- Two switch-on delays to prevent discolouration before steady-state operation

- · Average beam current and peak drive limiting

- PAL/SECAM or NTSC matrix selection via I2C-bus

- Emitter-follower RGB output stages to drive the video output stages

- I<sup>2</sup>C-bus controlled DC output e. g. for hue-adjust of NTSC (multistandard) decoders

#### **GENERAL DESCRIPTION**

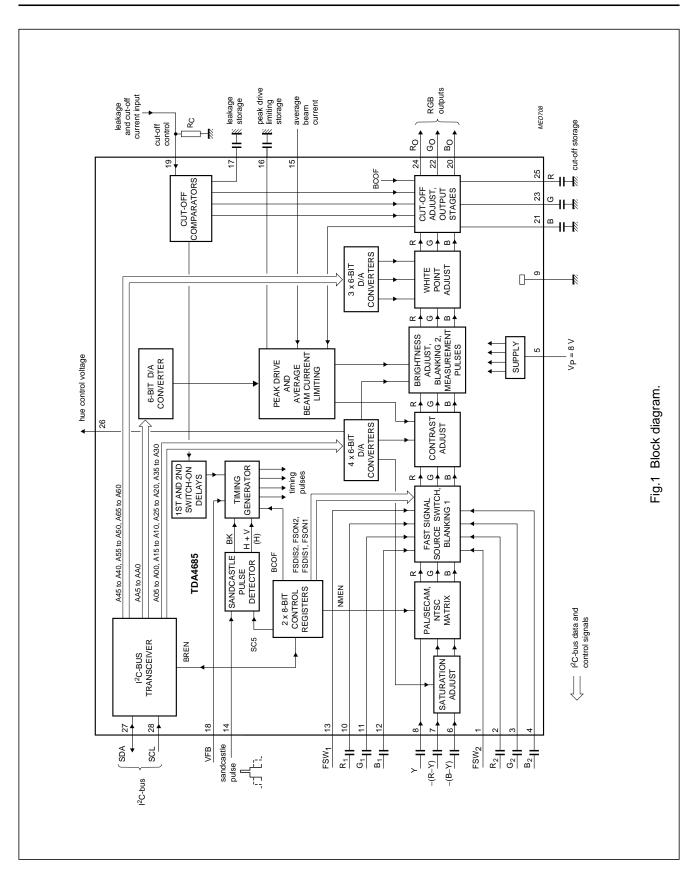

The TDA4685 is a monolithic, integrated circuit with a luminance and a colour difference interface for video processing in TV receivers.

Its primary function is to process the luminance and colour difference signals from a colour decoder which is equipped e. g. with the multistandard decoder TDA4655 or TDA9160 plus delayline TDA4661 and the Picture Signal

Improvement (PSI) IC TDA467X or from a Feature Module. The required input signals are:

- luminance and negative colour difference signals

- 2- or 3-level sandcastle pulse for internal timing pulse generation

- I<sup>2</sup>C-bus data and clock signals for microprocessor control.

Two sets of analog RGB colour signals can also be inserted, e.g. one from a peritelevision connector and the other from an on-screen display generator. The TDA4685 has I<sup>2</sup>C-bus control of all parameters and functions with automatic cut-off control of the picture tube cathode currents. It provides RGB output signals for the video output stages.

The TDA4685 is a simplified, pin compatible (except pin 18) version of the TDA4680. The module address via the I<sup>2</sup>C-bus can be used for both ICs; where a function is not included in the TDA4685 then the I<sup>2</sup>C-bus command is not executed. The differences with the TDA4680 are:

- no automatic white level control; the white levels are determined directly by the I<sup>2</sup>C-bus data

- RGB reference levels for automatic cut-off control are not adjustable via I<sup>2</sup>C-bus

- · clamping delay is fixed

- only contrast and brightness adjust for the RGB input signals

- the measurement lines are triggered either by the trailing edge of the vertical component of the sandcastle pulse or by the trailing edge of an optional external vertical flyback pulse (on pin 18), according to which occurs first.

The TDA4686 is like TDA4685 but intended for double line frequency application.

### Video processor with automatic cut-off control

TDA4685

### **QUICK REFERENCE DATA**

| SYMBOL              | PARAMETER                                                               | MIN. | TYP. | MAX. | UNIT |

|---------------------|-------------------------------------------------------------------------|------|------|------|------|

| V <sub>P</sub>      | supply voltage (pin 5)                                                  | 7.2  | 8.0  | 8.8  | V    |

| l <sub>P</sub>      | supply current (pin 5)                                                  | _    | 60   | _    | mA   |

| V <sub>8(p-p)</sub> | luminance input (peak-to-peak value)                                    | _    | 0.45 | _    | V    |

| V <sub>6(p-p)</sub> | -(B-Y) input (peak-to-peak value)                                       | _    | 1.33 | _    | V    |

| V <sub>7(p-p)</sub> | -(R-Y) input (peak-to-peak value)                                       | _    | 1.05 | _    | V    |

| V <sub>14</sub>     | three-level sandcastle pulse                                            |      |      |      |      |

|                     | H+V                                                                     | _    | 2.5  | _    | V    |

|                     | н                                                                       | _    | 4.5  | _    | V    |

|                     | BK                                                                      | _    | 8.0  | _    | V    |

|                     | two-level sandcastle pulse                                              |      |      |      |      |

|                     | H + V                                                                   | _    | 2.5  | _    | V    |

|                     | ВК                                                                      | _    | 4.5  | _    | V    |

| Vi                  | RGB input signals at pins 2, 3, 4, 10, 11 and 12 (black-to-white value) | _    | 0.7  | _    | V    |

| V <sub>o(p-p)</sub> | RGB outputs at pins 24, 22 and 20 (peak-to-peak value)                  | _    | 2.0  | _    | V    |

| T <sub>amb</sub>    | operating ambient temperature                                           | 0    | _    | +70  | °C   |

### **ORDERING INFORMATION**

| EXTENDED<br>TYPE NUMBER |      | PAC             | CKAGE    |                       |

|-------------------------|------|-----------------|----------|-----------------------|

|                         | PINS | PIN<br>POSITION | MATERIAL | CODE                  |

| TDA4685                 | 28   | DIL             | plastic  | SOT117 <sup>(1)</sup> |

### Note

1. SOT117-1; 1996 November 25.

**TDA4685**

### Video processor with automatic cut-off control

TDA4685

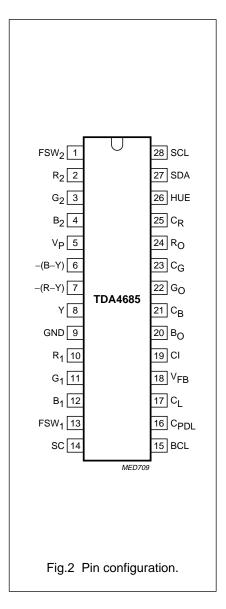

### **PINNING**

| SYMBOL           | PIN | DESCRIPTION                                                 |

|------------------|-----|-------------------------------------------------------------|

| FSW <sub>2</sub> | 1   | fast switch 2 input                                         |

| R <sub>2</sub>   | 2   | red input 2                                                 |

| G <sub>2</sub>   | 3   | green input 2                                               |

| B <sub>2</sub>   | 4   | blue input 2                                                |

| V <sub>P</sub>   | 5   | supply voltage                                              |

| -(B-Y)           | 6   | colour difference input –(B–Y)                              |

| -(R-Y)           | 7   | colour difference input –(R–Y)                              |

| Υ                | 8   | luminance input                                             |

| GND              | 9   | ground                                                      |

| R <sub>1</sub>   | 10  | red input 1                                                 |

| G <sub>1</sub>   | 11  | green input 1                                               |

| B <sub>1</sub>   | 12  | blue input 1                                                |

| FSW <sub>1</sub> | 13  | fast switch 1 input                                         |

| SC               | 14  | sandcastle pulse input                                      |

| BCL              | 15  | average beam current limiting input                         |

| C <sub>PDL</sub> | 16  | storage capacitor for peak drive limiting                   |

| C <sub>L</sub>   | 17  | storage capacitor for leakage current                       |

| V <sub>FB</sub>  | 18  | vertical flyback pulse input                                |

| CI               | 19  | cut-off measurement input                                   |

| B <sub>O</sub>   | 20  | blue output                                                 |

| C <sub>B</sub>   | 21  | blue cut-off storage capacitor                              |

| G <sub>O</sub>   | 22  | green output                                                |

| C <sub>G</sub>   | 23  | green cut-off storage capacitor                             |

| Ro               | 24  | red output                                                  |

| C <sub>R</sub>   | 25  | red cut-off storage capacitor                               |

| HUE              | 26  | hue control output                                          |

| SDA              | 27  | I <sup>2</sup> C-bus serial data input / acknowledge output |

| SCL              | 28  | I <sup>2</sup> C-bus serial clock input                     |

### Video processor with automatic cut-off control

TDA4685

#### I<sup>2</sup>C-BUS CONTROL

The I<sup>2</sup>C-bus transmitter provides the data bytes to select and adjust the following functions and parameters:

- · brightness adjust

- · saturation adjust

- · contrast adjust

- DC output e. g. for hue control

- · RGB gain adjust

- peak drive limiting level adjust

- selects either 3-level or 2-level (5 V) sandcastle pulse

- enables cut-off control / enables output clamping

- selects either PAL/SECAM or NTSC matrix

- enables/disables synchronization of the execution of I<sup>2</sup>C-bus commands with the vertical blanking interval

- enables Y-CD, RGB1 or RGB2 input.

### I<sup>2</sup>C-BUS TRANSMITTER AND DATA TRANSFER

#### I<sup>2</sup>C-bus specification

The I<sup>2</sup>C-bus is a bi-directional, two-wire, serial data bus for intercommunication between ICs in an equipment. The microcontroller transmits data to the I<sup>2</sup>C-bus receiver in the TDA4685 over the serial data line SDA (pin 27) synchronized by the serial clock line SCL (pin 28). Both lines are normally connected to a positive voltage supply through pull-up resistors. Data is transferred when the SCL line is LOW. When SCL is HIGH the serial data line SDA must be stable. A HIGH-to-LOW transition of the SDA line when SCL is HIGH is defined as a start bit. A LOW-to-HIGH transition of the SDA line when SCL is HIGH is defined as a stop bit. Each transmission must start with a start bit and end with a stop bit. The bus is busy after a start bit and is only free again after a stop bit has been transmitted.

#### I2C-bus receiver

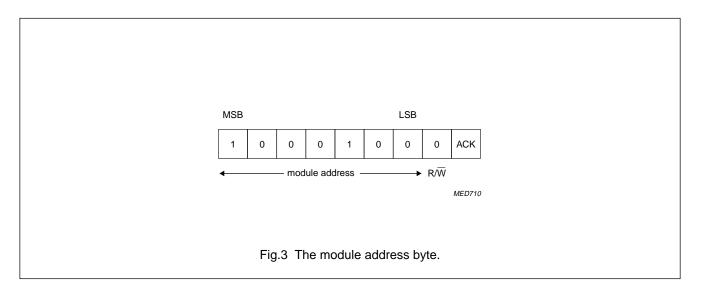

(microcontroller write mode) Each transmission to the  $I^2C$ -bus receiver consists of at least three bytes following the start bit. Each byte is acknowledged by an acknowledge bit immediately following each byte. The first byte is the Module ADdress (MAD) byte, also called slave address byte. This includes the module address,  $1000100_2$  for the TDA4685. The TDA4685 is a slave receiver ( $R/\overline{W} = 0$ ), therefore the module address byte is  $10001000_2$  (88 Hex), see Fig.3.

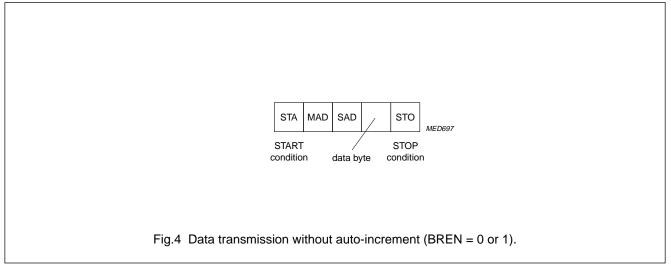

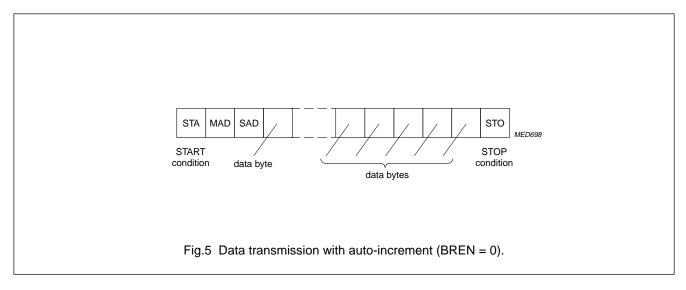

The length of a data transmission is unrestricted, but the module address and the correct sub-address must be transmitted before the data byte(s). The order of data transmission is shown in Fig.4 and Fig.5. Without auto-increment (BREN = 0 or 1) the Module ADdress (MAD) byte is followed by a Sub-ADdress (SAD) byte and one data byte only (Fig.4).

### Video processor with automatic cut-off control

**TDA4685**

### Video processor with automatic cut-off control

**TDA4685**

#### **Auto-increment**

The auto-increment format enables quick slave receiver initialization by one transmission, when the I<sup>2</sup>C-bus control bit BREN = 0 (see control register bits of Table 1). If BREN = 1 auto-increment is not possible. If the auto-increment format is selected, the MAD byte is followed by an SAD byte and by the data bytes of consecutive sub-addresses (Fig.5).

All sub-addresses from 00 to 0F are automatically incremented, the sub-address counter wraps round from 0F to 00. Reserved sub-addresses 07, 08, 09, 0B, 0E and 0F are treated as legal but have no effect. Sub-addresses outside the range 00 and 0F are not acknowledged by the device. The sub-addresses are stored in the TDA4685 to address the following parameters and functions, see Table 1:

- · brightness adjust

- saturation adjust

- · contrast adjust

- · hue control voltage

- RGB gain adjust

- · peak drive limiting adjust

- control register functions.

The data bytes (D7-D0 of Table 1) provide the data of the parameters and functions for video processing.

#### Control register 1

NMEN (NTSC-Matrix ENable):

0 = PAL/SECAM matrix

1 = NTSC matrix.

BREN (Buffer Register ENable):

0 = new data is executed as soon as it is received

1 = data is stored in buffer registers and is transferred to the data registers during the next vertical blanking interval.

The I<sup>2</sup>C-bus receiver does not accept any new data until this data is transferred into the data registers.

SC5 (SandCastle 5 V):

0 = 3-level sandcastle pulse

1 = 2-level (5 V) sandcastle pulse.

#### Control register 2

FSON2 - Fast Switch 2 ON FSDIS2 - Fast Switch 2 DISable FSON1 - Fast Switch 1 ON FSDIS1 - Fast Switch 1 DISable The RGB input signals are selected by FSON2 and FSON1 or FSW<sub>2</sub> and FSW<sub>1</sub>:

- FSON2 has priority over FSON1;

- FSW<sub>2</sub> has priority over FSW<sub>1</sub>;

- FSDIS1 and FSDIS2 disable FSW<sub>1</sub> and FSW<sub>2</sub> (see Table 2).

BCOF - Black level Control OFf:

0 = automatic cut-off control enabled

1 = automatic cut-off control disabled; RGB outputs are clamped to fixed DC levels.

When the supply voltage has dropped below approximately  $6.0\ V$  (usually occurs when the TV receiver is switched on or the supply voltage is interrupted) all data and function bits are set to  $01_{\text{Hex.}}$

### Video processor with automatic cut-off control

**TDA4685**

**Table 1** Sub-address (SAD) and data bytes<sup>(1)</sup>.

| FUNCTION            | SAD   | MSB |   |      | DATA | BYTE   |       |        | LSB   |

|---------------------|-------|-----|---|------|------|--------|-------|--------|-------|

| FUNCTION            | (HED) | 7   | 6 | 5    | 4    | 3      | 2     | 1      | 0     |

| Brightness          | 00    | 0   | 0 | A05  | A04  | A03    | A02   | A01    | A00   |

| Saturation          | 01    | 0   | 0 | A15  | A14  | A13    | A12   | A11    | A10   |

| Contrast            | 02    | 0   | 0 | A25  | A24  | A23    | A22   | A21    | A20   |

| Hue control voltage | 03    | 0   | 0 | A35  | A34  | A33    | A32   | A31    | A30   |

| Red gain            | 04    | 0   | 0 | A45  | A44  | A43    | A42   | A41    | A40   |

| Green gain          | 05    | 0   | 0 | A55  | A54  | A53    | A52   | A51    | A50   |

| Blue gain           | 06    | 0   | 0 | A65  | A64  | A63    | A62   | A61    | A60   |

| Reserved            | 07    | 0   | 0 | х    | х    | х      | Х     | х      | х     |

| Reserved            | 08    | 0   | 0 | х    | х    | х      | х     | х      | х     |

| Reserved            | 09    | 0   | 0 | х    | х    | х      | х     | х      | х     |

| Peak drive limit    | 0A    | 0   | 0 | AA5  | AA4  | AA3    | AA2   | AA1    | AA0   |

| Reserved            | 0B    | Х   | х | х    | х    | х      | Х     | х      | х     |

| Control register 1  | 0C    | SC5 | х | BREN | х    | NMEN   | Х     | х      | х     |

| Control register 2  | 0D    | Х   | х | х    | BCOF | FSDIS2 | FSON2 | FSDIS1 | FSON1 |

| Reserved            | 0E    | х   | х | х    | х    | х      | х     | х      | х     |

| Reserved            | 0F    | х   | х | х    | х    | х      | х     | х      | х     |

### Note to Table 1

1. X is 'don't care', but for software compatibility with other or future video ICs it is recommended to set all 'X' to '0'.

**Table 2** Signal input selection by the fast source switches<sup>(1)</sup>.

| l <sup>2</sup> C | -BUS CONT | ROL BITS |        | ANALOG SW                   | ITCH SIGNALS                 | INF              | TED  |      |

|------------------|-----------|----------|--------|-----------------------------|------------------------------|------------------|------|------|

| FSON2            | FSDIS2    | FSON1    | FSDIS1 | FSW <sub>2</sub><br>(pin 1) | FSW <sub>1</sub><br>(pin 13) | RGB <sub>2</sub> | RGB₁ | Y/CD |

| L                | L         | L        | L      | L                           | L                            |                  |      | ON   |

|                  |           |          |        | L                           | Н                            |                  | ON   |      |

|                  |           |          |        | Н                           | X                            | ON               |      |      |

| L                | L         | L        | Н      | L                           | X                            |                  |      | ON   |

|                  |           |          |        | Н                           | X                            | ON               |      |      |

| L                | L         | Н        | Х      | L                           | Х                            |                  | ON   |      |

|                  |           |          |        | Н                           | X                            | ON               |      |      |

| L                | Н         | L        | L      | Х                           | L                            |                  |      | ON   |

|                  |           |          |        | X                           | Н                            |                  | ON   |      |

| L                | Н         | L        | Н      | X                           | Х                            |                  |      | ON   |

| L                | Н         | Н        | Х      | X                           | Х                            |                  | ON   |      |

| Н                | Х         | Х        | X      | Х                           | Х                            | ON               |      |      |

### Note to Table 2

1. Where L is a logic LOW (< 0.4 V), H is a logic HIGH (> 0.9 V), X is 'don't care', and ON is the selected input signal.

### Video processor with automatic cut-off control

TDA4685

### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC134).

| SYMBOL           | PARAMETER                                                | MIN. | MAX.                 | UNIT |

|------------------|----------------------------------------------------------|------|----------------------|------|

| V <sub>P</sub>   | supply voltage (pin 5)                                   | _    | 8.8                  | V    |

| VI               | input voltage (pins 1 to 8, 10 to 13, 16, 21, 23 and 25) | -0.1 | V <sub>P</sub>       | V    |

|                  | input voltage (pins 15, 18 and 19)                       | -0.7 | V <sub>P</sub> + 0.7 | V    |

|                  | input voltage (pins 27 and 28)                           | -0.1 | 8.8                  | V    |

| V <sub>14</sub>  | sandcastle pulse voltage                                 | -0.7 | V <sub>P</sub> +5.8  | V    |

| I <sub>AV</sub>  | average current (pins 20, 22 and 24)                     | -10  | 4                    | mA   |

| I <sub>M</sub>   | peak current (pins 20, 22 and 24)                        | -20  | 4                    | mA   |

| I <sub>26</sub>  | output current                                           | -8   | 0.6                  | mA   |

| T <sub>stg</sub> | storage temperature                                      | -20  | +150                 | °C   |

| T <sub>amb</sub> | operating ambient temperature                            | 0    | +70                  | °C   |

| P <sub>tot</sub> | total power dissipation                                  | _    | 1.2                  | W    |

TDA4685

### Video processor with automatic cut-off control

TDA4685

#### **CHARACTERISTICS**

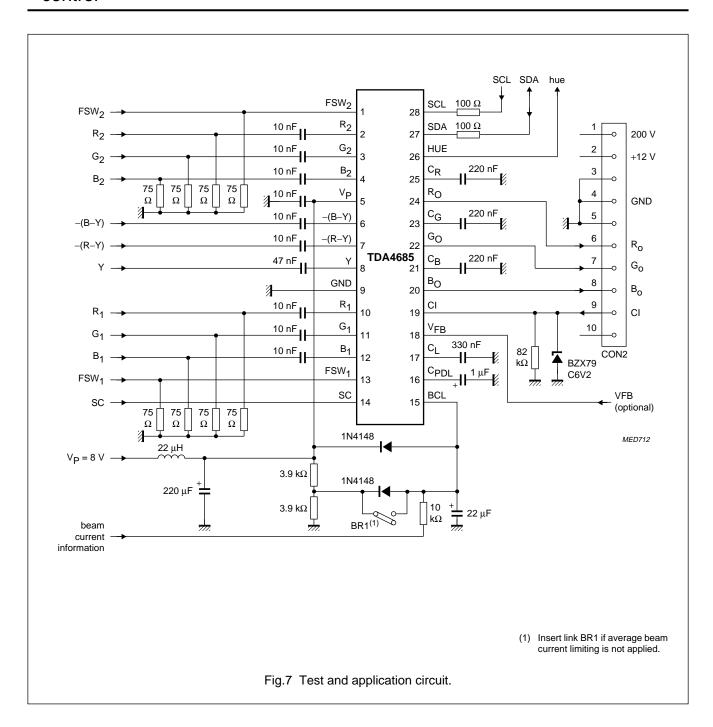

All voltages are measured in test circuit of Fig.7 with respect to GND (pin 9);  $V_P = 8.0 \text{ V}$ ;  $T_{amb} = +25 ^{\circ}\text{C}$ :

- at nominal signal amplitudes (black-to-white) at output pins 24, 22 and 20,

- at nominal settings of brightness, contrast, saturation and white level control,

- without beam current or peak drive limiting; unless otherwise specified.

| SYMBOL                              | PARAMETER                                                               | CONDITIONS              | MIN. | TYP. | MAX. | UNIT     |

|-------------------------------------|-------------------------------------------------------------------------|-------------------------|------|------|------|----------|

| V <sub>P</sub>                      | supply voltage (pin 5)                                                  |                         | 7.2  | 8.0  | 8.8  | V        |

| l <sub>P</sub>                      | supply current (pin 5)                                                  |                         | _    | 60   | _    | mA       |

| Colour dif                          | ference inputs                                                          |                         |      |      | •    |          |

| V <sub>6(p-p)</sub>                 | -(B-Y) input (peak-to-peak value)                                       | notes 1 and 2           | -    | 1.33 | _    | V        |

| V <sub>7(p-p)</sub>                 | -(R-Y) input (peak-to-peak value)                                       | notes 1 and 2           | _    | 1.05 | _    | V        |

| V <sub>6,7</sub>                    | internal DC bias voltage                                                | at black level clamping | -    | 4.1  | _    | V        |

| I <sub>6,7</sub>                    | input current                                                           | during line scan        | -    | _    | ±0.1 | μΑ       |

|                                     |                                                                         | at black level clamping | ±100 | _    | _    | μΑ       |

| R <sub>6,7</sub>                    | input resistance                                                        |                         | 10   | _    | _    | ΜΩ       |

| Luminanc                            | e/sync (VBS)                                                            |                         |      |      |      |          |

| $V_{i(p-p)}$                        | luminance input at pin 8 (peak-to-peak value)                           | note 2                  | _    | 0.45 | _    | V        |

| V <sub>8</sub>                      | internal DC bias voltage                                                | at black level clamping | _    | 4.1  | _    | V        |

| I <sub>8</sub>                      | input current                                                           | during line scan        | -    | _    | ±0.1 | μΑ       |

|                                     |                                                                         | at black level clamping | ±100 | _    | _    | μΑ       |

| R <sub>8</sub>                      | input resistance                                                        |                         | 10   | _    | _    | ΜΩ       |

| R <sub>1</sub> ,G <sub>1</sub> and  | B <sub>1</sub> inputs                                                   | ,                       |      |      | •    | •        |

| $V_{i(p-p)}$                        | black-to-white input signals at pins 10, 11 and 12 (peak-to-peak value) | note 2                  | -    | 0.7  | _    | V        |

| V <sub>10/11/12</sub>               | internal DC bias voltage                                                | at black level clamping | _    | 5.7  | _    | V        |

| I <sub>10/11/12</sub>               | input current                                                           | during line scan        | _    | _    | ±0.1 | μΑ       |

|                                     |                                                                         | at black level clamping | ±100 | _    | _    | μΑ       |

| R <sub>10/11/12</sub>               | input resistance                                                        |                         | 10   | _    | _    | ΜΩ       |

| R <sub>2</sub> , G <sub>2</sub> and | I B <sub>2</sub> inputs                                                 | ,                       |      |      | •    | •        |

| $V_{i(p-p)}$                        | black-to-white input signals at pins 2, 3 and 4 (peak-to-peak value)    | note 2                  | -    | 0.7  | _    | V        |

| V <sub>2/3/4</sub>                  | internal DC bias voltage                                                | at black level clamping | _    | 5.7  | _    | V        |

| I <sub>2/3/4</sub>                  | input current                                                           | during line scan        | _    | _    | ±0.1 | μΑ       |

|                                     |                                                                         | at black level clamping | ±100 | _    | _    | μΑ       |

| R <sub>2/3/4</sub>                  | input resistance                                                        |                         | 10   | _    | _    | ΜΩ       |

| PAL/SECA                            | AM and NTSC matrix (note 3)                                             |                         |      |      |      | <u> </u> |

|                                     | PAL/SECAM matrix                                                        | control bit NMEN = 0    |      |      |      |          |

|                                     | NTSC matrix                                                             | control bit NMEN = 1    |      |      |      | 1        |

### Video processor with automatic cut-off control

TDA4685

| SYMBOL                                                  | PARAMETER                                                                                                                                                                                                                             | CONDITIONS                                                                | MIN. | TYP. | MAX. | UNI |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------|------|------|-----|

| Fast signa                                              | al switch FSW <sub>1</sub> to select Y, CD or R <sub>1</sub> , G <sub>1</sub>                                                                                                                                                         | , B <sub>1</sub> inputs                                                   | '    | 1    |      | !   |

| control bits                                            | s FSDIS1, FSON1 (see Table 2)                                                                                                                                                                                                         |                                                                           |      |      |      |     |

| V <sub>13</sub>                                         | voltage to select Y and CD                                                                                                                                                                                                            |                                                                           | _    | _    | 0.4  | V   |

|                                                         | voltage range to select R <sub>1</sub> , G <sub>1</sub> , B <sub>1</sub>                                                                                                                                                              |                                                                           | 0.9  | _    | 5.0  | V   |

| R <sub>13</sub>                                         | internal resistance to ground                                                                                                                                                                                                         |                                                                           | _    | 4.0  | _    | kΩ  |

| Δt                                                      | difference between transit times for signal switching and signal insertion                                                                                                                                                            |                                                                           | _    | _    | 10   | ns  |

| _                                                       | al switch FSW <sub>2</sub> to select Y, CD / R <sub>1</sub> , G <sub>1</sub> , s<br>FSDIS2, FSON2 (see Table 2)                                                                                                                       | B <sub>1</sub> or R <sub>2</sub> , G <sub>2</sub> , B <sub>2</sub> inputs |      |      |      |     |

| $V_1$                                                   | voltage to select Y, CD/R <sub>1</sub> , G <sub>1</sub> , B <sub>1</sub>                                                                                                                                                              |                                                                           | _    | _    | 0.4  | V   |

|                                                         | voltage range to select R <sub>2</sub> , G <sub>2</sub> , B <sub>2</sub>                                                                                                                                                              |                                                                           | 0.9  | _    | 5.0  | V   |

| R <sub>1</sub>                                          | internal resistance to ground                                                                                                                                                                                                         |                                                                           | _    | 4.0  | _    | kΩ  |

| Δt                                                      | difference between transit times for signal switching and signal insertion                                                                                                                                                            |                                                                           | _    | _    | 10   | ns  |

| data byte t                                             | saturation below maximum                                                                                                                                                                                                              | at 23 <sub>Hex</sub>                                                      |      | 5    | _    | dB  |

|                                                         | 23 <sub>Hex</sub> for nominal saturation<br>00 <sub>Hex</sub> for minimum saturation                                                                                                                                                  |                                                                           |      |      |      |     |

| d <sub>s</sub>                                          | saturation below maximum                                                                                                                                                                                                              |                                                                           |      |      | _    | _   |

|                                                         |                                                                                                                                                                                                                                       | at $00_{Hex}$ ; f = 100 kHz                                               | _    | 50   | _    | dB  |

| sub-addres<br>data byte 3<br>data byte 2<br>data byte 0 | ernal RGB signals under I <sup>2</sup> C-bus control, ss 02 <sub>Hex</sub> (bit resolution 1.5% of maximum BF <sub>Hex</sub> for maximum contrast 22 <sub>Hex</sub> for nominal contrast 00 <sub>Hex</sub> for minimum contrast       | contrast);                                                                |      |      |      |     |

| d <sub>c</sub>                                          | contrast below maximum                                                                                                                                                                                                                | at 22 <sub>Hex</sub>                                                      | _    | 5    | _    | dB  |

|                                                         |                                                                                                                                                                                                                                       | at 00 <sub>Hex</sub>                                                      | _    | 22   | _    | dB  |

| Brightnes                                               | s adjust                                                                                                                                                                                                                              |                                                                           |      |      |      |     |

| sub-addres<br>data byte 3<br>data byte 2                | ernal RGB signals under I <sup>2</sup> C-bus control, ss 00 <sub>Hex</sub> (bit resolution 1.5% of maximum BF <sub>Hex</sub> for maximum brightness 26 <sub>Hex</sub> for nominal brightness 00 <sub>Hex</sub> for minimum brightness | brightness);                                                              |      |      |      |     |

| d <sub>br</sub>                                         | black level shift of nominal signal                                                                                                                                                                                                   | at 3F <sub>Hex</sub>                                                      | _    | 30   | _    | %   |

|                                                         | amplitude referred to cut-off measurement level                                                                                                                                                                                       | at 00 <sub>Hex</sub>                                                      | _    | -50  | _    | %   |

|                                                         |                                                                                                                                                                                                                                       |                                                                           |      |      |      |     |

### Video processor with automatic cut-off control

TDA4685

| SYMBOL                     | PARAMETER                                                                                                                                                                                          | CONDITIONS                   | MIN. | TYP. | MAX.                | UNIT |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|------|---------------------|------|

| White pot                  | entiometers, under I <sup>2</sup> C-bus control,                                                                                                                                                   | •                            | •    |      |                     |      |

| data byte 3<br>data byte 1 | sses 04 <sub>Hex</sub> (red), 05 <sub>Hex</sub> (green) and 06 <sub>Hex</sub> (b<br>BF <sub>Hex</sub> for maximum gain<br>19 <sub>Hex</sub> for nominal gain<br>00 <sub>Hex</sub> for minimum gain | olue); note 4.               |      |      |                     |      |

| $\Delta G_v$               | relative to nominal gain:                                                                                                                                                                          |                              |      |      |                     |      |

|                            | increase of gain                                                                                                                                                                                   | at 3F <sub>Hex</sub>         | _    | 50   | _                   | %    |

|                            | decrease of gain                                                                                                                                                                                   | at 00 <sub>Hex</sub>         | _    | 50   | _                   | %    |

| •                          | uts pins 24, 22 and 20 oing output signals; peak drive limiter set =                                                                                                                               | 3F <sub>Hex</sub> ); note 5. |      |      |                     |      |

| $V_{o(b-w)}$               | nominal output signal amplitudes (black-to-white value)                                                                                                                                            |                              | _    | 2    | _                   | V    |

|                            | maximum output signal amplitudes (black-to-white value)                                                                                                                                            |                              | 3.0  | _    | _                   | V    |

| $\Delta V_{o}$             | spread between RGB output signals                                                                                                                                                                  |                              |      | _    | 10                  | %    |

| $V_{o}$                    | minimum output voltages                                                                                                                                                                            |                              |      | _    | 0.8                 | V    |

|                            | maximum output voltages                                                                                                                                                                            |                              | 6.8  | _    | _                   | V    |

| V <sub>24,22,20</sub>      | voltage of cut-off measurement line = voltage during ultra-black                                                                                                                                   | BCOF = 1 (output clamping)   | 2.3  | 2.5  | 2.7                 | V    |

| I <sub>int</sub>           | internal current sources                                                                                                                                                                           |                              | _    | 5.0  | _                   | mA   |

| R <sub>o</sub>             | output resistance                                                                                                                                                                                  |                              | _    | 20   | _                   | Ω    |

| Frequency                  | y response                                                                                                                                                                                         |                              |      |      |                     | •    |

| d                          | frequency response of Y path (from pin 8 to pins 24, 22, 20)                                                                                                                                       | f = 10 MHz                   | _    | _    | 3                   | dB   |

|                            | frequency response of CD path (from pins 7 to 24 and 6 to 20)                                                                                                                                      | f = 8 MHz                    | _    | _    | 3                   | dB   |

|                            | frequency response of RGB <sub>1</sub> path (from pins 10 to 24, 11 to 22 and 12 to 20)                                                                                                            | f = 10 MHz                   | _    | _    | 3                   | dB   |

|                            | frequency response of RGB <sub>2</sub> path (from pins 2 to 24, 3 to 22 and 4 to 20)                                                                                                               | f = 10 MHz                   | _    | _    | 3                   | dB   |

| Sandcastl                  | e pulse detector (control bit SC5 = 0)                                                                                                                                                             |                              |      |      |                     |      |

| three level                | ; notes 6 and 7                                                                                                                                                                                    |                              |      |      |                     |      |

| V <sub>14</sub>            | required voltage range                                                                                                                                                                             |                              |      |      |                     |      |

|                            | for H and V blanking pulses                                                                                                                                                                        |                              | 2.0  | 2.5  | 3.0                 | V    |

|                            | for H pulses (line count)                                                                                                                                                                          |                              | 4.0  | 4.5  | 5.0                 | V    |

|                            | for burst key pulses (clamping)                                                                                                                                                                    |                              | 7.6  | _    | V <sub>P</sub> +5.8 | V    |

### Video processor with automatic cut-off control

TDA4685

| SYMBOL                | PARAMETER                                                  | CONDITIONS                     | MIN. | TYP. | MAX.                | UNIT |

|-----------------------|------------------------------------------------------------|--------------------------------|------|------|---------------------|------|

|                       | e pulse detector (control bit SC5 = 1) notes 6 and 7       |                                | ,    |      |                     |      |

| V <sub>14</sub>       | required voltage range                                     |                                |      |      |                     |      |

|                       | for H and V blanking pulses                                |                                | 2.0  | 2.5  | 3.0                 | V    |

|                       | for burst key pulses                                       |                                | 4.0  | 4.5  | V <sub>P</sub> +5.8 | V    |

| Sandcastl             | e pulse detector                                           |                                |      | 1    | <b>-</b>            |      |

| I <sub>14</sub>       | output current                                             | V <sub>14</sub> = 0 V          | _    | _    | -100                | μΑ   |

| t <sub>d</sub>        | leading edge delay of the clamping pulse                   |                                | _    | 1.5  | _                   | μs   |

| VFB (note             | 7)                                                         |                                |      | 1    |                     |      |

| V <sub>18</sub>       | vertical flyback pulse                                     | for LOW                        |      | _    | 2.5                 | V    |

| .0                    |                                                            | for HIGH                       | 4.5  | _    | _                   | V    |

|                       | internal voltage                                           | pin 18 open-circuit;<br>note 8 | _    | 5.0  | _                   | V    |

| I <sub>18</sub>       | input current                                              |                                | _    | _    | 5                   | μΑ   |

| Average b             | peam current limiting (note 9)                             |                                | •    | ,    | •                   |      |

| V <sub>c(15)</sub>    | contrast reduction starting voltage                        |                                | _    | 4.0  | _                   | V    |

| $\Delta V_{c(15)}$    | voltage difference for full contrast reduction             |                                | _    | -2.0 | _                   | V    |

| V <sub>br(15)</sub>   | brightness reduction starting voltage                      |                                | _    | 2.5  | _                   | V    |

| $\Delta V_{br(15)}$   | voltage difference for full brightness reduction           |                                | _    | -1.6 | _                   | V    |

| Peak drive            | e limiting voltage (note 10)                               |                                | '    | •    |                     | •    |

| internal pe           | ak drive limiting level (V <sub>pdl</sub> ) acts on RGB ou | tputs                          |      |      |                     |      |

|                       | ntrol, sub-address 0A <sub>Hex</sub>                       |                                |      |      |                     |      |

| V <sub>20/22/24</sub> | level for minimum RGB outputs                              | at byte 00 <sub>Hex</sub>      | _    | _    | 3.0                 | V    |

|                       | level for maximum RGB outputs                              | at byte 3F <sub>Hex</sub>      | 7.0  | _    | _                   | V    |

| I <sub>16</sub>       | charge current                                             |                                | _    | -1   | _                   | μΑ   |

|                       | discharge current                                          | during peak white              | _    | 5    | _                   | mA   |

| V <sub>16</sub>       | internal voltage limitation                                |                                | 4.5  | _    | _                   | V    |

| V <sub>c(16)</sub>    | contrast reduction starting voltage                        |                                | _    | 4.0  | _                   | V    |

| ΔV <sub>c(16)</sub>   | voltage difference for full contrast reduction             |                                | -    | -2.0 | _                   | V    |

| V <sub>br(16)</sub>   | brightness reduction starting voltage                      |                                | _    | 2.5  | _                   | V    |

| $\Delta V_{br(16)}$   | voltage difference for full brightness reduction           |                                | -    | -1.6 | _                   | V    |

### Video processor with automatic cut-off control

TDA4685

| SYMBOL                  | PARAMETER                                                                                                                                                             | CONDITIONS                           | MIN. | TYP.                   | MAX.                 | UNIT |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------|------------------------|----------------------|------|

| Automation see Fig.9    | cut-off control (notes 7, 11, 12 and 13)                                                                                                                              |                                      |      | 1                      | 1                    | '    |

| V <sub>19</sub>         | external voltage                                                                                                                                                      |                                      | _    | _                      | V <sub>P</sub> - 1.4 | V    |

| I <sub>19</sub>         | output current                                                                                                                                                        |                                      | _    | _                      | -60                  | μΑ   |

|                         | input current                                                                                                                                                         |                                      | 150  | _                      | _                    | μΑ   |

|                         | additional input current                                                                                                                                              | switch-on delay 1                    | _    | 0.5                    | _                    | mA   |

| V <sub>24,22,20</sub>   | monitor pulse amplitude (under I <sup>2</sup> C-bus control, sub-address 0A <sub>Hex</sub> )                                                                          | switch-on delay 1;<br>note 12        | _    | V <sub>pdl</sub> – 1.0 | _                    | V    |

| V <sub>19</sub>         | voltage threshold for picture tube cathode warm-up                                                                                                                    | switch-on delay 1                    | _    | 4.5                    | _                    | V    |

|                         | internally controlled voltage (V <sub>REF</sub> )                                                                                                                     | during leakage<br>measurement period | -    | 2.7                    | _                    | V    |

| $\Delta V_{19}$         | voltage difference between V <sub>MEAS</sub> (cut-off measurement voltage) and V <sub>REF</sub>                                                                       |                                      | _    | 1.0                    | _                    | V    |

| Cut-off sto             | orage                                                                                                                                                                 |                                      | '    |                        |                      | •    |

| I <sub>21/23/25</sub>   | charge and discharge currents                                                                                                                                         | during cut-off measurement lines     | -    | ±0.3                   | _                    | mA   |

|                         | current                                                                                                                                                               | outside measurement                  | _    | _                      | ±0.1                 | μΑ   |

| Leakage s               | storage                                                                                                                                                               |                                      | •    |                        |                      | •    |

| I <sub>17</sub>         | charge and discharge currents                                                                                                                                         | during leakage<br>measurement period | -    | ±0.4                   | _                    | mA   |

|                         | current                                                                                                                                                               | outside measurement                  | _    | _                      | ±0.1                 | μА   |

| V <sub>17</sub>         | threshold voltage for reset to switch-on state                                                                                                                        |                                      | -    | 2.5                    | -                    | V    |

| Hue contr               | <b>ol</b> (note 14)                                                                                                                                                   | -                                    | !    | 1                      | '                    | !    |

| data byte 3 data byte 2 | bus control, sub-address 03 <sub>Hex</sub><br>BF <sub>Hex</sub> for maximum voltage<br>20 <sub>Hex</sub> for nominal voltage<br>00 <sub>Hex</sub> for minimum voltage |                                      |      |                        |                      |      |

| V <sub>26</sub>         | output voltage                                                                                                                                                        | at byte 3F <sub>Hex</sub>            | 4.8  | _                      | _                    | V    |

|                         |                                                                                                                                                                       | at byte 20 <sub>Hex</sub>            | -    | 3.0                    | _                    | V    |

|                         |                                                                                                                                                                       | at byte 00 <sub>Hex</sub>            | _    | _                      | 1.2                  | V    |

| I <sub>int</sub>        | current of the internal current source at pin 26                                                                                                                      |                                      | 500  | _                      | _                    | μΑ   |

### Video processor with automatic cut-off control

**TDA4685**

| SYMBOL                  | PARAMETER                             | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|-------------------------|---------------------------------------|------------|------|------|------|------|

| I <sup>2</sup> C-bus re | ceiver clock SCL (pin 28)             | ,          |      |      |      |      |

| f <sub>SCL</sub>        | input frequency range                 |            | 0    | _    | 100  | kHz  |

| V <sub>IL</sub>         | LOW level input voltage               |            | _    | _    | 1.5  | V    |

| V <sub>IH</sub>         | HIGH level input voltage              |            | 3.0  | _    | 6.0  | V    |

| I <sub>IL</sub>         | LOW level input current               |            | _    | _    | -10  | μΑ   |

| I <sub>IH</sub>         | HIGH level input current              |            | _    | _    | 10   | μΑ   |

| t <sub>d</sub>          | pulse delay time LOW                  |            | 4.7  | _    | _    | μs   |

|                         | pulse delay time HIGH                 |            | 4.0  | _    | _    | μs   |

| t <sub>r</sub>          | rise time                             |            | _    | _    | 1.0  | μs   |

| t <sub>f</sub>          | fall time                             |            | _    | _    | 0.3  | μs   |

| I <sup>2</sup> C-bus re | ceiver data input/output SDA (pin 27) | ,          |      |      | •    | •    |

| V <sub>IL</sub>         | LOW level input voltage               |            | _    | _    | 1.5  | V    |

| V <sub>IH</sub>         | HIGH level input voltage              |            | 3.0  | _    | 6.0  | V    |

| I <sub>IL</sub>         | LOW level input current               |            | _    | _    | -10  | μΑ   |

| I <sub>IH</sub>         | HIGH level input current              |            | _    | _    | 10   | μΑ   |

| I <sub>OL</sub>         | LOW level output current              |            | 3.0  | _    | _    | mA   |

| t <sub>r</sub>          | rise time                             |            | _    | _    | 1.0  | μs   |

| t <sub>f</sub>          | fall time                             |            | _    | _    | 0.3  | μs   |

| t <sub>SU;DAT</sub>     | data set-up time                      |            | 0.25 | _    | _    | μs   |

#### Notes to the characteristics

- 1. The values of the -(B-Y) and -(R-Y) colour difference input signals are for a 75% colour-bar signal.

- 2. The pins are capacitively coupled to a low ohmic source, with a recommended maximum output impedance of  $600 \Omega$ .

- 3. PAL/SECAM signals are matrixed by the equation:  $V_{G-Y} = -0.51V_{R-Y} 0.19V_{B-Y}$  NTSC signals are matrixed by the equations (hue phase shift of -5 degrees):  $V_{R-Y^*} = 1.57V_{R-Y} 0.41V_{B-Y}$ ;  $V_{G-Y}^* = -0.43V_{R-Y} 0.11V_{B-Y}$ ;  $V_{B-Y}^* = V_{B-Y}$  In the matrix equations:  $V_{R-Y}$  and  $V_{B-Y}$  are conventional PAL demodulation axes and amplitudes at the output of the NTSC demodulator.  $V_{G-Y}^*$ ,  $V_{R-Y}^*$  and  $V_{B-Y}^*$  are the NTSC-modified colour difference signals; this is equivalent to the following demodulator axes and amplification factors:

|                             | NTSC | PAL  |

|-----------------------------|------|------|

| (B–Y)* demodulator axis     | 0°   | 0°   |

| (R-Y)* demodulator axis     | 115° | 90°  |

| (R-Y)* amplification factor | 1.97 | 1.14 |

| (B–Y)* amplification factor | 2.03 | 2.03 |

$$V_{G-Y}^* = -0.27V_{R-Y}^* - 0.22V_{B-Y}^*$$

.

- 4. The white potentiometers affect the amplitudes of the RGB output signals.

- 5. The RGB outputs at pins 24, 22 and 20 are emitter followers with current sources.

### Video processor with automatic cut-off control

**TDA4685**

- 6. Sandcastle pulses are compared with internal threshold voltages independent of V<sub>P</sub>. The threshold voltages separate the components of the sandcastle pulse. The particular component is generated when the voltage on pin 14 exceeds the defined internal threshold voltage. The internal threshold voltages (control bit SC5 = 0) are:

- 1.5 V for horizontal and vertical blanking pulses (H and V blanking pulses),

- 3.5 V for horizontal pulses,

- 6.5 V for the burst key pulse.

The internal threshold voltages, control bit SC5 = 1, are:

- 1.5 V for horizontal and vertical blanking pulses,

- 3.5 V for the burst key pulse.

- 7. Vertical signal blanking is determined by the vertical component of the sandcastle pulse. The leakage and the RGB cut-off measurement lines are positioned in the first four complete lines after the end of the vertical component. In this case, the RGB output signals are blanked until the end of the last measurement line; see Fig 9(a). If an extra vertical flyback pulse VFB is applied to pin 18, the four measurement lines start in the first complete line after the end of the VFB pulse; see Fig 9(b). In this case, the output signals are blanked either until the end of the last measurement line or until the end of the vertical component of the sandcastle pulse, according to which occurs last.

- 8. If no VFB pulse is applied, pin 18 can be left open-circuit or connected to V<sub>P</sub>. If pin 18 is always LOW neither automatic cut-off control nor output clamping can happen.

- 9. Average beam current limiting reduces the contrast, at minimum contrast it reduces the brightness.

- 10. Peak drive limiting reduces the RGB outputs by reducing the contrast, at minimum contrast it reduces the brightness. The maximum RGB outputs are determined via the I<sup>2</sup>C-bus under sub-address 0A<sub>Hex</sub>. When an RGB output exceeds the maximum voltage, peak drive limiting is delayed by one horizontal line.

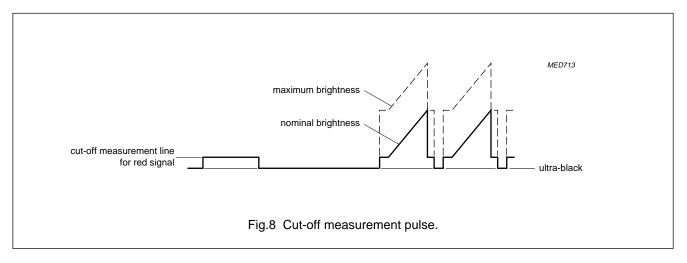

- 11. During leakage current measurement, the RGB channels are blanked to ultra-black level. During cut-off measurement one channel is set to the measurement pulse level, the other channels are blanked to ultra-black. Since the brightness adjust shifts the colour signal relative to the black level, the brightness adjust is disabled during the vertical blanking interval (see Fig.8 and Fig.9).

- 12. During picture cathode warm-up (first switch-on delay) the RGB outputs (pins 24, 22 and 20) are blanked to the ultra-black level during line scan. During the vertical blanking interval a white-level monitor pulse is fed out on the RGB outputs and the cathode currents are measured. When the voltage threshold on pin 19 is greater than 4.5 V, the monitor pulse is switched off and cut-off control is activated (second switch-on delay). As soon as cut-off control stabilizes, RGB output blanking is removed.

- 13. The cut-off measurement level range at the RGB outputs is 1 to 5 V. The recommended value is 3 V.

- 14. The hue control output at pin 26 is an emitter follower with current source.

**TDA4685**

### Video processor with automatic cut-off control

**TDA4685**

**TDA4685**

### **PACKAGE OUTLINE**

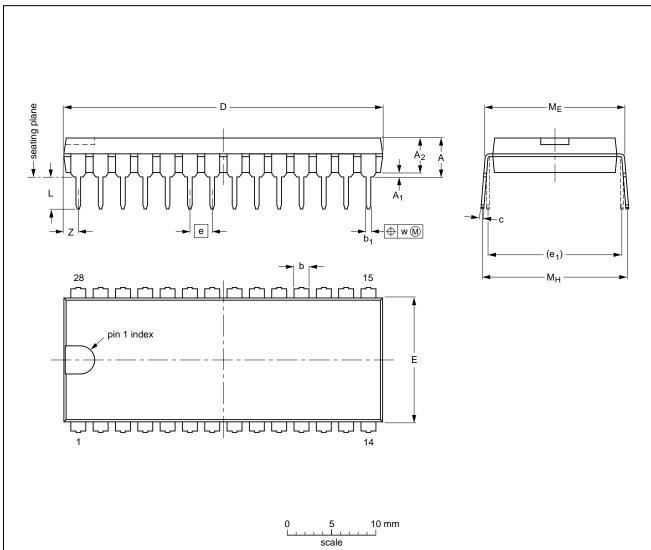

DIP28: plastic dual in-line package; 28 leads (600 mil)

SOT117-1

### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | ME             | Мн             | w    | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|----------------|----------------|------|--------------------------|

| mm     | 5.1       | 0.51                   | 4.0                    | 1.7<br>1.3     | 0.53<br>0.38   | 0.32<br>0.23   | 36.0<br>35.0     | 14.1<br>13.7     | 2.54 | 15.24          | 3.9<br>3.4   | 15.80<br>15.24 | 17.15<br>15.90 | 0.25 | 1.7                      |

| inches | 0.20      | 0.020                  | 0.16                   | 0.066<br>0.051 | 0.020<br>0.014 | 0.013<br>0.009 | 1.41<br>1.34     | 0.56<br>0.54     | 0.10 | 0.60           | 0.15<br>0.13 | 0.62<br>0.60   | 0.68<br>0.63   | 0.01 | 0.067                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUT  | OUTLINE REFERENCES |        |          |      |  |            | ISSUE DATE                      |  |

|------|--------------------|--------|----------|------|--|------------|---------------------------------|--|

| VERS | SION               | IEC    | JEDEC    | EIAJ |  | PROJECTION | ISSUE DATE                      |  |

| SOT1 | 117-1              | 051G05 | MO-015AH |      |  |            | <del>92-11-17</del><br>95-01-14 |  |

### Video processor with automatic cut-off control

TDA4685

#### **SOLDERING**

#### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "IC Package Databook" (order code 9398 652 90011).

#### Soldering by dipping or by wave

The maximum permissible temperature of the solder is 260 °C; solder at this temperature must not be in contact

with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature ( $T_{stg\ max}$ ). If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

#### Repairing soldered joints

Apply a low voltage soldering iron (less than 24 V) to the lead(s) of the package, below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300 °C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400 °C, contact may be up to 5 seconds.

#### **DEFINITIONS**

| Data sheet status         |                                                                                       |

|---------------------------|---------------------------------------------------------------------------------------|

| Objective specification   | This data sheet contains target or goal specifications for product development.       |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later. |

| Product specification     | This data sheet contains final product specifications.                                |

|                           |                                                                                       |

#### Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### **Application information**

Where application information is given, it is advisory and does not form part of the specification.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

#### PURCHASE OF PHILIPS I2C COMPONENTS

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specification defined by Philips. This specification can be ordered using the code 9398 393 40011.