BULLETIN NO. DL-S 7211581, DECEMBER 1972

## description

Each of these 16-bit active-element memories is a high-speed, monolithic, transistor-transistor-logic (TTL) array of 16 flip-flops and two write amplifiers interconnected to form a scratch-pad memory with direct-address and nondestructive read-out. These devices are interchangeable with and replace SN5481, SN7481, SN5484, and SN7484, but feature diode-clamped inputs, improved switching speeds, and lower supply current requirements.

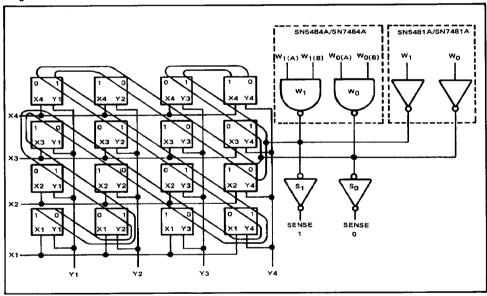

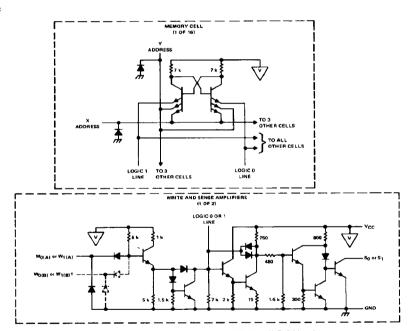

The flip-flops are arranged in a four-by-four matrix with each flip-flop representing one bit of 16 words. Four X-address lines and four Y-address lines permit the address of one bit at a time. Each flip-flop, composed of two cross-coupled three-emitter transistors, is used to store one bit. To determine if a logic 1 or logic 0 has been stored, it is necessary to know which one of the two flip-flop transistors is conducting. One emitter of each of these transistors serves as the sensing output. All 16 of the logic 1 sensing outputs are connected to the sense 1 (S<sub>1</sub>) amplifier input and all 16 of the logic 0 sensing outputs are connected to the sense 0 (So) amplifier input. The two remaining emitters of each transistor are used to complete the matrix connections necessary for the X- and Y-address lines. Address line inputs are normally held low and currents from all conducting flip-flop transistors flow out of these address lines.

To address a flip-flop both the X- and Y-address lines associated with that flip-flop are taken to a high level. Due to the matrix nature of the circuit, at least one address line of all flip-flops except the one being addressed will continue to remain at a low level and no change will occur in those flip-flops. But, in the addressed flip-flop, the current in the conducting transistor diverts from the address lines to the appropriate sense line and then to one of the sense amplifiers. Thus, either the sense 1 amplifier or the sense 0 amplifier is activated. When this occurs, the output of the activated sense amplifier drops from a high logic level to a low logic level. The memory is nondestructive as the states of the flip-flops are not disturbed during sensing. The memory is volatile and information will be lost if the supply voltage is removed.

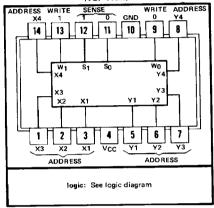

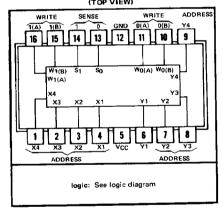

SN5481A ... J OR W PACKAGE SN7481A ... J OR N PACKAGE (TOP VIEW)

SN5484A ... J OR W PACKAGE SN7484A ... J OR N PACKAGE (TOP VIEW)

To store new information in a flip-flop, it is necessary to address it and apply a high-level voltage to the appropriate write amplifier. (The SN5484A and SN7484A have gated write-amplifier inputs). The output of the write amplifier responds by dropping to a low logic level. Since all Sense 0 lines are connected to the output of the write 0 amplifier and all sense 1 lines are connected to the output of a write amplifier

076

TEXAS INSTRUMENTS

INCORPORATED

POST OFFICE BOX 5012 . DALLAS, TEXAS 75222

## description (continued)

will cause the emitters of all flip-flop transistors connected to that amplifier to go low. In all the flip-flops except the one being addressed, this low voltage has no effect since at least one other emitter on each of the flip-flop transistors is held low by the address lines. Two possibilities exist with the flip-flop that is addressed. The flip-flop may already be in the desired state, in which case no change occurs. If the flip-flop must be changed from one state to the other, the low voltage applied to the emitter of the transistor which is not conducting turns that transistor on causing the other transistor to turn off.

Since the connection between the output of the write amplifier and the sense line is common to the input of the sense amplifier, the memory cannot be used to provide information on the state of a bit while the write amplifiers are activated.

A number of active-element memories may be paralleled to form the desired matrix size (number of words) and to form the desired word length (number of bits). All inputs and outputs are compatible with most DTL and TTL circuits. Average power dissipation is typically 225 milliwatts, and the open-collector outputs may be wire-AND connected to similar outputs. Internal circuitry of the write and sense amplifiers are operated within their linear range to improve speed. Sensing propagation delay times are typically 12 nanoseconds when operated at full fan-out and 30 picofarads of circuit capacitance. The SN5481A and SN5484A circuits are designed for operation over the full military temperature range of -55°C to 125°C; the SN7481A circuits are designed for operation from 0°C to 70°C.

## logic diagram

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted) Supply voltage, VCC (see Note 1) Input voltage . . . . . . Interemitter voltage (see Note 2) High-level output voltage 5.5 V

NOTES: 1. Voltage values, except interemitter voltage, are with respect to network ground terminal.

2. This is the voltage between two emitters of a multiple-emitter transistor. For this circuit, this rating applies to any X input in

## recommended operating conditions

|                                                           | SN548 | SN5481A, SN5484A |     |      | SN7481A, SN7484A |      |      |

|-----------------------------------------------------------|-------|------------------|-----|------|------------------|------|------|

|                                                           | MIN   | NOM              | MAX | MIN  | NOM              | MAX  | UNIT |

| Supply voltage, VCC                                       | 4.5   | 5                | 5.5 | 4.75 | 5                | 5.25 | ٧    |

| High-level output voltage, VOH                            |       |                  | 5.5 |      |                  | 5.5  | _ v  |

| Low-level output current, IQL                             |       |                  | 20  |      |                  | 40   | mA   |

| Width of write pulse, tw(write) (see Figure 1)            | 20    |                  |     | 20   |                  |      | ns   |

| Address input setup time, t <sub>sti</sub> (see Figure 1) | 0     |                  |     | 0    |                  |      | ns   |

| Operating free-air temperature, TA                        | -55   |                  | 125 | 0    |                  | 70   | °c   |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                                  |                                   |                                          | TEST COMPLETIONS! | SN5481A, SN5484A                               |      |     | SN748 | UNIT |     |      |          |

|----------------------------------|-----------------------------------|------------------------------------------|-------------------|------------------------------------------------|------|-----|-------|------|-----|------|----------|

|                                  | PARAMETER                         |                                          | TEST CONDITIONS   | MIN                                            | TYP‡ | MAX | MIN   | TYP‡ | MAX | Old. |          |

| VIH                              | High-level voltage at any input   |                                          |                   |                                                | 2    |     |       | 2    |     |      | <u> </u> |

|                                  | Low-level voltage                 | to prevent writing<br>to prevent sensing |                   |                                                |      |     | 8.0   |      |     | 0.8  | V        |

| VIL                              | at address inputs                 |                                          |                   | 1                                              |      |     | 1     |      |     | 1    |          |

| VIL                              | Low-level voltage at write inputs |                                          |                   |                                                |      | 8.0 |       |      | 1   | V    |          |

| VIK                              |                                   |                                          |                   | V <sub>CC</sub> = MIN, I <sub>I</sub> = -12 mA |      |     | -1.5  |      |     | -1.5 | V        |

| Іон                              | High-level output current         |                                          |                   | V <sub>CC</sub> = MIN, V <sub>OH</sub> = 5.5 V |      |     | 250   |      |     | 250  | μΑ       |

| VOL                              | Low-level output voltage          |                                          |                   | VCC = MIN, IOL = MAX                           | Ī    |     | 0.4   |      |     | 0.4  | V        |

|                                  | Input current at Write            | 557                                      |                   |                                                | 1    |     |       | 1    | mA  |      |          |

| 1լ                               | maximum input vo                  | tage                                     | Address           | V <sub>CC</sub> = MAX,V <sub>I</sub> = 5.5 V   |      |     | 3     |      |     | 3    |          |

|                                  |                                   |                                          | Write             | V <sub>CC</sub> = MAX,V <sub>I</sub> = 2.4 V   |      |     | 40    | l    |     | 40   | Aμ       |

| I <sub>IH</sub> High-level input | High-level input cui              | Address                                  |                   | V <sub>CC</sub> = MAX,V <sub>1</sub> = 4.5 V   | 400  |     |       |      | -   | 400  | <u> </u> |

| IIL L                            | Low-level input current           |                                          | Write             | V <sub>CC</sub> MAX, V <sub>I</sub> = 0.4 V    |      |     | 1.6   |      |     | 1.6  | mA       |

|                                  |                                   |                                          | Address           |                                                |      |     | -11   |      |     | -11  |          |

|                                  |                                   |                                          |                   | V <sub>CC</sub> = MAX,All inputs at 0 V        | T    |     | 70    |      |     | 65   | mA       |

| 1CC                              | 1CC Supply current                |                                          |                   | VCC = 5 V, All inputs at 0 V                   |      | 45  | 60    |      | 45  | 60   | A        |

<sup>&</sup>lt;sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.  $\ddagger$  AII typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

TEXAS INSTRUMENTS

7-46

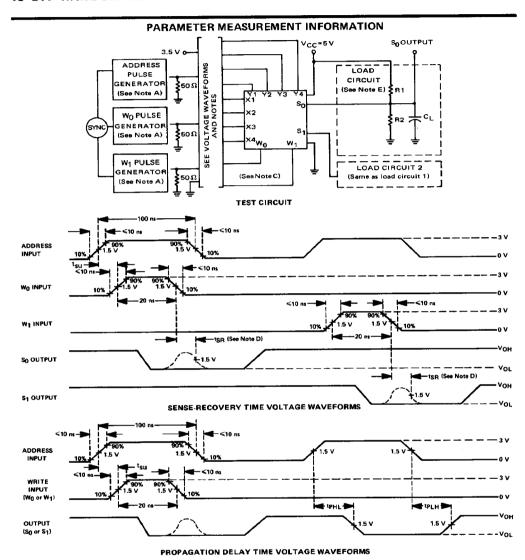

# switching characteristics, $V_{CC} = 5 \text{ V}$ , $I_{OL} = \text{MAX}^{\dagger}$ , $T_{A} = 25^{\circ}\text{C}$ , see figure 1

| PARAMETER §      | LOCATION<br>ADDRESSED  | TEST CONDITIONS         | SN5481A, SN | SN7481A, SN7484A |     |     |     |       |

|------------------|------------------------|-------------------------|-------------|------------------|-----|-----|-----|-------|

|                  |                        |                         | MIN TYP     | MAX              | MIN | TYP | MAX | UNIT  |

| <sup>t</sup> SR  | V4 V4                  | C <sub>L</sub> = 30 pF  | 13          |                  |     | 13  |     | l     |

|                  | X1 – Y1                | C <sub>L</sub> = 200 pF | 18          | 30               |     | 18  | 30  | ns    |

| <sup>†</sup> PHL |                        | C <sub>L</sub> = 30 pF  | 30 pF 11 19 |                  | 12  | 20  |     |       |

|                  | X1 - Y1                | CL = 200 pF             | 17          | 26               |     | 18  | 27  | ns    |

| tРLН             | 7 71-11                | C <sub>L</sub> = 30 pF  | 13          | 20               |     | 12  | 19  | ] "s  |

|                  |                        | CL = 200 pF             | 27          | 40               |     | 18  | 27  |       |

| †PHL             |                        | C <sub>L</sub> = 30 pF  | 10          | 18               |     | 11  | 19  |       |

|                  | X1 thru X4 and Y1      | CL = 200 pF             | 16          | 25               |     | 17  | 26  | ns    |

| <sup>t</sup> PLH | 7 A I trifu X4 and Y I | C <sub>L</sub> = 30 pF  | 13          | 20               |     | 13  | 20  | ] '15 |

|                  |                        | Cլ = 200 pF             | 27          | 40               |     | 19  | 28  |       |

type.

$t_{PHL} \equiv Propagation delay time, high-to-low-level output <math>t_{PLH} \equiv Propagation delay time, low-to-high-level output$

## schematic

$<sup>^\</sup>dagger W_{Q(B)}$  and  $W_{1(B)}$  inputs (indicated with dashed lines) are applicable for the SN5484A, SN7484A only.

₩ . . . V<sub>CC</sub> bus

Resistor values shown are nominal and in ohms.

1272

# TEXAS INSTRUMENTS INCORPORATED POST OFFICE BOX 5012 . DALLAS, TEXAS 75222

$<sup>\</sup>S t_{SR} \equiv Sense recovery time after writing$

- NOTES: A. The pulse generators have the following characteristics: for the address pulse generator, PRR = 2 MHz; for the W<sub>0</sub> and W<sub>1</sub> pulse generators, PRR = 1 MHz.

B. CL includes probe and jig capacitance.

C. For the SN5484A and SN7484A, unused W<sub>0</sub> and W<sub>1</sub> inputs are at 3.5 V.

D. t<sub>QR</sub> ≡ sense-recovery time

E. For the SN5481A and SN5484A: R1 = 240 Ω and R2 = 560 Ω. For the SN7481A and SN7484A: R1 = 120 Ω and R2 = 330 Ω.

FIGURE 1-SWITCHING CHARACTERISTICS

TEXAS INSTRUMENTS POST OFFICE BOX 5012 . DALLAS. TEXAS 75222

7-48