### INTEGRATED CIRCUITS

## DATA SHEET

# **PCF8522E** 256 $\times$ 8-bit CMOS EEPROM with $I^2$ C-bus interface

Objective specification Supersedes data of April 1995 File under Integrated Circuits, IC12

### $256\times 8\text{-bit}$ CMOS EEPROM with $I^2\text{C-bus}$ interface

**PCF8522E**

#### **CONTENTS**

| 1            | FEATURES                                        |

|--------------|-------------------------------------------------|

| 2            | APPLICATIONS                                    |

| 3            | GENERAL DESCRIPTION                             |

| 4            | ORDERING INFORMATION                            |

| 5            | BLOCK DIAGRAM                                   |

| 6            | PINNING                                         |

| 7            | FUNCTIONAL DESCRIPTION                          |

| -            |                                                 |

| 7.1<br>7.1.1 | Pinning information Serial clock (SCL)          |

| 7.1.2        | Serial data (SDA)                               |

| 7.1.3        | Address pins (A0 to A2)                         |

| 7.1.4        | Write control (WC)                              |

| 7.2          | Endurance and data retention                    |

| 7.3          | Characteristics of the I <sup>2</sup> C-bus     |

| 7.3.1        | General description                             |

| 7.3.2        | Input data protocol                             |

| 7.3.3        | START and STOP conditions.                      |

| 7.4          | Device operation                                |

| 7.4.1        | Acknowledge (ACK)                               |

| 7.4.2        | Slave address byte                              |

| 7.4.3        | Read/write bit                                  |

| 7.5          | Write operations                                |

| 7.5.1        | Byte write                                      |

| 7.5.2        | Page write                                      |

| 7.5.3        | Acknowledge polling                             |

| 7.6          | Read operations                                 |

| 7.6.1        | Current address byte read                       |

| 7.6.2        | Random address byte read                        |

| 7.6.3        | Sequential read                                 |

| 8            | LIMITING VALUES                                 |

| 9            | DC CHARACTERISTICS                              |

| 10           | AC CHARACTERISTICS                              |

| 11           | PACKAGE OUTLINE                                 |

| 12           | SOLDERING                                       |

| 12.1         | Introduction                                    |

| 12.2         | Soldering by dipping or by wave                 |

| 12.3         | Repairing soldered joints                       |

| 13           | DEFINITIONS                                     |

| 14           | LIFE SUPPORT APPLICATIONS                       |

| 15           | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS |

### $256 \times 8$ -bit CMOS EEPROM with I<sup>2</sup>C-bus interface

**PCF8522E**

#### 1 FEATURES

- Low power CMOS:

- operating current: <2 mA

- standby current: <2 μA</li>

- · Hardware write protection:

- Write Control (WC) pin

- Operation supply voltage 2.7 to 5.5 V

- Extended temperature range –40 to +85 °C

- Internally organized as 256 × 8-bit memory bank

- I<sup>2</sup>C interface (bidirectional data transfer protocol)

- Four-byte page-write mode (minimizes total write time per byte

- Automatic word address incrementing (sequential register read)

- Self-timed write cycle

- · High reliability:

- endurance: 100000 cyclesdata retention: 10 years

- DIP8 or SO8 package (8 pins).

#### 2 APPLICATIONS

The PCF8522E is ideal for high-volume applications requiring low power and low density storage.

Typical applications:

- Televisions

- Monitors

- Robotics

- Alarm devices

- Electronic locks

- Measuring devices

- · Instrumentation.

#### 3 GENERAL DESCRIPTION

The PCF8522E is a cost effective 2048 bit ( $256 \times 8$ -bit) serial Electrical Erasable Programmable Read Only Memory (EEPROM). The device is fabricated using advanced CMOS EEPROM technology. This IC operates from a single supply voltage within the range of 2.7 to 5.5 V.

The PCF8522E is internally organized as a  $256 \times 8$ -bit memory bank. It features an I<sup>2</sup>C-bus serial interface and software protocol allowing operation on a 2-wire bus.

Up to eight PCF8522Es may be connected to the 2-wire bus establishing their device addresses using the address input pins (A0 to A2).

#### 4 ORDERING INFORMATION

| TYPE NUMBER   |      | PACKAGE                                         |         |  |  |  |  |

|---------------|------|-------------------------------------------------|---------|--|--|--|--|

| I TPE NOWIBER | NAME | DESCRIPTION                                     | VERSION |  |  |  |  |

| PCF8522EP     | DIP8 | plastic dual in-line package; 8 leads (300 mil) | SOT97-1 |  |  |  |  |

## $256\times8\text{-bit}$ CMOS EEPROM with I²C-bus interface

PCF8522E

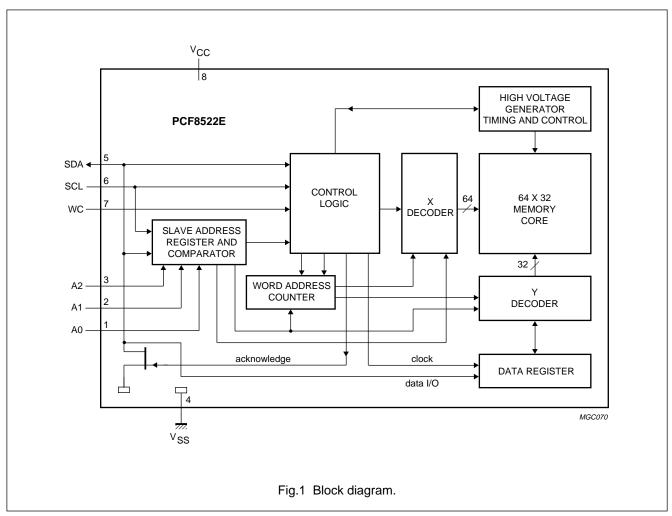

#### 5 BLOCK DIAGRAM

### $256 \times 8$ -bit CMOS EEPROM with I<sup>2</sup>C-bus interface

**PCF8522E**

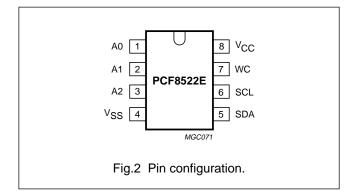

#### 6 PINNING

| SYMBOL          | PIN | DESCRIPTION                    |

|-----------------|-----|--------------------------------|

| A0              | 1   | address 1 input                |

| A1              | 2   | address 2 input                |

| A2              | 3   | address 3 input                |

| V <sub>SS</sub> | 4   | ground                         |

| SDA             | 5   | serial data input/output (I/O) |

| SCL             | 6   | serial clock input             |

| WC              | 7   | write control input            |

| V <sub>CC</sub> | 8   | supply voltage                 |

#### 7 FUNCTIONAL DESCRIPTION

#### 7.1 Pinning information

#### 7.1.1 SERIAL CLOCK (SCL)

The SCL input is used to clock data into and out of the device. In the write mode, data must remain stable when SCL is HIGH. In the read mode, data is clocked out on the falling edge of SCL.

#### 7.1.2 SERIAL DATA (SDA)

The SDA pin is a bidirectional pin used to transfer data into and out of the device. Data may only change when SCL is LOW, except START and STOP conditions. It is an open-drain output, and may be wire-ORed with any number of open-drain or open-collector outputs.

#### 7.1.3 ADDRESS PINS (A0 TO A2)

The address inputs are used to set the 3-bit device address of the PCF8522E which will identify it on the I<sup>2</sup>C-bus. The address pins may be tied HIGH or LOW, or they may be actively driven. These inputs allow up to eight PCF8522E devices to be distinguished on the I<sup>2</sup>C-bus.

#### 7.1.4 WRITE CONTROL (WC)

The write control input pin is used to disable the write circuitry to the memory. If WC = HIGH the write function is disabled, to protect previously written data. If WC = LOW the write function is enabled.

#### 7.2 Endurance and data retention

The PCF8522E is designed for applications requiring up to 100000 write cycles and unlimited number of read cycles. It provides 10 years of secure data retention, with or without supply voltage applied, after the execution of 100000 write cycles.

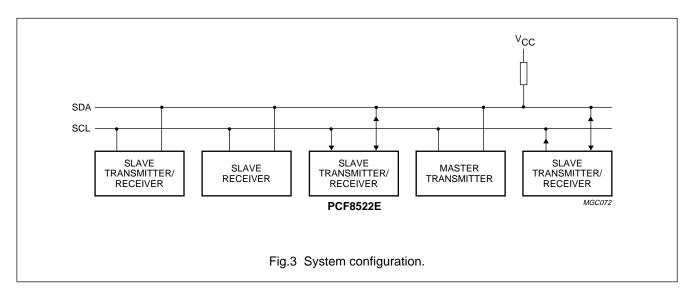

#### 7.3 Characteristics of the I<sup>2</sup>C-bus

#### 7.3.1 GENERAL DESCRIPTION

The I<sup>2</sup>C-bus is designed for two-way, 2-line serial communication for different integrated circuits. The 2-lines are:

- 1. Serial Data line (SDA).

- 2. Serial Clock Line (SCL).

The SDA line must be connected to the positive supply voltage by a pull-up resistor, located somewhere on the I<sup>2</sup>C-bus (see Fig.3)). Data transfer between devices may be initiated with a START condition only when SCL and SDA are HIGH (I<sup>2</sup>C-bus is not busy).

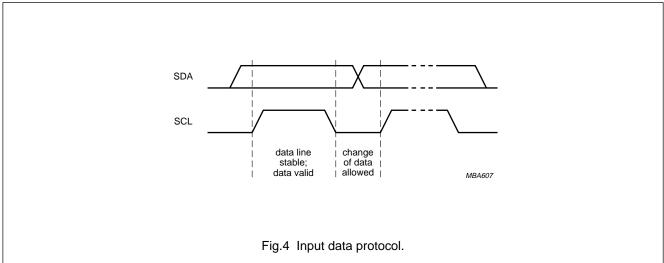

#### 7.3.2 INPUT DATA PROTOCOL

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable while the clock is HIGH, because changes on the data line, while SCL is HIGH will be interpreted as a 'START' or 'STOP' condition (see Fig.4).

#### 7.3.3 START AND STOP CONDITIONS.

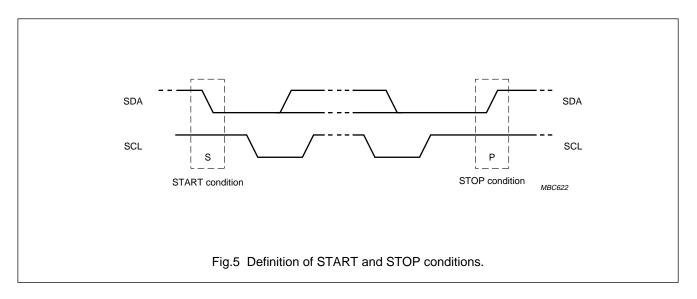

When both data (SDA) and clock (SCL) lines are HIGH, the I<sup>2</sup>C-bus is referred to as 'not busy'. A HIGH-to-LOW transition of the data line, while the clock is HIGH is defined as the 'START' condition. A LOW-to-HIGH transition of the data line, while the clock is HIGH, is defined as the 'STOP' condition (see Fig.5).

### $256 \times 8$ -bit CMOS EEPROM with I<sup>2</sup>C-bus interface

**PCF8522E**

#### 7.4 Device operation

The device supports the I<sup>2</sup>C-bus bidirectional data transmission protocol. The protocol defines any device that sends data onto the I<sup>2</sup>C-bus as a 'transmitter' and the receiving device as the 'receiver'. The device controlling the data transmission is the 'master' and the controlled device is the 'slave'. In all events the PCF8522E will be a 'slave' device because it never initiates any data transfers.

Up to eight PCF8522Es can be connected to the  $I^2$ C-bus and can be selected by the A0 to A2 device addresses. A0 to A2 must be connected to either  $V_{CC}$ ,  $V_{SS}$  or they may be actively driven. A0 to A2 define the address of the device. Other devices may be connected to the  $I^2$ C-bus but each device needs its own device identification code.

#### 7.4.1 ACKNOWLEDGE (ACK)

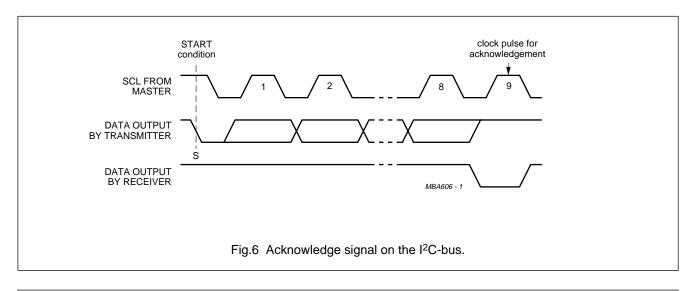

Acknowledge is a software convention used to indicate successful data transfers. The transmitting device, either the master or the slave, will release the I<sup>2</sup>C-bus after transmitting 8-bits. During the ninth clock cycle, the receiver will pull the SDA line LOW to acknowledge that it has received 8-bits of data (see Fig.6).

The PCF8522E will respond with an acknowledge after recognition of a START condition and its slave address byte. If both the device and a write operation have been selected, the PCF8522E will respond with an acknowledge after the receipt of each subsequent 8-bit word.

In the read mode, the PCF8522E transmits 8-bits of data, then releases the SDA line, and monitors the line for an acknowledge signal. If an acknowledge is detected, and no STOP condition is generated by the master, the PCF8522E will continue to transmit data.

If an acknowledge is not detected, the PCF8522E terminates further data transmissions and awaits a STOP condition before returning to the standby power mode.

#### 7.4.2 SLAVE ADDRESS BYTE

Following a START condition, the master must output the address to be accessed. The most significant 4 bits of the slave address are the 'device type identifier'. For a PCF8522E the address identifier is 1010 (see Table 1).

The next 3 bits are device address, addressing a particular device. Using this addressing scheme, a system may cascade up to eight PCF8522E devices on the I<sup>2</sup>C-bus. The device address is defined by the state of the A0 to A2 input pins.

#### 7.4.3 READ/WRITE BIT

The last bit of the slave address defines the operation to be performed. When  $R/\overline{W}=1$ , a read operation is selected. If  $R/\overline{W}=0$ , a write operation is selected (see Table 1).

Table 1 Slave address byte

| l | DEVICI | E TYPE<br>TIFIER | Ī | I<br>A | R/W |    |        |

|---|--------|------------------|---|--------|-----|----|--------|

| 1 | 0      | 1                | 0 | A2     | A1  | A0 | note 1 |

#### Note

- 1. This is the read/write bit:

- a) When  $R/\overline{W} = 1$ , a read operation is selected.

- b) When  $R/\overline{W} = 0$ , a write operation is selected.

### $256\times8\text{-bit}$ CMOS EEPROM with I²C-bus interface

PCF8522E

### $256 \times 8$ -bit CMOS EEPROM with I<sup>2</sup>C-bus interface

**PCF8522E**

#### 7.5 Write operations

The PCF8522E allows two types of write operations:

- Byte write operation; this operation writes a single byte during the nonvolatile write period (t<sub>WR</sub>).

- Page write operation; this operation allows up to 4-bytes in the same page to be stored during t<sub>WR</sub>.

#### 7.5.1 BYTE WRITE

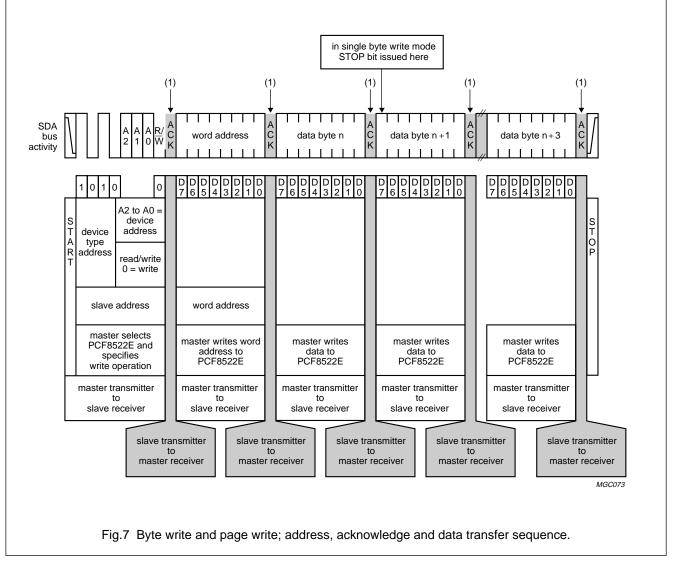

For a write operation, the PCF8522E requires a word address field after the slave address. This address field, comprised of 8 bits, with the Most Significant Bit (MSB) 'don't care', provides access to any one of the 256 words of memory.

Upon receipt of the word address, the PCF8522E responds with an acknowledge, and waits for the next 8 bits of data, again responding with an acknowledge. The master then terminates the transfer by generating a STOP condition, at which time the PCF8522E begins the internal write cycle to the nonvolatile array.

While the internal write cycle is in progress, the PCF8522E inputs are disabled, and the device will not respond to any requests from the master. Figure 7 shows an overview of the address, acknowledge and data transfer sequence.

#### 7.5.2 PAGE WRITE

The PCF8522E has the capability to perform a 4 byte page write operation. It is initiated in the same way as the byte write operation, but instead of terminating the write cycle after the first data word is transferred, the master can transmit up to three more words. After the receipt of each word, the PCF8522E will respond with an acknowledge.

The device automatically increments the address for subsequent data words. After the receipt of each word, the two low order address bits are internally incremented by one. The high order 5 bits of the address remain constant. If the master should transmit more than 4 words, prior to generating the STOP condition, the address counter will 'roll over', and the previously written data will be overwritten. In the same way as during a byte write operation, all inputs are disabled during the internal write cycle. Figure 7 shows an overview of the address, acknowledge and data transfer sequence.

#### 7.5.3 ACKNOWLEDGE POLLING

When the PCF8522E is performing an internal write operation, it will not recognize a START condition. Since the device will only return an acknowledge after it accepts the START condition, the part can be continuously queried until an acknowledge is issued, indicating that the internal write cycle is complete.

To poll the device, give it a START condition, followed by a slave address for a write operation (see Fig.8).

#### 7.6 Read operations

Read operations are initiated with setting the  $R/\overline{W}$  bit of the slave address byte to logic 1. There are four different read operations:

- 1. Current address byte read.

- 2. Random address byte read.

- 3. Current address sequential read.

- 4. Random address sequential read.

#### 7.6.1 CURRENT ADDRESS BYTE READ

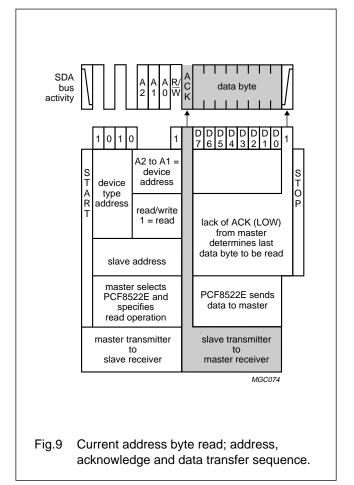

The PCF8522E contains an internal address counter which maintains the address of the last word accessed, incremented by one. If the last address accessed (either a read or a write operation) was to address location n, the next read operation would access data from address n + 1, and update the current address pointer. When the PCF8522E receives the slave address field with the  $R/\overline{W}$  bit set to logic 1, it issues an acknowledge signal and transmits the 8-bit word stored at address n + 1.

The current address read operation only accesses a single byte of data. The master does not acknowledge the transfer, but does generate a STOP condition. At this point, the PCF8522E discontinues the transmission (see Fig.9 for the address, acknowledge and data transfer sequence).

### $256\times8\text{-bit}$ CMOS EEPROM with I²C-bus interface

PCF8522E

### $256 \times 8$ -bit CMOS EEPROM with I<sup>2</sup>C-bus interface

**PCF8522E**

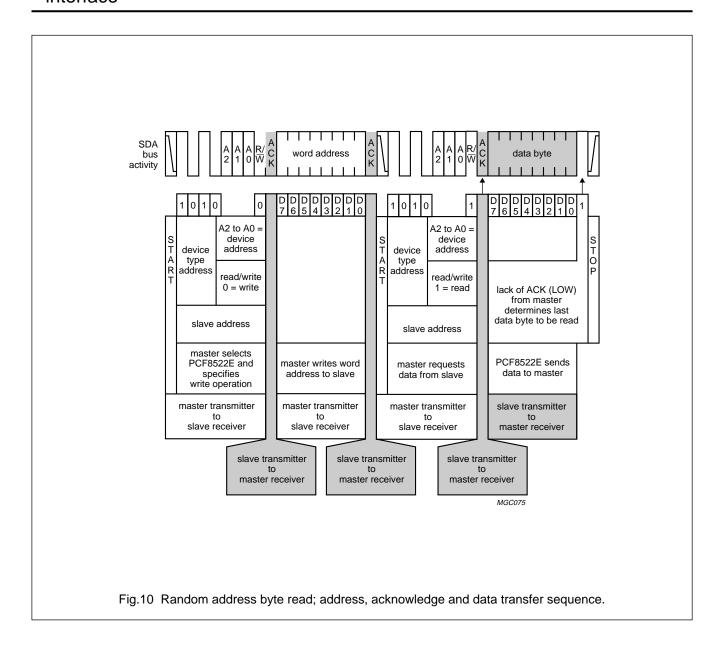

#### 7.6.2 RANDOM ADDRESS BYTE READ

Random address read operations allow the master to access any memory location at random. This operation involves a two-step process. First the master issues a write command which includes the START condition and the slave address field (with the R/W bit set to write), followed by the address of the word it is to read. This procedure sets the internal address counter of the PCF8522E to the desired address.

After the word address acknowledge is received by the master, the master immediately reissues a START condition followed by another slave address field with the R/W bit set to read. The PCF8522E will respond with an acknowledge and transmits the 8 data bits stored in the addressed location. At this point, the master does not acknowledge the transmission, but generates the STOP condition. The PCF8522E discontinues the data transmission and reverts to its standby power mode (see Fig.10 for the address, acknowledge and data transfer sequence).

### internal write cycle in progress: begin ACK polling issue START issue slave adress and R/W = 0issue STOP ACK returned? yes (internal write cycle compared) next operation a write? yes issue STOP issue byte address await next proceed with write MGC077 Fig.8 Acknowledge polling.

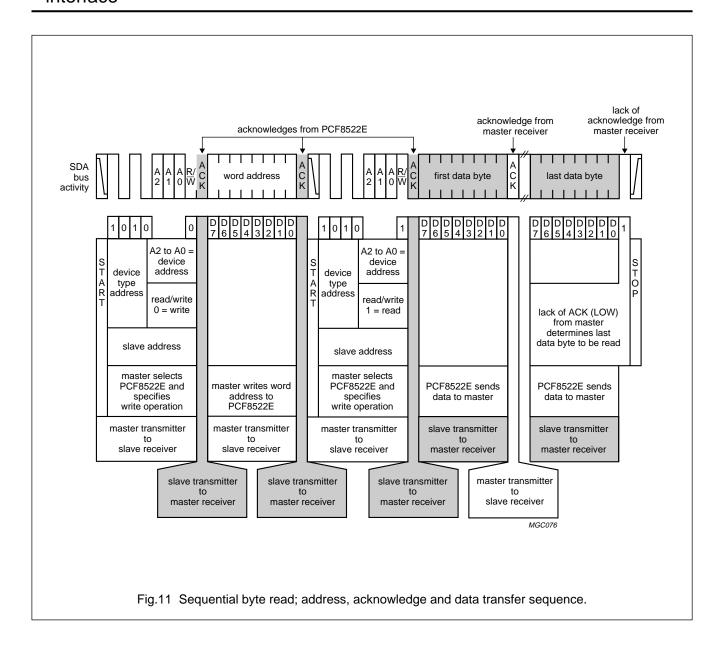

#### 7.6.3 SEQUENTIAL READ

Sequential reads can be initiated as either a current address read or random address read. The first word is transmitted in the same way as during the other byte read modes (current address byte read or random address byte read), but in this event the master responds with an acknowledge signal, indicating that it requires additional data from the PCF8522E.

The PCF8522E continues to output data for each received acknowledge signal. The master terminates the sequential read operation by not responding with an acknowledge signal, and issues a STOP condition.

During a sequential read operation, the internal address counter is automatically incremented with each acknowledge signal. For read operations, all address bits are incremented, allowing the entire array to be read using a single read command.

When the counter reaches the top of the array, it will 'roll over' to the bottom of the array and continue to transmit data for each acknowledge bit it receives (see Fig.11).

### $256\times8\text{-bit}$ CMOS EEPROM with I²C-bus interface

**PCF8522E**

### $256\times8\text{-bit}$ CMOS EEPROM with I²C-bus interface

**PCF8522E**

### $256\times8\text{-bit}$ CMOS EEPROM with I²C-bus interface

PCF8522E

#### 8 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL           | PARAMETER                     | CONDITIONS   | MIN.       | MAX.                  | UNIT |

|------------------|-------------------------------|--------------|------------|-----------------------|------|

| V <sub>CC</sub>  | supply voltage                |              | 0          | 6.5                   | V    |

| V <sub>n</sub>   | voltage on any pin            |              | -0.5       | V <sub>CC</sub> + 0.5 | V    |

| I <sub>O</sub>   | output current                |              | _          | 5                     | mA   |

| T <sub>sol</sub> | soldering temperature         | <10 s        | _          | 300                   | °C   |

| T <sub>stg</sub> | storage temperature           |              | <b>–65</b> | +125                  | °C   |

| T <sub>amb</sub> | operating ambient temperature |              | -40        | +85                   | °C   |

| V <sub>es</sub>  | electrostatic handling        | JEDEC method | -2000      | +2000                 | V    |

#### 9 DC CHARACTERISTICS

$V_{CC}$  = 2.7 to 5.5 V;  $T_{amb}$  = -40 to +85 °C; unless otherwise specified.

| SYMBOL           | PARAMETER                                             | CONDITIONS                                                     | MIN.               | MAX.               | UNIT |

|------------------|-------------------------------------------------------|----------------------------------------------------------------|--------------------|--------------------|------|

| Icc              | supply current (CMOS)                                 | $V_{CC} = 5 \text{ V} \pm 10\%;$<br>note 1                     | _                  | 2                  | mA   |

|                  |                                                       | $V_{CC} = 3 \text{ V} \pm 10\%;$<br>note 1                     | _                  | 1                  | mA   |

| I <sub>stb</sub> | standby current (CMOS)                                | SCL = SDA = V <sub>CC</sub> ;<br>note 2                        | _                  | 2                  | μА   |

| ILI              | input leakage current                                 | $V_I = 0$ to $V_{CC}$                                          | _                  | 10                 | μΑ   |

| I <sub>LO</sub>  | output leakage current                                | $V_O = 0$ to $V_{CC}$                                          | _                  | 10                 | μΑ   |

| V <sub>IL</sub>  | LOW level input voltage<br>pins A0 to A2, SCL and SDA |                                                                | _                  | 0.3V <sub>CC</sub> | V    |

| V <sub>IH</sub>  | HIGH level input voltage pins A0 to A2, SCL and SDA   |                                                                | 0.7V <sub>CC</sub> | _                  | V    |

| V <sub>OL</sub>  | LOW level output voltage                              | $I_{OL} = 3 \text{ mA}$                                        | _                  | 0.4                | V    |

| C <sub>I</sub>   | input capacitance                                     | $T_{amb} = 25 ^{\circ}\text{C};$<br>$f_{SCL} = 100 \text{kHz}$ | _                  | 5                  | pF   |

| C <sub>O</sub>   | output capacitance                                    | $T_{amb} = 25 ^{\circ}\text{C};$<br>$f_{SCL} = 100 \text{kHz}$ | _                  | 8                  | pF   |

#### Notes

- 1.  $f_{SCL} = 100 \text{ kHz}$ ; SDA = open-circuit; all other inputs connected to ground ( $V_{SS}$ ) or  $V_{CC}$ .

- 2. All other inputs connected to ground ( $V_{SS}$ ) or  $V_{CC}$ .

### $256\times8\text{-bit}$ CMOS EEPROM with I²C-bus interface

PCF8522E

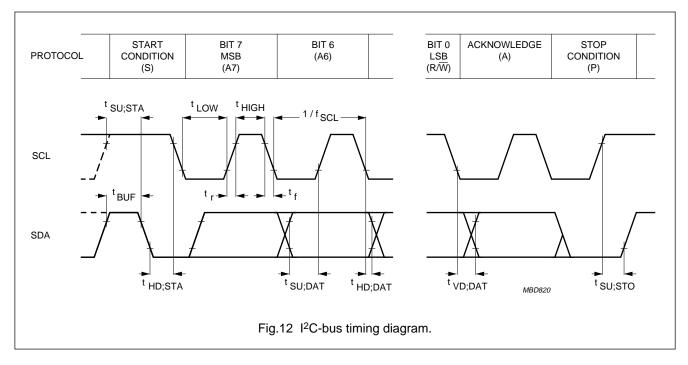

#### 10 AC CHARACTERISTICS

$V_{CC}$  = 2.7 to 5.5 V;  $T_{amb}$  = -40 to +85 °C; unless otherwise specified (see Fig.12); note 1.

| SYMBOL              | PARAMETER                       | CONDITIONS                        | MIN. | MAX. | UNIT |

|---------------------|---------------------------------|-----------------------------------|------|------|------|

| f <sub>SCL</sub>    | SCL clock frequency             |                                   | 0    | 100  | kHz  |

| t <sub>LOW</sub>    | SCL LOW time                    |                                   | 4.7  | _    | μs   |

| t <sub>HIGH</sub>   | SCL HIGH time                   |                                   | 4.0  | _    | μs   |

| t <sub>BUF</sub>    | bus free time                   | before new transmission           | 4.7  | _    | μs   |

| t <sub>SU;STA</sub> | START condition set-up time     |                                   | 4.7  | _    | μs   |

| t <sub>HD;STA</sub> | START condition hold time       |                                   | 4.0  | _    | μs   |

| t <sub>SU;STO</sub> | STOP condition set-up time      |                                   | 4.7  | _    | μs   |

| t <sub>VD;DAT</sub> | SCL LOW-to-SDA data out valid   |                                   | 0.3  | 3.5  | μs   |

| t <sub>HD;DAT</sub> | data hold time                  | SCL LOW to SDA output data change | 0.3  | _    | μs   |

| t <sub>r</sub>      | SCL and SDA rise time           |                                   | _    | 1000 | ns   |

| t <sub>f</sub>      | SCL and SDA fall time           |                                   | _    | 300  | ns   |

| t <sub>SU;DAT</sub> | input data set-up time          |                                   | 250  | _    | ns   |

| t <sub>HD;DAT</sub> | data hold time                  |                                   | 0    | _    | ns   |

| t <sub>SP</sub>     | noise spike width               |                                   | _    | 100  | ns   |

| T <sub>cy(w)</sub>  | write cycle time <sup>(2)</sup> | V <sub>CC</sub> = 5 V ±10%        | _    | 10   | ms   |

|                     |                                 | V <sub>CC</sub> = 3 V ±10%        | _    | 25   | ms   |

#### Notes

- 1. A detailed description of the I<sup>2</sup>C-bus specification, with applications, is given in brochure "The I<sup>2</sup>C-bus and how to use it". This brochure may be ordered using the code 9398 393 40011.

- 2. Typical  $T_{cy(w)}$  = 6 ms if  $V_{CC}$  = 5 V ±10%;  $T_{cy(w)}$  = 12 ms when  $V_{CC}$  = 3 V ±10%.

# $256\times8\text{-bit}$ CMOS EEPROM with I²C-bus interface

PCF8522E

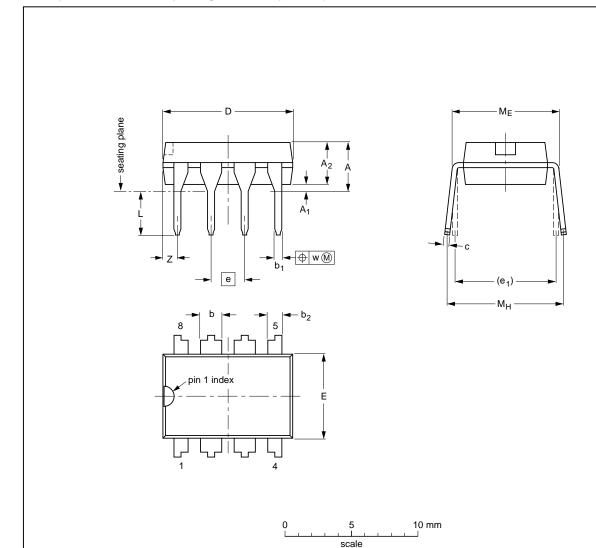

#### 11 PACKAGE OUTLINE

DIP8: plastic dual in-line package; 8 leads (300 mil)

SOT97-1

#### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | b <sub>2</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | e    | e <sub>1</sub> | L            | ME           | Мн           | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|--------------|--------------|-------|--------------------------|

| mm     | 4.2       | 0.51                   | 3.2                    | 1.73<br>1.14   | 0.53<br>0.38   | 1.07<br>0.89   | 0.36<br>0.23   | 9.8<br>9.2       | 6.48<br>6.20     | 2.54 | 7.62           | 3.60<br>3.05 | 8.25<br>7.80 | 10.0<br>8.3  | 0.254 | 1.15                     |

| inches | 0.17      | 0.020                  | 0.13                   | 0.068<br>0.045 | 0.021<br>0.015 | 0.042<br>0.035 | 0.014<br>0.009 | 0.39<br>0.36     | 0.26<br>0.24     | 0.10 | 0.30           | 0.14<br>0.12 | 0.32<br>0.31 | 0.39<br>0.33 | 0.01  | 0.045                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE |        | REFER    | EUROPEAN | ISSUE DATE |            |                                 |

|---------|--------|----------|----------|------------|------------|---------------------------------|

| VERSION | IEC    | JEDEC    | EIAJ     |            | PROJECTION | ISSUE DATE                      |

| SOT97-1 | 050G01 | MO-001AN |          |            |            | <del>92-11-17</del><br>95-02-04 |

### $256 \times 8$ -bit CMOS EEPROM with I<sup>2</sup>C-bus interface

**PCF8522E**

#### 12 SOLDERING

#### 12.1 Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "IC Package Databook" (order code 9398 652 90011).

#### 12.2 Soldering by dipping or by wave

The maximum permissible temperature of the solder is 260 °C; solder at this temperature must not be in contact with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature ( $T_{stg\ max}$ ). If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

#### 12.3 Repairing soldered joints

Apply a low voltage soldering iron (less than 24 V) to the lead(s) of the package, below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300  $^{\circ}\text{C}$  it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400  $^{\circ}\text{C}$ , contact may be up to 5 seconds.

### $256 \times 8$ -bit CMOS EEPROM with I<sup>2</sup>C-bus interface

**PCF8522E**

#### 13 DEFINITIONS

| Data sheet status          |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Objective specification    | This data sheet contains target or goal specifications for product development.       |

| Preliminary specification  | This data sheet contains preliminary data; supplementary data may be published later. |

| Product specification      | This data sheet contains final product specifications.                                |

| I too title as a select of |                                                                                       |

#### Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### **Application information**

Where application information is given, it is advisory and does not form part of the specification.

#### 14 LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

#### 15 PURCHASE OF PHILIPS I2C COMPONENTS

Purchase of Philips  $I^2C$  components conveys a license under the Philips'  $I^2C$  patent to use the components in the  $I^2C$  system provided the system conforms to the  $I^2C$  specification defined by Philips. This specification can be ordered using the code 9398 393 40011.