# **Signetics**

# PCF2100 LCD Duplex Driver

**Product Specification**

### **Linear Products**

### DESCRIPTION

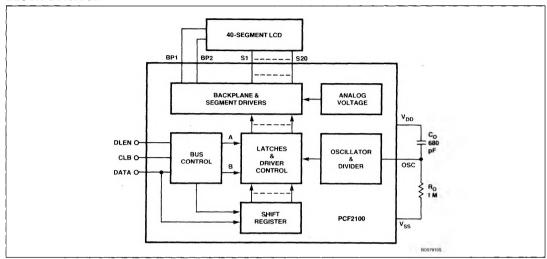

The PCF2100 is a single-chip, silicongate CMOS circuit designed to drive an LCD (Liquid Crystal Display) with up to 40 segments in a duplex manner, especially for low-voltage applications. A three-line bus structure enables serial data transfer with microcontrollers. All inputs are CMOS/NMOS compatible.

### **FEATURES**

- 40 LCD segment drive capability

- Supply voltage 2.25 to 6.5V

- Low current consumption

- Serial data input

- CBUS control

- One-point built-in oscillator

- Expansion possibility

### **APPLICATIONS**

- LCD displays

- Gauges

- Level/volume indicators

- Thermometers

### ORDERING INFORMATION

| DESCRIPTION                                    | TEMPERATURE RANGE | ORDER CODE |

|------------------------------------------------|-------------------|------------|

| 28-Pin Plastic DIP (SOT-117D)                  | -40°C to +85°C    | PCF2100PN  |

| 28-Pin Plastic SO package<br>(SO-28; SOT-136A) | -40°C to +85°C    | PCF2100TD  |

### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL           | PARAMETER                                      | RATING                           | UNIT |

|------------------|------------------------------------------------|----------------------------------|------|

| V <sub>DD</sub>  | Supply voltage with respect to V <sub>SS</sub> | -0.3 to 8                        | ٧    |

| V <sub>N</sub>   | Voltage on any pin                             | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ | ٧    |

| T <sub>A</sub>   | Operating ambient temperature range            | -40 to +85                       | °C   |

| T <sub>STG</sub> | Storage temperature range                      | -65 to +150                      | °C   |

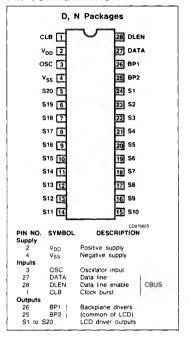

#### PIN CONFIGURATION

PCF2100

### **BLOCK DIAGRAM**

### **HANDLING**

Inputs and outputs are protected against electrostatic charge in normal handling. How-

ever, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices.

PCF2100

DC AND AC ELECTRICAL CHARACTERISTICS  $V_{DD}$  = 2.25 to 6.5 V;  $V_{SS}$  = 0 V;  $T_A$  = -40 to +85°C;  $R_O$  = 1M $\Omega$ ;  $C_O$  = 680pF, unless otherwise specified.

| SYMBOL                                                                                                | PARAMETER                                               | 7507 001/2/2/01/2                                  | LIMITS |      |           |          |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------|--------|------|-----------|----------|

|                                                                                                       |                                                         | TEST CONDITIONS                                    | Min    | Тур  | Max       | UNIT     |

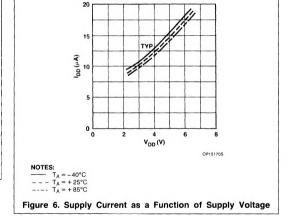

| I <sub>DD</sub>                                                                                       | Supply current                                          | No external load                                   |        | 10   | 50        | μΑ       |

| I <sub>DD</sub>                                                                                       | Supply current                                          | No external load;<br>T <sub>A</sub> = -25 to +85°C | ,      | -    | 30        | μΑ       |

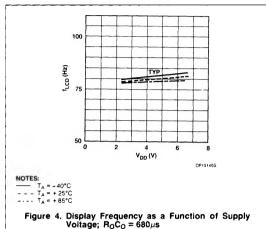

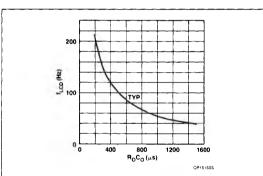

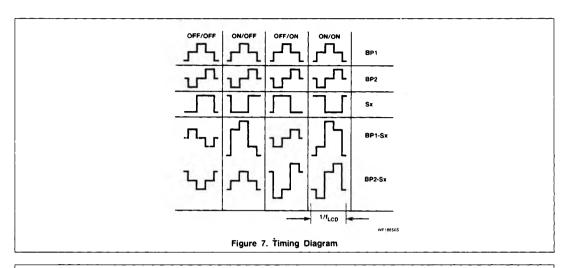

| f <sub>LCD</sub>                                                                                      | Display frequency                                       | See Figure 7; T = 680μs                            | 60     | 80   | 100       | Hz       |

| V <sub>BP</sub> DC component of LCD drive  Load on each segment driver  Load on each backplane driver | DC component of LCD drive                               | With respect to V <sub>SX</sub>                    |        | ± 10 |           | mV       |

|                                                                                                       | Load on each segment driver                             |                                                    |        |      | 10<br>500 | MΩ<br>pF |

|                                                                                                       |                                                         |                                                    |        | 1 5  | MΩ<br>nF  |          |

| V <sub>IH</sub>                                                                                       | Input voltage HIGH                                      | See Figure 8                                       | 2      |      |           | ٧        |

| V <sub>IL</sub>                                                                                       | Input voltage LOW                                       | See Figure 8                                       |        |      | 0.6       | V        |

| t <sub>R</sub>                                                                                        | Rise time V <sub>BP</sub> to V <sub>SX</sub>            | Maximum load                                       |        | 20   |           | μs       |

| Inputs C                                                                                              | LB, DATA, DLEN'                                         |                                                    |        |      |           |          |

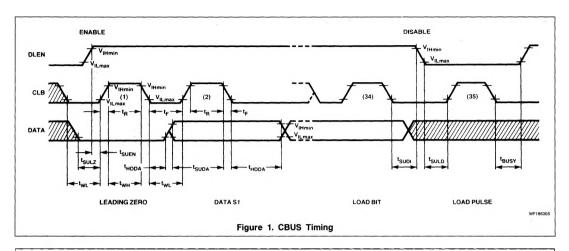

| t <sub>R</sub> , t <sub>F</sub>                                                                       | Rise and fall times                                     | See Figure 1                                       |        |      | 10        | μs       |

| t <sub>WH</sub>                                                                                       | CLB pulse width HIGH                                    | See Figure 1                                       | 1      |      |           | μs       |

| t <sub>WL</sub>                                                                                       | CLB pulse width LOW                                     | See Figure 1                                       | 9      |      |           | μs       |

| t <sub>SUDA</sub>                                                                                     | Data setup time<br>DATA → CLB                           | See Figure 1                                       | 8      |      |           | μs       |

| t <sub>HDDA</sub>                                                                                     | Data hold time<br>DATA → CLB                            | See Figure 1                                       | 8      |      |           | μs       |

| t <sub>SUEN</sub>                                                                                     | Enable setup time DLEN → CLB                            | See Figure 1                                       | 1      |      |           | μs       |

| t <sub>SUDI</sub>                                                                                     | Disable setup time<br>CLB → DLEN                        | See Figure 1                                       | 8      |      |           | μs       |

| t <sub>SULD</sub>                                                                                     | Setup time (load pulse) DLEN → CLB                      | See Figure 1                                       | 8      |      |           | μs       |

| t <sub>BUSY</sub>                                                                                     | Busy-time from load pulse to next start of transmission | See Figure 1                                       | 8      |      |           | μs       |

| t <sub>SULZ</sub>                                                                                     | Setup time (leading zero) DATA → CLB                    | See Figure 1                                       | 8      |      |           | μs       |

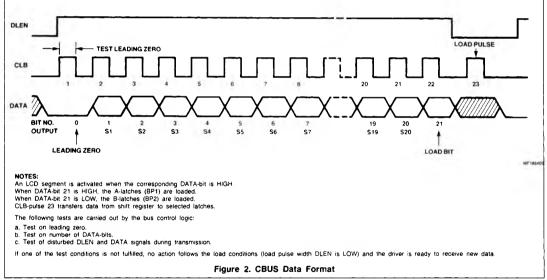

### NOTE:

All timing values are referred to V<sub>IHmin</sub> and V<sub>ILmax</sub> (see Figure 1). If external resistors are used in the bus lines (see Figure 8), the extra time constant has to be added.

PCF2100

PCF2100

Figure 5. Display Frequency as a Function of  $\rm R_{O} \times \rm C_{O}$  Time;  $\rm T_{A} = 25^{\circ}\rm C$

Signetics Linear Products Product Specification

## **LCD** Duplex Driver

**PCF2100**

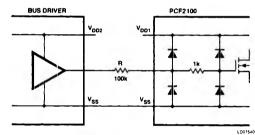

NOTES:  $V_{SS}$  line is common. In systems where it is expected that  $V_{0D2} > V_{0D1} + 0.5V$ , a resistor should be inserted to reduce the current flowing through the input protection. Maximum input current  $\leq 40~\mu$ A.

Figure 8. Input Circuitry

PCF2100

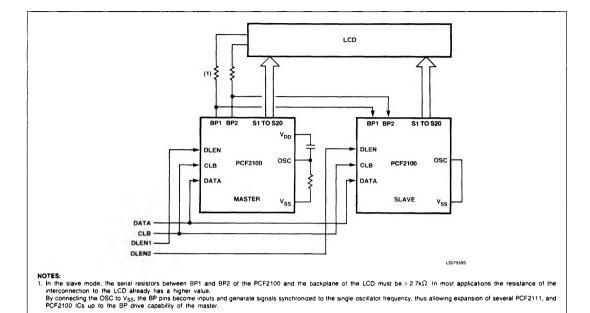

PCF2111 is a 64 LCD-segment driver.

Figure 9. Diagram Showing Expansion Possibility