# **OKI** semiconductor

# MSM6404VS

### MSM6404 PIGGY BACK

#### **GENERAL DESCRIPTION**

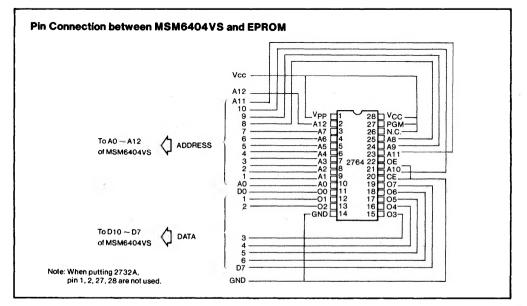

The MSM6404VS is a device whose built-in ROM is replaced by external EPROM using the piggy-back method.

#### FEATURES

- Supply Voltage: 5V ± 5% Frequency: DC ~ 4.2 MHz Operating Temperature: 0 ~ 70°C

- Note: There are a few differences in the electrical characteristics of this chip and the evaluation chip. Please refer to next page for the detail.

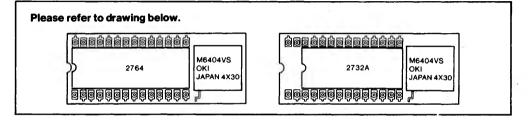

## **PUTTING METHOD OF ROM**

#### **PIN CONFIGURATION**

• MSM6404VS •-

# DIFFERENCES BETWEEN MSM6404 AND MSM6404 VS (PIGGY-BACK)

|    | Item                                          | 6404                                                                                                                    | 6404VS (Piggy-Back)                                                                                                                                           |

|----|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | Port<br>initialization<br>during reset        | Port P0, 1, 3 are set to "1" and port<br>2, 4, 5, 6, 7, 8 are reset to "0"<br>directly by signal put into the<br>RESET. | Port P0, 1, 3 are set to "1" and port 2,<br>4, 5, 6,7, 8 are reset to "0" during rese<br>cycle being executed.                                                |

| 2. | Timer<br>Operation                            | After being reset, timer stops counting until data are set in it.                                                       | It is undecidable whether the timer<br>starts counting or not after being reset<br>Therefore, the timer should be<br>initialized by software.                 |

| 3. | Shift registor                                | Serial Out F/F (SOF/F) is set to "0"<br>after being reset.                                                              | It is undecidable whether Serial Out<br>F/F (SOF/F) is set to "0" or "1" after<br>being reset. Therefore Serial Out F/F<br>should be initialized by software. |

| 4. | Port<br>input/output<br>timing                | Internal clock                                                                                                          | Internal clock                                                                                                                                                |

|    |                                               | Internal clock<br>Josephinisten<br>Synchronized<br>with falling edge<br>Data are output<br>at this moment               | Internal clock                                                                                                                                                |

| 5. | Port<br>input/output<br>(maracteris-<br>tics) | TTL F0=1<br>(I <sub>OL</sub> = 1.6 mA 0.4V)                                                                             | LSTTL F0=1<br>(I <sub>OL</sub> = 0.4 mA 0.4V)                                                                                                                 |

|    |                                               | VDD                                                                                                                     |                                                                                                                                                               |

|    | -                                             | TTL compatible input<br>P00~P83                                                                                         | CMOS input<br>P00~83                                                                                                                                          |

|    | Available<br>ROM capacity                     | 4K byte                                                                                                                 | Accessible up to 8K byte                                                                                                                                      |

|    | PL call<br>instruction                        | Not available                                                                                                           | Available                                                                                                                                                     |