SGLS099 - MARCH 1997

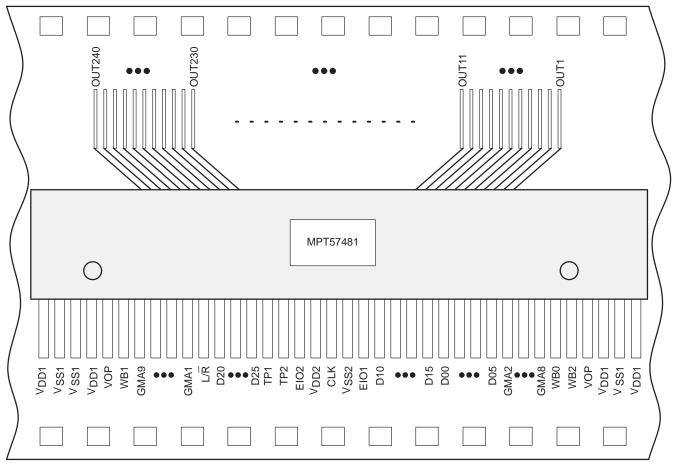

- 436 Terminal 70-mm Tab Assembly

- Selection Of Start Driver Input From Right Or Left By L/R Function

- CMOS Technology

- 6-Bit × 3 RGB Color Data Inputs

- 64-Gray-Scale Sub-Pixel Outputs Generated By 6-Bit DAC

- 55-MHz Operation

- Gamma Correction

- RGB Voltage Adjust

- Automatic Low-Power Standby Function

- 5-V Digital and Analog Voltage Supply

#### description

The MPT57481 is a 240-channel output, low-power, 5-V, signal source (column) driver for an active matrix LCD panel. This device has a digital-to-analog converter for each output. The MPT57481 utilizes 10 reference voltages for a 64 gray-scale subpixel output. Eight drivers are required for a  $640 \times 480$  color LCD and ten drivers are required for a  $800 \times 600$  color LCD.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

SGLS099 - MARCH 1997

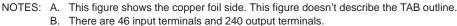

#### functional block diagram

#### detailed description

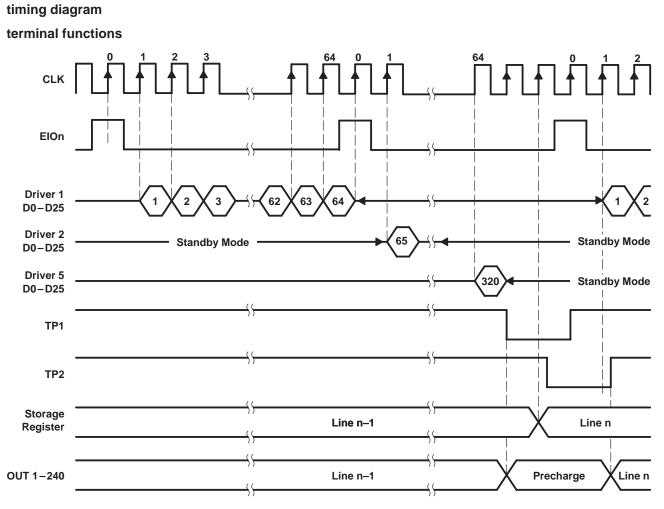

#### acquisition of line data

Acquisition of line data begins when a start pulse is applied to the EIO1 or EIO2 input terminal and is complete when all 240 channels of the Input Register have been loaded with new RGB data. When the first clock pulse, CLK0, is applied while the EIO terminal is biased high by the start pulse, an enable pulse enters the Shift Register and RGB data enters the Data Latch on the clock's rising edge. The enable pulse, after entering the Shift Register, positions itself to address the Input Register for loading of RGB data from the Data Latch on the rising edge of succeeding clock pulses after CLK0.

With each succeeding clock pulse, CLK (1-80), the Input Register is repeatedly addressed by the Shift Register and updated with new RGB data. One of 80 parallel outputs of the Shift Register addresses the Input Register with each transition of the clock pulse. Each output addresses three separate but adjacent channels of the Input Register simultaneously in a ascending or descending order between channels (1..240) as the enable pulse advances to the right or left from one output to the next. Channels (3n-2, 3n-1, and 3n) are addressed on the rising edge of CLKn by each output where 'n' is the number of clock pulse and addressing output.

While channels (3n-2, 3n-1, and 3n) are being addressed by the Shift Register outputs, 18-bit (6 bit  $\times$  3) RGB data stored in the Data Latch is loaded into the channels that are enabled. RGB data, originating at three 6-bit data input terminals, D05..D00, D15..D10, and D25..D20, is routed through the 18-bit Data Latch to the input of channels (3n-2, 3n-1, and 3n), respectively. New RGB data can be entered at the data input terminals and routed to the Input Register with each transition of the clock pulse from 1 to 80. After CLK(80), all 240 channels of the Input Register are addressed and loaded completing the acquisition of RGB line data.

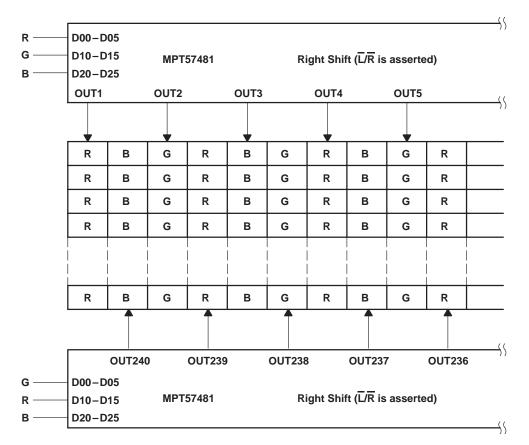

#### cascading drivers

If the pixels of a LCD display are greater than what one MPT57481 can drive, additional drivers can be cascaded together to extend the RGB line data by connecting the EIO output terminals of one driver to the EIO input terminals of the next driver. Between the rising edges of clock pulse, CLK( d80–1 and d80: d = number of driver), the enable pulse exits the Shift Register of one driver at the EIO output terminal and enters at the EIO input terminal of the next driver. When the enable pulse exits a driver, the driver enters a low-power standby mode while the next driver is set up to receive new RGB input data. The driver in standby mode goes back into normal mode when the next enable start pulse enters at its EIO input terminal.

#### transfer of line data

RGB line data is transferred from the Input Register to subpixel outputs, OUT (1..240) by a sequence of transitions of the TP1 and TP2 inputs. TP1 and TP2 are biased high while data is being acquired. After line data is acquired, data is transferred to the Storage Register and enters each DAC on the rising edge of the last clock pulse, CLK(d80+1; d = number of last driver) after TP1 transitions to low while TP2 remains high. Transfer of data beyond the Storage Register is independent of the clock. When TP1 or TP2 are low, each DAC is disabled from the subpixel outputs while the panel is precharged by V<sub>DD1</sub> using the outputs. During the precharging period, line data from the Storage Register, already inside each DAC, is converted to analog voltages during the second and third sequence when TP2 transitions to low with TP1 remaining low, and then when TP1 transitions back to high with TP2 remaining low. After TP1 goes high, line data, now represented as analog voltages, transfers to the output of each DAC. The last sequence, when TP2 goes back to high while TP1 remains high, the precharging period ends and all of the DACs are enabled allowing the analog voltages to transfer to the subpixel outputs.

#### 64 gray scale subpixel outputs

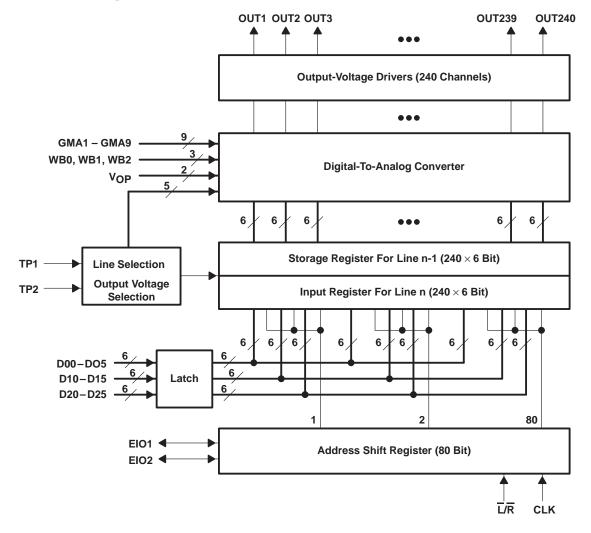

All 240 outputs of the MPT57481 are driven by separate 6-bit DACs. The output voltage of each DAC, 64 gray scale, is determined by the reference voltages GMA(0..9) and WB(0,1, or 2) selected by a 6-bit data input and by the VOP bias voltage. GMA (0..9) gamma correction voltages, WB(0..2) RGB Shift voltages, and VOP

#### SGLS099 - MARCH 1997

bias voltage can be adjusted to tailor the pixel output voltages needed for the particular LCD panel. GMA and VOP voltages affect all outputs, while WB0, WB1, and WB2 voltages affect only the 3n–2, 3n–1, or 3n outputs, respectively.

#### calculation of subpixel output voltage

Theoretical calculation of analog voltage with no process deviations assumed.

$$V_{O} = \frac{(m + 1) (VA(n + 1)) + (7 - m) (VA(n))}{8}$$

(1)

m: Upper 3 bits of 6-bit data

n: Lower 3 bits of 6-bit data

(2)

VAd = VOP +  $\frac{8(VOP - GMA(d + 1))}{7} + \frac{VOP - Vk}{7}$

(2)

Vk:WB0, WB1, and WB2

d = 0 - 8

#### graphical representation of output voltage

Calculation of analog voltage is shown graphically in Figure 1. The graph represents the output voltage verse 6-bit data input.

Figure 1. Output Voltage Verse 6-Bit Data Input

SGLS099 - MARCH 1997

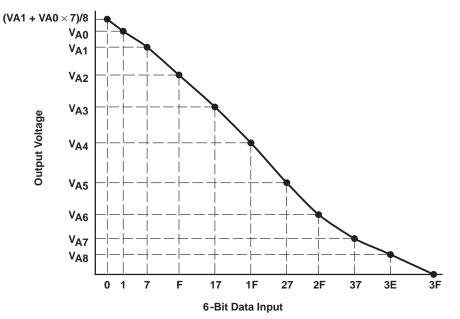

Figure 2.

SGLS099 - MARCH 1997

#### **Terminal Functions**

| TERMINAL<br>NAME NO.          | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CLK                           | I   | ift Clock. CLK synchronizes internal control logic with its rising edge. Also, CLK generates a data clock the Data Latch, a shift clock for the Address Shift Register, and a write enable for the Storage Register.                                                                                                                                                                                                                                                        |  |  |  |  |  |

| D00-D05<br>D10-D15<br>D20-D25 | I   | <ul> <li>a Input. Data inputs consist of 6-bit words for each of three channels (18 bits) for color input data.</li> <li>D05D00 (MSB to LSB) selects one of 64 gray-scale voltages on OUT (3n-2) with n = 1 - 80.</li> <li>D15D10 selects one of 64 gray-scale voltages on OUT (3n-1) with n = 1 - 80.</li> <li>D25D20 selects one of 64 gray-scale voltage on OUT (3n) with n = 1 - 80.</li> </ul>                                                                         |  |  |  |  |  |

| EIO1<br>EIO2                  | I/O | Enable I/O. EIO enables the Data Latch and Input Register to load 18-bit RGB data into the input Register on the rising edge of the clocks. The cascade output is for adding additional drivers to extend the length of line data. This helps to accommodate any particular LCD panel being driven.<br>$L/\overline{R} = is asserted \qquad L/\overline{R} is deasserted$                                                                                                   |  |  |  |  |  |

|                               |     | EIO1 Right-shift input Left-shift output                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                               |     | EIO2 Right-shift output Left-shift input                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| GMA1GMA9                      | I   | Analog circuit bias voltage. GMA supplies the bias voltage to the DAC and the gamma correction voltage adjust reference voltage.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Ī/R                           | I   | Shift Direction. $\overline{L/R}$ controls the direction in which the data is loaded into the input register. The data is loaded from OUT1 to OUT240 when $\overline{L/R}$ is asserted and from OUT240 to OUT1 when $\overline{L/R}$ is deasserted.                                                                                                                                                                                                                         |  |  |  |  |  |

| OUT1-OUT240                   | 0   | Subpixel output. Out provides 64 gray-scale signals to the LCD panel.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| TP1, TP2                      | ı   | Transfer input register contents. The next CLK rising edge after TP1 is deasserted causes the contents of<br>he input register (line n-1) to be transferred to the storage register (line n). After the transfer, the input<br>egister receives new line n–1 data from the data inputs. During the period that either TP1, TP2, or both are<br>leasserted, pixel-driver output is in a precharge mode that supplies voltage to all the OUT terminals (LCD<br>pixel drivers) |  |  |  |  |  |

| V <sub>DD1</sub>              | 1   | Analog supply voltage. The four $V_{DD1}$ terminals supply power for the analog circuitry.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| V <sub>DD2</sub>              | I   | Power supply for digital circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| VOP                           | I   | Bias voltage. VOP supplies the bias voltage for each DAC.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| VSS1                          | I   | Analog circuit ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| V <sub>SS2</sub>              | I   | Digital circuit ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| WB0, WB1,<br>WB2              | I   | <ul> <li>WBO adjusts OUT (3 n - 2) outputs with (n = 1 - 80)</li> <li>WB1 adjusts OUT (3 n - 1) outputs with (n = 1 - 80)</li> <li>WB2 adjusts OUT (3 n) outputs with (n = 1 - 80)</li> </ul>                                                                                                                                                                                                                                                                               |  |  |  |  |  |

SGLS099 - MARCH 1997

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>DD</sub> (V <sub>DD1</sub> , V <sub>DD2</sub> ) (see Note 1) | 0.3 V to +7 V                      |

|-------------------------------------------------------------------------------------|------------------------------------|

| Input voltage, VI (GMA1 – GMA9, VOP, WB0–WB2)                                       | -0.3 V to V <sub>DD1</sub> + 0.3 V |

| Input voltage, V <sub>I</sub> (all other terminals)                                 | -0.3 V to V <sub>DD2</sub> + 0.3 V |

| Output voltage, V <sub>O</sub> (EIO1, EIO2)                                         | -0.3 V to V <sub>DD2</sub> + 0.3 V |

| Output voltage, V <sub>O</sub> (OUT1 – OUT240)                                      | -0.3 V to V <sub>DD2</sub> + 0.3 V |

| Operating temperature range, T <sub>A</sub>                                         | –55°C to 125°C                     |

| Storage temperature range, T <sub>stg</sub>                                         | −65°C to 150°C                     |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to  $\mathsf{V}_{\ensuremath{\mathsf{SS}}}.$

#### recommended operating conditions

|                                                                                      | MIN                     | NOM                 | MAX                     | UNIT |

|--------------------------------------------------------------------------------------|-------------------------|---------------------|-------------------------|------|

| Supply voltage, V <sub>DD</sub> , (V <sub>DD1</sub> ,V <sub>DD2</sub> ) (See Note 2) | 4.5                     | 5                   | 5.5                     | V    |

| DAC bias supply voltage (VOP)                                                        | V <sub>DD1</sub> /2-0.2 | V <sub>DD1</sub> /2 | V <sub>DD1</sub> /2-0.2 | V    |

| DAC reference voltage (GMA1 – GMA9)                                                  | 0                       |                     | V <sub>DD1</sub>        |      |

| DAC reference voltage (WB0WB2)                                                       | 0                       |                     | $V_{DD}$                | V    |

| Clock frequency, f <sub>clk</sub>                                                    |                         |                     | 55                      | MHz  |

| Load capacitance for pixel outputs, CL                                               |                         |                     | 150                     | рF   |

| Operating Free-air Temperature, T <sub>A</sub>                                       | -55                     |                     | 125                     | °C   |

2.  $V_{DD1}$  and  $V_{DD2}$  are connected directly together.  $V_{SS1}$  and  $V_{SS2}$  are connected directly together. Power on sequence:  $V_{DD1} \rightarrow V_{DD2} \rightarrow GMA1...GMA9 \rightarrow input voltage.$

SGLS099 - MARCH 1997

# electrical characteristics over recommended operating conditions (unless otherwise noted), $V_{DD1}$ , $V_{DD2} = 5 V$ (see Note 3)

| PARAMETER         |                                            |                                                      | TEST CONDITIONS                    |                       | MIN                   | TYP† | MAX                   | UNIT |

|-------------------|--------------------------------------------|------------------------------------------------------|------------------------------------|-----------------------|-----------------------|------|-----------------------|------|

| ⊻ін               | High level input voltage                   | Dx0 – Dx5, CLK, TP1,<br>TP2, EIO1, EIO2              |                                    |                       | 2.2                   |      |                       | V    |

|                   | 0 1 0                                      | L/R                                                  |                                    |                       | 0.7 V <sub>DD2</sub>  |      |                       |      |

| VIL               | Low level input voltage                    | Dx0 – Dx5, CLK, TP1,<br>TP2, EIO1, EIO2              |                                    |                       |                       |      | 0.8                   | V    |

|                   | 1 0                                        | L/R                                                  |                                    |                       |                       |      | 0.3 V <sub>DD2</sub>  |      |

| ΙK                | Input leakage current                      | Dx0 – Dx5, CLK, T <u>P1,</u><br>TP2, EIO1, EIO2, L/R |                                    |                       | -10                   |      | 10                    | μΑ   |

| IO(1)             |                                            |                                                      | TP1, TP2 = 0 V,                    | $V_{O} = 4 V$         |                       | -1.5 |                       |      |

| I <sub>O(2)</sub> | Output current                             | OUT1 – 240                                           | TP1, TP2 = 5 V,<br>Dx5 – Dx0 = 00h | V <sub>O</sub> = 4 V, |                       | -10  |                       | mA   |

| I <sub>O(3)</sub> |                                            |                                                      | TP1, TP2 = 5 V,<br>Dx5 – Dx0 = 63h | V <sub>O</sub> = 4 V, |                       | 0.8  |                       |      |

| VO                | Subpixel output error (see Note 4)         | OUT1 – 240                                           |                                    |                       |                       |      | ±30                   | mV   |

| VO                | Subpixel output voltage range (see Note 5) | OUT1 – 240                                           |                                    |                       | V <sub>SS1</sub> +0.2 |      | V <sub>DD1</sub> -0.2 | V    |

|                   |                                            |                                                      | Hsync = 30 µs,                     | No load               |                       | 9    |                       |      |

| IDD               | Supply current                             | VDD1                                                 | Hsync = 30 μs,                     | See Note 6            |                       | 5    |                       | mA   |

|                   |                                            | V <sub>DD2</sub>                                     | Hsync = 30 µs,                     | No load               |                       | 5    |                       |      |

<sup>†</sup> All typical values are at  $V_{DD1}$ ,  $V_{DD2} = 5$  V and  $T_A = 25^{\circ}$ C.

NOTES: 3. For this table, the following are true: GMA1 – GMA9 = 0.5 V to 4.5 V in increments of 0.5 V, VOP = 2.5 V and WB0 – WB2 = 2.5 V.

4. Vo is the difference between the highest and the lowest reading across OUT1 - OUT240.

5. This is the range of output voltage between 6-bit input data 00h and 63h.

6. The load consists of a 75-pF capacitor connected from the output to V<sub>SS</sub> and in parallel with a series combination of a 75-pF capacitor and a 2-k $\Omega$  resistor.

SGLS099 - MARCH 1997

# timing requirements over recommended operating free-air temperature range, $V_{DD1}$ , $V_{DD2}$ = 5 V, See Note 7

| PARAMETER         |                                          | TEST CONDITIONS                      | MIN | TYP | MAX | UNIT |

|-------------------|------------------------------------------|--------------------------------------|-----|-----|-----|------|

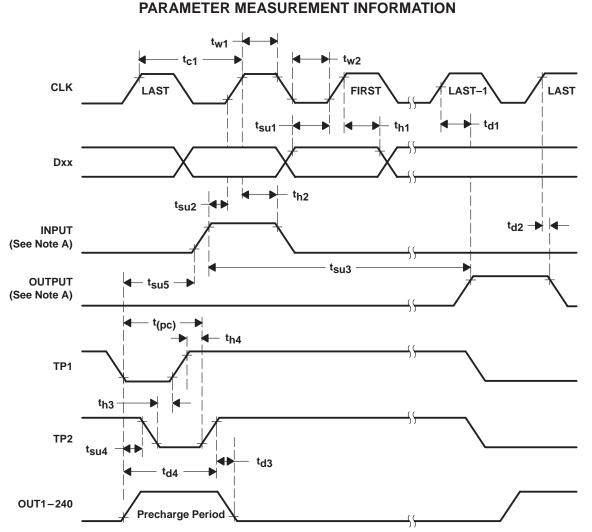

| t <sub>c1</sub>   | Clock cycle time                         | See Figure 3                         | 18  |     |     | ns   |

| tw1               | High-level pulse width duration          | See Figure 3                         | 5   |     |     | ns   |

| tw2               | Low-level pulse width duration           | See Figure 3                         | 5   |     |     | ns   |

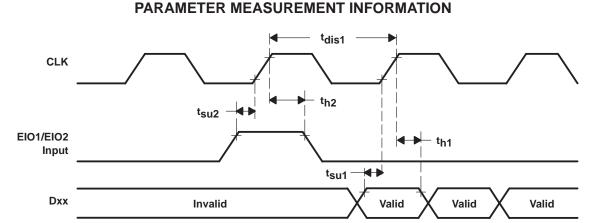

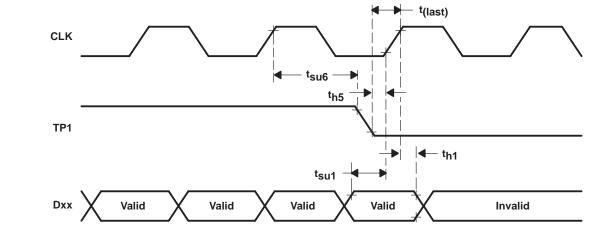

| t <sub>su1</sub>  | Data setup time                          | See Figure 3, Figure 4, and Figure 5 | 5   |     |     | ns   |

| <sup>t</sup> h1   | Data hold time                           | See Figure 3, Figure 4, and Figure 5 | 5   |     |     | ns   |

| t <sub>su2</sub>  | Start pulse setup time                   | See Figure 3 and Figure 4            | 5   |     |     | ns   |

| th2               | Start pulse hold time                    | See Figure 3 and Figure 4            | 5   |     |     | ns   |

| t <sub>su3</sub>  | Enable propagation setup time            | See Figure 3                         | 80  |     |     | CLK  |

| t(pc)             | Precharge time                           | See Figure 3                         | 3   |     |     | μs   |

| t <sub>h3</sub>   | TP1 hold time (with respect to TP2)      | See Figure 3                         | 1   |     |     | μs   |

| t <sub>su4</sub>  | TP1 setup time (with respect to TP2)     | See Figure 3                         | 1   |     |     | μs   |

| t <sub>h4</sub>   | TP2 hold time (with respect to TP1)      | See Figure 3                         | 0.5 |     |     | μs   |

| t <sub>su5</sub>  | TP1 shift input setup time               | See Figure 3                         | 1   |     |     | CLK  |

| <sup>t</sup> dis1 | Data input disable time                  | See Figure 4                         | 1   |     |     | CLK  |

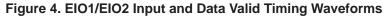

| t(last)           | Last data timing                         | See Figure 5                         | 1   |     |     | CLK  |

| t <sub>su6</sub>  | TP1 setup time (with respect to CLK)     | See Figure 5                         | 7   |     |     | ns   |

| t <sub>h5</sub>   | TP1, CLK hold time (with respect to CLK) | See Figure 5                         | 7   |     |     | ns   |

NOTE 7: All VIH and VIL input voltage levels are 5 V and 0 V, respectively.

# switching characteristics over recommended operating free-air temperature range, $V_{DD1}$ , $V_{DD2}$ = 5 V, See Figure 3 and Note 7

| PARAMETER       |                               | TEST CONDITIONS                                          |                        | MIN | TYP | MAX | UNIT |

|-----------------|-------------------------------|----------------------------------------------------------|------------------------|-----|-----|-----|------|

| <sup>t</sup> d1 | Enable propagation delay time | CL = 35 pF                                               |                        |     |     | 11  | ns   |

| t <sub>d2</sub> | Enable propagation delay time | CL = 35 pF                                               |                        |     |     | 15  | ns   |

| t <sub>d3</sub> | Output propagation delay time | C <sub>L1</sub> . C <sub>L2</sub> = 75 pF,<br>See Note 6 | $R_L = 2 k\Omega$ ,    |     |     | 3   | ns   |

| t <sub>d4</sub> | Output propagation delay time | C <sub>L1</sub> . C <sub>L2</sub> = 75 pF,<br>See Note 6 | R <sub>L</sub> = 2 kΩ, |     |     | 10  | ns   |

NOTES: 6. The load consists of a 75-pF capacitor connected from the output to V<sub>SS</sub> and in parallel with a series combination of a 75-pF capacitor and a 2-kΩ resistor.

7. All VIH and VIL input voltage levels are 5 V and 0 V, respectively.

SGLS099 - MARCH 1997

- NOTES: A. EIO1 (L/R is asserted), EIO2 (L/R is asserted)

- B. The input pulse is supplied by a generator having the following characteristics: PRR < 1 MHz, duty cycle < 50%, t<sub>r</sub>, t<sub>f</sub>  $\leq$  15 ns,  $z_{O} = 50 \Omega$ .

- C. The trip point for  $t_{d3}$  is output voltage + 0.5 V. The trip point for  $t_{d4}$  is output voltage ±100 mV.

#### Figure 3. Input, Output, and Precharge Period Timing Waveforms

SGLS099 - MARCH 1997

NOTE A. The input pulse is supplied by a generator having the following characteristics: PRR < 1 MHz, duty cycle < 50%,  $t_{f}$ ,  $t_{f} \le$  15 ns,  $z_{O} = 50 \Omega$ .

NOTE A. The input pulse is supplied by a generator having the following characteristics: PRR < 1 MHz, duty cycle < 50%, t<sub>f</sub>, t<sub>f</sub>  $\leq$  15 ns,  $z_{O} = 50 \Omega$ .

Figure 5. TP1 and Data Valid Timing Waveforms

SGLS099 - MARCH 1997

**APPLICATION INFORMATION**

Figure 6. MPT57481 Connections to a Strip-Type Color-Filter Panel

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated