## MN863440

## TFT LCD Gate Driver with 200, 240, 256, or 263 Outputs

#### Overview

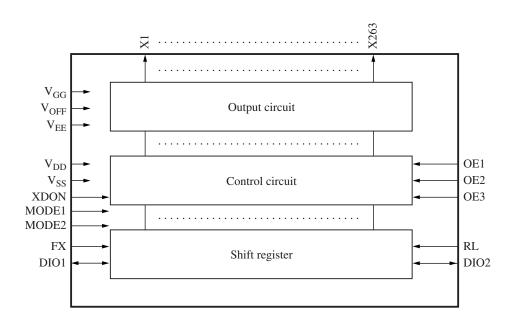

The MN863440 is a TFT LCD gate driver with 200, 240, 256, or 263 2-value outputs. The number of outputs can be selected to be any one of these by the user.

This IC implements 2-value (pseudo 3-value) drive, and provides a cascade-connection pin to support large-screen displays. It is provided in a TCP package.

#### Features

- Adopts a bidirectional shift register system

- Provides an expansion pin so that the number of output pins can be increased.

- Pulse width modulation function (OE1 to OE3)

- Driver operating frequency: 500 kHz (maximum)

- LCD drive voltage: V<sub>EE</sub> + 40 V (maximum)

- Driver output levels: 2 levels (The low level can be modified.)

- Supports TCP mounting.

#### Applications

• LCD TV sets

#### ■ Block Diagram

#### ■ Functional Descriptions

#### 1. LCD drive voltages

The MN863440 can provide LCD drive voltages that are negative relative to logic ground.

#### 2. Operation

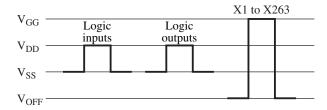

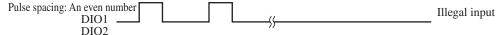

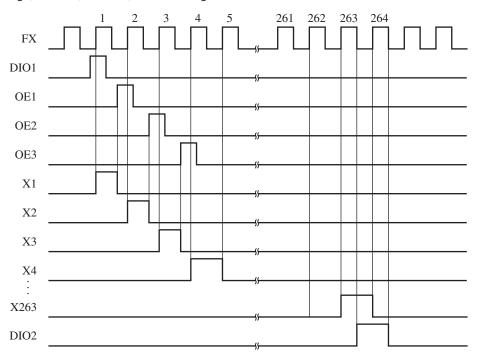

The MN863440 outputs either the display level ( $V_{GG}$ ) or the off level ( $V_{OFF}$ ) from the LCD driver outputs (X1 to X263) under control of the shift data and the OE input signal.

The data shift direction can be controlled with the shift direction switching pin (RL).

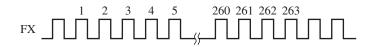

The DIO input signal is acquired on the rising edge of FX. The shift register operates and the drive voltages are output with this timing as well. The DIO output is synchronized with the falling edge of FX.

|           | Start       | Data transfer         | Carry pulse |

|-----------|-------------|-----------------------|-------------|

| RL        | pulse input | direction             | output      |

| RL = High | DIO1        | X1 → X263             | DIO2        |

| RL=Low    | DIO2        | $X263 \rightarrow X1$ | DIO1        |

## ■ Functional Descriptions (continued)

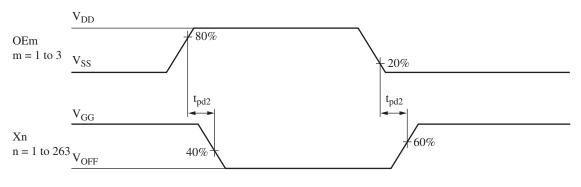

#### 3. OE function

The outputs can be forced to the display off level regardless of the data in the shift register in sets consisting of every third output pin by setting the OE1, OE2, and OE3 pins to the high level.

This function operates asynchronously with the FX pin.

| 200 output TCP | 240 output TCP | 256 output TCP 263 output TC |              |  |

|----------------|----------------|------------------------------|--------------|--|

| MODE1 = Low    | MODE1 = Low    | MODE1 = High                 | MODE1 = High |  |

| MODE2 = Low    | MODE2 = High   | MODE2 = Low                  | MODE2 = High |  |

| X1 (OE1)       | X1 (OE1)       | X1 (OE1)                     | X1 (OE1)     |  |

| X2 (OE2)       | X2 (OE2)       | X2 (OE2)                     | X2 (OE2)     |  |

| X3 (OE3)       | X3 (OE3)       | X3 (OE3)                     | X3 (OE3)     |  |

| <u> </u>       | : :            | : :                          | <u> </u>     |  |

| X98 (OE2)      | : :            | : :                          | X98 (OE2)    |  |

| X99 (OE3)      | : :            | : :                          | X99 (OE3)    |  |

| X100 (OE1)     | : :            | : :                          | X100 (OE1)   |  |

|                | : :            | : :                          | : :          |  |

|                | X118 (OE1)     | : :                          | X118 (OE1)   |  |

|                | X119 (OE2)     | : :                          | X119 (OE2)   |  |

|                | X120 (OE3)     | : :                          | X120 (OE3)   |  |

|                |                | : :                          | : :          |  |

|                |                | X126 (OE3)                   | X126 (OE3)   |  |

|                |                | X127 (OE1)                   | X127 (OE1)   |  |

|                |                | X128 (OE2)                   | X128 (OE2)   |  |

|                |                |                              | X129 (OE3)   |  |

|                |                |                              | X130 (OE1)   |  |

|                |                |                              | X131 (OE2)   |  |

|                |                |                              | X132 (OE3)   |  |

|                |                |                              | X133 (OE1)   |  |

|                |                |                              | X134 (OE2)   |  |

|                |                |                              | X135 (OE3)   |  |

|                |                | X136 (OE3)                   | X136 (OE1)   |  |

|                |                | X137 (OE1)                   | X137 (OE2)   |  |

|                |                | X138 (OE2)                   | X138 (OE3)   |  |

|                |                | <u> </u>                     | <u> </u>     |  |

|                | X144 (OE1)     | : :                          | X144 (OE3)   |  |

|                | X145 (OE2)     | : :                          | X145 (OE1)   |  |

|                | X146 (OE3)     | : :                          | X146 (OE2)   |  |

|                | : :            | : :                          | : :          |  |

#### ■ Functional Descriptions (continued)

#### 3. OE function (continued)

| 200 output TCP | 240 output TCP | 256 output TCP | 263 output TCP |

|----------------|----------------|----------------|----------------|

| X164 (OE2)     | : :            | : :            | X164 (OE2)     |

| X165 (OE3)     | : :            | : :            | X165 (OE3)     |

| X166 (OE1)     | : :            | : :            | X166 (OE1)     |

| : :            | : :            | : :            | : :            |

| X261 (OE3)     | X261 (OE1)     | X261 (OE2)     | X261 (OE3)     |

| X262 (OE1)     | X262 (OE2)     | X262 (OE3)     | X262 (OE1)     |

| X263 (OE2)     | X263 (OE3)     | X263 (OE1)     | X263 (OE2)     |

Here, (OEn) indicates which of OE1, OE2, and OE3 is the related signal.

#### 4. XDON function

The outputs can be set to the output the display on potential  $(V_{GG})$  regardless of the states of the OEn pins and the shift register data by setting the XDON pin to the low level.

This function operates asynchronously with the FX pin. This pin is pulled up.

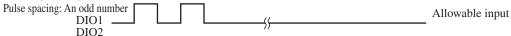

#### 5. Carry input (DIO1, DIO2)

The waveform input to the carry input must meet the following conditions.

#### 2) Input with a width of 2 pulses or longer

#### 3) Double pulse input

#### 4) Double pulse input

## ■ Pin Descriptions

| Pin Name          | I/O   | Function                                                     | Description                                                                                                                                                                                                                                                                    |                 |                                       |        |

|-------------------|-------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------|--------|

| FX                | I     | Shift register clock input                                   | The start pulse is acquired and the shift register shifted on th FX rising edge. The carry pulse is output on the FX falling edge.                                                                                                                                             |                 |                                       |        |

| RL                | I     | Right shift/left shift selection input                       | RL = High: $X1 \rightarrow X263$ (Left shift)<br>RL = Low: $X263 \rightarrow X1$ (Right shift)                                                                                                                                                                                 |                 |                                       |        |

| DIO1              | I/O   | Start pulse input and carry                                  |                                                                                                                                                                                                                                                                                | DIO1            | DIO2                                  |        |

| DIO2              |       | pulse output                                                 | RL = High                                                                                                                                                                                                                                                                      | I               | 0                                     |        |

|                   |       |                                                              | RL = Low                                                                                                                                                                                                                                                                       | 0               | I                                     |        |

| MODE1<br>MODE2    | I     | Output pin count switching                                   | MODE1                                                                                                                                                                                                                                                                          | MODE2           | LCD outputs                           |        |

| MODE2             |       | inputs                                                       | High                                                                                                                                                                                                                                                                           | High            | 263                                   |        |

|                   |       |                                                              | High                                                                                                                                                                                                                                                                           | Low             | 256                                   |        |

|                   |       |                                                              | Low                                                                                                                                                                                                                                                                            | High            | 240                                   |        |

|                   |       |                                                              | Low                                                                                                                                                                                                                                                                            | Low             | 200                                   |        |

| OE1 to OE3        | I     | Display signal enable/disable inputs                         | When OEn is high, the corresponding LCD drive output pare set to the display off potential (V <sub>OFF</sub> ) asynchronously with the FX pin, regardless of the states of the shift register and other input data.  See 3. OE function in the Functional Descriptions section |                 |                                       |        |

| X1 to X263        | 0     | LCD drive outputs                                            | These pins output, in synchronization with the FX rising $\epsilon$ either the $V_{GG}$ or the $V_{OFF}$ voltage level according to the shift register data and the states of the OE1 to OE3, DIO and DIO2 pins.                                                               |                 |                                       |        |

| $V_{ m GG}$       | Power | LCD drive output block<br>power supply<br>LCD drive supply 1 |                                                                                                                                                                                                                                                                                |                 | ters and output be LCD drive voltage. |        |

| V <sub>OFF</sub>  | Power | LCD drive supply 2                                           | Supplies an LC                                                                                                                                                                                                                                                                 | D drive voltage | •                                     |        |

| $V_{EE}$          | Power | V <sub>GG</sub> system ground                                |                                                                                                                                                                                                                                                                                |                 |                                       |        |

| $V_{\mathrm{DD}}$ | Power | 3 V system logic power supply                                | Power supply u                                                                                                                                                                                                                                                                 | sed for the 3 V | system logic circ                     | cuits. |

| $V_{SS}$          | Power | V <sub>DD</sub> system ground                                |                                                                                                                                                                                                                                                                                |                 |                                       |        |

#### ■ Basic Waveforms

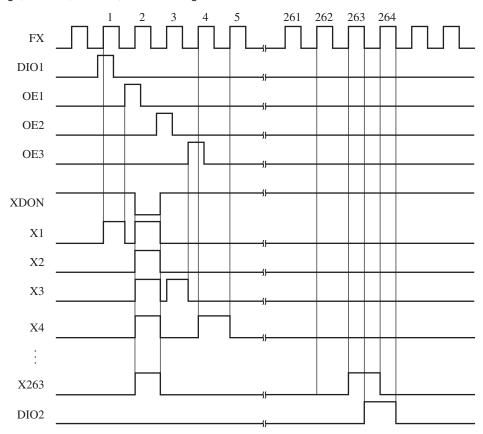

1. RL = High, left shift, MODE1, MODE2 = high

2. RL = Low, right shift, MODE1, MODE2 = high

## ■ XDON Usage Example

• RL = High, left shift, MODE1, MODE2 = high

#### ■ Electrical Characteristics

#### 1. Absolute Maximum Ratings at V<sub>SS</sub> = 0 V

| Item                                    | Symbol           | Rating                                 | Unit |

|-----------------------------------------|------------------|----------------------------------------|------|

| Supply voltage 1                        | $V_{DD}$         | - 0.3 to +4.5                          | V    |

| Supply voltage 2                        | $V_{GG}$         | V <sub>EE</sub> to V <sub>EE</sub> +44 | V    |

| Drive voltage                           | V <sub>OFF</sub> | $V_{EE}$ – 0.3 to $V_{GG}$ +0.3        | V    |

| Supply voltage 3                        | $V_{EE}$         | - 24 to +0.3                           | V    |

| Digital input voltage                   | $V_{I}$          | - 0.3 to V <sub>DD</sub> +0.3          | V    |

| Operating and storage temperature range | Ta               | -30 to +85                             | °C   |

| Operating ambient temperature           | $T_{opr}$        | -20 to +75                             | °C   |

| Storage temperature                     | $T_{stg}$        | -55 to +120                            | °C   |

- Note) 1. The absolute maximum ratings are limit values for stresses applied to the chip so that the chip will not be destroyed. Operation is not guaranteed within these ranges.

- The operating and storage temperature range is the temperature range over which the chip will not be damaged even if operated. Note that performance is not guaranteed throughout this range.

- 3. These ratings are guaranteed values when the standard Panasonic package is used.

- The power supply voltages must meet the condition V<sub>EE</sub> ≤ V<sub>GG</sub> at all times, including when power is being applied, during operation, and when power is being turned off.

- 5. When power is applied, certain sequences of power application can cause large currents to flow and permanently damage the IC. To avoid this problem, first apply  $V_{DD}$ , and then, after  $V_{DD}$  has reached 90% of its set voltage, apply  $V_{EE}$ ,  $V_{GG}$ , and  $V_{OFF}$ .

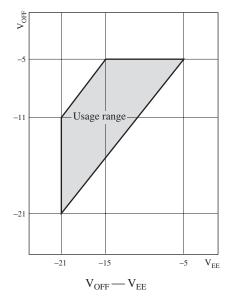

#### 2. Operating Conditions at $V_{SS} = 0 \text{ V}$ , $T_{opr} = -20^{\circ}\text{C}$ to $+75^{\circ}\text{C}$

| Item                       | Symbol            | Condition                | Min             | Тур | Max                 | Unit |

|----------------------------|-------------------|--------------------------|-----------------|-----|---------------------|------|

| Operating supply voltage 1 | $V_{\mathrm{DD}}$ |                          | 2.3             | _   | 3.6                 | V    |

| Operating supply voltage 2 | $V_{GG}$          |                          | 10              | _   | V <sub>EE</sub> +40 | V    |

| Operating supply voltage 3 | V <sub>EE</sub>   |                          | -21             | _   | -5                  | V    |

| Operating supply voltage 3 | V <sub>OFF</sub>  | $-21 \le V_{EE} \le -15$ | V <sub>EE</sub> |     | V <sub>EE</sub> +10 | V    |

|                            |                   | $-15 < V_{EE} < -5$      | V <sub>EE</sub> |     | -5                  |      |

Note) These ratings are guaranteed values when the standard Panasonic package is used.

## ■ Electrical Characteristics (continued)

3. DC Characteristics at  $V_{SS} = 0 \text{ V}$ ,  $T_{opr} = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$

| Item                                        | Symbol               | Condition                          | Min                 | Тур | Max                 | Unit |

|---------------------------------------------|----------------------|------------------------------------|---------------------|-----|---------------------|------|

| Operating supply current (V <sub>DD</sub> ) | I <sub>DD</sub>      | $f_{EX} = 15.7 \text{ kHz}$        |                     |     | 800                 | μА   |

| operating suppry current (* DD)             | -DD                  | $f_{DIO} = 60 \text{ Hz}$          |                     |     | 000                 | μ21  |

|                                             |                      | $V_{DD} = 3.0 \text{ V}$           |                     |     |                     |      |

| Operating supply current (V <sub>GG</sub> ) | $I_{GG}$             | $V_{OFF} = -15 \text{ V}$          | _                   | _   | 300                 | μΑ   |

|                                             |                      | $V_{GG} = 15 \text{ V}$            |                     |     |                     |      |

|                                             |                      | With no output load                |                     |     |                     |      |

| Standby mode current                        | $I_{DS}$             | In standby mode                    | _                   | _   | 600                 | μΑ   |

| consumption (V <sub>DD</sub> )              |                      | $V_{DD} = 3.0 \text{ V}$           |                     |     |                     |      |

| Standby mode current                        | $I_{GS}$             | $V_{OFF} = -15 \text{ V}$          | _                   | _   | 100                 | μΑ   |

| consumption (V <sub>GG</sub> )              | 4 OF2 MG             | $V_{GG} = 15 \text{ V}$            |                     |     |                     |      |

|                                             |                      | DDE1, MODE2                        | 0.0                 |     | X7.                 | X 7  |

| High-level input voltage                    | V <sub>IH1</sub>     |                                    | $0.8 \times V_{DD}$ |     | V <sub>DD</sub>     | V    |

| Low-level input voltage                     | V <sub>IL1</sub>     |                                    | 0                   |     | $0.2 \times V_{DD}$ | V    |

| Input leakage current                       | I <sub>LI1</sub>     |                                    | -10                 |     | 10                  | μΑ   |

|                                             | DON                  | I                                  |                     |     |                     |      |

| High-level input voltage                    | V <sub>IH2</sub>     |                                    | $0.8 \times V_{DD}$ |     | $V_{DD}$            | V    |

| Low-level input voltage                     | V <sub>IL2</sub>     |                                    | 0                   |     | $0.2 \times V_{DD}$ | V    |

| Pull-up resistance                          | R <sub>PU</sub>      | $V_{DD} = 3.0 \text{ V}$           | 10                  | _   | 100                 | kΩ   |

| 3) I/O pins DIO1, DIO2                      |                      |                                    |                     |     |                     |      |

| High-level input voltage                    | $V_{IH3}$            |                                    | $0.8 \times V_{DD}$ | _   | $V_{DD}$            | V    |

| Low-level input voltage                     | V <sub>IL3</sub>     |                                    | 0                   | _   | $0.2 \times V_{DD}$ | V    |

| High-level output voltage                   | V <sub>OH</sub>      | –100 μΑ                            | $V_{DD} - 0.4$      | _   | _                   | V    |

| Low-level output voltage                    | V <sub>OL</sub>      | 100 μΑ                             | _                   | _   | 0.4                 | V    |

| 4) LCD drive voltage input pir              | V <sub>OFF</sub>     |                                    |                     |     |                     |      |

| Input leakage current                       | V <sub>LI1</sub>     |                                    | -50                 | _   | 50                  | μΑ   |

| 5) LCD drive output pins                    | X1 ~ X263            |                                    |                     |     |                     |      |

| Output leakage current                      | I <sub>LO1</sub>     |                                    | -50                 | _   | 50                  | μΑ   |

| Output on resistance                        | RON-V <sub>GG</sub>  | V <sub>GG</sub> = 15 V             | 200                 | 400 | 800                 | Ω    |

|                                             |                      | $V_{OFF} = -15 \text{ V}$          |                     |     |                     |      |

|                                             |                      | $V_{OM} = V_{GG} - 0.5 \text{ V}$  |                     |     |                     |      |

|                                             |                      | V <sub>OM</sub> is the X1 to X263  |                     |     |                     |      |

|                                             |                      | applied voltage.                   |                     |     |                     |      |

|                                             | RON-V <sub>OFF</sub> | $V_{GG} = 15 \text{ V}$            | 200                 | 400 | 800                 |      |

|                                             |                      | $V_{EE} = -15 \text{ V}$           |                     |     |                     |      |

|                                             |                      | $V_{OFF} = -15 \text{ V}$          |                     |     |                     |      |

|                                             |                      | $V_{OM} = V_{OFF} + 0.5 \text{ V}$ |                     |     |                     |      |

|                                             |                      | V <sub>OM</sub> is the X1 to X263  |                     |     |                     |      |

|                                             |                      | applied voltage.                   |                     |     |                     |      |

Note) These ratings are guaranteed values when the standard Panasonic package is used.

## ■ Electrical Characteristics (continued)

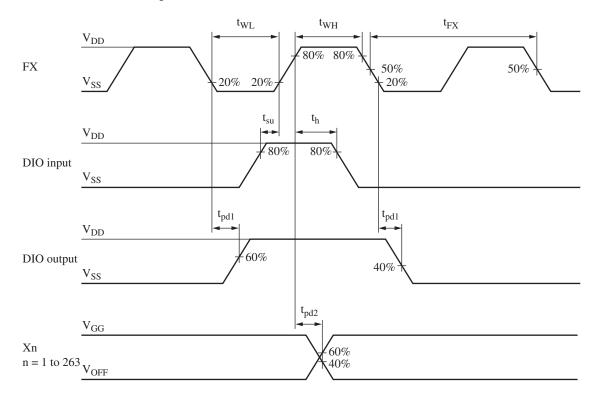

## 4. AC Characteristics at $V_{SS}$ = 0 V, $T_{opr}$ = -20°C to +75°C

| Item                         | Symbol            | Condition   | Min | Тур | Max | Unit |

|------------------------------|-------------------|-------------|-----|-----|-----|------|

| Clock period                 | t <sub>FX</sub>   |             | 2.0 | _   | _   | μs   |

| Clock high-level pulse width | t <sub>WH</sub>   |             | 700 | _   | _   | ns   |

| Clock low-level pulse width  | $t_{\mathrm{WL}}$ |             | 700 |     | _   | ns   |

| DIO data setup time          | t <sub>su</sub>   |             | 300 | _   | _   | ns   |

| DIO data hold time           | t <sub>h</sub>    |             | 300 | _   | _   | ns   |

| DIO output delay time        | t <sub>pd1</sub>  | CL = 50 pF  | _   | _   | 600 | ns   |

| Xn output delay time         | t <sub>pd2</sub>  | CL = 300 pF | _   | _   | 800 | ns   |

Note) These ratings are guaranteed values when the standard Panasonic package is used.

#### AC Characteristics Timing Charts

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this book and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this book is limited to showing representative characteristics and applied circuits examples of the products. It neither warrants non-infringement of intellectual property right or any other rights owned by our company or a third party, nor grants any license.

- (3) We are not liable for the infringement of rights owned by a third party arising out of the use of the product or technologies as described in this book.

- (4) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (5) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (6) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage, and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment.

Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (7) When using products for which damp-proof packing is required, observe the conditions (including shelf life and amount of time let standing of unsealed items) agreed upon when specification sheets are individually exchanged.

- (8) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of Matsushita Electric Industrial Co., Ltd.