October 1987 Revised January 1999

# MM74C912 6-Digit BCD Display Controller/Driver

### **General Description**

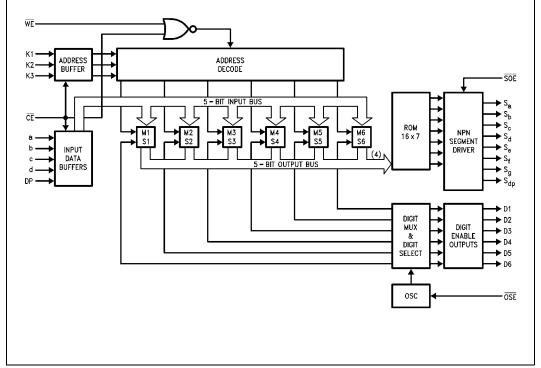

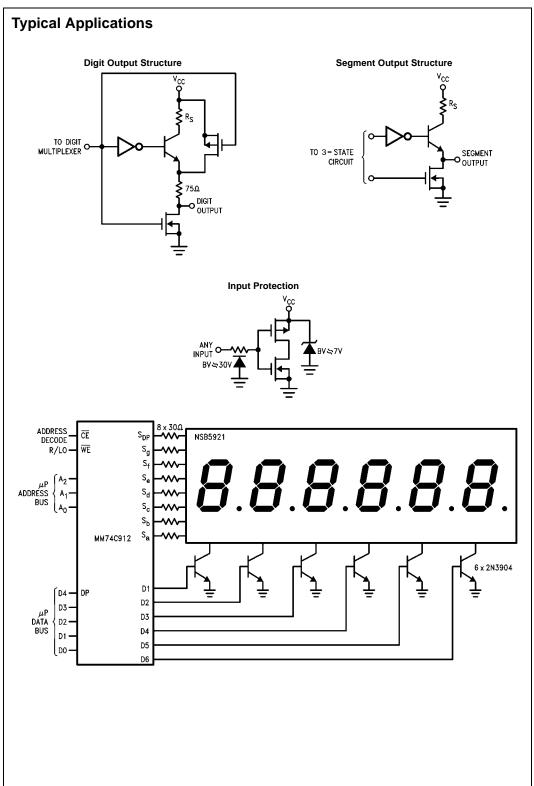

The MM74C912 display controllers are interface elements, with memory, that drive a 6-digit, 8-segment LED display.

The display controllers receive data information through 5 data inputs A, B, C, D and DP, and digit information through 3 address inputs K1, K2 and K3.

The input data is written into the register selected by the address information when CHIP ENABLE, ( $\overline{\text{CE}}$ ), and WRITE ENABLE, ( $\overline{\text{WE}}$ ), are LOW and is latched when either  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$  return HIGH. Data hold time is not required. A self-contained internal oscillator sequentially presents the stored data to a decoder where 4 data bits control the format of the displayed character and 1 bit controls the decimal point. The internal oscillator is controlled by a control input labeled OSCILLATOR ENABLE, ( $\overline{\text{OSE}}$ ), which is tied LOW in normal operation. A high level at  $\overline{\text{OSE}}$  prevents automatic refresh of the display.

The 7-segment plus decimal point output information directly drives an LED display through high drive (100 mA

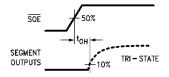

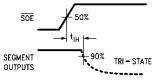

typ.) output drivers. The drivers are active when the control pin labeled SEGMENT OUTPUT ENABLE, ( $\overline{SOE}$ ), is LOW and go into 3-STATE when  $\overline{SOE}$  is HIGH. This feature allows for duty cycle brightness control and for disabling the output drivers for power conservation.

The MM74C912 segment decoder converts BCD data into 7-segment format.

All inputs are TTL compatible and do not clamp to the  $V_{\mbox{\footnotesize CC}}$  supply.

#### **Features**

- Direct segment drive (100 mA typ.) 3-STATE

- 6 registers addressed like RAM

- Internal oscillator and scanning circuit

- Direct base drive to digit transistor (20 mA typ.)

- Internal segment decoder

- TTL compatible inputs

### **Ordering Code:**

| Order Number | Package Number | Package Description                                                    |

|--------------|----------------|------------------------------------------------------------------------|

| MM74C912N    | N28B           | 28-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.600" Wide |

#### **Connection Diagram**

#### **Dual-In-Line Package**

# **Truth Tables**

Input Control

| CE | Di | git Addre | ss | WE | Operation        |  |  |

|----|----|-----------|----|----|------------------|--|--|

|    | К3 | K2        | K1 |    |                  |  |  |

| 0  | 0  | 0         | 0  | 0  | Write Digit 1    |  |  |

| 0  | 0  | 0         | 0  | 1  | Latch Digit 1    |  |  |

| 0  | 0  | 0         | 1  | 0  | Write Digit 2    |  |  |

| 0  | 0  | 0         | 1  | 1  | Latch Digit 2    |  |  |

| 0  | 0  | 1         | 0  | 0  | Write Digit 3    |  |  |

| 0  | 0  | 1         | 0  | 1  | Latch Digit 3    |  |  |

| 0  | 0  | 1         | 1  | 0  | Write Digit 4    |  |  |

| 0  | 0  | 1         | 1  | 1  | Latch Digit 4    |  |  |

| 0  | 1  | 0         | 0  | 0  | Write Digit 5    |  |  |

| 0  | 1  | 0         | 0  | 1  | Latch Digit 5    |  |  |

| 0  | 1  | 0         | 1  | 0  | Write Digit 6    |  |  |

| 0  | 1  | 0         | 1  | 1  | Latch Digit 6    |  |  |

| 0  | 1  | 1         | 0  | 0  | Write Null Digit |  |  |

| 0  | 1  | 1         | 0  | 1  | Latch Null Digit |  |  |

| 0  | 1  | 1         | 1  | 0  | Write Null Digit |  |  |

| 0  | 1  | 1         | 1  | 1  | Latch Null Digit |  |  |

| 1  | Х  | Х         | Х  | Х  | Disable Writing  |  |  |

X = Don't Care

#### **Output Control**

| SOE | OSE | Operation                |

|-----|-----|--------------------------|

| 0   | 0   | Refresh Display          |

| 0   | 1   | Stop Oscillator (Note 1) |

| 1   | 0   | Disable Segment Outputs  |

| 1   | 1   | Standby Mode             |

Note 1: Segment drive may exceed maximum display dissipation.

## **Functional Description**

#### **Character Font**

| MM74C912               | Hi – Z | ננ | 1 | 2 | 3 | 4 | 5 | 5 | 7- | 8 | 9 | 0 | 0 | 1 | 1 | 1 |   | • |

|------------------------|--------|----|---|---|---|---|---|---|----|---|---|---|---|---|---|---|---|---|

| Input A 2 <sup>0</sup> | Х      | 0  | 1 | 0 | 1 | 0 | 0 | 0 | 1  | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 |

| Data B2 <sup>1</sup>   | Х      | 0  | 0 | 1 | 1 | 0 | 1 | 1 | 1  | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 |

| C 2 <sup>2</sup>       | Х      | 0  | 0 | 0 | 0 | 1 | 1 | 1 | 1  | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| D 2 <sup>3</sup>       | Х      | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| DP                     | Х      | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| OUTPUT ENABLE SOE      | 1      | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### Segment Identification

The MM74C912 display controller is manufactured using metal gate CMOS technology. A single 5V 74 series TTL supply can be used for power and should be bypassed at the  $\rm V_{CC}$  pin.

All inputs are TTL compatible; the segment outputs drive the LED display directly through current limiting resistors. The digit outputs are designed to directly drive the base of a grounded emitter digit transistor without the need of a Darlington configuration.

As seen in the block diagram, these display controllers contain six 5-bit registers; any one of which may be randomly written. The internal multiplexer scans the registers and refreshes the display. This combination of write only memory and self-scan display makes the display controller a "refreshing experience" for an over-burdened microprocessor.

## **Block Diagram**

## Absolute Maximum Ratings(Note 2)

(Note 3)

Voltage at Any Pin

Except Inputs  $-0.3 \text{V to V}_{\text{CC}} + 0.3 \text{V}$

Voltage at Any Input -0.3V to +15V

Operating Temperature

Range ( $T_A$ )  $-40^{\circ}$ C to  $+85^{\circ}$ C

Storage Temperature

Range (T<sub>S</sub>)  $-65^{\circ}$ C to  $+150^{\circ}$ C

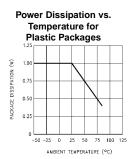

Power Dissipation ( $P_D$ ) Refer to  $P_{D \text{ MAX}}$  vs  $T_A$  Graph

$\begin{array}{ll} \mbox{Operating V}_{\mbox{CC}} \mbox{ Range} & \mbox{3V to 6V} \\ \mbox{Absolute Maximum (V}_{\mbox{CC}}) & \mbox{6.5V} \end{array}$

Lead Temperature

(Soldering, 10 seconds) 260°C

Note 2: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Range" they are not meant to imply that the device should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device acceptance.

device operation.

Note 3: All voltages reference to ground.

#### **DC Electrical Characteristics**

Min/Max limits apply at  $40^{\circ}C \leq T_{J} \leq 85^{\circ}C,$  unless otherwise noted

| Symbol              | Parameter                  | Conditions                         | Min                   | Тур    | Max      | Units |

|---------------------|----------------------------|------------------------------------|-----------------------|--------|----------|-------|

| CMOS TO             | CMOS                       |                                    |                       |        | <u>L</u> | 1     |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage  | V <sub>CC</sub> = 5V               | 3.0                   |        |          | V     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage  | $V_{CC} = 5V$                      |                       |        | 1.5      | V     |

| I <sub>IN(1)</sub>  | Logical "1" Input Current  | $V_{CC} = 5V$ , $V_{IN} = 15V$     |                       | 0.005  | 1.0      | μА    |

| I <sub>IN(0)</sub>  | Logical "0" Input Current  | $V_{CC} = 5V$ , $V_{IN} = 0V$      | -1.0                  | -0.005 |          | μА    |

| Icc                 | Supply Current             | V <sub>CC</sub> = 5V, Outputs Open |                       | 0.5    | 2        | mA    |

| l <sub>OUT</sub>    | 3-STATE                    | $V_{CC} = 5V$ , $V_O = 5V$         |                       | 0.03   | 10       | μА    |

|                     | Output Current             | $V_{CC} = 5V$ , $V_O = 0V$         | -10                   | -0.03  |          | μΑ    |

| CMOS/LP             | TTL INTERFACE              |                                    |                       |        |          |       |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage  | V <sub>CC</sub> = 4.75V            | V <sub>CC</sub> - 2.0 |        |          | V     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage  | V <sub>CC</sub> = 4.75V            |                       |        | 0.8      | V     |

| OUTPUT D            | DRIVE                      |                                    |                       |        |          |       |

| I <sub>SH</sub>     | High Level                 | $V_{CC} = 5V, V_{O} = 3.4V$        |                       |        |          |       |

|                     | Segment Current            | $T_J = 25^{\circ}C$                | -60                   | -100   |          | mA    |

|                     |                            | T <sub>J</sub> = 100°C             | -40                   | -60    |          | mA    |

| I <sub>DH</sub>     | High Level                 | $V_{CC} = 5V$ , $V_O = 1V$         |                       |        |          | 1     |

|                     | Digit Current              | $T_J = 25^{\circ}C$                | -10                   | -20    |          | mA    |

|                     |                            | T <sub>J</sub> = 100°C             | -7                    | -15    |          | mA    |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage | $V_{CC} = 5V, I_{O} = -360\mu A$   | 4.6                   |        |          | V     |

| 1                   | Any Digit                  |                                    |                       |        |          |       |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage | $V_{CC} = 5V, I_{O} = 360\mu A$    |                       |        | 0.4      | V     |

| 1                   | Any Digit                  |                                    |                       |        |          |       |

| $\theta_{JA}$       | Thermal Resistance         | (Note 4)                           |                       | 100    |          | °C/W  |

Note 4:  $\theta_{\text{JA}}$  measured in free air with device soldered into printed circuit board.

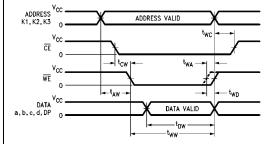

# AC Electrical Characteristics (Note 5) $V_{CC} = 5V, \, t_r = t_f = 20 \, \text{ns}, \, C_L = 50 \, \text{pF}$

| Symbol                            | Parameter                   | Conditions                                        | Min | Тур | Max | Units |

|-----------------------------------|-----------------------------|---------------------------------------------------|-----|-----|-----|-------|

| t <sub>CW</sub>                   | Chip Enable to Write        | T <sub>J</sub> = 25°C                             | 35  | 15  |     | ns    |

|                                   | Enable Setup Time           | T <sub>J</sub> = 125°C                            | 50  | 20  |     | ns    |

| t <sub>AW</sub>                   | Address to Write            | T <sub>J</sub> = 25°C                             | 35  | 15  |     | ns    |

|                                   | Enable Setup Time           | T <sub>J</sub> = 125°C                            | 50  | 20  |     | ns    |

| t <sub>WW</sub>                   | Write Enable Width          | T <sub>J</sub> = 25°C                             | 400 | 225 |     | ns    |

|                                   |                             | T <sub>J</sub> = 125°C                            | 450 | 250 |     | ns    |

| t <sub>DW</sub>                   | Data to Write Enable        | T <sub>J</sub> = 25°C                             | 390 | 225 |     | ns    |

|                                   | Setup Time                  | T <sub>J</sub> = 125°C                            | 430 | 250 |     | ns    |

| $t_{WD}$                          | Write Enable to Data        | T <sub>J</sub> = 25°C                             | 0   | -10 |     | ns    |

|                                   | Hold Time                   | T <sub>J</sub> = 125°C                            | 0   | -15 |     | ns    |

| t <sub>WA</sub>                   | Write Enable to Address     | T <sub>J</sub> = 25°C                             | 0   | -10 |     | ns    |

|                                   | Hold Time                   | T <sub>J</sub> = 125°C                            | 0   | -15 |     | ns    |

| t <sub>WC</sub>                   | Write Enable to Chip Enable | T <sub>J</sub> = 25°C                             | 50  | 30  |     | ns    |

|                                   | Hold Time                   | T <sub>J</sub> = 125°C                            | 75  | 40  |     | ns    |

| t <sub>1H</sub> , t <sub>0H</sub> | Logical "1", Logical "0"    | $R_L = 10k, T_J = 25^{\circ}C$                    |     | 275 | 500 | ns    |

|                                   | Levels into 3-STATE         | $C_L = 10 \text{ pF, } T_J = 125^{\circ}\text{C}$ |     | 325 | 600 | ns    |

| t <sub>H1</sub> , t <sub>H0</sub> | 3-STATE to Logical "1" to   | $R_L = 10k, T_J = 25^{\circ}C$                    |     | 325 | 600 | ns    |

|                                   | Logical "0" Level           | $C_L = 50 \text{ pF, } T_J = 125^{\circ}\text{C}$ |     | 375 | 700 | ns    |

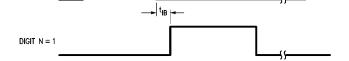

| t <sub>IB</sub>                   | Interdigit Blanking Time    | T <sub>J</sub> = 25°C                             | 5   | 10  |     | μs    |

|                                   |                             | T <sub>J</sub> = 125°C                            | 10  | 20  |     | μs    |

| $f_{MUX}$                         | Multiplex Scan Frequency    | T <sub>J</sub> = 25°C                             |     | 350 |     | Hz    |

|                                   |                             | T <sub>J</sub> = 125°C                            |     | 250 |     | Hz    |

| C <sub>IN</sub>                   | Input Capacitance           | (Note 6)                                          |     | 5   | 7.5 | pF    |

| C <sub>OUT</sub>                  | 3-STATE Output Capacitance  | (Note 6)                                          |     | 30  | 50  | pF    |

|                                   |                             |                                                   |     |     |     |       |

Note 5: AC Parameters are guaranteed by DC correlated testing.

Note 6: Capacitance is guaranteed by periodic testing.

# **Switching Time Waveforms**

#

$T=1/f_{\hbox{\scriptsize MUX}}$

# **Typical Performance Characteristics**

DIGIT N

Segment outputs if shorted to ground will exceed maximum power dissipation of the device

$\ensuremath{\text{V}_{\text{CE}}}$  is the saturation voltage of the digit drive transistor.

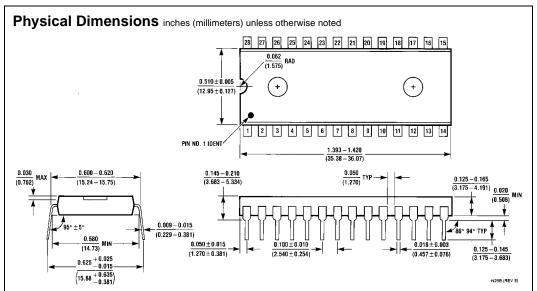

28-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.600" Wide Package Number N28B

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com