# OKI Semiconductor ML7005

## DTMF Transceiver

## **GENERAL DESCRIPTION**

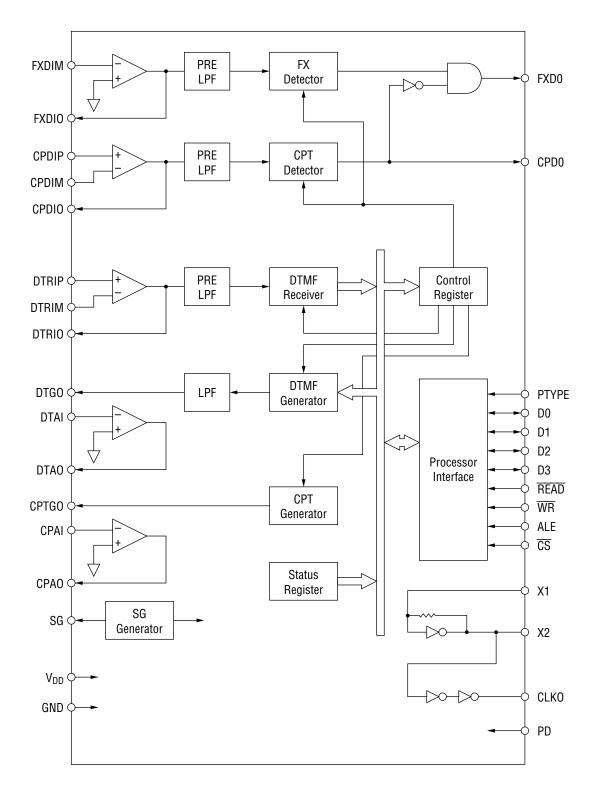

The ML7005 is a multi-functional DTMF transceiver LSI with built-in a DTMF signal generator, a DTMF signal receiver, a call progress tone generator, a call progress tone detector, and a FAX (FX) signal detector.

Each functional block can be controlled by an external MCU via a 4-bit processor interface. The ML7005 does not contains a modem. However, the DTMF system data transmission is possible at less than 66 bps by setting the DTMF receiver to the high-speed detection mode. The ML7005 operates with low-power consumption and is suitable for remote control systems, especially for ACR (Automatic Cost Routing) controllers.

## FEATURES

- Wide range of power supply voltage : +2.7 V to +5.5 V

- Low power consumption Operating mode :  $4.0 \text{ mA} (V_{DD} = 3 \text{ V}) \text{ Typ.}$ Operating mode :  $5.0 \text{ mA} (V_{DD} = 5 \text{ V}) \text{ Typ.}$ Power down mode :  $1 \mu \text{A} \text{ Typ.}$

- The 4-bit processor interface supports both the Intel processor mode in which a read signal and a write signal are used independently of each other, and the Motorola processor mode in which a read signal and a write signal are used in common.

- The DTMF receiver can select either the high-speed detection mode (signal repeat time: more than 60 ms) or the normal detection mode (signal repeat time: more than 90 ms).

- Built-in call progress tone generator

- Built-in FAX signal (FX: 1300 Hz) detector

- The DTMF signal generator, DTMF signal detector, call progress tone generator, and call progress tone detector can operate concurrently.

- Built-in 3.579545 MHz crystal oscillator circuit

- Package :

32-pin plastic SSOP (SSOP32-P-430-1.00-K) (Product name: ML7005MB)

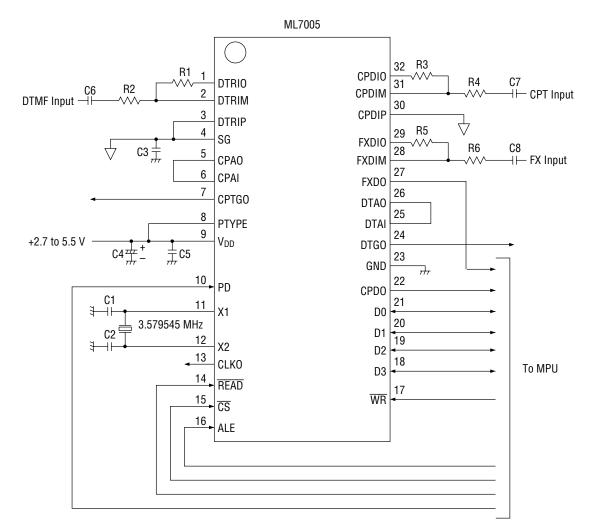

## **BLOCK DIAGRAM**

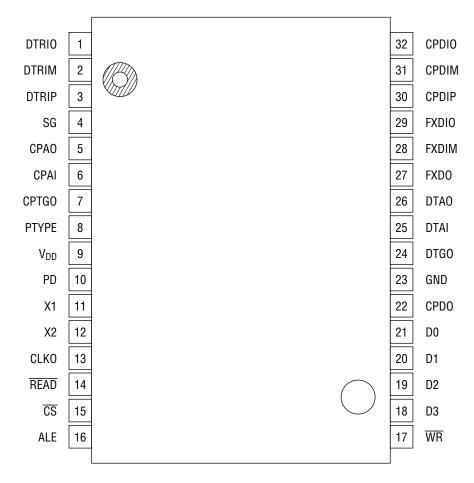

## **PIN CONFIGURATION (TOP VIEW)**

**32-Pin Plastic SSOP**

## **PIN DESCRIPTION**

| Pin | Symbol          | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

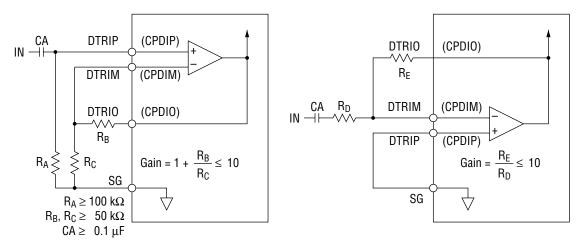

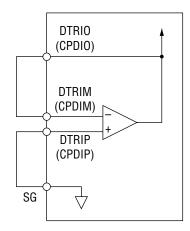

| 1   | DTRIO           | 0    | Output pin for DTMF signal receiver input amplifier.<br>See the figure 8 for adjusting the receive signal level. See the figure 10 when the<br>DTMF signal receiver is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2   | DTRIM           | I    | Inverting input pin for DTMF signal receiver input amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3   | DTRIP           | I    | Non-inverting input pin for DTMF signal receiver input amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4   | SG              | 0    | Output pin for signal ground.<br>The output voltage is half of $V_{DD}$ .<br>Connect SG and GND by a 1 $\mu$ F capacitor.<br>This pin goes to a high impedance state when in power down mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

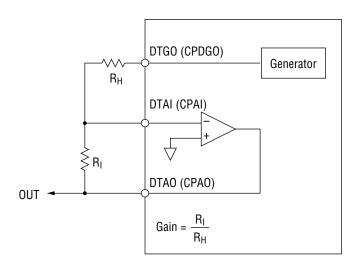

| 5   | CPAO            | 0    | Output pin for amplifier used for adjusting the transmit output level of CPT (Call Progress Tone) signal generator. The non-inverting input of this amplifier is internally connected to SG. See the figure 11 for adjusting the transmit signal level. When this amplifier is not used, the CPAO pin should be shorted to the CPAI pin.                                                                                                                                                                                                                                                                                                                         |

| 6   | CPAI            | I    | Inverting input pin for amplifier used to adjust the transmit level of the CPT signal generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7   | CPTGO           | 0    | Analog output pin for CPT signal generator.<br>The tone amplitude is approximately - 3 dBm. The transmit signal level can be<br>changed by using the CPAO and CPAI pins. See the figure 11 for adjusting the<br>transmit signal level. Control the ON/OFF of CPT transmission by using CPGC of<br>the control register.                                                                                                                                                                                                                                                                                                                                          |

| 8   | PTYPE           | I    | Input pin for selecting the processor mode.<br>This selection determines the functions of $\overline{READ}$ , $\overline{CS}$ , ALE, $\overline{WR}$ , D1 and D0 pins.<br>When this pin is "1", the Intel processor mode is selected. When this pin is "0", the<br>Motorola processor mode (MSM7524-compatible) is selected. This pin should be<br>fixed at "0" or "1".                                                                                                                                                                                                                                                                                          |

| 9   | V <sub>DD</sub> | —    | Power supply pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10  | PD              | 1    | Input pin for controlling the power down mode.<br>When this pin is set to "1", the entire LSI enters the power down mode and each<br>functional operation stops. The DC level of the analog output pin becomes undefined<br>The digital output pins (FXD0, CPD0) and status register indicate a non-detection<br>state. At that time, the control register CR and DTMF transmit register DTMFT are<br>cleared. ("0" is written)<br>The internal circuits (timer, etc. for each detector) also are reset.<br>After turning on the power, set this pin to "1" to reset the LSI before using this LSI.<br>When this pin is set to "0", the normal operation starts. |

| 11  | X1              | 1    | X1 and X2 are connected to a 3.579545 MHz crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12  | X2              | 0    | See "Oscillation Circuit" of the FUNCTIONAL DESCRIPTION for reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 13  | CLKO            | 0    | 3.579545 MHz clock output pin. This pin can drive one ML7005 device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pin     | Symbol  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14      | READ    | Ι    | Input pin for processor interface.<br>When PTYPE is "1" (Intel processor mode) :<br>This pin is the read control input pin. When this pin is set to "0", data in the<br>specified register is output to the bus lines (D3 to D0). At that time, $\overline{CS}$ must be "0".<br>See the figure 4 for processor interface timing.<br>When PTYPE is "0" (Motorola processor mode) :<br>This pin is the clock input pin (equivalent to SCLK of the MSM7524).<br>When in Write mode, data in D3 to D0 is written to the specified register at the<br>falling edge of the READ signal.<br>When in Read mode, data in the specified register is output to D3 to D0 when the<br>READ signal is "1", and D3 to D0 is opened when the READ signal is "0".<br>The READ signal is not necessarily a periodical signal.<br>See the figure 5 for processor interface timing. |

| 15      | CS      | Ι    | Chip select input pin for processor interface.<br>When the $\overline{CS}$ signal is "0", read and write operations are possible.<br>When the $\overline{CS}$ signal is "1", read and write operations are impossible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16      | ALE     | 1    | Input pin for processor interface.<br>When PTYPE is "1" (Intel processor mode) :<br>This pin is the address latch enable input pin.<br>The register address data in D1 to D0 is latched at the falling edge of ALE.<br>When PTYPE is "0" (Motorola processor mode) :<br>This pin is the address data input pin (equivalent to AD0 of the MSM7524).<br>When this pin is "1", data can be written to the control register (CR) and data can<br>be read from the status register (STR).<br>When this pin is "0", data can be written to the DTMF transmit register (DTMFT)<br>and data can be read from the DTMF receive register (DTMFR).                                                                                                                                                                                                                         |

| 17      | WR      | 1    | Input pin for processor interface.<br>When PTYPE is "1" (Intel processor mode) :<br>This pin is the Write control input.<br>Data in the data bus lines (D3 to D0) is written to the specified register. At that time,<br>$\overline{CS}$ must be "0".<br>When PTYPE is "0" (Motorola processor mode) :<br>This is the signal input pin for controlling the Read and Write modes<br>(equivalent to R/W of the MSM7524).<br>When this pin is "1", the LSI enters the Read mode. When this pin is "0", the LSI<br>enters the Write mode.                                                                                                                                                                                                                                                                                                                           |

| 18 - 21 | D3 - D0 | I/0  | 4-bit data bus I/O pins for processor interface.<br>When PTYPE is "1" (Intel processor mode), D1 and D0 are also used for addressing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 22      | CPDO    | 0    | Digital output pin for CPT detector.<br>When a 400 Hz signal is input to the CPDIP and CPDIM pins, this pin is "1".<br>When the DOEN register is "0", this pin is fixed at "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 23      | GND     | —    | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 24      | DTGO    | 0    | Analog output pin for DTMF signal generator.<br>The tone amplitude is approximately - 9.0 dBm for a low group and approximately<br>- 7.0 dBm for a high group. The transmit signal level can be changed by using the<br>DTAI and DTAO pins. See the figure 11 for adjusting the transmit signal level.<br>Control the ON/OFF of signal transmission by using MFC of the control register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pin | Symbol | Туре | Description                                                                                                                                                                                                                                                                                                                                            |

|-----|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25  | DTAI   | I    | Inverting input pin for operational amplifier used for adjusting the transmit output<br>level of the DTMF signal generator. The non-inverting input of this amplifier is<br>internally connected to SG. See the figure 11 for adjusting the transmit signal level.<br>When this amplifier is not used, the DTAO pin should be shorted to the DTAI pin. |

| 26  | DTAO   | 0    | Output pin for operational amplifier used for adjusting the transmit output level of the DTMF signal generator.                                                                                                                                                                                                                                        |

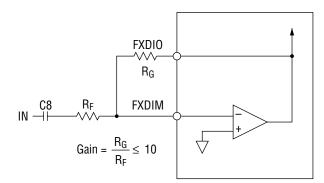

| 27  | FXDO   | 0    | Digital output pin for FAX signal (FX) detector.<br>When a 1300 Hz signal is input to the FXDIM, this pin is "1".<br>When a call progress tone (CPT) is received (CPD0="1"), this pin is forced to be "0".<br>When the DOEN register is "0", this pin is fixed at "0".                                                                                 |

| 28  | FXDIM  | I    | Inverting input pin for input amplifier used for detecting the FAX signal (FX).<br>See the figure 9 for adjusting the receive signal level.<br>When the FX detector is not used, the FXDIM pin should be shorted to the FXDIO pin.                                                                                                                     |

| 29  | FXDIO  | 0    | Output pin for input amplifier used for detecting the FAX signal (FX).                                                                                                                                                                                                                                                                                 |

| 30  | CPDIP  | Ι    | Non-inverting input pin for input amplifier used for detecting the CPT.<br>See the figure 8 for adjusting the receive signal level.<br>When the CPT detector is not used, see the figure 10.                                                                                                                                                           |

| 31  | CPDIM  | I    | Inverting input pin for input amplifier used for detecting the CPT.                                                                                                                                                                                                                                                                                    |

| 32  | CPDIO  | 0    | Output pin for input amplifier used for detecting the CPT.                                                                                                                                                                                                                                                                                             |

# ABSOLUTE MAXIMUM RATINGS

| Parameter            | Symbol           | Condition                       | Rating                        | Unit |  |

|----------------------|------------------|---------------------------------|-------------------------------|------|--|

| Power Supply Voltage | V <sub>DD</sub>  | Ta = 25°C                       | -0.3 to +7.0                  | V    |  |

| Input Voltage        | VI               | With respect to GND             | -0.3 to V <sub>DD</sub> + 0.3 | V    |  |

| Storage Temperature  | T <sub>stg</sub> | —                               | -55 to +150                   | °C   |  |

| Output Short Current | I <sub>SHT</sub> | Short to V <sub>DD</sub> or GND | 35                            | mA   |  |

| Power Dissipation    | PD               | —                               | 100                           | mW   |  |

# **RECOMMENDED OPERATING CONDITIONS**

|                 | Parameter                    | Symbol           | Condition                                               | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------|------------------|---------------------------------------------------------|------|------|------|------|

| Po              | wer supply voltage           | V <sub>DD</sub>  | —                                                       | 2.7  | 3.6  | 5.5  | V    |

| Op              | erating Temperature Range    | T <sub>OP</sub>  | —                                                       | -30  |      | +85  | °C   |

| Inp             | ut Clock Frequency Deviation | f <sub>CLK</sub> | An external clock is applied to                         | -0.1 |      | +0.1 | %    |

| Inp             | out Clock duty               | DUTY             | X1                                                      | 40   |      | 60   | %    |

| X1,             | , X2 Load Capacitance        | C1, C2           | —                                                       | 18   | 20   | 22   | pF   |

| SG              | Bypass Capacitance           | C3               | SG - GND                                                | 1    |      | _    |      |

| V <sub>DI</sub> | D Bypass Capacitance         | C4               | V <sub>DD</sub> - GND                                   | 10   | —    |      | μF   |

|                 |                              | C5               |                                                         | 0.1  | _    | _    |      |

| Dig             | jital Input Rise Time        | T <sub>IR</sub>  | PD, $\overline{\text{READ}}$ , $\overline{\text{CS}}$ , |      |      | 50   |      |

| Dig             | jital Input Fall Time        | T <sub>IF</sub>  | ALE, WR, D3 to D0                                       |      | —    | 50   | ns   |

| Dig             | jital Ouput Load Capacitance | C <sub>DL1</sub> | FCDO, CPDO, D3 to D0                                    |      |      | 40   | ~F   |

|                 |                              | C <sub>DL2</sub> | CLKO                                                    |      |      | 20   | pF   |

|                 | Frequency Deviation          |                  | +25°C ±5°C                                              | -100 |      | +100 |      |

| stal            | Temperature Characteristics  | _                | -30°C to +85°C                                          | -100 | _    | +100 | ppm  |

| Crystal         | Equivalent Series Resistance | _                | _                                                       |      |      | 90   | Ω    |

|                 | Load Capacitance             | _                |                                                         |      | 16   | _    | pF   |

## **ELECTRICAL CHARACTERISTICS**

#### **DC and Digital Interface Characteristics**

|                               | onaraott          |                     | (                        | $V_{DD} = 2.7$         | to 5.5 V,              | Ta = -30 1             | to +85°C) |

|-------------------------------|-------------------|---------------------|--------------------------|------------------------|------------------------|------------------------|-----------|

| Parameter                     | Symbol            | Condition or        | Applicable pin           | Min.                   | Тур.                   | Max.                   | Unit      |

|                               | I <sub>DD1</sub>  | V <sub>DD</sub> = 2 | .7 to 5.5 V              | —                      |                        | 9.0                    |           |

| Dowar Supply Current          |                   | Operating Mode      | $V_{DD} = 3 V$           | —                      | 4.0                    | —                      | mA        |

| Power Supply Current          |                   |                     | $V_{DD} = 5 V$           | —                      | 5.0                    | —                      |           |

|                               | I <sub>DD2</sub>  | Power Down M        | ode                      | _                      | 1                      | 40                     | μA        |

| Digital Input Voltage         | V <sub>IH</sub>   |                     |                          | 0.7 V <sub>DD</sub>    |                        | V <sub>DD</sub>        | V         |

|                               | V <sub>IL</sub>   | _                   | —                        | 0.0                    |                        | 0.3V <sub>DD</sub>     | v         |

| Digital Input Current         | I <sub>IH</sub>   | $V_I = V_{DD}$      |                          | -10                    | 0                      | +10                    | ۸         |

|                               | ١ <sub>١L</sub>   | $V_I = 0 V$         | -10                      | 0                      | +10                    | μA                     |           |

| Digital Output Voltage        | V <sub>OH</sub>   | Other than          | $I_{0H} = -100 \ \mu A$  | $V_{DD}-0.2$           | V <sub>DD</sub> – 0.06 | V <sub>DD</sub>        |           |

|                               | V <sub>OL</sub>   | CLK0                | l <sub>0L</sub> = 100 μA | 0.0                    | 0.06                   | 0.2                    | V         |

|                               | V <sub>OHCK</sub> |                     |                          | $V_{DD} - 0.5$         |                        | V <sub>DD</sub>        |           |

|                               | V <sub>OLCK</sub> | CLKO, CL $\leq$ 20p | IL                       | 0.0                    |                        | 0.5                    |           |

| Analog Input Resistance       | R <sub>IN</sub>   | *1                  |                          | —                      | 10                     | _                      | MΩ        |

| Analog Output DC Potential    | V <sub>SG</sub>   | \$G<br>*2           |                          | V <sub>DD</sub> /2–0.1 | V <sub>DD</sub> /2     | V <sub>DD</sub> /2–0.1 | V         |

|                               | V <sub>AO</sub>   |                     |                          | _                      | V <sub>DD</sub> /2     | —                      | v         |

| Analog Output Load Resistance | R <sub>OUT</sub>  | *3                  |                          | 20                     |                        | _                      | KΩ        |

\*1 DTRIM, DTRIP, CPAI, DTAI, FXDIM, CPDIP, CPDIM

\*2 DTRIO, CPAO, CPTGO, DTGO, DTAO, FXDIO, CPDIO

\*3 DTRIO, CPAO, CPTGO, DTGO, DTAO, FXDIO, CPDIO, SG

## **AC CHARACTERISTICS**

#### AC Characteristics 1 DTMF Signal Generator

|                               |                   |                 | (                     | V <sub>DD</sub> = 2.7 | to 5.5 V, | Ta = -30 | to +85°C) |

|-------------------------------|-------------------|-----------------|-----------------------|-----------------------|-----------|----------|-----------|

| Parameter                     | Symbol            | Condition       |                       | Min.                  | Тур.      | Max.     | Unit      |

| DTMF Tone Transmit Amplitude  | V <sub>DTTL</sub> |                 | Low Group Tone        | -10.5                 | -9.0      | -7.5     | dPm       |

|                               | V <sub>DTTH</sub> |                 | High Group Tone       | -8.5                  | -7.0      | -5.5     | dBm<br>*1 |

| Tone Transmit Amplitude Ratio | V <sub>DTDF</sub> | Measured at     | $V_{DTTH} - V_{DTTL}$ | 1.0                   | 2.0       | 3.0      | dB        |

| Tone Frequency Accuracy       | f <sub>DDT</sub>  | DTGO            | To Nominal            | -1.5                  | _         | +1.5     | %         |

|                               |                   |                 | Frequency             | -1.5                  |           | +1.5     | 70        |

| Total Harmonic Distortion     | THDDT             |                 | Harmonics -           |                       | -40       | -23      | ЧD        |

|                               | INDDT             |                 | Fundamental           |                       | -40       | -23      | dB        |

|                               | V <sub>S1</sub>   | With respect to | 4kHz to 8kHz          |                       | P–51      | P–20     |           |

| Out of Pond Courious          | V <sub>S2</sub>   | output signal   | 8kHz to 12kHz         |                       | P60       | P-40     | ٩D        |

| Out-of-Band Spurious          | N.                | level measured  | 12 kHz to each        |                       | P-75      | D 00     | dB        |

|                               | V <sub>S3</sub>   | at DTGO         | 4 kHz band            |                       | F=70      | P60      |           |

\*1 0dBm = 0.775 Vrms (For all AC characteristics)

|                           | 0                  | · · · ·                 | (V <sub>DD</sub> = 2.7 | ′ to 5.5 V, | Ta = -30 | to +85°C) |

|---------------------------|--------------------|-------------------------|------------------------|-------------|----------|-----------|

| Parameter                 | Symbol             | Condition               | Min.                   | Тур.        | Max.     | Unit      |

| Tone Transmit Amplitude   | V <sub>CPT</sub>   | —                       | -4                     | -2.5        | -1       | dBm       |

| Output Frequency          | fcpt               | —                       | 380                    | 400         | 420      | Hz        |

| Total Harmonic Distortion | THD <sub>CPT</sub> | Harmonics - Fundamental | _                      | -39         | -23      | dB        |

## AC Characteristics 2 Call Progress Tone (CPT) Generator

# AC Characteristics 3 Call Progress Tone (CPT) Detector $(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}. \text{ Ta})$

|                          | an rogic           |                             |                                  | (V <sub>DD</sub> = 2.7 | to 5.5 V, | Ta = -30 | to +85°C) |

|--------------------------|--------------------|-----------------------------|----------------------------------|------------------------|-----------|----------|-----------|

| Parameter                | Symbol             | Con                         | Min.                             | Тур.                   | Max.      | Unit     |           |

| CPT Detect Amplitude     | N .                | 2.7 V ≤                     | $\leq V_{DD} \leq 5.5 \text{ V}$ | -46                    | —         | -6       |           |

|                          | VDETCP             | 4.5 V ≤                     | $\leq V_{DD} \leq 5.5 \text{ V}$ | -46                    | —         | 0        | dBm       |

| CPT Non-detect Amplitude | V <sub>REJCP</sub> | f <sub>in</sub> = 350 to 45 | 50 Hz at CPDIO                   |                        |           | -60      |           |

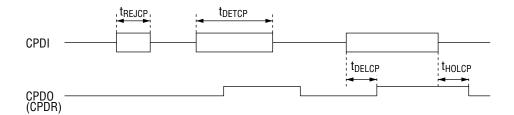

| Time to Detect           | <b>t</b> DETCP     |                             | Detect                           | 30                     |           | _        |           |

| Time to Reject           | t <sub>REJCP</sub> |                             | Non-detect                       | —                      | —         | 10       | ms        |

| CPT Detect Delay Time    | t <sub>DELCP</sub> | See Fi                      | auro 1                           | 10                     | 18        | 30       |           |

| CPT Detect Hold Time     | t <sub>HOLCP</sub> | 566 FI                      | gure 1.                          | 10                     | 18        | 30       | ms        |

| CPT Detect Frequency     | <b>f</b> DETCP     |                             |                                  | 350                    |           | 450      | Hz        |

| ODT Non-datast Fraguanov | 4                  |                             |                                  | 530                    | _         | _        | U-7       |

| CPT Non-detect Frequency | † <sub>RETCP</sub> | _                           |                                  |                        | _         | 290      | Hz        |

Figure 1 CPT Detect Timing

## AC Characteristics 4 FAX Signal (FX) Detector

$(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, \text{ Ta} = -30 \text{ to } +85^{\circ}\text{C})$

| Parameter               | Symbol             | Condition                                |                                                            | Min. | Тур. | Max. | Unit |  |

|-------------------------|--------------------|------------------------------------------|------------------------------------------------------------|------|------|------|------|--|

| EV Dataat Amplituda     | N                  | $2.7 \text{ V} \leq \text{V}_{\text{E}}$ | $_{ m OD} \leq 5.5 \  m V$                                 | -40  |      | -6   |      |  |

| FX Detect Amplitude     | V <sub>DETFX</sub> | $4.5 \text{ V} \leq \text{V}_{\text{D}}$ | $4.5 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$ |      | _    | 0    | dBm  |  |

| FX Non-detect Amplitude | V <sub>REJFX</sub> | f <sub>in</sub> = 1280 to 1320           | ) Hz at FXDIO                                              | _    | _    | -60  |      |  |

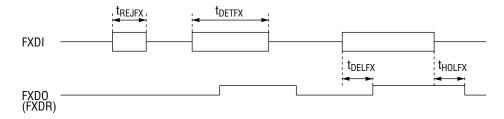

| Time to Detect          | t <sub>DETFX</sub> | D                                        | etect                                                      | 65   |      | —    |      |  |

| Time to Reject          | t <sub>REJFX</sub> | N                                        | on-detect                                                  | —    | _    | 30   |      |  |

| FX Detect Delay Time    | t <sub>DELFX</sub> | Coo Figur                                | ro 0                                                       | 35   | 50   | 65   | ms   |  |

| FX Detect Hold Time     | tHOLFX             | See Figur                                | re 2.                                                      | 35   | 50   | 65   |      |  |

| FX Detect Frequency     | f <sub>DETFX</sub> |                                          |                                                            | 1280 | _    | 1320 | Hz   |  |

| EV Non-detect Frequency |                    |                                          |                                                            |      |      | _    | Hz   |  |

| FX Non-detect Frequency | † <sub>REJFX</sub> | —                                        |                                                            | _    |      | 1200 |      |  |

| $(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, 1a = -30 \text{ to } +85^{\circ}$ |                      |           |                         |                                  |      |      |      |      |

|-----------------------------------------------------------------------------|----------------------|-----------|-------------------------|----------------------------------|------|------|------|------|

| Parameter                                                                   | Symbol               |           | Cor                     | ndition                          | Min. | Тур. | Max. | Unit |

| DTMF Detect Amplitude                                                       | V <sub>DETDT1</sub>  |           | 2.7 V                   | $\leq V_{DD} \leq 5.5 \text{ V}$ | -42  |      | -10  |      |

| DTMF Delect Amplitude                                                       | V <sub>DETDT2</sub>  |           | 4.5 V                   | $\leq V_{DD} \leq 5.5 \text{ V}$ | -42  |      | 0    | dBm  |

| DTMF Non-detect Amplitude                                                   | V <sub>REJDT</sub>   |           | Per Freque              | ency at DTRIO                    |      |      | -60  |      |

| Detect Frequency                                                            | f <sub>DETDT</sub>   |           |                         |                                  | -1.8 |      | +1.8 |      |

| Non datast Frequency                                                        | f                    |           | To Nomin                | al Frequency                     | 3.8  | —    | —    | %    |

| Non-detect Frequency                                                        | f <sub>REJDT</sub>   |           |                         |                                  |      |      | -3.8 |      |

| Level Twist                                                                 | VTWIST               |           | V <sub>High</sub> Group | o - V <sub>Low</sub> Group       | -6.0 | _    | +6.0 |      |

| Noise to Signal Ratio                                                       | V <sub>N/S</sub>     |           | N/S (N : 0              | .3 to 3.4 kHz)                   |      | -12  | —    | dB   |

| Dial Tone Rejection Ratio                                                   | V <sub>REJDT</sub>   |           | 360 t                   | o 440 Hz                         | —    | 45   | —    |      |

| Cignal Danstition Time                                                      | t <sub>CYCDT0</sub>  |           |                         | DTTIM = "1"                      | 60   | _    | _    |      |

| Signal Repetition Time                                                      | t <sub>CYCDT1</sub>  |           |                         | DTTIM = "0"                      | 90   | —    | —    |      |

| Time to Detect                                                              | t <sub>DETDT0</sub>  | ]         | Dataat                  | DTTIM = "1"                      | 35   | _    | _    |      |

|                                                                             | t <sub>DETDT1</sub>  |           | Detect                  | DTTIM = "0"                      | 49   | _    | _    |      |

| Time to Deject                                                              | t <sub>REJDT0</sub>  |           | Non datas               | DTTIM = "1"                      | _    | —    | 10   |      |

| Time to Reject                                                              | t <sub>REJDT1</sub>  | Non-detec |                         | DTTIM = "0"                      |      | _    | 24   |      |

| Interdigit Dayon Time                                                       | t <sub>POSDT0</sub>  |           |                         | DTTIM = "1"                      | 21   | —    | —    |      |

| Interdigit Pause Time                                                       | tposdt1              | *1        |                         | DTTIM = "0"                      | 30   | _    | —    |      |

| -                                                                           | t <sub>BRKDT10</sub> |           | <u>SP</u> = "1"         | DTTIM = "1"                      |      | _    | 0.4  | ms   |

| Accontable Dran Out Time                                                    | t <sub>BRKDT11</sub> |           | (Before outpu           | t) DTTIM = "0"                   |      | _    | 0.4  |      |

| Acceptable Drop Out Time                                                    | t <sub>BRKDT20</sub> | ]         | <u>SP</u> = "0"         | DTTIM = "1"                      |      |      | 3    |      |

|                                                                             | t <sub>BRKDT21</sub> |           | (During outpu           | t) DTTIM = "0"                   |      | _    | 10   |      |

| Data at Dalay Time                                                          | t <sub>DELDT0</sub>  | 1         |                         | DTTIM = "1"                      | 12   | 26   | 37   |      |

| Detect Delay Time                                                           | t <sub>DELDT1</sub>  | ]         |                         | DTTIM = "0"                      | 24   | 41   | 49   |      |

| Dataat Llaid Tima                                                           | t <sub>HOLDTO</sub>  | 1         |                         | DTTIM = "1"                      | 15   | 20   | 27   |      |

| Detect Hold Time                                                            | t <sub>HOLDT1</sub>  | 1         |                         | DTTIM = "0"                      | 24   | 28   | 35   |      |

| SP Delay Time                                                               | t <sub>SP</sub>      | 1         | D                       | TTIM = "1", "0"                  | 0.2  | 0.6  | 1.0  |      |

|                                                                             |                      |           |                         |                                  |      |      |      |      |

## **AC Characteristics 5 DTMF Receiver**

$(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, \text{ Ta} = -30 \text{ to } +85^{\circ}\text{C})$

\*1 See the figure 3 for timing.

The input level includes the entire range indicated in  $V_{DETDT1}$  and  $V_{DETDT2}$ . The input frequency includes the entire range indicated in  $f_{DETDT}$ .

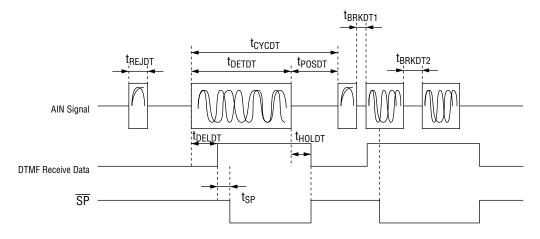

#### Timing When DTMF is received

Figure 3 Timing When DTMF is Received

t<sub>DETDT</sub>: Time to Detect

When Time to Detect is the specified value of t<sub>DETDT</sub> or more, the DTMF signal is normally received.

- t<sub>REJDT</sub>: Time to Reject When Time to Reject is the specified value of t<sub>REJDT</sub> or less, the input signal is ignored and the SP and DTMF receive data are not output.

- t<sub>POSDT</sub>: Interdigit Pause When there is no input signal for the period of t<sub>POSDT</sub> or more, the DTMF receive data and  $\overline{SP}$  are reset. Even if the receive data is changed, when Interdigit Pause Time is the value of t<sub>POSDT</sub> or less (including the change without Drop Out),  $\overline{SP}$  remains at "0" and the DTMF receive data may maintain its initial value.

#### t<sub>BRKDT1</sub> : Acceptable Drop Out Time 1 Acceptable Drop Out Time 1 is applied between when the input signal comes and when SP becomes "0". Even if there is no input signal for the period of t<sub>BRKDT1</sub> or less, the SP and DTMF receive data are normally output.

- $t_{BRKDT2} : Acceptable Drop Out Time 2$  $Acceptable Drop Out Time 2 is applied when <math>\overline{SP}$  is "0" (when receive data is output). Even if there is no input signal during signal reception for the period of  $t_{BRKDT2}$  or less,  $\overline{SP}$  and DTMF receive data are not reset.

- t<sub>CYCDT</sub>: Signal Repetition Time Signal Repetition Time should be the specified value of t<sub>CYCDT</sub> or more so that a signal is normally received.

- t<sub>DELDT</sub>: Detect Delay Time The DTMF receive data is output with a delay of the specified value of t<sub>DELDT</sub> after the input signal appears.

- $t_{HOLDT}$ : Detect Hold Time The  $\overline{SP}$  and DTMF receive data outputs stop with a delay of the specified value of  $t_{HOLDT}$  after the input signal disappears.

- $t_{SP}: SP \ Delay \ Time \\ The \ \overline{SP} \ data \ is \ output \ with \ a \ delay \ of \ the \ specified \ value \ of \ t_{SP} \ after \ the \ DTMF \ receive \\ data \ is \ output. \ The \ DTMF \ receive \ data \ should \ be \ latched \ after \ detecting \ the \ fall \ of \ \overline{SP}.$

|                                     |                  |                                                                         | $V_{DD} = 2.7$ | to 5.5 V, | Ta = -30 | to +85°C) |

|-------------------------------------|------------------|-------------------------------------------------------------------------|----------------|-----------|----------|-----------|

| Parameter                           | Symbol           | Condition                                                               | Min.           | Тур.      | Max.     | Unit      |

| Address Data Setup Time             | t <sub>AL</sub>  | —                                                                       | 80             | —         |          | ns        |

| Address Data Hold Time              | t <sub>LA</sub>  | —                                                                       | 30             | —         |          | ns        |

| ALE Signal Time                     | t <sub>LL</sub>  | —                                                                       | 80             | —         | —        | ns        |

| Chip Select Setup Time before Read  | t <sub>CRS</sub> | —                                                                       | 30             |           |          | ns        |

| Chip Select Hold Time after Read    | t <sub>CRH</sub> | —                                                                       | 30             | —         |          | ns        |

| READ Data Output Delay Time         | t <sub>RD</sub>  | $V_{OL} \leq 0.4 \text{ V}, \text{ V}_{OH} \geq V_{DD} - 0.4 \text{ V}$ | 0              | 90        | 180      | ns        |

| Data Float Time after Read          | t <sub>RDF</sub> | —                                                                       | 5              | 37        | 60       | ns        |

| <b>READ</b> Signal Time             | t <sub>RW</sub>  | —                                                                       | 200            |           |          | ns        |

| Chip Select Setup Time before Write | t <sub>CWS</sub> | —                                                                       | 30             |           |          | ns        |

| Chip Select Hold Time after Write   | t <sub>CWH</sub> | —                                                                       | 30             | —         |          | ns        |

| WR Signal Time                      | t <sub>WW</sub>  | —                                                                       | 140            | —         |          | ns        |

| Data Setup Time before Write        | t <sub>DW</sub>  | _                                                                       | 80             | _         | _        | ns        |

| Data Hold Time                      | t <sub>WD</sub>  | _                                                                       | 30             | _         | _        | ns        |

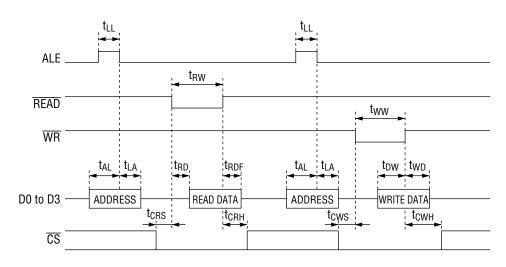

## Processor Interface Charactceristics (Intel Processor Mode)

Figure 4 Processor Interface Timing (Intel Processor Mode : PTYPE="1")

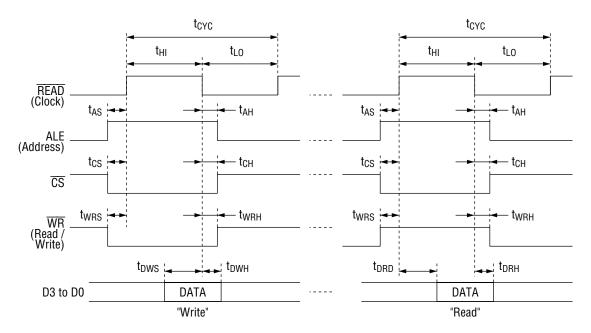

## Processor Interface Characteristics (Motorola Processor Mode)

$(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, \text{ Ta} = -30 \text{ to } +85^{\circ}\text{C})$

| Parameter                 |                             | Symbol           |                                                 | Condition                                                 | Min. | Тур. | Max. | Unit |

|---------------------------|-----------------------------|------------------|-------------------------------------------------|-----------------------------------------------------------|------|------|------|------|

| <b>READ</b> Signal Period |                             | tcyc             |                                                 |                                                           | 1    |      |      | μs   |

| READ Signal Pulse Width   |                             | t <sub>HI</sub>  |                                                 | "H" period                                                | 200  |      |      |      |

| NEAD Siyilai Fi           |                             | t <sub>LO</sub>  |                                                 | "L" period                                                | 200  | —    | _    |      |

| ALE                       | SETUP Time                  | t <sub>AS</sub>  |                                                 | $ALE \rightarrow \overline{READ}$                         | 80   | —    | _    | 1    |

| ALE                       | HOLD Time                   | t <sub>AH</sub>  |                                                 | $\overline{\text{READ}} \rightarrow \text{ALE}$           | 20   | —    | _    |      |

| <del>CS</del> -           | SETUP Time                  | tcs              |                                                 | $\overline{\text{CS}} \rightarrow \overline{\text{READ}}$ | 80   |      | —    |      |

|                           | HOLD Time                   | t <sub>CH</sub>  |                                                 | $\overline{\text{READ}} \rightarrow \overline{\text{CS}}$ | 20   | —    | —    |      |

| WR                        | SETUP Time                  | t <sub>WRS</sub> | See $\overline{WR} \rightarrow \overline{READ}$ |                                                           | 80   | —    | —    | ns   |

| Wh                        | HOLD Time                   | t <sub>WRH</sub> | Figure 5                                        | $\overline{\text{READ}} \rightarrow \overline{\text{WR}}$ | 20   | —    | _    |      |

| D3 to D0                  | SETUP Time                  | t <sub>DWS</sub> |                                                 | D3 to D0 $\rightarrow \overline{\text{READ}}$             | 80   |      | —    |      |

| (Write)                   | HOLD Time                   | t <sub>DWH</sub> |                                                 | $\overline{\text{READ}} \rightarrow \text{D3 to D0}$      | 30   |      | —    |      |

|                           |                             |                  |                                                 | $\overline{\text{READ}} \rightarrow \text{D3 to D0}$      |      |      |      |      |

| D3 to D0                  | Delay Time t <sub>DRD</sub> |                  |                                                 | $V_{OL} \le 0.4 V$ ,                                      | 0    |      | 180  |      |

| (Read)                    |                             |                  |                                                 | $V_{OH} \ge V_{DD} - 0.4 V$                               |      |      |      |      |

|                           | Hold Time                   | t <sub>DRH</sub> |                                                 | D3 to D0 $\rightarrow \overline{\text{READ}}$             | 5    | 37   | 60   |      |

## **REGISTER DESCRIPTION**

#### **Register Interface Description**

The ML7005 contains a 4-bit DTMF transmit data register (DTMFT), a 4-bit DTMF receive data register (DTMFR), a 4-bit control register (CR), and a 4-bit status register (STR). The DTMFT and CR registers are for Write-only and the DTMFR and STR registers are for Read-only. When the PTYPE pin is "1", accessing the registers is possible in the Intel processor mode. When the PTYPE pin is "0", accessing the registers is possible in the Motorola processor mode. In the Intel processor mode (PTYPE="1"), when  $\overline{CS}$  is "0", data can be written to the DTMFT and CR registers by fetching data from D3 to D0 at the rising edge of the  $\overline{WR}$  signal. When  $\overline{CS}$  is "0", the contents of DTMFR and STR can be transferred to D3 to D0 by setting READ to "0". In the Motorola processor mode (PTYPE="0"), when  $\overline{CS}$  and  $\overline{WR}$  are "0", data can be written to the DTMFT and the DTMFT and CR registers by fetching D3 to D0 data and ALE at the falling edge of READ. When  $\overline{CS}$  is "0" and  $\overline{WR}$  is "1", the contents of DTMFR and STR are transferred to D3 to D0 by latching ALE at the rising edge of  $\overline{READ}$ .

When the PD pin is set to "1" the DTMFT and CR registers are reset.

| Register<br>name | Accessing<br>(address) in Intel<br>processor mode |    | Accessing in<br>Motorola<br>processor mode |    | Description        |

|------------------|---------------------------------------------------|----|--------------------------------------------|----|--------------------|

| name             | D1                                                | D0 | ALE                                        | WR |                    |

| DTMFT            | 0                                                 | 0  | 0                                          | 0  | Writing to DTMFT   |

| DTMFR            | 0                                                 | 1  | 0                                          | 1  | Reading from DTMFR |

| CR               | 1                                                 | 0  | 1                                          | 0  | Writing to CR      |

| STR              | 1                                                 | 1  | 1                                          | 1  | Reading from STR   |

#### Table 1 Outline of Registers

Note: The contents of the DTMFT and CR registers cannot be read.

#### Table 2 Register Names

| Register name | Register name D3 |       | D1   | D0   |  |

|---------------|------------------|-------|------|------|--|

| DTMFT         | DTT3             | DTT2  | DTT1 | DTT0 |  |

| DTMFR         | DTR3             | DTR2  | DTR1 | DTR0 |  |

| CR            | CPGC             | DTTIM | DOEN | MFC  |  |

| STR           | SP               | FXDR  | CPDR | DETF |  |

#### **DTMFT and DTMFR Registers**

16 kinds of DTMF transmit signals can be determined by setting the DTMFT register.

16 kinds of DTMF receive signals can be monitored from the DTMFR register.

The table 3 shows the DTMF signal codes.

Even if the DTMF transmit code is changed while the DTMF signal is being transmitted (MFC="1"), the output frequency is not changed.

| DTT3 | DTT2 | DTT1 | DTT0 | DIGIT | Low group   | High group  |  |  |

|------|------|------|------|-------|-------------|-------------|--|--|

| DTR3 | DTR2 | DTR1 | DTR0 | Dian  | signal (Hz) | signal (Hz) |  |  |

| 0    | 0    | 0    | 1    | 1     | 697         | 1209        |  |  |

| 0    | 0    | 1    | 0    | 2     | 697         | 1336        |  |  |

| 0    | 0    | 1    | 1    | 3     | 697         | 1477        |  |  |

| 0    | 1    | 0    | 0    | 4     | 770         | 1209        |  |  |

| 0    | 1    | 0    | 1    | 5     | 770         | 1336        |  |  |

| 0    | 1    | 1    | 0    | 6     | 770         | 1477        |  |  |

| 0    | 1    | 1    | 1    | 7     | 852         | 1209        |  |  |

| 1    | 0    | 0    | 0    | 8     | 852         | 1336        |  |  |

| 1    | 0    | 0    | 1    | 9     | 852         | 1477        |  |  |

| 1    | 0    | 1    | 0    | 0     | 941         | 1336        |  |  |

| 1    | 0    | 1    | 1    | *     | 941         | 1209        |  |  |

| 1    | 1    | 0    | 0    | #     | 941         | 1477        |  |  |

| 1    | 1    | 0    | 1    | A     | 697         | 1633        |  |  |

| 1    | 1    | 1    | 0    | В     | 770         | 1633        |  |  |

| 1    | 1    | 1    | 1    | С     | 852         | 1633        |  |  |

| 0    | 0    | 0    | 0    | D     | 941         | 1633        |  |  |

Table 3 DTMF Signal Code List

## **Control Register CR**

| D3   | D3 D2 |      | D0  |  |  |

|------|-------|------|-----|--|--|

| CPGC | DTTIM | DOEN | MFC |  |  |

| Bit No. | Name  | Description                                                                                                                                                                                                                                                                                 |

|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D3      | CPGC  | This bit is used to control the ON/OFF of call progress tone transmitting.<br>"0" : The GPTGO output is OFF and the SG level is output.<br>"1" : The GPTGO output is ON and CPT is output.                                                                                                  |

| D2      | DTTIM | This bit is used to control the detect time of DTMF receiver.<br>"0" : Normal detect "1" : High-speed detect<br>When there is enough time, set to the normal detect mode (DTTIM = "0") because the<br>high-speed detect mode sometimes causes erroneous detection by noise or voice signal. |

| D1      | DOEN  | This bit is used to control the call progress tone detector and FX detector.<br>"0" : The CPDO and FXDO output pins and CPDR and FXDR registers are fixed to "0".<br>"1" : The CPDO and FXDO output pins and CPDR and FXDR registers become valid.                                          |

| D0      | MFC   | This bit is used to control the ON/OFF of DTMF transmit output.<br>"0" : The DTGO output is OFF and the SG level is output.<br>"1" : The DTGO output is ON and the DTMF signal is output.                                                                                                   |

## Status Register STR

| D3 | D3 D2 |      | D0   |  |  |

|----|-------|------|------|--|--|

| SP | FXDR  | CPDR | DETF |  |  |

| Bit No. | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| D3      | SP   | This bit is used to indicate whether the DTMF receive signal is being received.<br>"0" : Indicates that the valid DTMF signal is being received.<br>"1" : Indicates that the DTMF signal is not being received.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| D2      | FXDR | This bit is used to indicate whether the FAX signal (FX) is being received.<br>"0" : Indicates that the FAX signal (FX) is not being received.<br>"1" : Indicates that the valid FAX signal (FX: 1300 Hz) is being received.<br>When a call progress tone is received (CPD0="1"), this bit is forced to be "0".<br>When the DOEN register is "0", this bit also is fixed at "0". This bit has the same<br>function as that of the FXDO.                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| D1      | CPDR | This bit is used to indicate whether the call progress tone is being received.<br>"0" : Indicates that the call progress tone is not being received.<br>"1" : Indicates that the valid call progress tone (400 Hz) is being received.<br>When the DOEN register is "0", this bit is fixed at "0". This bit has the same function<br>as that of the CPDO pin.                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| DO      | DETF | This is a flag to indicate that a detector has changed its status from a non-detect state to a detect state.         This bit is "1" when:         (1) SP is changed from "1" to "0",         (2) FXDR is changed from "0" to "1", or         (3) CPDR is changed from "0" to "1".         This bit remains "0" even if a 1300 Hz or 400 Hz signal is input, because the FXDR and CPDR are fixed at "0" when the DOEN regsiter is "0".         When the processor has read the status register, this bit is reset to "0".         When the processor does not read the status register after a signal is detected, this bit is "0" after the detected signal disappears. |  |  |  |  |  |  |

## FUNCTIONAL DESCRIPTION

#### **Oscillation Circuit**

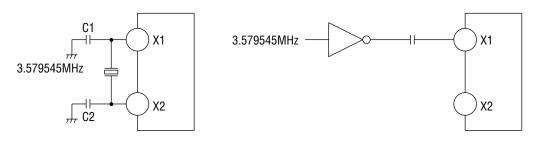

The X1 and X2 should be connected by a 3.579545 MHz crystal.

When the load capacitance of the crystal is 16pF, X1 and GND should be connected by a 20 pF capacitor, and X2 and GND also should be connected by a 20 pF capacitor.

If necessary, an external clock should be input to X1 via a 1000 pF capacitor, and X2 should be left open.

Figure 6 Crystal Connection Figure 7 External Clock Connection

#### **DTMF Receiver, CPT Detector Input Level Adjustment**

Adjust the input level according to the method shown in the figure 8. Determine the value of a usable resistor so that the levels of the outputs (DTIO, CPDIO) of each amplifier at a maximum input level are less than the maximum detect level described in the AC Characteristics.

Figure 8 DTMF, CPT Input Level Adjustment

#### **FX Detector Input Level Adjustment**

Adjust the input level according to the method shown in the figure 9.

Determine the value of a usable resistor so that the output level of FXDIO is less than the maximum detect level described in the AC Characteristics.

Figure 9 FX Input Level Adjustment

#### Processing the Input Pin when the DTMF Receiver and CPT Detector are not Used

Process the Input pin according to the method shown in the figure 10.

Figure 10 Processing the Unused Input Pin

## Adjusting the Analog Output Level

Adjust the analog output level according to the method shown in the figure 11.

$R_I/R_H \le 1.6$  is always required when  $V_{DD} \ge 4.5$  V.

In the case of  $R_I / R_H > 1$ , if  $R_I / R_H = A$ , the maximum analog output load resistance is 20\*A (k $\Omega$ ). If  $V_{DD}$  is less than 4.5 V,  $R_I / R_H \le 1$  is required.

Figure 11 Analog Output Level Adjustment

## **Concurrent Operation of 4 Functions**

The DTMF signal generator, DTMF signal detector, call progress tone generator, and call progress tone detector can operate concurrently.

When both the DTMF signal generator and call progress tone generator operate concurrently, the DTMF signal sometimes cannot be detected if the receive level of the DTMF signal is less than -36 dBm.

## **Register Settings for Each Mode**

An example of register settings for each mode is shown below.

| Mode         | Description                     | intel pro |     | orola<br>essor<br>ode | D3  | D2 | D1 | D0 | Active<br>register |

|--------------|---------------------------------|-----------|-----|-----------------------|-----|----|----|----|--------------------|

|              |                                 | D1, D0    | ALE | WR                    |     |    |    |    | register           |

| Power ON     | (1) Wait until power supply is  |           |     | _                     |     |    |    | _  |                    |

|              | stabilized                      |           |     |                       |     | _  | _  |    |                    |

|              | (2) PD pin = "1"                |           |     |                       |     |    |    |    |                    |

|              | (internal circuit is reset)     |           |     |                       |     |    |    |    |                    |

|              | (3) Wait 200 µs or more         |           | _   | _                     | _   |    | —  | —  |                    |

|              | (4) PD pin = "0"                | —         | _   | _                     | _   | _  | —  | —  | —                  |

|              | (5) CR setting                  | 10        | 1   | 0                     | Х   | Х  | Х  | Х  | CR                 |

| DTMF Detect  | (1) Detect timing setting       | 10        | 1   | 0                     | 0   | 1  | 0  | 0  | CR                 |

| (High Speed) | (2) STR monitoring              | 11        | 1   | 1                     | 1   | 0  | 0  | 0  | STR                |

|              | (when not detected)             | 11        | 1   | I                     |     | 0  | 0  | U  |                    |

|              | (3) STR monitoring              | 11        | 1   | 1                     | 0   | 0  | 0  | 1  | STR                |

|              | (when detected)                 | 11        | 1   |                       | 0   | 0  | 0  | I  | JIN                |

|              | (4) DTMF receive data reading   | 01        | 0   | 1                     | Х   | Х  | Х  | Х  | DTMFR              |

|              | (5) STR monitoring (when        | 11        | 1   | 1                     | 0   | 0  | 0  | 0  | STR                |

|              | detected and after reading STR) |           |     |                       |     |    |    |    | JIN                |

|              | (6) STR monitoring (after       | 11        | 1   | 1                     | 1   | 0  | 0  | 0  | STR                |

|              | making the input signal OFF)    | 11        | 1   |                       | ' ' | 0  | 0  | 0  | 511                |

| CPT Detect   | (1) CPT detect enable setting   | 10        | 1   | 0                     | 0   | 0  | 1  | 0  | CR                 |

|              | (2) STR monitoring              | 11        | 1   | 1                     | 1   | 0  | 0  | 0  | STR                |

|              | (when not detected)             |           |     |                       |     |    |    |    |                    |

|              | (3) STR monitoring              | 11        | 1   | 1                     | 1   | 0  | 1  | 1  | STR                |

|              | (when detected)                 |           | I   | I                     | Ι   | U  | I  | 1  | JIN                |

|              | (4) STR monitoring (when        | 11        | 1   | 1                     | 1   | 0  | 1  | 0  | STR                |

|              | detected and after reading STR) |           | 1   | I                     | 1   | 0  | 1  | 0  | 511                |

| DTMF         | (1) DTMF transmit data setting  | 00        | 0   | 0                     | Х   | Х  | Х  | Х  | DTMFT              |

| Transmit     | (2) DTMF transmit ON            | 10        | 1   | 0                     | 0   | 0  | 0  | 1  | CR                 |

|              | (3) Wait transmit ON time       |           |     | —                     | _   |    | —  | —  |                    |

|              | (4) DTMF transmit OFF           | 10        | 1   | 0                     | 0   | 0  | 0  | 0  | CR                 |

|              | (5) Wait transmit OFF time      |           | _   | _                     | _   |    | —  | —  |                    |

|              | (6) To transmit next data,      | _         |     |                       |     |    |    |    | _                  |

|              | return to (1)                   |           |     |                       |     |    |    |    |                    |

| CPT Transmit | (1) CPT transmit ON             | 10        | 1   | 0                     | 1   | 0  | 0  | 0  | CR                 |

|              | (2) Wait transmit ON time       | —         |     |                       |     |    | —  | —  |                    |

|              | (3) CPT transmit OFF            | 10        | 1   | 0                     | 0   | 0  | 0  | 0  | CR                 |

## Table 4 Register Setting

## APPLICATION CIRCUIT EXAMPLE

Note :  $\downarrow$  indicates connection to the SG pin.

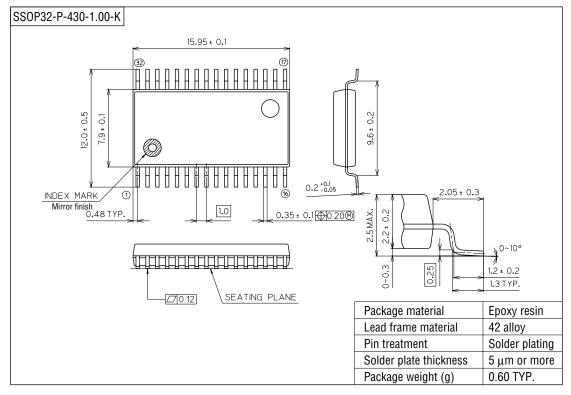

## PACKAGE DIMENSIONS

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, TQFP, LQFP, SOJ, QFJ (PLCC), SHP, and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person on the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 1999 Oki Electric Industry Co., Ltd.