# 4096 x 1-BIT STATIC RAM Processed to MIL-STD-883, Method 5004, Class B

MKB4104 (P/J/E)-84/85

## FEATURES

- $\square$  Extended operating temperature range (-55°C  $\leq$  T\_A  $\leq$  125°C)

- □ Combination static storage cells and dynamic control circuitry for truly high performance

| Part Number | Access Time | Cycle Time |  |  |

|-------------|-------------|------------|--|--|

| 4104(J)-84  | 250ns       | 385ns      |  |  |

| 4104(J)-85  | 300ns       | 510ns      |  |  |

□ Average power dissipation less than 150mW

#### DESCRIPTION

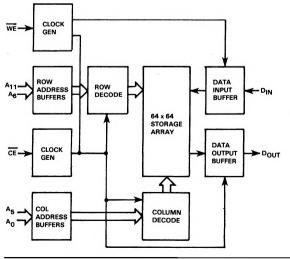

The Mostek MKB4104 is a high performance static random access memory organized as 4096 one bit words. The MKB4104 combines the best characteristics of static and dynamic memory techniques to achieve a TTL compatible, 5 volt only, high performance, low

## FUNCTIONAL DESCRIPTION

- □ Standby power dissipation less than 53mW

- □ Single +5V power supply (5% tolerance)

- □ Fully TTL compatible

Fanout:

- 2 Standard TTL

- 2 Schottky TTL

12 - Low Power Schottky TTL

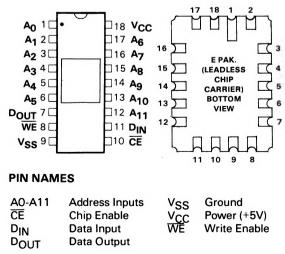

- □ Standard 18 pin DIP

- Leadless chip carrier (E package) available for high density applications

- Ruggedized for use in severe military environments

power memory device. It utilizes advanced circuit design concepts and an innovative state-of-the-art N-channel silicon gate process specially tailored to provide static data storage with the performance (speed and power) of dynamic RAMs. Since the storage cell is static the device may be stopped indefinitely with the CE clock in the off (Logic 1) state.

## **PIN CONNECTIONS**

## **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on any pin relative to V <sub>SS</sub> | 1.0V to +7.0V  |

|------------------------------------------------|----------------|

| Operating Temperature T <sub>A</sub> (Ambient) |                |

| Storage Temperature (Ambient)(Ceramic)         | 65°C to +150°C |

| Power Dissipation                              | 1 Watt         |

| Short Circuit Output Current                   |                |

| 10                                             |                |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability

#### **RECOMMENDED DC OPERATING CONDITIONS<sup>6</sup>**

$(-55^{\circ}C \leq T_{\Delta} \leq +125^{\circ}C)$

| SYM             | PARAMETER                    | MIN  | ТҮР | MAX  | UNITS | NOTES |

|-----------------|------------------------------|------|-----|------|-------|-------|

| V <sub>CC</sub> | Supply Voltage               | 4.75 | 5.0 | 5.25 | V     | 1     |

| V <sub>SS</sub> | Supply Voltage               | 0    | 0   | 0    | V     | 1     |

| VIH             | Logic "1" Voltage All Inputs | 2.4  |     | 7.0  | V     | 1     |

| VIL             | Logic "0" Voltage All Inputs | -1.0 |     | .65  | V     | 1     |

#### DC ELECTRICAL CHARACTERISTICS

$(-55^{\circ}C \le T_{A} \le +125^{\circ}C) (V_{CC} = 5.0 \text{ volts} \pm 5\%)$

| SYM             | PARAMETER                                       | MIN | MAX | UNITS | NOTES |

|-----------------|-------------------------------------------------|-----|-----|-------|-------|

| ICC1            | Average V <sub>CC</sub> Power Supply Current    |     | 27  | mA    | 2     |

| ICC2            | Standby V <sub>CC</sub> Power Supply Current    |     | 10  | mA    | 3     |

| Ι <u>Ι</u>      | Input Leakage Current (Any Input)               | -10 | 10  | μA    | 4     |

| lol             | Output Leakage Current                          | -10 | 10  | μA    | 3,5   |

| VOH             | Output Logic "1" Voltage $I_{OUT} = -500 \mu A$ | 2.4 |     | V     | 11    |

| V <sub>OL</sub> | Output Logic "-" Voltage I <sub>OUT</sub> = 5mA |     | 0.4 | V     | 11    |

## **AC ELECTRICAL CHARACTERISTICS**

(-55°C  $\leq$  T<sub>A</sub>  $\leq$  +125°C) (V<sub>CC</sub> = +5.0 volts  $\pm$  5%)

| SYM            | PARAMETER          | MIN | ТҮР | MAX | NOTES |

|----------------|--------------------|-----|-----|-----|-------|

| CI             | Input Capacitance  |     | 4pF | 6pF | 14    |

| с <sub>О</sub> | Output Capacitance |     | 7pF | 7pF | 14    |

#### NOTES:

- All voltages referenced to VSS 1

- 2 ICC1 is related to precharge and cycle times. Guaranteed maximum values for ICC1 are at minimum cycle time

- 3. Output is disabled (open circuit), CE is at logic 1.

- All device pins at 0 volts except pin under test at  $0 \le V_{IN} \le 5.5 V (V_{CC} 5V)$ 4.

- 5 OV  $\leq$  VOUT  $\leq$  +5.5V (VCC \_ 5V) 6. During power up, CE and WE must be at VIH for minimum of 2ms after VCC reaches 4.75V, before a valid memory cycle can be accomplished.

- 7 Measured with load circuit equivalent to 2 TTL loads and CL 100pF

- 8 If WE follows after  $\overline{\text{CE}}$  by more than  $t_{WS},$  then data out may not remain open circuited

- 9. Determined by user. Total cycle time cannot exceed tCF max.

- 10. Data-in set-up time is referenced to the later of the two failing clock edges CE or WE

- 11. AC measurements assume tj 5ns. Timing points are taken at .8V and 2.0V on inputs and .8V and 2.0V on the output. Transition times are also taken between these levels.

- 12. tc tcL + tp + 2tj.

- 13 The true level of the output in the open circuit condition will be determined totally by output load conditions. The output is guaranteed to be open circuit within tOFF

- 14. Effective capacitance calculated from the equation C  $1\Delta t$  with  $\Delta V$ equal to 3V and V<sub>CC</sub> nominal ۸V

- 15. For RMW, tCE tAC ' tWPL ' 5MOD 16. tC tAC ' tWPL ' 1P ' 3tj ' 1MOD

# AC ELECTRICAL CHARACTERISTICS AND RECOMMENDED OPERATING CONDITIONS<sup>6,11</sup>

| $(-55^{\circ}C \leq T_{\mu})$ | $x \le +125^{\circ}C) (V_{CC} =$ | = +5.0 Volts ± 5%) |

|-------------------------------|----------------------------------|--------------------|

|-------------------------------|----------------------------------|--------------------|

|                  | PARAMETER                             | MKB4104-84 |          | MKB4104-85 |      | 1     |       |

|------------------|---------------------------------------|------------|----------|------------|------|-------|-------|

| SYM              |                                       | MIN        | MAX      | MIN        | MAX  | UNITS | NOTES |

| tC               | Read or Write Cycle Time              |            | 410      | 510        |      | ns    | 12    |

| tAC              | Random Access                         |            | 250      |            | 300  | ns    | 7     |

| <sup>t</sup> CE  | Chip Enable Pulse Width               | 250        | 5000     | 300        | 5000 | ns    | 15    |

| tp               | Chip Enable Precharge Time            | 150        |          | 200        |      | ns    |       |

| <sup>t</sup> AH  | Address Hold Time                     | 135        |          | 165        | -    | ns    |       |

| tAS              | Address Set-Up Time                   | 0          |          | 0          |      | ns    |       |

| tOFF             | Output Buffer Turn-Off Delay          | 0          | 65       | 0          | 75   | ns    | 13    |

| tws              | Write Enable Set-Up Time              | 0          |          | 0          |      | ns    | 8     |

| <sup>t</sup> DHC | Data Input Hold Time Referenced to CE | 210        |          | 250        |      | ns    |       |

| <sup>t</sup> DHW | Data Input Hold Time Referenced to WE | 90         |          | 105        |      |       |       |

| tww              | Write Enabled Pulse Width             | 60         |          | 90         |      | ns    |       |

| tMOD             | Modify Time                           | 0          | 5000     | 0          | 5000 | ns    | 9     |

| tWPL             | WE to CE Precharge Lead Time          | 85         |          | 105        |      | ns    | 10    |

| tDS              | Data Input Set-Up Time                | 0          |          | 0          |      | ns    |       |

| twн              | Write Enable Hold Time                | 185        | <u> </u> | 225        |      | ns    |       |

| t <sub>T</sub>   | Transition Time                       | 5          | 50       | 5          | 50   | ns    |       |

| tRMW             | Read-Modify-Write Cycle Time          | 500        |          | 620        | T    | ns    | 16    |

| tRS              | Read Set-Up Time                      | 0          |          | 0          |      | ns    |       |

#### **DESCRIPTION (Continued)**

All input levels, including write enable ( $\overline{WE}$ ) and chip enable ( $\overline{CE}$ ) are TTL with a one level of 2.4 volts and a zero level of .65 volts. The push-pull output (no pull-up resistor required) delivers a one level of 2.4V minimum and a zero level of .4 volts maximum. The output has a fanout of 2 standard TTL loads or 12 low power Schottky loads.

The RAM employs an innovative static cell which occupies a mere 2.75 square mils ( $\frac{1}{2}$  the area of previous cells) and dissipates power levels comparable to CMOS. The static cell eliminates the need for refresh cycles and associated hardware thus allowing easy system implementation.

Power supply requirement of +5V combined with TTL compatibility on all I/O pins permits easy integration into large memory configurations. The single supply reduces capacitor count and permits denser packaging on printed circuit boards. The 5V only supply requirement and TTL compatible I/O makes this part an ideal choice for next generation +5V only micro-processors such as Mostek's Z80. The early write mode (WE active prior to CE) permits common 1/O operation, needed for Z80 interfacing, without external circuitry.

Reliability is greatly enhanced by the low power dissipation which causes a maximum junction rise of only 6.6° at 1.6 Megahertz operation. The MKB4104 was designed for the system designer and user who require the highest performance available along with Mostek's proven reliability.

## SUPPLEMENTAL DATA SHEET TO BE USED IN CONJUNCTION WITH MOSTEK MK4104(P/N) DATA SHEET