# MK44S80(N,X) -15/17/20

# 65,536-BIT FAST CMOS 16 K X 4 CACHE TAGRAM<sup>™</sup>

#### **ADVANCE DATA**

# FEATURES

- 16K x 4 FAST CMOS CACHE TAGRAM

- 15,17,20ns ADDRESS TO COMPARE ACCESS

- 10,12,14ns TAG DATA TO COMPARE ACCESS

- EQUAL ACCESS, READ/WRITE CYCLE TIMES

- FLASH CLEAR FUNCTION

- 24-PIN 300 MIL STANDARD PLASTIC DIP

# DESCRIPTION

The MK44S80 is a 65,536-bit CMOS Static TA-GRAM, organized as 16Kx4 using SGS-THOM-SON Microelectronics' advanced fast HCMOS process technology. This device is functionally compatible with the industry standard MK41S80 4Kx4 TAGRAM. All inputs and outputs are TTL compatible using a single 5V supply.

The MK44S80 provides full static operation, requiring no external clocks or refresh operations, and features a MATCH output for indicating either a cache hit or miss condition. The on-board 4-bit comparator compares RAM contents with current input (tag) data. The result on the MATCH pin is an active high match ("hit"), or active low for a "miss" condition. The MK44S80 offers a totem-pole MATCH output design for fast access times, allowing the MATCH pins of several devices to be gated together to provide an enable or acknowledge to the data cache or cache control logic (refer to Figure 2).

# PIN CONNECTION

| 24-Pin DIP or SOJ |    |   |         |   |    |       |

|-------------------|----|---|---------|---|----|-------|

| Ao                | 1  |   | •       |   | 24 | Vcc   |

| A 1               | 2  |   |         |   | 23 | A 13  |

| A <sub>2</sub>    | 3  |   |         |   | 22 | A 12  |

| A <sub>3</sub>    | 4  |   |         |   | 21 | A 11  |

| Α4                | 5  |   |         |   | 20 | A 10  |

| Α5                | 6  | E | MK44S80 |   | 19 | Ag    |

| A <sub>6</sub>    | 7  | C |         |   | 18 | CLR   |

| Α7                | 8  |   |         |   | 17 | DQ 3  |

| A <sub>8</sub>    | 9  |   |         |   | 16 | DQ2   |

| OE                | 10 |   |         |   | 15 | DQ 1  |

| WE                | 11 |   |         |   | 14 | DQO   |

| Vss               | 12 |   |         |   | 13 | MATCH |

|                   |    | L |         | J |    |       |

#### MK44S80 TRUTH TABLE

| WE | OE | CLR | MATCH   | MODE    |

|----|----|-----|---------|---------|

| Н  | Н  | Н   | Valid   | Compare |

| L  | Х  | Н   | Invalid | Write   |

| Н  | L  | н   | Invalid | Read    |

| X  | Х  | L   | Invalid | Clear   |

#### **PIN NAMES**

| A0-A13  | Address Inputs          |

|---------|-------------------------|

| DQ0-DQ3 | Data I/O <sub>0-3</sub> |

| MATCH   | Comparator Output       |

| OE      | Output Enable           |

| WE      | Write Enable            |

| CLR     | Ram Flash Clear         |

| Vcc,Vss | +5V, GND                |

#### **TAGRAM FUNCTION**

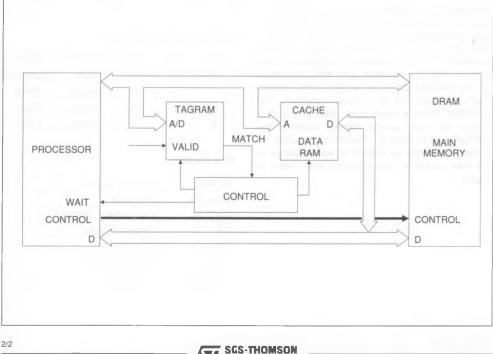

The MK44S80 is an SRAM based Cache Tag directory (hence the name TAGRAM). Figure 2 shows a general block diagram using a cache tag directory (TAGRAM) in a cache subsystem application. The system must detect whether the requested data resides in the cache data RAM, or if extended read cycles to main memory are necessary.

The MK44S80 features four modes of operation: Write, Read, Compare, and Clear. The MK44S80 incorporates an on-board 4 bit comparator that compares internal RAM contents with current (tag) input data. If the device is in the compare mode, and the comparator detects a "match", then the MATCH pin will go high for a hit condition. If a match is not detected by the comparator, then the MATCH pin drives low to denote a "miss" condition. Standard write/read operations are performed with Write (WE) and Output (OE) Enable inputs. Additionally, the device provides a Flash Clear operation via the CLR pin.

When a low level (VIL) is applied to the CLR input pin for the specified tore time, all RAM bits are set to a logic zero.

Compare data (internal RAM) can be read from the data pins by bringing Output Enable (OE) low. This will allow data stored in the memory array to be displayed at the Outputs (DQn -DQ3).

# **GENERAL CACHE SUB SYSTEM BLOCK DIAGRAM**

00100