MCM10147 MEMORIES

TRUTH TABLE

| MODE      | INPUT |     |    |     | OUTPUT |

|-----------|-------|-----|----|-----|--------|

|           | CET   | CE2 | WE | Din | Dout   |

| Write "0" | L     | L   | L  | L   | L      |

| Write "1" | L     | L   | L  | H   | L      |

| Read      | L     | Γ.  | н  | •   | 0      |

| Disabled  | н     | L   | 2  | φ   | L      |

|           | L     | н   |    | Φ   | L      |

PD = 415 mW typ/pkg

tAccess = 10 ns typ

## 128-1-Bit Random Access Memory

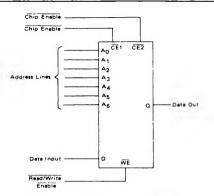

The MCM10147 is a 128-bit RAM organized as a 128-word by 1-bit array. This organization and the high speed of this MECL 10,000 device make the MCM10147 particularly useful in fast scratch pad, register file, and buffer memory applications. Full address decoding, and two Chip Enables (CE) are included in this device to permit simple memory expansion.

For writing Data (D) into this memory, both Chip Enables CE1 and CE2 are brought low, the address is presented at A0-A6, and the Read/Write Enable (WE) is taken low while Data is valid. To read a particular address, both Chip Enable inputs must again be low, but the Read/Write input is high (Data input disabled) while the location is addressed.

The two Chip Enables are provided for row or column selection of device packages in an expanded memory system. Either input can be used to select a particular row or column of stored data bits.

Open emitter outputs permit full wire-

Open emitter outputs permit full wire-ORing to data buses, with the output being held low when either Chip Enable is high. Internal input pulldown resistors are not used on this device. Unused inputs should be tied to VEE.