## Advance Information MC68176 2-BIT A/D CONVERTER IC

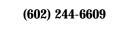

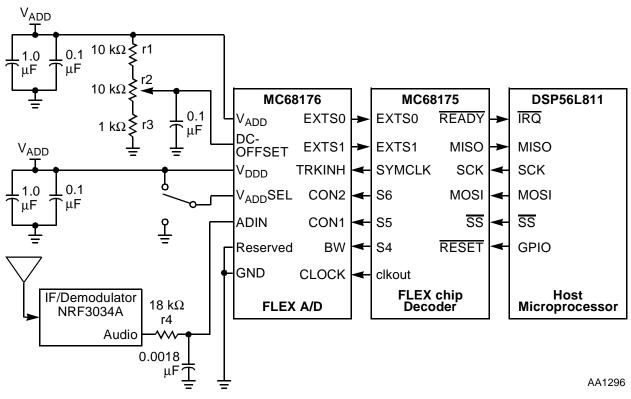

The MC68176 chip is part of a total solution available from Motorola for providing FLEX<sup>™</sup> paging capabilities in a low-power, low-cost system. Working in conjunction with standard paging receivers, the MC68176 takes the 4-level baseband audio signals from the receiver and performs 2-bit A/D using 8-bit DACs for peak and valley detection, passing the 2-bit digital signal directly to the MC68175 FLEX chip or MC68181 Roaming FLEX chip for further decoding and FLEX protocol handling. Received messages are then passed to the host microcontroller or microprocessor via the Serial Peripheral Interface (SPI). The host processor (running FLEXstack<sup>™</sup> software) interprets the data appropriately (as binary, alphanumeric or numeric message types), and handles all I/O and user interaction functions.

The FLEX paging protocol is the multi-speed, high-performance protocol adopted by leading service providers worldwide. FLEX protocol gives service providers the increased capacity, added reliability, and enhanced pager battery performance required today. It also provides an upward migration path to the service provider which is completely transparent to the end user.

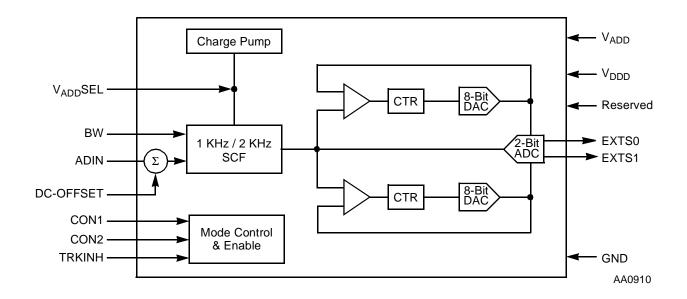

Figure 1 MC68176 Functional Block Diagram

This document contains information on a new product. Specifications and information herein are subject to change without notice.

### TABLE OF CONTENTS

| SECTION 1  | SIGNAL/CONNECTION DESCRIPTIONS | -1          |

|------------|--------------------------------|-------------|

| SECTION 2  | SPECIFICATIONS                 | 2-1         |

| SECTION 3  | PACKAGING                      | 3-1         |

| SECTION 4  | DESIGN CONSIDERATIONS 4        | I-1         |

| SECTION 5  |                                | 5-1         |

| APPENDIX A | DESCRIPTION OF OPERATION.      | <u>۱</u> -۱ |

### FOR TECHNICAL ASSISTANCE:

**Telephone:** 1-800-521-6274

Email: dsphelp@dsp.sps.mot.com

Internet: <u>http://www.motorola-dsp.com</u>

## **Data Sheet Conventions**

This data sheet uses the following conventions:

| OVERBAR      | Used to indicate a signal that is active when pulled low (For example, the $\overline{\text{RESET}}$ pin is active when low.) |                       |                           |                  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------|------------------|--|--|

| "asserted"   | Means that a high true (active high) signal is high or that a low true (active low) signal is low                             |                       |                           |                  |  |  |

| "deasserted" | Means that a high tru<br>signal is high                                                                                       | ıe (active high) sign | al is low or that a low t | rue (active low) |  |  |

| Examples:    | Signal/Symbol                                                                                                                 | Logic State           | Signal State              | Voltage          |  |  |

|              | PIN                                                                                                                           | True                  | Asserted                  | $V_{IL}/V_{OL}$  |  |  |

|              | PIN                                                                                                                           | False                 | Deasserted                | $V_{IH}/V_{OH}$  |  |  |

|              | PIN                                                                                                                           | True                  | Asserted                  | $V_{IH}/V_{OH}$  |  |  |

|              | PIN                                                                                                                           | False                 | Deasserted                | $V_{IL}/V_{OL}$  |  |  |

Note: Values for  $V_{IL}, V_{OL}, V_{IH},$  and  $V_{OH}$  are defined by individual product specifications.

MC68176 Technical Data Sheet

# FEATURES

- 2-bit A/D converter

- Supports FLEX Protocol with the MC68175 and MC68181 FLEX Decoder chips

- Peak and valley 8-bit DAC detectors compensate for signal strength variation

- Pin-selectable 2-Pole Butterworth Low Pass Filter

- BW = 0: 1 Khz  $\pm$  5% (-3 dB) (for 1600 symbols/second)

- BW = 1: 2 Khz  $\pm$  5% (-3 dB) (for 3200 symbols/second)

- 600 mV input voltage range  $@V_{ADD} = 2.7$  V and 1.8 V

- 100  $\mu$ A typical operating current @ V<sub>ADD</sub> = 2.7 V

- Three Modes of Operation:

- Fast Track mode

- Slow Track mode

- Hold Acquisition

- Standby mode for low power consumption

- -30 °C to 85 °C temperature range

- + 2 V and 3 V operation  $\pm$  10% for both  $V_{DDD}$  and  $V_{ADD}$

- Flexible supply mode (i.e.,  $V_{ADD}$  can be at 2 V and  $V_{DDD}$  can be at 3 V or vice-versa)

- For  $V_{ADD}$  = 2 V, an internal charge pump is enabled to provide higher voltages for some analog circuits.

- 14-pin SOIC package

# ADDITIONAL SUPPORT

FLEX System Software from Motorola is a family of software components for building worldclass products incorporating messaging capabilities. FLEXstack<sup>™</sup> Software is specifically designed to support the FLEX chip IC. FLEXstack Software runs on a product host processor and takes care of communicating with the FLEX chip IC and fully interpreting the codewords that are passed to the host from the FLEX chip IC.

## DOCUMENTATION

This document is the primary document supporting the MC68176 FLEX 2-bit A/D. Documentation is available from a local Motorola distributor, a Motorola semiconductor sales office, a Motorola Literature Distribution Center, or through the Motorola DSP home page on the Internet (the source for the latest information).

### Documentation

# SECTION 1

# SIGNAL/CONNECTION DESCRIPTIONS

## SIGNAL GROUPINGS

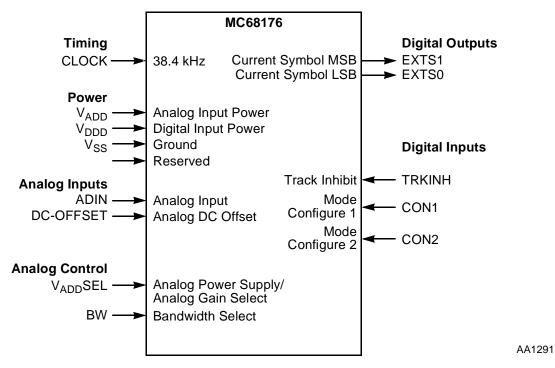

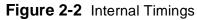

The input and output signals of the MC68176 are organized into six functional groups, as shown in **Table 1-1** and as illustrated in **Figure 1-1**.

| Functional Group          | Number of<br>Signals | Detailed<br>Description |

|---------------------------|----------------------|-------------------------|

| Power and Reserved Signal | 4                    | Table 1-2               |

| Timing                    | 1                    | Table 1-3               |

| Analog Inputs             | 2                    | Table 1-4               |

| Analog Controls           | 2                    | Table 1-5               |

| Digital Outputs           | 2                    | Table 1-6               |

| Digital Inputs            | 3                    | Table 1-7               |

### Table 1-1 MC68176 Functional Signal Groupings

Figure 1-1 on page 1-2 is a diagram of MC68176 signals by functional group.

Power

Figure 1-1 Signals Identified by Functional Group

## POWER

**Table 1-2** Power and Reserved Signal

| Signal Name      | Description                                                                    |  |  |  |

|------------------|--------------------------------------------------------------------------------|--|--|--|

| V <sub>ADD</sub> | <b>Power</b> — $V_{ADD}$ is the input power for the analog portion of the IC.  |  |  |  |

| V <sub>DDD</sub> | <b>Power</b> — $V_{DDD}$ is the input power for the digital portion of the IC. |  |  |  |

| V <sub>SS</sub>  | <b>Ground</b> —V <sub>SS</sub> is ground connection for the IC.                |  |  |  |

| Reserved         | Reserved—This pin must be connected to VSS to ensure proper operation          |  |  |  |

## TIMING

| Signal Name | Туре | Signal Description                                                                                                                               |

|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| CLOCK       |      | <b>Clock Input</b> —This is a 38.4 kHz 50% duty cycle clock, typically provided by CLKOUT on the MC68175 FLEX chip or MC68181 Roaming FLEX chip. |

### **Table 1-3**Timing Signal

# ANALOG INPUTS

| Signal Name | Туре  | Signal Description                                                                                                                                                                                                              |

|-------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADIN        | Input | <b>Analog Data In</b> —This is the 4-level baseband analog audio input signal to be digitized.                                                                                                                                  |

| DC-OFFSET   | Input | <b>DC Offset</b> —This analog input signal is the dc content of the analog input signal ADIN. This pin needs a dc voltage (identical to the IF dc voltage content) applied to it, to prevent clipping of the ADIN input signal. |

**Table 1-4**Analog Input Signals

## ANALOG CONTROL

| Signal Name          | Туре  | Signal Description                                                                                                                                                                                                                  |  |  |  |  |

|----------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| V <sub>ADD</sub> SEL | Input | $\label{eq:VADD} \begin{array}{l} \textbf{V}_{ADD} \ \textbf{Select} \\ - \text{If } V_{ADD} \ \text{is nominal 3 V, set } V_{ADD} \text{SEL to 0. If } V_{ADD} \ \text{is nominal 2 V, set } V_{ADD} \text{SEL to 1.} \end{array}$ |  |  |  |  |

|                      |       | This signal has two functions—to enable a charge pump when $V_{ADD}$ is 2 V, and to control the analog gain of the filter stage.                                                                                                    |  |  |  |  |

|                      |       | If $V_{ADD}$ SEL is 1, the charge pump is enabled, ensuring parts of the analog circuit have a higher supply.                                                                                                                       |  |  |  |  |

|                      |       | DDSEL also controls the gain of the filter stage:                                                                                                                                                                                   |  |  |  |  |

|                      |       | $V_{ADD}SEL = 0$ : gain = 3.656<br>$V_{ADD}SEL = 1$ : gain = 2.437                                                                                                                                                                  |  |  |  |  |

| BW                   | Input | <b>BandWidth Select</b> —This digital signal controls the cutoff frequency for the second-order low-pass Butterworth or Switched Capacitor filter:                                                                                  |  |  |  |  |

|                      |       | BW = 0: 1 kHz filter (for 1600 symbols/second)<br>BW = 1: 2 kHz filter (for 3200 symbols/second)                                                                                                                                    |  |  |  |  |

Table 1-5

Analog Control Signals

**Digital Outputs**

# **DIGITAL OUTPUTS**

| Signal<br>Name | Signal Type | Signal Description                                                                                                                                                                                           |

|----------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTS0-1        | Output      | Digitized Output bits—These are the gray-scale encoded digitizedrepresentation of ADIN. The transition levels are relative to themeasured peak and valley signal levels.EXTS0 = 1, EXTS1 = 0: 5/6 < ADIN < 1 |

### Table 1-6 Digital Output Signals

## **DIGITAL INPUTS**

| Signal<br>Name | Signal<br>Type | Signal Description                                                                                                                                                      |

|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CON0-1         | Input          | <b>Mode Configuration</b> —CON0 and CON1 specify the mode of operation for the MC68176.                                                                                 |

|                |                | CON0 = 0, CON1 = 0: Lower Power Standby mode                                                                                                                            |

|                |                | CON0 = 0, CON1 = 1: Fast Track mode                                                                                                                                     |

|                |                | CON0 = 1, $CON1 = 0$ : Hold mode                                                                                                                                        |

|                |                | CON0 = 1, CON1 = 1: Slow Track mode                                                                                                                                     |

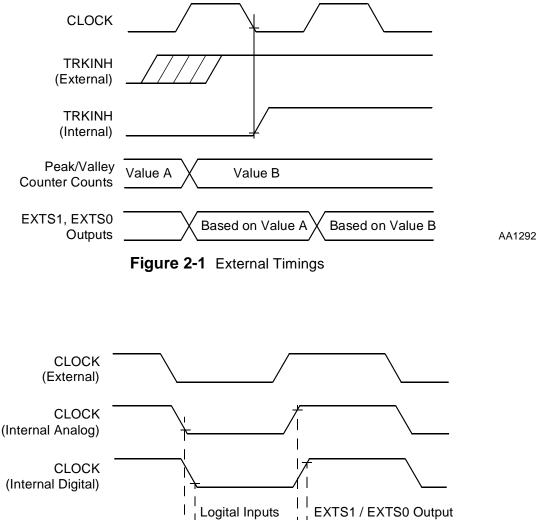

| TRKINH         | Input          | <b>Track Inhibit</b> —This signal controls the operation of the peak and valley audio signal strength detectors. TRKINH is synchronized with the falling edge of CLOCK. |

|                |                | TRKINH = 0: Enables peak and valley counters and enables decay.<br>TRKINH = 1: Disables peak and valley counters and disables decay.                                    |

|                |                |                                                                                                                                                                         |

Table 1-7

Digital Input Signals

Note: All digital signals are latched on the falling edge of CLOCK except  $V_{ADD}SEL$ .

dsp-

# SECTION 2

# **SPECIFICATIONS**

### INTRODUCTION

The MC68176 is fabricated in high density CMOS with Transistor-Transistor Logic (TTL) compatible inputs and outputs. The MC68176 specifications are preliminary and are from design simulations, and may not be fully tested or guaranteed at this early stage of the product life cycle. Finalized specifications will be published after full characterization and device qualifications are complete.

### MAXIMUM RATINGS

### CAUTION

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., GND,  $V_{DDD}$  or  $V_{ADD}$ ).

| Spec. | Rating                                                              | Symbol           | Value                | Unit |

|-------|---------------------------------------------------------------------|------------------|----------------------|------|

| M 1   | Supply Voltage                                                      | V <sub>CC</sub>  | -0.3 to +3.3         | V    |

| M 2   | All input voltages                                                  | V <sub>IN</sub>  | GND -0.5 to VCC +0.5 | V    |

| M 3   | Current drain per pin excluding $V_{\mbox{DD}}$ and $V_{\mbox{SS}}$ | Ι                | 10                   | mA   |

| M 4   | Operating temperature range                                         | T <sub>A</sub>   | -30 to +85           | °C   |

| M 5   | Storage temperature                                                 | T <sub>STG</sub> | -55 to +150          | °C   |

**Recommended Operating Conditions**

## **RECOMMENDED OPERATING CONDITIONS**

| Spec. | Characteristic                             | Symbol           | Min  | Тур  | Max  | Unit |

|-------|--------------------------------------------|------------------|------|------|------|------|

| 1     | Analog Supply Voltage ( $V_{ADD}SEL = 1$ ) | V <sub>ADD</sub> | 1.8  | 2.0  | 2.2  | V    |

| 2     | Analog Supply Voltage ( $V_{ADD}SEL = 0$ ) | V <sub>ADD</sub> | 2.7  | 3.0  | 3.3  | V    |

| 3     | Input Clock Frequency                      | CLOCK            | _    | 38.4 | —    | kHz  |

| 4     | Input Clock Duty Cycle                     | CLOCK            | 45   | 50   | 55   | %    |

| 5     | Operating Temperature                      | T <sub>A</sub>   | - 30 |      | + 85 | °C   |

Table 2-2

Recommended Operating Conditions

## **DC ELECTRICAL CHARACTERISTICS**

| Spec. | Characteristics                                                                         | Symbol            | Min                     | Тур | Max                  | Unit |

|-------|-----------------------------------------------------------------------------------------|-------------------|-------------------------|-----|----------------------|------|

| 6     | Output high voltage (I <sub>OH</sub> = – 0.3 mA, $V_{DDD}$ = 3.0 V ± 10%)               | V <sub>oh</sub>   | V <sub>DDD</sub> - 0.13 | —   | —                    | V    |

| 7     | Output high voltage ( $I_{OH} = -0.3 \text{ mA}$ , $V_{DDD} = 2.0 \text{ V} \pm 10\%$ ) | V <sub>oh</sub>   | V <sub>DDD</sub> – 0.3  | _   |                      | V    |

| 8     | Output low voltage ( $I_{OL} = 2 \text{ mA}$ ,<br>V <sub>DDD</sub> = 3.0 V $\pm$ 10%)   | V <sub>oL</sub>   | —                       | _   | 0.13                 | V    |

| 8     | Output low voltage ( $I_{OL} = 2 \text{ mA}$ ,<br>V <sub>DDD</sub> = 2.0 V $\pm$ 10%)   | V <sub>oL</sub>   | —                       | _   | 0.3                  | V    |

| 10    | Input high voltage                                                                      | V <sub>ih</sub>   | $0.8 \times V_{DDD}$    | —   | V <sub>DDD</sub>     | V    |

| 11    | Input low voltage                                                                       | V <sub>il</sub>   | - 0.3                   |     | $0.2 \times V_{DDD}$ | V    |

| 12    | Digital Internal Supply Current<br>( $V_{DDD} = 3 V$ ) $\pm 10\%$                       | IV <sub>DDD</sub> | —                       | 2.5 | 8.0                  | μΑ   |

| 13    | Digital Internal Supply Current<br>(V <sub>DDD</sub> = 2 V ± 10%)                       | IV <sub>DDD</sub> | —                       | 1.6 | 5.3                  | μA   |

| 14    | Analog Internal Supply Current<br>( $V_{ADD} = 3 V \pm 10\%, V_{ADD}SEL = 0$ )          | I <sub>SBY</sub>  | —                       | 110 | 220                  | μΑ   |

| 15    | Analog Internal Supply Current<br>( $V_{ADD} = 2V \pm 10\%$ , $V_{ADD}SEL = 1$ )        | I <sub>SBY</sub>  | —                       | 75  | 150                  | μΑ   |

| 16    | Standby Supply Current                                                                  | I <sub>SBY</sub>  | —                       |     | 1                    | μΑ   |

| 17    | Digital Input capacitance                                                               | C <sub>di</sub>   | —                       |     | 10                   | pF   |

| 18    | Analog Input capacitance                                                                | C <sub>ai</sub>   | —                       |     | 10                   | pF   |

| 19    | DC-OFFSET Range                                                                         | V <sub>DCO</sub>  | 0.0                     |     | V <sub>ADD</sub>     | V    |

**Table 2-3** DC Electrical Characteristics

### Peak and Valley DAC

## PEAK AND VALLEY DAC

| Spec. | Characteristic                     | Symbol | Min                       | Тур                       | Max                        | Unit       |

|-------|------------------------------------|--------|---------------------------|---------------------------|----------------------------|------------|

| 20    | Specification Deleted              |        |                           |                           |                            |            |

| 21    | DAC output voltage                 | _      | IV <sub>AG</sub> -128 LSB |                           | IV <sub>AG</sub> + 128 LSB | V          |

| 22    | Step Size (input<br>referred)      | LSB    | 0.336                     | $37 \times V_{ADD}$ / 255 | ± 1%                       | V          |

| 23    | Differential Linearity             |        |                           |                           | 1                          | LSB        |

| 24    | Min/Max Full Scale<br>Error        | _      | —                         | —                         | 1                          | LSB        |

| 25    | Zero Code Error                    |        |                           | _                         | 7                          | LSB        |

| 26    | Voltage Output Drift,<br>Hold mode | _      | —                         | _                         | 0.0                        | mV /<br>mS |

| Note: | $IV_{AG} = (V_{ADD} / 2) \pm 1\%$  |        | 1                         | 1                         | 1                          | I          |

**Table 2-4**Peak and Valley DAC

## SWITCH CAPACITOR FILTER

Table 2-5

Switch Capacitor Filter

| Spec. | Characteristic                                                                                                                                                                                     | Symbol          | Min   | Тур   | Max              | Unit |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|-------|------------------|------|

| 27    | Pass Band Gain ( $V_{ADD}SEL = 0$ )                                                                                                                                                                |                 | 11.16 | 11.26 | 11.36            | dB   |

| 28    | Pass Band Gain ( $V_{ADD}SEL = 1$ )                                                                                                                                                                | —               | 7.64  | 7.74  | 7.84             | dB   |

| 29    | Cutoff Frequency, – 3 dB, BW = 1                                                                                                                                                                   | —               | 1.95  | 2.0   | 2.05             | kHz  |

| 30    | Cutoff Frequency, $-3 \text{ dB}$ , BW = 0                                                                                                                                                         | —               | 0.95  | 1.0   | 1.05             | kHz  |

| 31    | Stabilization time, off mode to hold mode                                                                                                                                                          | —               |       | _     | 5.0              | mS   |

| 32    | Analog Input Impedance (f <sub>IN</sub> = 10 kHz)                                                                                                                                                  | Z <sub>IN</sub> | 1.0   | _     | —                | MΩ   |

| 33    | ADIN Voltage Range (See Note)                                                                                                                                                                      | ADIN            | 0.0   | _     | V <sub>ADD</sub> | V    |

| Note: | Although the voltage on ADIN may be any value in the range specified, the actual maximum permitted ac signal peak is given by:<br>$V_{ADIN-peak} = 0.410 \times V_{ADD} / SCFGAIN - V_{difoffset}$ |                 |       |       |                  |      |

|       |                                                                                                                                                                                                    |                 |       |       |                  |      |

2-bit A/D Converter

# 2-BIT A/D CONVERTER

| Spec. | Characteristic                                                                                                                                                                                                                                                            | Min | Тур                                 | Max | Unit |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------|-----|------|

| 34    | Lower Threshold                                                                                                                                                                                                                                                           | J   | + (Peak – Valley<br>@ Peak – Valley |     | V    |

| 35    | Middle Threshold                                                                                                                                                                                                                                                          | 0   | + (Peak – Valley<br>@ Peak – Valley |     | V    |

| 36    | Upper Threshold                                                                                                                                                                                                                                                           | v   | + (Peak – Valley<br>@ Peak – Valley |     | V    |

| Note: |                                                                                                                                                                                                                                                                           |     |                                     |     |      |

|       | $V_{DC-OFFSET}$ = Voltage of input offset signal DC-OFFSET.<br>(V <sub>diffoffset</sub> is the absolute value of the difference between V <sub>ADoffset</sub> and V <sub>DC-OFFSET</sub> , that is the absolute value of the error in the input offset signal DC-OFFSET.) |     |                                     |     |      |

### Table 2-62-bit A/D Converter

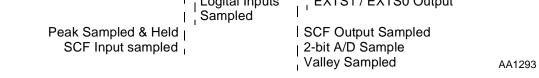

#### **Timing Diagrams**

## TIMING DIAGRAMS

<del>ds:</del>>

### Specifications

Timing Diagrams

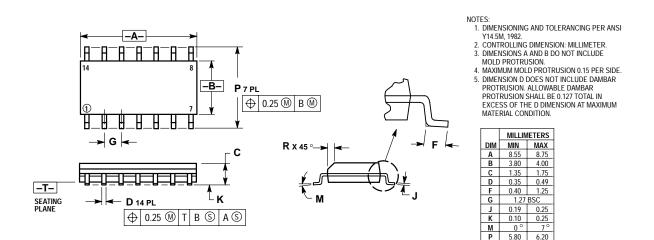

# SECTION 3

# PACKAGING

## **PIN-OUT AND PACKAGE INFORMATION**

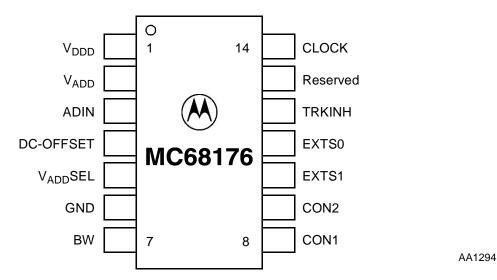

This sections provides information about the available packages for this product, including diagrams of the package pinouts and tables describing how the signals described in **Section 1** are allocated. The MC68176 is available in a 14-pin Small Outline Integrated Circuit (SOIC) package.

### Pin-out and Package Information

## **TQFP** Package Description

Top and bottom views of the SOIC package are shown in **Figure 3-1** and **Figure 3-2** with their pinouts.

Figure 3-1 MC68176 Small Outline Integrated Circuit (SOIC), Top View

| Pin # | Signal Name          | Pin # | Signal Name |

|-------|----------------------|-------|-------------|

| 1     | V <sub>DDD</sub>     | 8     | CON1        |

| 2     | V <sub>ADD</sub>     | 9     | CON2        |

| 3     | ADIN                 | 10    | EXTS1       |

| 4     | DC-OFFSET            | 11    | EXTS0       |

| 5     | V <sub>ADD</sub> SEL | 12    | TRKINH      |

| 6     | V <sub>SS</sub>      | 13    | Reserved    |

| 7     | BW                   | 14    | CLOCK       |

| Table 3-1 | Signal by Pin Number |

|-----------|----------------------|

|-----------|----------------------|

Table 3-2Signal by Name

| Signal Name | Pin # | Signal Name          | Pin # |

|-------------|-------|----------------------|-------|

| ADIN        | 3     | EXTS1                | 10    |

| BW          | 7     | Reserved             | 13    |

| CLOCK       | 14    | TRKINH               | 12    |

| CON1        | 8     | V <sub>ADD</sub>     | 2     |

| CON2        | 9     | V <sub>ADD</sub> SEL | 5     |

| DC-OFFSET   | 4     | V <sub>DDD</sub>     | 1     |

| EXTS0       | 11    | V <sub>SS</sub>      | 6     |

## **ORDERING DRAWINGS**

Complete mechanical information regarding MC68176 packaging is available by facsimile through Motorola's Mfax<sup>™</sup> system. Call the following number to obtain information by facsimile:

The Mfax automated system requests the following information:

- The receiving facsimile telephone number including area code or country code

- The caller's Personal Identification Number (PIN)

- **Note:** For first time callers, the system provides instructions for setting up a PIN, which requires entry of a name and telephone number.

- The type of information requested:

- Instructions for using the system

- A literature order form

- Specific part technical information or data sheets

- Other information described by the system messages

A total of three documents may be ordered per call.

The MC68176 14-pin SOIC package mechanical drawing is referenced as 751-A.

-csp

# SECTION 4

# **DESIGN CONSIDERATIONS**

### THERMAL DESIGN CONSIDERATIONS

An estimation of the chip junction temperature,  $T_J$ , in °C can be obtained from the equation:

**Equation 1:**  $T_J = T_A + (P_D \times R_{\theta JA})$

Where:

| TA              | = ambient temperature °C                              |

|-----------------|-------------------------------------------------------|

| $R_{\theta JA}$ | = package junction-to-ambient thermal resistance °C/W |

| P <sub>D</sub>  | = power dissipation in package                        |

Historically, thermal resistance has been expressed as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

#### **Equation 2:** $R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

Where:

| $R_{\theta JA}$ | = package junction-to-ambient thermal resistance °C/W |

|-----------------|-------------------------------------------------------|

| $R_{\theta IC}$ | = package junction-to-case thermal resistance °C/W    |

| $R_{\theta CA}$ | = package case-to-ambient thermal resistance °C/W     |

$R_{\theta JC}$  is device-related and cannot be influenced by the user. The user controls the thermal environment to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For example, the user can change the air flow around the device, add a heat sink, change the mounting arrangement on the Printed Circuit Board (PCB), or otherwise change the thermal dissipation capability of the area surrounding the device on a PCB. This model is most useful for ceramic packages with heat sinks; some 90% of the heat flow is dissipated through the case to the heat sink and out to the ambient environment. For ceramic packages, in situations where the heat flow is split between a path to the case and an alternate path through the PCB, analysis of the device thermal performance may need the additional modeling capability of a system level thermal simulation tool.

#### **Thermal Design Considerations**

The thermal performance of plastic packages is more dependent on the temperature of the PCB to which the package is mounted. Again, if the estimations obtained from  $R_{\theta JA}$  do not satisfactorily answer whether the thermal performance is adequate, a system level model may be appropriate.

A complicating factor is the existence of three common ways for determining the junction-to-case thermal resistance in plastic packages:

- To minimize temperature variation across the surface, the thermal resistance is measured from the junction to the outside surface of the package (case) closest to the chip mounting area when that surface has a proper heat sink.

- To define a value approximately equal to a junction-to-board thermal resistance, the thermal resistance is measured from the junction to where the leads are attached to the case.

- If the temperature of the package case (T<sub>T</sub>) is determined by a thermocouple, the thermal resistance is computed using the value obtained by the equation  $(T_J T_T) / P_D$ .

As noted above, the junction-to-case thermal resistances quoted in this data sheet are determined using the first definition. From a practical standpoint, that value is also suitable for determining the junction temperature from a case thermocouple reading in forced convection environments. In natural convection, using the junction-to-case thermal resistance to estimate junction temperature from a thermocouple reading on the case of the package will estimate a junction temperature slightly hotter than actual temperature. Hence, the new thermal metric, Thermal Characterization Parameter or  $\Psi_{JT}$ , has been defined to be  $(T_J - T_T) / P_D$ . This value gives a better estimate of the junction temperature in natural convection when using the surface temperature of the package. Remember that surface temperature readings of packages are subject to significant errors caused by inadequate attachment of the sensor to the surface and to errors caused by heat loss to the sensor. The recommended technique is to attach a 40-gauge thermocouple wire and bead to the top center of the package with thermally conductive epoxy.

#### **Application Design Considerations**

## **APPLICATION DESIGN CONSIDERATIONS**

The FLEX chip IC connects to a receiver capable of converting a four-level audio signal into a 2-bit digital signal with the MC68176 FLEX 2-bit D/A. The FLEX chip IC has eight receiver control lines used for warming up and shutting down a receiver in stages, dual bandwidth control signals for two post detection filter bandwidths for receiving the two symbol rates of the FLEX signal, and the ability to detect a low battery signal during the receiver control sequences. It interfaces to a host MCU through a standard SPI. It has a 38.4 kHz clock output capable of driving other devices, in particular the MC68176. It has a 1 minute timer that offers low power support for time of day function on the host. **Figure 4-1** shows a typical application block diagram.

Figure 4-1 FLEX chip System Block Diagram

#### **Application Design Considerations**

## **Sample Application Circuit**

**Figure 4-2** shows an application example of the MC68176 2-bit FLEX A/D chip in a FLEX pager application. The MC68176 A/D chip will convert an analog FLEX baseband signal into a 2-bit digital signal. The MC68176 A/D can be controlled by a FLEX decoder, such as the MC68175 or MC68181. The following schematic shows the MC68176 A/D chip in a pager application.

Figure 4-2 An Application Example for the MC68176, FLEX A/D

Note that the dc offset of the audio input signal to the FLEX A/D must be applied to the DC-OFFSET pin for the converter to work properly. Theoretically speaking, we can view the DC-OFFSET pin as an internal resistance of 50 k $\Omega$  and a internal capacitance of 1.6 pF in serial. So, the external resisters, r1, r2, and r3 can be as large as 600 k $\Omega$ , 600 k $\Omega$ , and 60 k $\Omega$ , respectively— this will guarantee settling to an accuracy of at least 9 bits.

dsp-

# **SECTION** 5

# **ORDERING INFORMATION**

Consult a Motorola Semiconductor sales office or authorized distributor to determine product availability and to place an order.

| Part                                                                                                                                                                                                      | Supply<br>Voltage           | Package Type | Pin<br>Count | Frequency<br>(KHz) | Order Number |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------|--------------|--------------------|--------------|

| MC68176                                                                                                                                                                                                   | 1.8 V—3.3 V<br>(see Note 1) | SOIC         | 14           | 38.4               | MC68176DW    |

| Note: 1. The MC68176 has two separate power rails for the analog and digital portions of the circuitry, $V_{ADD}$ and $V_{DDD}$ . Both rails may be set independently to a nominal 2.0 V or 3.0 V supply. |                             |              |              |                    |              |

|  | Table 5-1 | Ordering | Information |

|--|-----------|----------|-------------|

|--|-----------|----------|-------------|

dsp

# APPENDIX A

# **DESCRIPTION OF OPERATION**

### **OPERATIONAL DESCRIPTION**

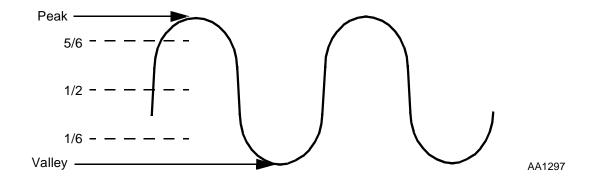

The MC68176 is a four-level audio band 2-bit A/D symbol decoder for the FLEX paging system. The input signal to the ADIN pin is generated by a FLEX RF receiver. There are four amplitude levels, which represent four unique output digital codes. The digital levels are defined relative to the peak and valley voltages of the signal.

Figure A-1 ADIN Analog Input Signal

The ideal digital transition levels are at the following thresholds:

- Upper Threshold =  $(\text{Peak} \text{Valley}) \times 5 / 6 + \text{Valley}$

- Middle Threshold = (Peak Valley)  $\times 1 / 2$  + Valley

- Lower Threshold =  $(\text{Peak} \text{Valley}) \times 1 / 6 + \text{Valley}$

The Gray scale regions are shown in **Table A-1** on page A-2.

### **Operational Description**

| Signal Range | EXTS1, EXTS0 |

|--------------|--------------|

| Peak         |              |

| 5/6          | 1, 0         |

| 1/2          | 1, 1<br>0, 1 |

| 1/6          | 0, 0         |

| Valley       | -            |

Table A-1

Gray Scale Regions

Each threshold in **Table A-1** must be accurate to within 5% of the ideal threshold, or the FLEX bit error rate will increase beyond acceptable levels.

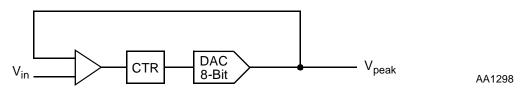

The problem is that both the amplitude and the dc offset of the received signal will be affected by many variables—temperature, voltage, production lot, vendor, and receiver design. Because of this increase in the dynamic range, an 8-bit DAC is required for both the peak and valley servo loops. This means that the peak and valley levels used by the MC68176 are within one LSB of the actual peak and valley voltage levels.

### **Peak and Valley Servo Description**

A control loop is used to acquire the actual Peak and Valley voltages to an accuracy of one LSB. The Peak control loop is described below; the Valley control loop is similar, with appropriate changes made to acquire a minimum rather than a maximum signal value.

Figure A-2 Peak/Valley Control Loop

The FLEX system uses a symbol rate of 1600 symbols per second during the synchronization period. The MC68176 must acquire the Peak and Valley levels in six symbol periods, with sufficient accuracy that the threshold levels used by the two-bit A/D are within 5% of the actual thresholds.

### **Operational Description**

There are two tracking modes, Fast Track mode and Slow Track mode. The use of these two modes allows the threshold specification to be acquired in the required six symbol periods, that is 6/1600 seconds or six times  $625 \ \mu$ S. Fast Track mode is used for one symbol period to obtain a very approximate value quickly, and Slow Track mode is used for the remaining five periods to obtain an accurate value. In both Fast Track mode and Slow Track mode, the Control loop acquires the Peak and Valley by attacking or decaying the Peak counter at different rates.

In Fast Track mode, tracking is controlled only by the relative levels of the two signals  $V_{in}$  and the Peak DAC output. If the Peak DAC output is above  $V_{in}$ , then the Peak counter will decay, and if it is below  $V_{in}$ , then the Peak counter will attack.

Slow Track mode is a little more complicated. For the Peak counter to decay, TRKINH must be low (i.e., tracking is not inhibited), the Peak DAC output must be greater than  $V_{in}$ , and no attack or decay may have happened for a set number of CLOCK cycles. If all these conditions are met, then the Peak DAC is decremented. The Peak counter is incremented if TRKINH is low and the Peak DAC output is less than  $V_{in}$ .

dsp-

**Operational Description**

Mfax, FLEX and FLEXstack are trademarks of Motorola Inc.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and ᠺ are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/ Affirmative Action Employer.

#### How to reach us:

#### USA/Europe/Locations Not Listed:

Motorola Literature Distribution P.O. Box 5405 Denver, Colorado 80217 1 (800) 441-2447 1 (303) 675-2140

#### Mfax™:

RMFAX0@email.sps.mot.com TOUCHTONE (602) 244-6609 USA and Canada ONLY: 1 (800) 774-1848

#### Asia/Pacific:

Motorola Semiconductors H.K. Ltd. 8B Tai Ping Industrial Park 51 Ting Kok Road Tai Po, N.T., Hong Kong 852-26629298

#### Technical Resource Center:

1 (800) 521-6274

DSP Helpline

dsphelp@dsp.sps.mot.com

#### Japan:

Nippon Motorola Ltd SPD, Strategic Planning Office 4-32-1, Nishi- Gotanda Shinagawa-ku, Tokyo 141, Japan 81-3-5487-8488

Internet: http://www.motorola.com/sps