## **Smart Voltage Regulator for Peripheral Card Applications**

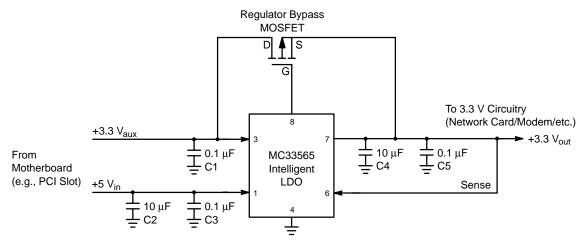

The MC33565 Low Drop Out Voltage Regulator is designed for computer peripheral card applications, allowing glitch–free transitions from "sleep" to "active" system modes. It has internal logic circuitry to detect whether there is a 5 V supply ("active" system mode) or an auxiliary 3.3 V supply ("sleep" system mode). A guaranteed 3.3 V regulated output voltage at 200 mA is always available even if the main 5 V supply drops out.

The regulated 3.3 V output voltage is provided by either an internal dropout 5.0 V-to-3.3 V voltage regulator or an external P-channel MOSFET, depending on the system being in the "active" or "sleep" mode.

#### **Features**

- Glitch–Free Transition from "Sleep" to "Active" Mode

- Compatible with Instantly Available PC Systems

- Output Current up to 200 mA

- Output Regulated to 2% over Temperature

- Excellent Line and Load Regulation (0.4%)

- Prevents Reverse Current Flow during Sleep Mode

#### **Applications**

- Computer

- Ethernet

- PCI/NIC Cards

## ON Semiconductor

http://onsemi.com

# 200 mA INTELLIGENT LDO REGULATOR WITH SMART BYPASS CONTROL

## MARKING DIAGRAM

SOIC-8 D SUFFIX CASE 751

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

#### **PIN CONNECTIONS**

| 1 | 0 | 8 | Drive out             |

|---|---|---|-----------------------|

| 2 |   | 7 | +3.3 V <sub>out</sub> |

| 3 |   | 6 | Sense in              |

| 4 |   | 5 | N/C                   |

|   |   |   | 3 6                   |

Pins 2 and 5 Not Connected

#### ORDERING INFORMATION

| Device     | Package | Shipping           |

|------------|---------|--------------------|

| MC33565D   | SOIC-8  | 98 Units / Rail    |

| MC33565DR2 | SOIC-8  | 2500 / Tape & Reel |

### **MAXIMUM RATINGS** ( $T_C = 25$ °C, unless otherwise noted) (Note 1.)

| Parameter                                       | Symbol                     | Max Value    | Unit |

|-------------------------------------------------|----------------------------|--------------|------|

| Input Voltage, V <sub>CC</sub>                  | V <sub>max</sub>           | 7.0          | Vdc  |

|                                                 | V <sub>min</sub>           | -0.5         | Vdc  |

| Operating Ambient Temperature                   | T <sub>a</sub>             | −5 to +70    | °C   |

| Operating Junction Temperature                  | T <sub>J</sub>             | – 5 to +150  | °C   |

| Lead Temperature (Soldering, 10 seconds)        | T <sub>L</sub>             | 300          | °C   |

| Storage Temperature Range                       | T <sub>stg</sub>           | - 55 to +150 | °C   |

| Package Thermal Resistance, Junction to Ambient | R <sub>θJA</sub> (Note 1.) | 171          | °C/W |

| Thermal Resistance, Junction to Case            | $R_{	heta JC}$             | 28           | °C/W |

<sup>1.</sup> Minimum pad test board with 5 mil wide and 2.8 mil thick copper traces 1 inch long.

## AC ELECTRICAL SPECIFICATIONS (Notes 1., 2., 3., and 4.)

| Parameter                                                                                                                                                        |                 | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| Drive High Delay ( $V_{in}$ ramping up)<br>$C_{Drive} = 1.2 \text{ nF}$ , measured from +5 $V_{in} = V_{thresHi}$ to $V_{Drive} = 2 \text{ V}$                   | t <sub>DH</sub> | _   | 1.3 | 3.5 | μS   |

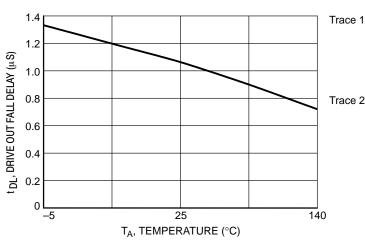

| Drive Low Delay (V <sub>in</sub> ramping down)  C <sub>Drive</sub> = 1.2 nF, measured from +5 V <sub>in</sub> = V <sub>thresLo</sub> to V <sub>Drive</sub> = 2 V |                 | _   | 1.2 | 3.5 | μS   |

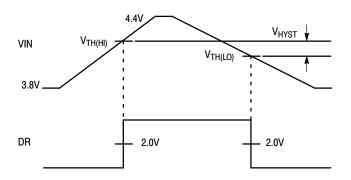

- 1. See 5 V Detect Thresholds Diagram.

- 2. Recommended source impedance for 5 V supply:  $\leq$  0.25  $\Omega$ . This will ensure that I<sub>0</sub> x R<sub>source</sub> < V<sub>hyst</sub>, thus avoiding drive out toggling during 5 V detect threshold transitions.

- 3. See Figure 2. Application Block Diagram.

- 4. See Timing Diagram.

## DC ELECTRICAL CHARACTERISTICS (Note 1.)

| Characteristic                                  | Symbol               | Min | Тур | Max | Unit |

|-------------------------------------------------|----------------------|-----|-----|-----|------|

| +5 V <sub>in</sub> Supply Voltage Range         | +5 V <sub>in</sub>   | 4.3 | 5.0 | 5.5 | Vdc  |

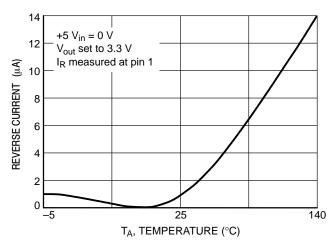

| Reverse Leakage Current from Output             | I <sub>reverse</sub> | _   | _   | 25  | μΑ   |

| V <sub>Aux</sub> quiescent current              | _                    | _   | _   | 3.0 | mA   |

| +5 V <sub>in</sub> quiescent current, operating | _                    | _   | _   | 10  | mA   |

| Load Capacitance (Note 2.)                      | C <sub>load</sub>    | 4.7 | 22  |     | μF   |

## **REGULATOR OUTPUT**

| Output Voltage $ (4.3 \text{ V} \leq \text{V}_{in} \leq 5.5 \text{ V}, \text{ 0 mA} \leq \text{I}_{o} \leq 200 \text{ mA}) \text{ T}_{A} = 25^{\circ}\text{C} \\ (\text{T}_{J} = -5^{\circ}\text{C to } 150^{\circ}\text{C}) $ | +3.3 V <sub>out</sub> | 3.267<br>3.234 | 3.30<br>3.30 | 3.333<br>3.366 | Vdc |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|--------------|----------------|-----|

| In-to-Out Voltage (3.9 V $\leq$ V <sub>in</sub> $\leq$ 4.3 V, V <sub>aux</sub> = 3.3 V)                                                                                                                                        | V <sub>d</sub>        | 3.0            | _            | _              | Vdc |

| Voltage Out at Max Voltage In (V <sub>in</sub> = 7 V)                                                                                                                                                                          | V <sub>outmax</sub>   | 3.1            | 3.3          | 3.5            | Vdc |

| Line Regulation (I <sub>o</sub> = 200 mA)                                                                                                                                                                                      | _                     | _              | _            | 0.4            | %   |

| Load Regulation (I <sub>o</sub> = 0 to 200 mA)                                                                                                                                                                                 | _                     | _              | _            | 0.4            | %   |

| Short Circuit Current                                                                                                                                                                                                          | I <sub>sc</sub>       | 230            | 435          | _              | mA  |

## **5 V DETECT**

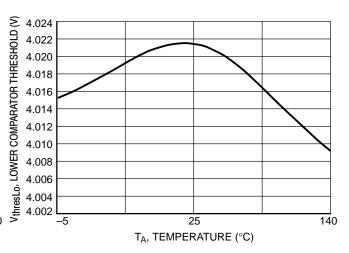

| Low Threshold Voltage (+5 V <sub>in</sub> falling) | V <sub>thresLo</sub> | 3.9  | 4.02 | 4.3  | Vdc |

|----------------------------------------------------|----------------------|------|------|------|-----|

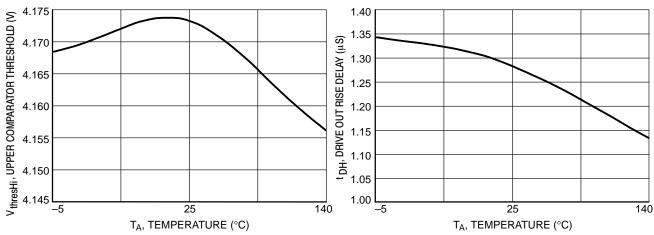

| High Threshold Voltage (+5 V <sub>in</sub> rising) | V <sub>thresHi</sub> | _    | 4.17 | 4.3  | Vdc |

| Hysteresis                                         | V <sub>Hyst</sub>    | 0.12 | 0.15 | 0.18 | Vdc |

- 1.  $-5^{\circ}\text{C} < \text{T}_{a} < 70^{\circ}\text{C}$ , 4.3 V < V<sub>in</sub> < 5.5 V, C<sub>load</sub> = 4.7  $\mu\text{F}$  unless otherwise noted 2. 4.7  $\mu\text{F}$  minimum over temperature; 22  $\mu\text{F}$  recommended; 500 m $\Omega$  ESR maximum.

## DC ELECTRICAL CHARACTERISTICS (Note 1.) (continued)

## DRIVE OUTPUT

| Characteristic                                                                                        | Symbol            | Min | Тур                   | Max | Unit |

|-------------------------------------------------------------------------------------------------------|-------------------|-----|-----------------------|-----|------|

| Output peak source Current<br>(+5 V <sub>in</sub> > V <sub>thresHi</sub> , Pin 8 current into 1.2 nF) | I <sub>peak</sub> | 15  | _                     | _   | mA   |

| Output peak sink Current<br>(+5 V <sub>in</sub> < V <sub>thresLo</sub> , Pin 8 current into 1.2 nF)   | I <sub>peak</sub> | 15  | _                     | _   | mA   |

| Low Output Voltage<br>(I <sub>oL</sub> = 200 μA, V <sub>in</sub> < V <sub>thresLo</sub> )             | V <sub>oL</sub>   | _   | 145                   | 200 | mVdc |

| High Output Voltage $(I_{OH} = 200 \mu A)$                                                            | V <sub>oH</sub>   | 3.4 | V <sub>in</sub> -0.85 | _   | Vdc  |

<sup>1.</sup>  $-5^{\circ}\text{C} < \text{T}_{\text{a}} < 70^{\circ}\text{C}$ , 4.3 V < V<sub>in</sub> < 5.5 V, C<sub>load</sub> = 4.7  $\mu\text{F}$  unless otherwise noted

## **DEVICE MARKING**

| Device   | Туре  | Sub-type | Marking (1st Line) |

|----------|-------|----------|--------------------|

| MC33565D | 3.3 V | _        | MC565              |

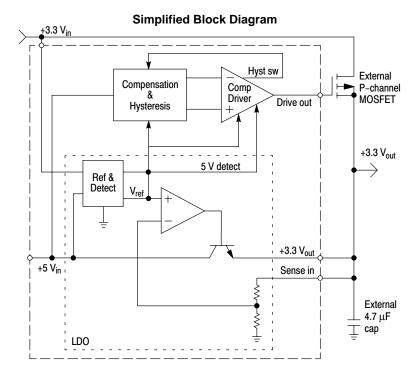

Figure 1. Functional Block Diagram

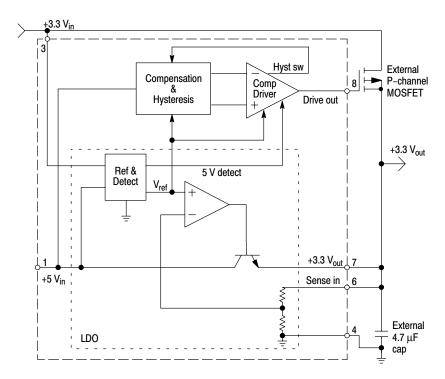

## PIN ASSIGNMENTS AND FUNCTIONS

| PIN# | PIN NAME              | PIN DESCRIPTION                                                                                                                                                                                                                  |

|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | +5 V <sub>in</sub>    | This is the input supply for the IC. Typical voltage 5 V.                                                                                                                                                                        |

| 2, 5 | N/C                   | Reserved                                                                                                                                                                                                                         |

| 3    | +3.3 V <sub>in</sub>  | Auxiliary input. Typical voltage 3.3 V.                                                                                                                                                                                          |

| 4    | Gnd                   | Logic and Power Gnd.                                                                                                                                                                                                             |

| 6    | Sense in              | Load–sense voltage input to internal regulator.                                                                                                                                                                                  |

| 7    | +3.3 V <sub>out</sub> | 3.3 V output provided to the application circuit (output current is sourced to this pin from the 5 V input.)                                                                                                                     |

| 8    | Drive out             | This output drives a P-channel MOSFET with up to 1.2 nF of "effective" gate capacitance.  Recommended device is MGSF1P02ELT MOSFET. Drive out has active internal pull-up and pull-down circuitry to guarantee fast transitions. |

#### **OPERATING DESCRIPTION**

The MC33565 is designed for power managed computer applications such as peripheral card interface (PCI) and network interface cards (NIC) where glitch–free transition between +3.3 V and +5 V is necessary. In this type of application, the presence of a +5 V supply represents the "active" system mode, while the presence of +3.3 V represents the "sleep" system mode. The MC33565 complies with the *instantly available requirements* as specified by the Advanced Configuration and Power Interface (ACPI) standards set by Intel, Microsoft, and Toshiba. A regulated output voltage of +3.3 V is available even when the +5 V supply has been shut down and only the +3.3 V auxiliary supply is available.

The MC33565 has dual inputs, +5 V<sub>in</sub> and +3.3 V<sub>in</sub>. It functions as a linear regulator when V<sub>in</sub> is greater than 4.02 V. Below this threshold value, the linear regulator turns off and the auxiliary DRIVE OUT feature allows the use of an external P-channel MOSFET to supply power to the output. The MC33565 connects the +3.3 V<sub>in</sub> auxiliary power supply directly to the output P-channel MOSFET.

#### **5 V Detect**

Internal circuitry detects if the system is being powered from a +5 V supply or a 3.3 V auxiliary supply. During normal operating conditions, the MC33565 is powered by the +5 V supply. A regulated output voltage of +3.3 V is provided by an internal low drop out 5.0 V-to-3.3 V voltage regulator. The gate of the P-channel MOSFET is driven high and therefore disabled.

If the +5 V supply is not available or the supply voltage drops below a typical threshold value of 4.02 V, the DRIVE OUT goes low. This enables the external P-channel MOSFET, connecting the +3.3 V auxiliary supply to the load and allowing the load to remain powered even though the +5 V supply is not available.

As the supply voltage begins to rise, the linear regulator output will be disabled until  $V_{in}$  reaches a typical threshold voltage of 4.17 V. The load continues to be powered by the auxiliary DRIVE OUT while  $V_{in}$  reaches the threshold voltage. When  $V_{in}$  reaches the threshold voltage, the gate of the external P-channel MOSFET is driven high and turns off.

The 5 V detect logic is active throughout the entire range of the +5 V supply ramp—up. The DRIVE OUT signal is never turned ON or OFF inappropriately during ramp—up of the +5 V $_{in}$  supply. The +3.3 V output voltage never drops below 3.0 V while the +5 V supply is above the 5 V DETECT minimum threshold of 3.9 V.

#### Input Blocking

The internal NPN pass transistor of the low drop out regulator (LDO) ensure that no significant reverse current will flow from  $V_{out}$  to  $V_{in}$  or GND when the +5  $V_{in}$  input is not powered and the +3.3  $V_{in}$  supply is present.

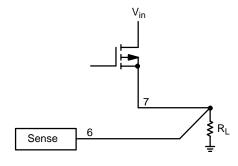

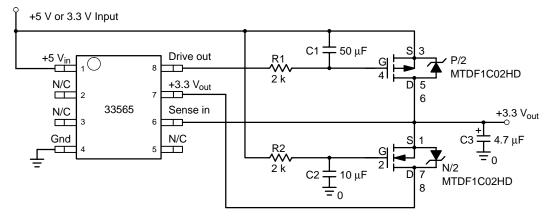

#### **P-Channel MOSFET Polarity**

It is imperative that the polarity of the P-channel MOSFET be observed because the P-channel MOSFET body diode will be connected between the auxiliary power supply and the load. The P-channel MOSFET drain is connected to the  $+3.3~V_{\rm in}$  auxiliary power supply; source is connected to load; gate is connected to DRIVE OUT. If the polarity is reversed with the drain connected to the load and the source connected to the auxiliary supply, the body diode could be forward biased if the auxiliary supply is not present. Consequently the linear regulator would not turn off and it would supply current to everything on the auxiliary supply rail

#### **Hysteresis**

The internal 5 V DETECT has a typical high threshold voltage of 4.17 V and a typical low threshold voltage of 4.02 V. This results in a typical hysteresis of 150 mV for noise immunity. The input supply voltage, V<sub>in</sub>, must drop 150 mV while the linear regulator is supplying power to the load before the auxiliary DRIVE OUT is enabled.

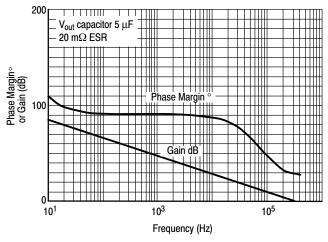

#### **External Compensation**

An external compensation capacitor with a minimum value of 4.7  $\mu F$  is required for the linear regulator to be stable. Increasing the capacitance will improve the overall transient response. The equivalent series resistance (ESR) of the capacitor should be less than 1  $\Omega$  in order for the output voltage to be maintained within tight tolerance.

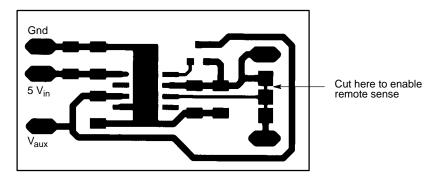

#### Sense

The SENSE IN pin provides tight regulation of the load voltage while the 5 V supply is present even with varying load current. To take advantage of the SENSE PIN, connect pin 6 as close to the load as possible. Use a separate trace to connect the source of the MOSFET to the load. Refer to Figure 2.

Figure 2.

#### **Board Layout**

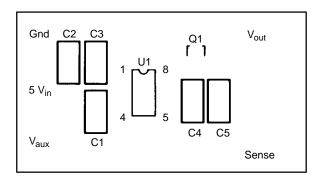

The PCB component layout shown in Figure 28 is designed for an input range of 4.3 V to 5.5 V; an output voltage range of 3.267 V to 3.333 V; and an output current of 200 mA.

#### **Current Limit and Thermal Shutdown**

Full protection with both current limit and thermal shutdown is provided. Internal thermal limiting circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When activated, typically at 170°C, the output is disabled. There

is no hysteresis built into the thermal limiting circuit. As a result, if the device is overheating, the output will appear to be oscillating. This feature is provided to prevent catastrophic failures from accidental device overheating. It is not intended to be used as a substitute for proper heatsinking.

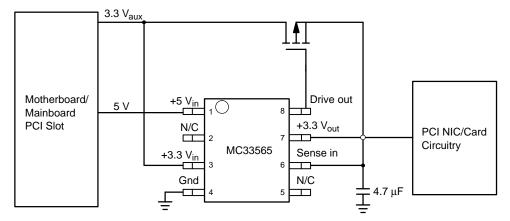

Figure 3. Application Block Diagram

Figure 4. Typical Application Schematic

Figure 5. Alternative Application: 5 V or 3.3 V Card Input with Hot Swap Circuitry

#### TYPICAL CHARACTERISTICS

#### NOTE:

(1) VIN rise and fall times (10% to 90%) to be  $\geq$  100  $\mu s.$

#### Figure 6. 5V Detect Thresholds Diagram

#### NOTE:

(1) VIN rise and fall times (10% to 90%) to be  $\leq$  100 ns.

Figure 7. Timing Diagram

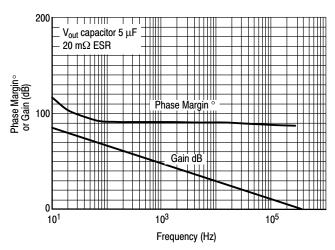

NOTE:  $V_{out}$  capacitor  $\geq$  4.7  $\mu$ F over operating temperature range. Maximum ESR permissible = 500 m $\Omega$  over operating temperature range.

Figure 8. Predicted Gain and Phase at Zero Load Current

Figure 9. Predicted Gain and Phase at Full Load Current

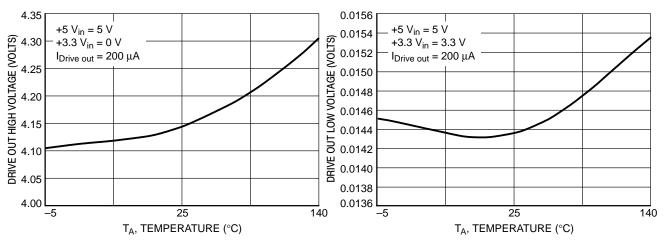

Figure 10. Drive Out High Voltage (external P-channel MOSFET turned off) versus Ambient Temperature

Figure 11. Drive Out Low Voltage (external P-channel MOSFET turned on) versus Ambient Temperature

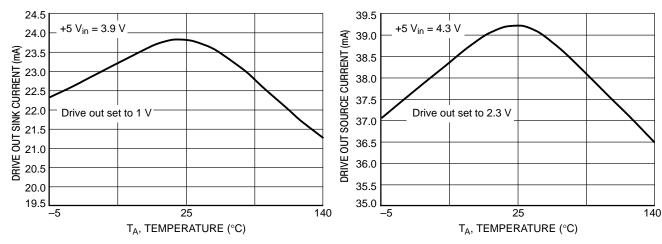

Figure 12. Drive Out Peak Sink Current versus Ambient Temperature

Figure 13. Drive Out Peak Source Current versus Ambient Temperature

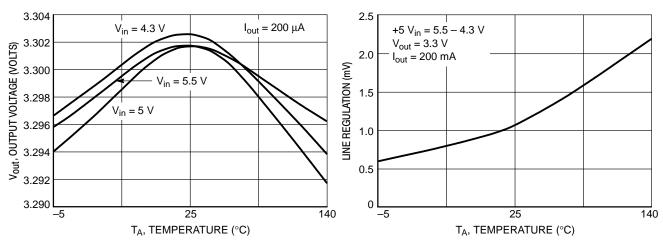

Figure 14. Output Voltage versus Ambient Temperature

Figure 15. Line Regulation versus Ambient Temperature

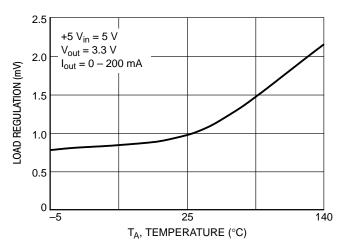

Figure 16. Load Regulation versus Ambient Temperature

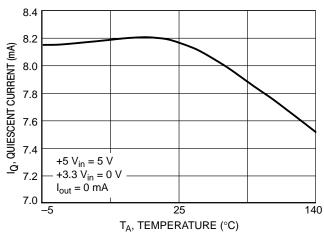

Figure 17. Quiescent Current versus Ambient Temperature (5 V only)

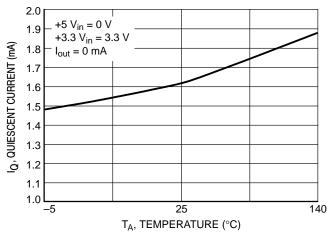

Figure 18. Quiescent Current versus Ambient Temperature (3.3 V aux only)

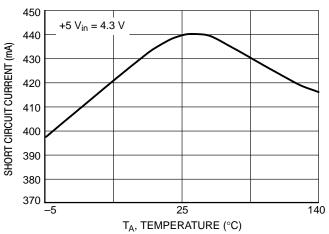

Figure 19. Short Circuit Current versus Ambient Temperature

Figure 20. Reverse Leakage Current from Output versus Ambient Temperature

Figure 21. Lower Comparator Threshold versus Ambient Temperature

Figure 22. Upper Comparator Threshold versus Ambient Temperature

Figure 23. Drive Out Rise Delay (after V<sub>in</sub> crosses threshold) versus Ambient Temperature

Figure 24. Drive Out Fall Delay (after V<sub>in</sub> crosses threshold) versus Ambient Temperature

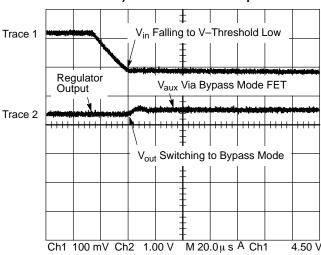

TRACE 1:  $V_{in}$  stepping from 5 V to  $V_{thresLo}$  TRACE 2:  $V_{out}$  switching from regulator output to  $V_{aux}$

Figure 25. Bypass Mode Transition

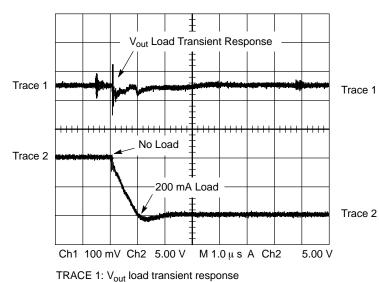

TRACE 2: No load to 200 mA

Figure 26. Load Transient Response: Load Applied

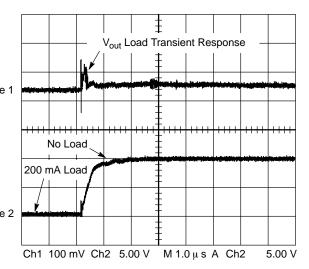

TRACE 1: Regulator 3.3 V<sub>out</sub>

TRACE 2: Iout stepping from 200 mA load to no load

Figure 27. Load Transient Response: Load Removed

Figure 28. PCB Component Layout

Figure 29. PCB Copper Layout

## **PARTS LIST**

| Qty | Reference  | Part/Description         | Vendor           | Notes            |

|-----|------------|--------------------------|------------------|------------------|

| 3   | C1, C3, C5 | 0.1 μF Ceramic Capacitor | Various          | -                |

| 2   | C2, C4     | 10 μF Tantalum Capacitor | Various          | -                |

| 1   | U1         | MC33565                  | ON Semiconductor | -                |

| 1   | Q1         | MGSF1P02ELT              | ON Semiconductor | P-Channel MOSFET |

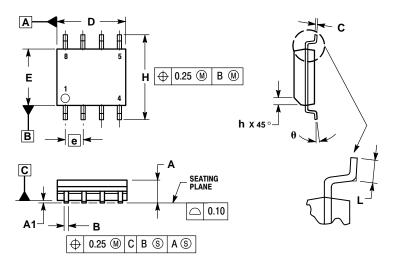

#### PACKAGE DIMENSIONS

SOIC-8 **D SUFFIX** PLASTIC PACKAGE CASE 751-06 **ISSUE T**

#### NOTES:

- 1 DIMENSIONING AND TOLERANCING PER ASME

- DIMENSION AND E DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

- DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTAL IN EXCESS OF THE B DIMENSION AT MAXIMUM MATERIAL

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 1.35        | 1.75 |  |

| A1  | 0.10        | 0.25 |  |

| В   | 0.35        | 0.49 |  |

| С   | 0.19        | 0.25 |  |

| D   | 4.80        | 5.00 |  |

| E   | 3.80        | 4.00 |  |

| е   | 1.27        | BSC  |  |

| Н   | 5.80        | 6.20 |  |

| h   | 0.25        | 0.50 |  |

| L   | 0.40        | 1.25 |  |

| θ   | 0 °         | 7°   |  |

are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes ON Semiconductor and ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

#### NORTH AMERICA Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

Fax Response Line: 303-675-2167 or 800-344-3810 Toll Free USA/Canada

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

EUROPE: LDC for ON Semiconductor - European Support

German Phone: (+1) 303-308-7140 (Mon-Fri 2:30pm to 7:00pm CET)

Email: ONlit-german@hibbertco.com

Phone: (+1) 303–308–7141 (Mon–Fri 2:00pm to 7:00pm CET)

Email: ONlit-french@hibbertco.com

English Phone: (+1) 303-308-7142 (Mon-Fri 12:00pm to 5:00pm GMT)

Email: ONlit@hibbertco.com

EUROPEAN TOLL-FREE ACCESS\*: 00-800-4422-3781

\*Available from Germany, France, Italy, UK, Ireland

#### CENTRAL/SOUTH AMERICA:

Spanish Phone: 303-308-7143 (Mon-Fri 8:00am to 5:00pm MST)

Email: ONlit-spanish@hibbertco.com

ASIA/PACIFIC: LDC for ON Semiconductor - Asia Support

Phone: 303-675-2121 (Tue-Fri 9:00am to 1:00pm, Hong Kong Time)

Toll Free from Hong Kong & Singapore: 001-800-4422-3781

Email: ONlit-asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center 4-32-1 Nishi-Gotanda, Shinagawa-ku, Tokyo, Japan 141-0031

Phone: 81-3-5740-2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.