# Advance Information

# Dual/Hex Low-Side Switch with Both SPI and Parallel Input Control

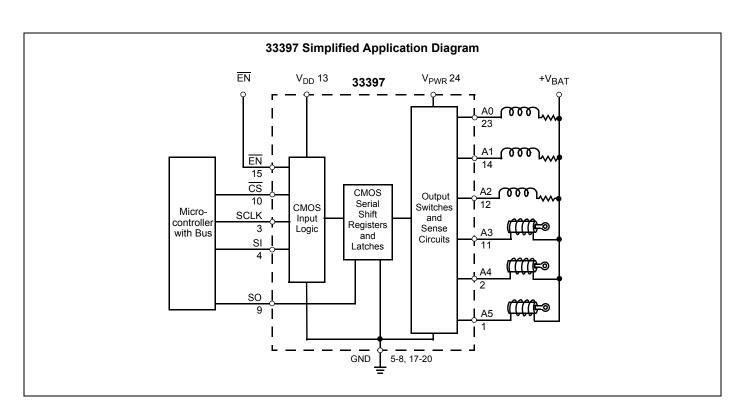

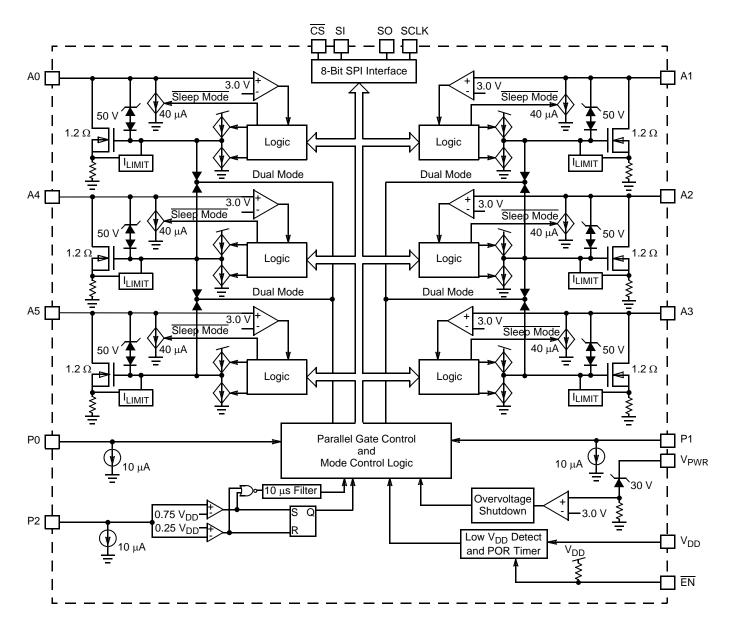

The 33397 is a low-side switch that is user configurable to be either two 333 m $\Omega$  outputs (dual mode) or six 900 m $\Omega$  outputs (hex mode). Each output is internally current limited and short-circuit protected. Output fault detection capability includes "off state" open loads and "on state" short-to-battery conditions. Faults for each output are latched into the fault register and serially shifted out during serial communication.

#### **Features**

- User Configurable to be Either Two 333 m $\Omega$  Outputs (Dual Mode) or Six 900 m $\Omega$  Outputs (Hex Mode)

- · Output Inductive Energy Clamps

- Parallel Input (3.3 V and 5.0 V Compatible) or Serial Peripheral Interface (SPI) Control

- · 8-Bit SPI Control and Fault Diagnostics

- · Short-to-Battery Detection and Shutdown with Automatic Retry

- · OFF-State Open-Circuit Detection

- Programmable Overvoltage Shutdown (V<sub>PWR</sub> Pin)

- Undervoltage Shutdown (V<sub>DD</sub> Pin)

- Sleep Mode— $I_{DD} \le 25 \mu A (1.0 \mu A Typical)$

# 33397

## **DUAL/HEX LOW-SIDE SWITCH**

#### **ORDERING INFORMATION**

| Device       | Temperature<br>Range (T <sub>A</sub> ) | Package  |  |  |

|--------------|----------------------------------------|----------|--|--|

| MC33397DW/R2 | -40 to 125°C                           | 24 SOICW |  |  |

This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

Figure 1. 33397 Simplified Block Diagram

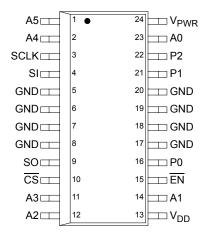

## **PIN FUNCTION DESCRIPTION**

| Pin                     | Pin Name         | Description                                                                                                                                                                            |

|-------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 11, 12,<br>14, 23 | A0-A5            | Power outputs                                                                                                                                                                          |

| 3                       | SCLK             | SPI clock input                                                                                                                                                                        |

| 4                       | SI               | SPI serial input                                                                                                                                                                       |

| 5-8, 17-20              | GND              | Power and signal ground                                                                                                                                                                |

| 9                       | SO               | SPI serial output                                                                                                                                                                      |

| 10                      | CS               | SPI chip select                                                                                                                                                                        |

| 13                      | V <sub>DD</sub>  | Supply input pin                                                                                                                                                                       |

| 15                      | EN               | Enable                                                                                                                                                                                 |

| 16                      | P0               | In hex mode, P0 controls output A0. In dual mode, P0 controls outputs A0, A4, and A5 simultaneously                                                                                    |

| 21                      | P1               | In hex mode, P1 controls output A1. In dual mode, P2 controls outputs A1, A2, and A3 simultaneously                                                                                    |

| 22                      | P2               | In hex mode, P2 controls output A2. P2 is also the mode control pin. If 0.25*V <sub>DD</sub> <p2<0.75*v<sub>DD for more than 10 µs, the 33397 will change to dual mode</p2<0.75*v<sub> |

| 24                      | V <sub>PWR</sub> | Overvoltage threshold shutdown monitoring pin (not a power supply pin for the IC)                                                                                                      |

## **MAXIMUM RATINGS**

All voltages are with respect to ground unless otherwise noted.

| Rating                                                                                                         | Symbol                                 | Value                        | Unit |  |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------|------|--|

| Power Supply Voltage                                                                                           | V <sub>PWR</sub>                       | 50                           | V    |  |

| Logic Supply Voltage                                                                                           | V <sub>DD</sub>                        | -0.3 to 7.0                  | V    |  |

| Input Pin Voltage                                                                                              | V <sub>IN</sub>                        | -0.3 to V <sub>DD</sub> +0.3 | V    |  |

| ESD Voltage Human Body Model (Note 1) Machine Model (Note 2)                                                   | V <sub>ESD1</sub><br>V <sub>ESD2</sub> | ±2000<br>±200                | V    |  |

| Single Pulse Output Clamp Energy $I_O$ =500 mA, $T_J$ =150°C (Hex Mode) $I_O$ =1.5 A, $T_J$ =150°C (Dual Mode) | JCLAMP1<br>JCLAMP1                     | 50<br>100                    | mJ   |  |

| Recommended SPI Operating Frequency                                                                            | f <sub>OP</sub>                        | 3.5                          | MHz  |  |

| Storage Temperature                                                                                            | T <sub>STG</sub>                       | -55 to 150                   | °C   |  |

| Operating Junction Temperature                                                                                 | T <sub>J</sub>                         | -40 to 150                   | °C   |  |

| Soldering Temperature (for 10 Seconds)                                                                         | T <sub>SOLDER</sub>                    | 260                          | °C   |  |

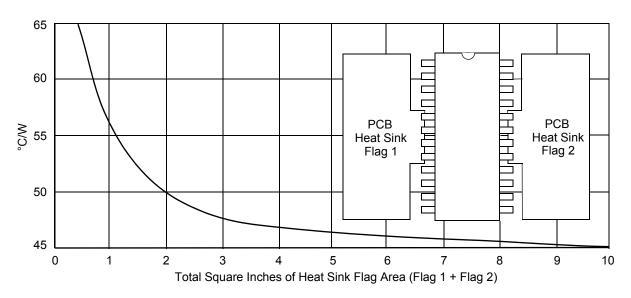

| Thermal Resistance, Junction-to-Lead (Note 3)                                                                  | $R_{	heta J	ext{-}L}$                  | 15                           | °C/W |  |

#### Notes

- 1. ESD1 performed in accordance with the Human Body Model (C<sub>ZAP</sub>=100 pF, R<sub>ZAP</sub>=1500  $\Omega$ ).

- 2. ESD2 performed in accordance with the Machine Model (C<sub>ZAP</sub>=200 pF, R<sub>ZAP</sub>=0  $\Omega$ ).

- 3. Leads 5, 6, 7, 8, 17, 18, 19, and 20 are soldered to a heat-sinking ground plane. See Figure 14.

# STATIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions 4.75 V  $\leq$  V  $_{DD} \leq$  5.25 V, -40°C  $\leq$  T  $_{A} \leq$  125°C, unless otherwise noted.

| Characteristic                                            | Symbol               | Min          | Тур        | Max        | Unit            |

|-----------------------------------------------------------|----------------------|--------------|------------|------------|-----------------|

| POWER INPUT                                               |                      |              |            |            |                 |

| V <sub>PWR</sub> Supply Current (All Outputs ON)          | I <sub>PWR(ON)</sub> | -            | 1.0        | 50         | μА              |

| V <sub>PWR</sub> Sleep State Supply Current               |                      |              |            |            | μА              |

| V <sub>PWR</sub> =17 V, SPI Bit 7=1, <del>EN</del> =5.0 V | I <sub>PWR(SS)</sub> | -            | 1.0        | 10         |                 |

| Overvoltage Shutdown                                      | V <sub>P(OV)</sub>   | 30           | 33         | 38         | V               |

| Overvoltage Shutdown Hysteresis                           | $V_{P(OV)Hys}$       | 0.3          | 0.5        | 1.5        | V               |

| Logic Supply Current (All Outputs ON)                     | I <sub>DD</sub>      | -            | 1.20       | 5.0        | mA              |

| Logic Supply Current (Sleep State: EN=5.0 V, SPI Bit 7=1) | I <sub>DDSS</sub>    | -            | 1.0        | 25         | μА              |

| Logic Supply Undervoltage Inhibit Threshold               | V <sub>DD(LVI)</sub> | 2.5          | 3.0        | 3.5        | V               |

| INPUT                                                     |                      |              | I          |            |                 |

| Input Voltage (P0, P1, P2, EN, SI, SCLK, CS)              |                      |              |            |            | $V_{DD}$        |

| High                                                      | V <sub>IH</sub>      | 8.0          | _          | 0.2        |                 |

| Low                                                       | V <sub>IL</sub>      |              | _          | 0.2        |                 |

| Dual Mode Threshold (P2)                                  | V <sub>DMH</sub>     | 0.7          | 0.75       | 0.8        | V <sub>DD</sub> |

| Upper Threshold<br>Lower Threshold                        |                      | 0.7          | 0.75       | 0.3        |                 |

|                                                           | V <sub>DML</sub>     |              | 0.20       | 0.0        |                 |

| Input Current                                             | I <sub>INPD</sub>    | 10           | 20         | 30         | μΑ              |

| Pull-Down (P0, P1)-V <sub>IN</sub> =V <sub>DD</sub>       | I <sub>INPD</sub>    | 5.0          | 10         | 30         |                 |

| Pull-Down (P2)-V <sub>IN</sub> =V <sub>DD</sub>           | I <sub>INPU</sub>    | -20          | -10        | -5.0       |                 |

| Pull-Up (CS)-V <sub>IN</sub> =0 V                         | I <sub>INPU</sub>    | -100         | _          | -10        |                 |

| Pull-Up (EN)-V <sub>IN</sub> =0 V                         | I <sub>INPU</sub>    | -10          | 0          | 10         |                 |

| Pull-Up (SCLK, SI)-V <sub>IN</sub> =2.5 V                 | INPU                 |              |            | 10         |                 |

| OUTPUT                                                    |                      |              | T          | ı          | 1               |

| Output Drain to Source ON Resistance (Hex Mode) (Note 4)  | R <sub>DS(ON)</sub>  | 0.20         | 0.5        | 4.0        | Ω               |

| $I_0 = 0.35 \text{ A}, T_J = -40^{\circ}\text{C}$         |                      | 0.39<br>0.51 | 0.5<br>0.7 | 1.2<br>1.2 |                 |

| I <sub>O</sub> =0.35 A, T <sub>J</sub> =25°C              |                      | 0.51         | 1.0        | 1.2        |                 |

| I <sub>O</sub> =0.35 A, T <sub>J</sub> =150°C             |                      | 0.51         | 1.0        | 1.2        |                 |

| Output Voltage Clamp                                      | BV <sub>DSS</sub>    | 50           |            | 00         | V               |

| I <sub>DS</sub> =20 mA, Output Off                        |                      | 50           | 55         | 60         |                 |

| I <sub>DS</sub> =200 mA, Output Off                       |                      | 50           | 56         | 60         |                 |

| Output Leakage Current (Hex Mode)                         | I <sub>O(SS)</sub>   |              |            |            | μА              |

| EN=H, bit 7=1, V <sub>DRAIN</sub> =24 V                   |                      | 0            | -          | 10         |                 |

| Output Logic Voltage (SO), I <sub>LOAD</sub> =1.0 mA      |                      |              |            |            | V <sub>DD</sub> |

| High                                                      | V <sub>OH</sub>      | 0.8          | _          | -          |                 |

| Low                                                       | V <sub>OL</sub>      | -            | _          | 0.2        |                 |

| Output Tristate Leakage (SO), V <sub>SO</sub> =2.5 V      | I <sub>SOT</sub>     | -10          | -          | 10         | μΑ              |

| Notes                                                     |                      |              | ı          | l .        | 1               |

<sup>4.</sup> This parameter is specified for hex mode. In dual mode, the parameter will be three times smaller.

# STATIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions  $4.75~\text{V} \le \text{V}_{DD} \le 5.25~\text{V}$ ,  $-40^{\circ}\text{C} \le \text{T}_{A} \le 125^{\circ}\text{C}$ , unless otherwise noted.

| Characteristic                                   | Symbol              | Min | Тур | Max | Unit     |

|--------------------------------------------------|---------------------|-----|-----|-----|----------|

| FAULT DETECTION                                  |                     |     |     |     |          |

| Output Self-Limiting Current (Hex Mode) (Note 5) | I <sub>O(LIM)</sub> |     |     |     | Α        |

| Outputs Programmed ON                            |                     | 1.0 | 1.5 | 2.0 |          |

| Output Fault Detect Threshold Voltage            | V <sub>OF(TH)</sub> |     |     |     | $V_{DD}$ |

| Outputs Programmed OFF, EN=0                     |                     | 0.5 | 0.6 | 0.7 |          |

| Output OFF Open Load Detect Current              | I <sub>O(OFF)</sub> |     |     |     | μА       |

| Output Programmed OFF, EN=0                      |                     | 20  | 40  | 80  |          |

### Notes

<sup>5.</sup> This parameter is specified for hex mode. In dual mode, the parameter will be three times smaller.

# **DYNAMIC ELECTRICAL CHARACTERISTICS**

Characteristics noted under conditions 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, unless otherwise noted.

| Characteristic                                                                                                          | Symbol              | Min | Тур  | Max | Unit |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|---------------------|-----|------|-----|------|--|--|--|

| OUTPUT TIMING                                                                                                           |                     |     |      |     |      |  |  |  |

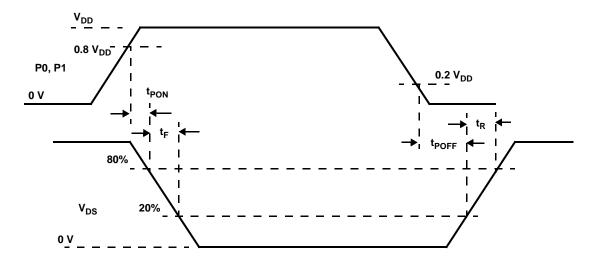

| Output Rise Time $V_{PWR}$ =14 V, $R_{LOAD}$ =25 $\Omega$ , 20–80%                                                      | t <sub>R</sub>      | 1.0 | 1.2  | 10  | μS   |  |  |  |

| Output Fall Time                                                                                                        | t <sub>F</sub>      | 1.0 |      | 40  | μS   |  |  |  |

| V <sub>PWR</sub> =14 V, R <sub>LOAD</sub> =25 Ω, 80–20%                                                                 |                     | 1.0 | 2.0  | 10  |      |  |  |  |

| Output Turn-Off Propagation Delay                                                                                       | t <sub>PON</sub>    | 1.0 | 4.0  | 10  | μ\$  |  |  |  |

| Output Turn-Off Propagation Delay                                                                                       | t <sub>POFF</sub>   | 1.0 | 4.0  | 10  | μ\$  |  |  |  |

| FAULT TIMING                                                                                                            | T                   | 1   |      | 1   | T    |  |  |  |

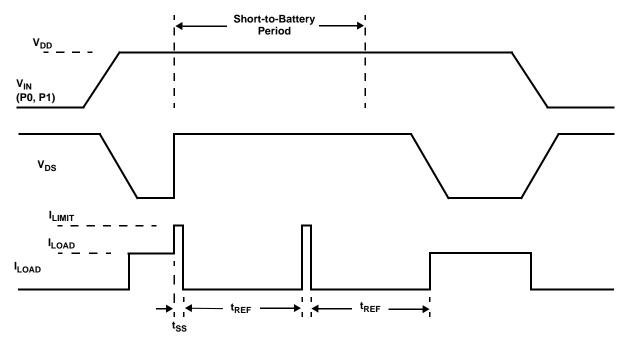

| Output Short-to-Battery Fault Filter Time                                                                               | t <sub>SS</sub>     | 30  | 50   | 90  | μS   |  |  |  |

| Output Refresh Timer                                                                                                    | t <sub>REF</sub>    | 3.0 | 4.1  | 6.0 | ms   |  |  |  |

| Output Refresh Timer Duty Cycle                                                                                         | D                   | 0.2 | 1.56 | 3.0 | %    |  |  |  |

| Output Off-State Open Circuit Fault Filter Time                                                                         | t <sub>OOF</sub>    | 30  | 50   | 90  | μS   |  |  |  |

| SPI/MISCELLANEOUS TIMING                                                                                                |                     |     |      |     |      |  |  |  |

| SO Disable Time (10 K Pull-Up Resistor on SO) $\overline{\text{CS}} = 0.8 \text{ V to SO} > 0.8^* \text{V}_{\text{DD}}$ | t <sub>SODIS</sub>  | _   | 80   | 110 | ns   |  |  |  |

| SO Enable Time (10 K Pull-Up Resistor on SO)  CS=0.8 V to SO Low Impedance                                              | t <sub>SOEN</sub>   | -   | 80   | 110 | ns   |  |  |  |

| SO Rise Time<br>CL < 200 pF                                                                                             | t <sub>SORISE</sub> | _   | 30   | 50  | ns   |  |  |  |

| SO Fall Time<br>CL < 200 pF                                                                                             | t <sub>SOFALL</sub> | _   | 30   | 50  | ns   |  |  |  |

| SO Valid Time Falling Edge of SCLK to SO Valid                                                                          | t <sub>VALID</sub>  | _   | 65   | 80  | ns   |  |  |  |

| Required Time Between Falling Edge of $\overline{\text{CS}}$ to Rising Edge of SCLK                                     | t <sub>LEAD</sub>   | -   | 100  | 140 | ns   |  |  |  |

| Required TIme Between Rising Edge of $\overline{\text{CS}}$ to Falling Edge of SCLK                                     | t <sub>LAG</sub>    | _   | 0    | 50  | ns   |  |  |  |

| Required Time Between SI to Rising Edge of SCLK                                                                         | t <sub>SU</sub>     | _   | 25   | 45  | ns   |  |  |  |

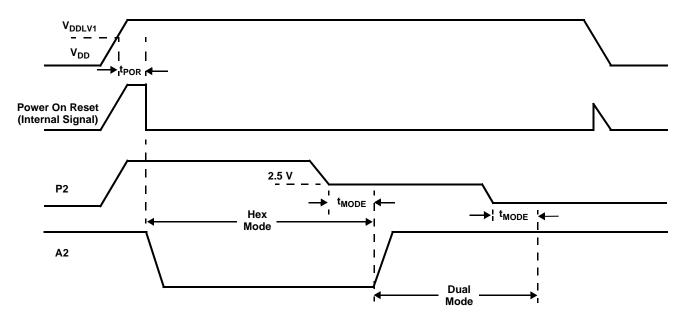

| POR/EN Wake-Up Timer                                                                                                    | t <sub>POR</sub>    | 20  | 40   | 60  | μS   |  |  |  |

| Mode Change Timer (P2)                                                                                                  | t <sub>MODE</sub>   | 5.0 | 10   | 25  | μS   |  |  |  |

# **Timing Diagrams**

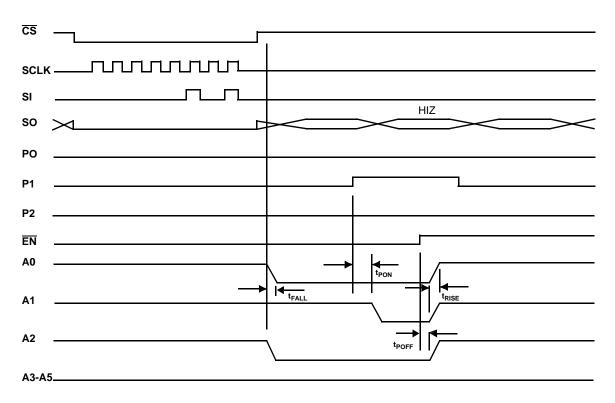

Figure 2. SPI Timing Diagram

Note: In hex mode, the outputs are controlled by the SPI or by the parallel inputs. However, P0, P1, and P2 only control A0, A1, and A2, respectively. When  $\overline{\text{EN}}$  goes high, the part is disabled.

Figure 3. Operation Waveforms for Hex Control

Figure 4. Response Times

Figure 5. Short-to-Battery Fault

Figure 6. Power On Reset and Mode Select

# **TYPICAL CHARACTERISTICS**

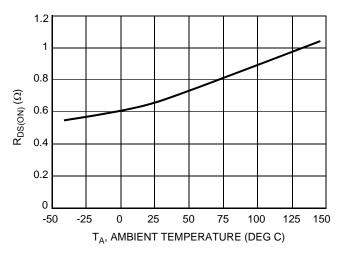

Figure 7. Output on Resistance versus Temperature

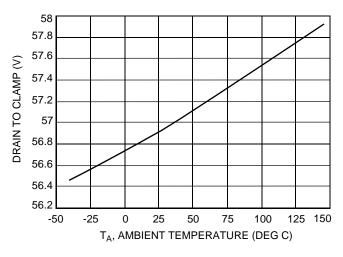

Figure 8. Drain to Source Clamp versus Temperature

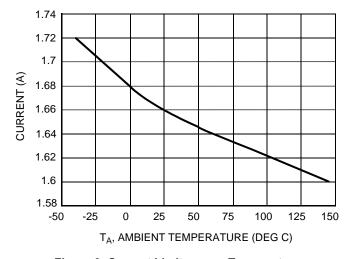

Figure 9. Current Limit versus Temperature

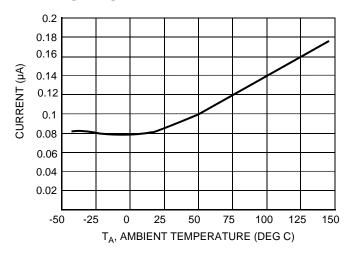

Figure 10. I<sub>VPWR</sub> versus Temperature

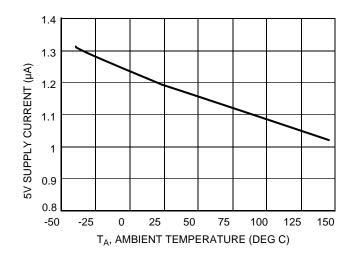

Figure 11.  $I_{DD}$  versus Temperature

Figure 12. I<sub>DD</sub> Sleep State versus Temperature

#### **SPI Output Word Definition SPI Input Word Definition** MSB <DOUT A0 Enable A0 Fault A1 Enable A1 Fault A2 Enable A2 Fault A3 Enable A3 Fault A4 Enable A4 Fault A5 Enable A5 Fault Not Used (Don't Care) Zero Sleep Mode Feedback (1=Sleep Mode Enabled) Enable Sleep Mode

The device will power up with sleep mode enabled.

In dual mode, input bits 0, 4, and 5 must all be high to turn on combinational output A0, A4, and A5 via the SPI.

In dual mode, input bits 1, 2, and 3 must all be high to turn on combinational output A1, A2, and A3 via the SPI.

Figure 13. SPI Input/Output Word Definition

**Table 1. Truth Table**

|    | Inputs |       | EN  | SPI Outputs |     |     | Comments |     |     |     |                                                                                                       |

|----|--------|-------|-----|-------------|-----|-----|----------|-----|-----|-----|-------------------------------------------------------------------------------------------------------|

| P0 | P1     | P2    | LIN | Bit7        | A0  | A1  | A2       | А3  | A4  | A5  | Comments                                                                                              |

| 0  | 0      | 0     | 0   | Х           | OFF | OFF | OFF      | *   | *   | *   | HEX MODE                                                                                              |

| 0  | 0      | 1     | 0   | Х           | OFF | OFF | ON       | *   | *   | *   | * = Outputs A3, A4, and A5 are SPI controlled only.                                                   |

| 0  | 1      | 0     | 0   | Х           | OFF | ON  | OFF      | *   | *   | *   | X = Don't care. Outputs A0, A1, and A2 are controlled either via SPI or inputs                        |

| 0  | 1      | 1     | 0   | Х           | OFF | ON  | ON       | *   | *   | *   | P0, P1, and P2.                                                                                       |

| 1  | 0      | 0     | 0   | Х           | ON  | OFF | OFF      | *   | *   | *   |                                                                                                       |

| 1  | 0      | 1     | 0   | Х           | ON  | OFF | ON       | *   | *   | *   |                                                                                                       |

| 1  | 1      | 0     | 0   | Х           | ON  | ON  | OFF      | *   | *   | *   |                                                                                                       |

| 1  | 1      | 1     | 0   | Х           | ON  | ON  | ON       | *   | *   | *   |                                                                                                       |

| 0  | 0      | 0     | 1   | 0           | OFF | OFF | OFF      | OFF | OFF | OFF | HEX MODE                                                                                              |

| 0  | 0      | 1     | 1   | 0           | OFF | OFF | ON       | OFF | OFF | OFF | Outputs A3, A4, and A5 are always OFF.                                                                |

| 0  | 1      | 0     | 1   | 0           | OFF | ON  | OFF      | OFF | OFF | OFF | Outputs are not controlled via SPI. Outputs A0, A1, and A2 are only controlled via inputs P0, P1,     |

| 0  | 1      | 1     | 1   | 0           | OFF | ON  | ON       | OFF | OFF | OFF | and P2.                                                                                               |

| 1  | 0      | 0     | 1   | 0           | ON  | OFF | OFF      | OFF | OFF | OFF | Sleep mode disabled.                                                                                  |

| 1  | 0      | 1     | 1   | 0           | ON  | OFF | ON       | OFF | OFF | OFF |                                                                                                       |

| 1  | 1      | 0     | 1   | 0           | ON  | ON  | OFF      | OFF | OFF | OFF |                                                                                                       |

| 1  | 1      | 1     | 1   | 0           | ON  | ON  | ON       | OFF | OFF | OFF |                                                                                                       |

| 0  | 0      | 2.5 V | 0   | Х           | OFF | OFF | OFF      | OFF | OFF | OFF | DUAL MODE                                                                                             |

| 0  | 1      | 2.5 V | 0   | Х           | OFF | ON  | ON       | ON  | OFF | OFF | Outputs are also controlled via SPI. SPI fully functional.                                            |

| 1  | 0      | 2.5 V | 0   | Х           | ON  | OFF | OFF      | OFF | ON  | ON  |                                                                                                       |

| 1  | 1      | 2.5 V | 0   | Х           | ON  | ON  | ON       | ON  | ON  | ON  |                                                                                                       |

| 0  | 0      | 2.5 V | 1   | 0           | OFF | OFF | OFF      | OFF | OFF | OFF | DUAL MODE                                                                                             |

| 0  | 1      | 2.5 V | 1   | 0           | OFF | ON  | ON       | ON  | OFF | OFF | Outputs are not controlled via SPI. Outputs are controlled via inputs P0 and P1. Sleep mode disabled. |

| 1  | 0      | 2.5 V | 1   | 0           | ON  | OFF | OFF      | OFF | ON  | ON  | impate i o ana i i. oleep mode disabled.                                                              |

| 1  | 1      | 2.5 V | 1   | 0           | ON  | ON  | ON       | ON  | ON  | ON  |                                                                                                       |

| Х  | Х      | Х     | 1   | 1           | OFF | OFF | OFF      | OFF | OFF | OFF | All outputs disabled. SPI is reset and ignored. No fault detection.                                   |

Figure 14. Approximate Thermal Resistance Using PCB Heat Sinking

## SYSTEM/APPLICATION INFORMATION

#### INTRODUCTION

The 33397 is a versatile dual-mode low-side switch that can be output-configured as two 333 m $\Omega$  open drain outputs in the dual mode or as six 900 m $\Omega$  open drain outputs in the hex mode (R<sub>DS(ON)</sub> @ 25°C).

Each open drain output has internal current limit and short-circuit protection. Current limit is typically 1.5 A, with 2.0 A maximum. The outputs can be input controlled via parallel inputs or the SPI. Three inputs provide parallel control, while a

serial 8-bit word provides SPI control of the outputs. Output fault detection capability includes OFF-state open loads and ON-state short-to-battery conditions. Individual output faults are latched into the fault register and serially shifted out during serial communication to the 33397. The 33397 has both overvoltage and undervoltage shutdown.

A low quiescent current sleep slate feature can be enabled or disabled on command via the SPI port.

#### **FUNCTIONAL PIN DESCRIPTION**

## $V_{DD}$

Logic power supply pin.

#### A0-A5

A0–A5 are the drains of the 1.2  $\Omega$  (max.) MOSFETs. They each have an internal voltage clamp of 50 V (min.) to clamp inductive loads during turn-off. When enabled, they are each internally current limited to a maximum of 2.0 A. If any output is in current limit (output voltage >3.0 V) for a time greater than  $t_{SS}$ , the output will be disabled for a time  $t_{REF}$  and then try to turn on again. When disabled, open circuits are detected if the output is less than 3.0 V for a time of  $t_{SS}$ . Either type of fault is reported as a fault on the SPI output word. If  $\overline{EN}$  input is high and SPI bit 7=1, the pull-down current sources on the outputs are disabled to minimize  $V_{DD}$  supply current.

In hex mode, all six outputs are independent. Outputs A0, A1, and A2 are controlled by either the SPI input word bits 0, 1, and 2, respectively, or parallel inputs P0, P1, and P2. Outputs A3, A4, and A5 are controlled only by SPI input word bits 3, 4, and 5, respectively.

In dual mode, outputs A0, A4, and A5 are all controlled simultaneously by input P0 or by SPI bits 0, 4, and 5. All three bits must be high to enable this output via the SPI. Outputs A1, A2, and A3 are all controlled simultaneously by input P1 or by SPI bits 1, 2, and 3. All three bits must be high to enable this output via the SPI.

## P0-P2

In hex mode, P0 is the parallel input to control output A0. It is OR'd with SPI bit 0 to enable output A0. Either one will enable output A0. In dual mode, P0 controls outputs A0, A4, and A5 simultaneously. P0 has a pull down current of 10  $\mu$ A. It is ignored when  $\overline{\text{EN}}$  is high and bit 7=1.

In hex mode, P1 is the parallel input to control output A1. It is OR'd with SPI bit 1 to enable output A1. Either one will enable output A1. In dual mode, P1 controls outputs A1, A2, and A3 simultaneously. P1 has a pull-down current of 10  $\mu$ A. It is ignored when  $\overline{\text{EN}}$  is high and bit 7=1.

In hex mode, P2 is the parallel input to control output A2. It is OR'd with SPI bit 2 to enable output A2. Either one will enable output A2.

P2 also is used to program the 33397 to either a dual or hex output device. The 33397 will be the hex mode if P2 is biased above  $0.75^*V_{DD}$  (typical) or below  $0.25^*V_{DD}$  (typical). Normal 5.0~V control logic on this parallel input will maintain the 33397 in hex mode and allow control of output A2. If  $0.25^*V_{DD}$  <P2<0.75\*V<sub>DD</sub> for more than 10 µs, the 33397 will switch to dual mode. P2 has a pull-down current of 10 µA. It is ignored when  $\overline{EN}$  is high and bit 7=1.

# $V_{PWR}$

$V_{PWR}$  is used to sense an overvoltage condition on the supply pin. When the voltage on  $V_{PWR}$  exceeds  $V_{OV},$  all outputs are disabled for the duration of the overvoltage condition. If  $V_{PWR}$  is grounded, overvoltage shutdown is disabled.  $V_{PWR}$  threshold can be modified with an external resistor divider if higher thresholds are desired.

# **SCLK**

SCLK is the clock for the serial interface.

# SI

SI is the serial input for the SPI port. When  $\overline{CS}$  is low, SI is read on the positive edge of SCLK and SO is updated on the falling edge. When  $\overline{CS}$  is high, SI is ignored. SI has a pull-down current source to pull it low in the event of an open circuit.

## SO

SO is the serial output of the SPI port. When  $\overline{\text{CS}}$  goes low, SO outputs bit 7 of the output word. On each falling edge of SCLK, SO will shift the next SPI output bit until on the eighth SCLK falling edge the bit present on SI during the first rising edge will appear. In this way devices can be daisy-chained to operate on a common  $\overline{\text{CS}}$ . When  $\overline{\text{CS}}$  is high, SO is high impedance.

# $\overline{\mathsf{cs}}$

$\overline{\text{CS}}$  is the chip select to enable the SPI interface. When  $\overline{\text{CS}}$  is high, no SPI communication is possible. When  $\overline{\text{CS}}$  goes low, SI will be read on each rising  $\underline{\text{SCLK}}$  edge and SO will shift on each SCLK falling edge. When  $\overline{\text{CS}}$  goes high, the bits present in the SPI input register will be interpreted as the SPI input command. Also when  $\overline{\text{CS}}$  goes high, all faults that were latched into the SPI output register are cleared. If faults are still present on outputs, they will be re-latched after  $t_{\text{SS}}$ .

## EN

$\overline{\text{EN}}$  must be low for complete IC functionality in either the dual or hex mode. When  $\overline{\text{EN}}$  transitions low while in the sleep mode

or when the IC is powered up from  $V_{DD}$ , a power-up timer of 40  $\mu s$  is started to allow the 33397 to determine which mode it is in (hex or dual). During this time all parallel inputs and serial control SPI bits will be ignored and all outputs will remain off. If  $\overline{EN}$  transitions low when not in the sleep mode, this "dead" time will not occur.

If a one was written to bit 7, the 33397 will be in the sleep mode when  $\overline{\text{EN}}$  goes high. In this mode all SPI registers are reset to zero and all faults are cleared. No fault detection is possible. The standby supply current on  $V_{DD}$  and  $V_{PWR}$  is minimized.

#### **APPLICATIONS**

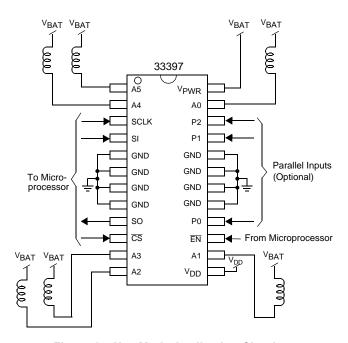

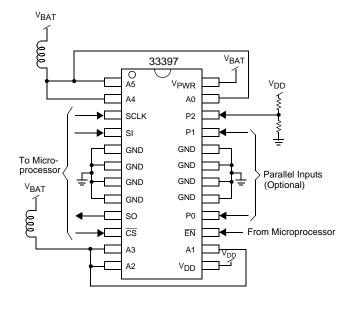

A voltage on the P2 input pin determines the mode. All six outputs can operate either independently (hex mode) (Figure 15) or in paralleled groups of three (dual mode) (Figure 16). In the dual mode, outputs A0, A1, and A2 are controlled by parallel inputs P0, P1, and P2, respectively, and they are also controlled by the SPI port with which they are OR'd. On the other hand, outputs A3, A4, and A5 are controlled only through the SPI port. When the voltage on P2 is between

$0.25~V_{DD}$  and  $0.75~V_{DD}$  (i.e., when P2 is held at an intermediate voltage, neither high nor low), the 33397 operates in the dual mode. However, the P2 pin must stay at that level for a minimum specified time. In this mode, outputs A0, A4, and A5 are all controlled in parallel by input P0. Outputs A1, A2, and A3 are all controlled in parallel by input P1. Both outputs can also be controlled via the SPI port as well, but only if the three outputs are commanded ON at the same time.

Figure 15. Hex Mode Application Circuit

Figure 16. Dual Mode Application Circuit

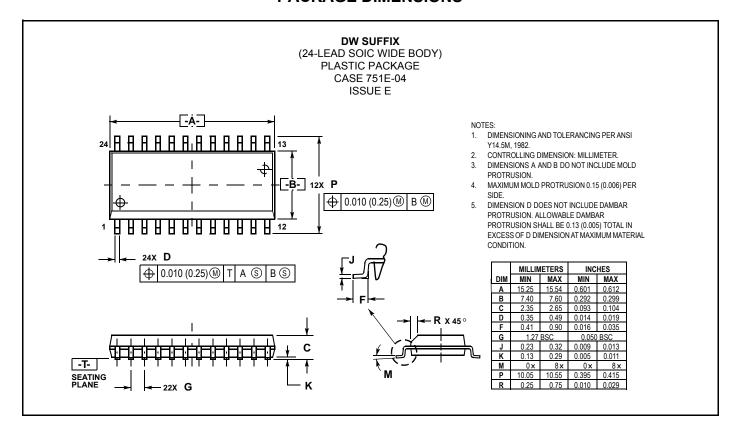

# **PACKAGE DIMENSIONS**

# **NOTES**

# **NOTES**

# **NOTES**

Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

MOTOROLA and the Stylized M Logo are registered in the US Patent and Trademark Office. All other product or service names are the property of their respective owners.

© Motorola, Inc. 2003

#### **HOW TO REACH US:**

USA/EUROPE/LOCATIONS NOT LISTED: Motorola Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-800-521-6274 or 480-768-2130 JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center 3-20-1 Minami-Azabu. Minato-ku, Tokyo 106-8573, Japan 81-3-3440-3569

**ASIA/PACIFIC:** Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong 852-26668334

HOME PAGE: http://motorola.com/semiconductors