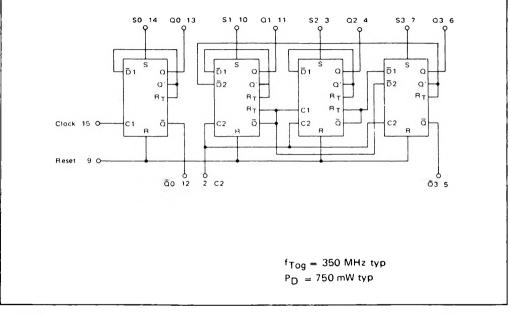

## **Bi-Quinary Counter**

The MC1678 is a four-bit counter capable of divide-by-two, divide-by-five, or divideby-10 functions. When used independently, the divide-by-two section will toggle at 350 MHz typically, while the divide-by-five section will toggle at 325 MHz typically. Clock inputs trigger on the positive going edge of the clock pulse. Set and Reset inputs override the clock, allowing asynchronous "set" or "clear". Individual Set and common Reset inputs are provided, as well as complementary outputs for the first and fourth bits. True outputs are available at all bits.\*

### COUNTER TRUTH TABLES

#### BCD

#### **BI-QUINARY**

(Clock connected to C1 and Q0 connected to C2)

| COUNT            | 00   | Q1   | Q2   | 03 |

|------------------|------|------|------|----|

| 0<br>1<br>2<br>3 | LIL  | LLHH |      |    |

| 4<br>5<br>6<br>7 | LILI | LLII | IIII |    |

| 89               | LH   | L    | LL   | II |

(Clock connected to C2 and Q3 connected to C1)

| COUNT            | Q1   | 02   | Q3      | 00   |

|------------------|------|------|---------|------|

| 0<br>1<br>2<br>3 | TLTL | LIII |         |      |

| 4<br>5<br>6<br>7 | LLHL | LLLE | I L L L | LIII |

| 8<br>9           | HL   | HL   | LH      | HH   |

#### B-S

| с | R | s | Qn + 1 |

|---|---|---|--------|

| 0 | L | L | Q,     |

| ø | н | L | н      |

| ¢ | L | н | н      |

| ø | н | н | ND     |

ç = Don't Care

ND = Not Defined

MC1678

# COUNTERS