## TRUTH TABLE

| Ć | V1 V2   | 00n+1 | 000.1 |

|---|---------|-------|-------|

| н | V1>V2   | H     | l.    |

| н | V1 < V2 | ١.    | T     |

| L | 0 0     | 00n   | 00n   |

o - Don't Care

$V_{CC} = +5.0 V = Pin 7, 10$

$V_{EE} = -5.2 V = Pin 8$

Gnd = Pin 1, 16

$P_D = 330 \text{ mW typ/pkg (No Load)}$

$t_{pd} = 3.5 \text{ ns typ (MC1650)}$ = 3.0 ns typ (MC1651)

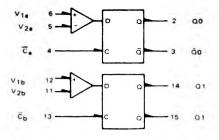

## Dual A/D Comparator

The MC1650 and the MC1651 are very high speed comparators utilizing differential amplifier inputs to sense analog signals above or below a reference level. An output latch provides a unique sample-hold feature. The MC1650 provides high impedance Darlington inputs, while the MC1651 is a lower impedance option, with higher input slew rate and higher speed capability. Complementary outputs permit maximum utility for applications in high speed test equipment, frequency measurement, sample and hold, peak voltage detection, transmitters, receivers, memory translation, sense amplifiers and more.

The clock inputs ( $\overline{C}_a$  and  $\overline{C}_b$  operate from MECL III or MECL 10,000 digital levels. When  $\overline{C}_a$  is at a logic high level, Q0 will be at a logic high level provided that  $V_1 \geq V_2$  ( $V_1$  is more positive than  $V_2$ ).  $\overline{Q}_0$  is the logic complement of Q0. When the clock input goes to a low logic level, the outputs are latched in their present state.