# **Dual Tone Multiple Frequency Line Interface**

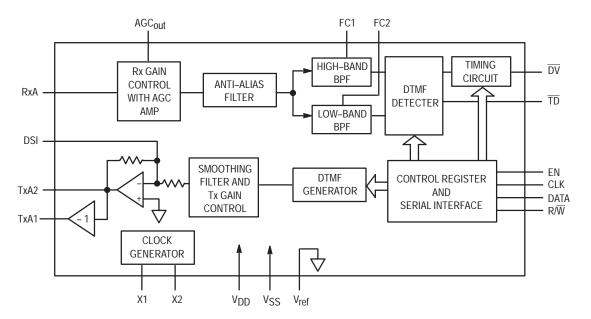

The MC145740 is a silicon gate HCMOS LSI designed for general purpose Dual Tone Multiple Frequency (DTMF) communications, and contains a DTMF signal generator and a receiver for all 16 standard digits.

The generator block has a differential line driver which drives a  $600\,\Omega$  load with 0 dBm level. The transmit signal level is adjusted in 1 dB steps by the programmable attenuator.

The receiver block has an Auto Gain Control (AGC) amplifier to demodulate 50 dB (typ) dynamic range of DTMF signals to the hexadecimal codes.

The device also includes a serial control interface that permits a CPU to exercise the following built–in features.

- Single Power Supply: 3.6 to 5.5 V

- DTMF Generator and Receiver for All 16 Standard Digits

- 0 dBm Line Driver Into 600  $\Omega$  Load

- AGC Amplifier

- Programmable Transmit Attenuator

- Serial Control Interface

- Power Down Mode, Less Than 1 μA

# MC145740

# **BLOCK DIAGRAM**

REV 1 6/00

# MAXIMUM RATINGS (Voltages Referenced to VSS Unless Otherwise Noted)

| Ratings                   | Symbol           | Value                         | Unit |

|---------------------------|------------------|-------------------------------|------|

| DC Supply Voltage         | Vcc              | -0.5 to 7.0                   | V    |

| Input Voltage, All Pins   | V <sub>in</sub>  | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| DC Current Per Pin        | I                | ±20                           | mA   |

| Power Dissipation         | PD               | 500                           | mW   |

| Storage Temperature Range | T <sub>stg</sub> | -65 to 150                    | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid applications of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation, it is recommended that  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \leq (V_{in} \text{ or } V_{out}) \leq V_{DD}.$

Reliability of operation is enhanced if unused logic inputs are tied to an appropriate logic voltage level (e.g., either VSS or VDD).

# RECOMMENDED OPERATING CONDITIONS

| Parameter                   | Symbol                          | Min | Тур    | Max | Unit |

|-----------------------------|---------------------------------|-----|--------|-----|------|

| DC Supply Voltage           | Vcc                             | 3.6 | 5      | 5.5 | V    |

| Input Voltage, All Pins     | V <sub>in</sub>                 | 0   | _      | Vcc | V    |

| Input Rise or Fall Time     | t <sub>r</sub> , t <sub>f</sub> | 0   | _      | 500 | ns   |

| Crystal Frequency           | f <sub>osc</sub>                | _   | 3.5795 | _   | MHz  |

| Operating Temperature Range | T <sub>A</sub>                  | -20 | 25     | 70  | °C   |

# DC ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 5 V $\pm$ 10%, T<sub>A</sub> = - 20 to 70°C)

| Parameter          | r             | Symbol          | Condition                                            | Min                   | Тур                    | Max        | Unit |

|--------------------|---------------|-----------------|------------------------------------------------------|-----------------------|------------------------|------------|------|

| Input Voltage      | H Level       | VIH             |                                                      | 3.15                  | _                      | _          | V    |

| EN, CLK, DATA, R/W | L Level       | V <sub>IL</sub> |                                                      | _                     | _                      | 1.1        |      |

| Output Voltage     | H Level       | VOH             | ΙΟΗ = 20 μΑ                                          | V <sub>CC</sub> - 0.1 | V <sub>CC</sub> - 0.01 | _          | V    |

| DV, TD, DATA       | L Level       | VOL             | I <sub>OL</sub> = -20 μA<br>I <sub>OL</sub> = -2 mA  | _                     | 0.01<br>—              | 0.1<br>0.4 |      |

| Input Current R/W, | DATA, EN, CLK | l <sub>in</sub> | V <sub>in</sub> = V <sub>DD</sub> or V <sub>SS</sub> | _                     | ±1.0                   | ±10.0      | μА   |

| Supply Current     |               | I <sub>DD</sub> | DTMF Tx Mode                                         | _                     | 5                      | _          | mA   |

|                    |               |                 | DTMF Rx Mode                                         | _                     | 8                      | _          |      |

| Standby Current    |               | I <sub>DD</sub> | Power Down 1                                         | _                     | _                      | 500        | μА   |

|                    |               |                 | Power Down 2                                         | _                     | _                      | 1          |      |

# **AC ELECTRICAL CHARACTERISTICS**

# DTMF TRANSMIT CHARACTERISTICS (V<sub>CC</sub> = 5 V $\pm 10\%$ , T<sub>A</sub> = $-20^{\circ}$ to $70^{\circ}$ C)

| Parameter                            |            | Symbol          | Condition                                                   | Min | Тур | Max | Unit |

|--------------------------------------|------------|-----------------|-------------------------------------------------------------|-----|-----|-----|------|

| Transmit Level                       | Low Group  | V <sub>fl</sub> | Attenuator = 0 dB                                           | _   | 2.5 | _   | dBm  |

|                                      | High Group | V <sub>fh</sub> | f <sub>OSC</sub> = 3.579545 MHz<br>VTxA1 <sup>-</sup> VTxA2 | _   | 3.5 | _   |      |

| High Group Pre–Emphasis              |            | PE              | $R_L = 1.2 \text{ k}\Omega$                                 | 0   | _   | 3   | dB   |

| DTMF Distortion                      |            | DIST            |                                                             | _   | 5   | _   | %    |

| DTMF Frequency Va                    | ariation   | ΔfV             |                                                             | -1  | _   | 1   | %    |

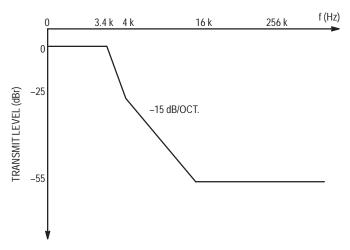

| Out-of-Band Energy<br>(See Figure 1) |            | VOE             |                                                             | _   | _   | _   |      |

| Setup Time                           |            | tosc            |                                                             | _   | 4   | _   | ms   |

# TRANSMIT ATTENUATOR CHARACTERISTICS (V<sub>CC</sub> = 5 V $\pm 10\%$ , T<sub>A</sub> = $-20^{\circ}$ to $70^{\circ}$ C)

| Parameter           | Symbol | Condition     | Min  | Тур | Max | Unit |

|---------------------|--------|---------------|------|-----|-----|------|

| Attenuator Range    | ARNG   |               | 0    | _   | 15  | dB   |

| Attenuator Accuracy | AACC   | 1 dB – 5 dB   | -0.5 | _   | 0.5 | dB   |

|                     |        | 6 dB – 9 dB   | -1   | _   | 1   |      |

|                     |        | 10 dB – 15 dB | -1.7 | _   | 1   |      |

# DTMF RECEIVER CHARACTERISTICS (V<sub>CC</sub> = 5 V $\pm 10\%$ , T<sub>A</sub> = $-20^{\circ}$ to $70^{\circ}$ C)

| Parameter               |           | Symbol | Condition        | Min         | Тур | Max  | Unit |

|-------------------------|-----------|--------|------------------|-------------|-----|------|------|

| Input Impedance         |           | RIDTMF |                  | 50          | _   | _    | kΩ   |

| Detect Signal Level (Ea | ach Tone) |        |                  | -48         | _   | 0    | dBm  |

| Twist (High Group/Low   | Group)    |        |                  | -10         | _   | 10   | dB   |

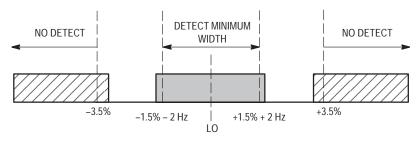

| Frequency Detect Band   | d Width   |        | See Figure 3     | ±1.5% ±2 Hz | _   | _    | % fc |

| Frequency Reject Band   | d Width   |        | ]                | _           | _   | ±3.5 |      |

| DTMF Detect Timing      | OFF to ON | TVDON  | CD1 = 0, CD0 = 1 | _           | 20  | _    | ms   |

| (See Figure 2)          |           |        | CD1 = 1, CD0 = 0 | _           | 30  | _    |      |

|                         |           |        | CD1 = 1, CD0 = 1 | _           | 40  | _    |      |

| ON to OFF               |           | TVDOFF | CD1 = 0, CD0 = 1 | _           | 20  | _    |      |

|                         |           |        | CD1 = 1, CD0 = 0 | _           | 30  | _    |      |

|                         |           |        | CD1 = 1, CD0 = 1 | _           | 20  | _    |      |

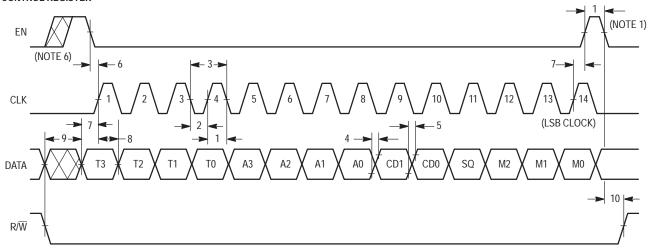

# **SWITCHING CHARACTERISTICS** ( $V_{CC} = 5 \text{ V} \pm 10\%$ , $T_A = -20^{\circ}$ to $70^{\circ}$ C, See Figure 4)

| Parame               | eter             | Symbol           | Number | Min | Тур | Max | Unit |

|----------------------|------------------|------------------|--------|-----|-----|-----|------|

| Pulse Width (H)      | EN, SCK          | <sup>t</sup> wh  | 1      | 50  | _   | _   | ns   |

| Pulse Width (L)      | EN, SCK          | t <sub>Wl</sub>  | 2      | 50  | _   | _   | ns   |

| Clock Cycle          |                  | t <sub>C</sub>   | 3      | 100 | _   | _   | ns   |

| Input Rise Time      |                  | t <sub>r</sub>   | 4      | _   | _   | 2   | μs   |

| Input Fall Time      |                  | tf               | 5      | _   | _   | 2   | μs   |

| Recovery Time        | EN to SCK        | t <sub>rec</sub> | 6, 18  | 50  | _   | _   | ns   |

| Setup Time           | DATA to SCK      | t <sub>su</sub>  | 7      | 50  | _   | _   | ns   |

|                      | R/W Low to DATA  |                  | 9      | 100 | _   | _   | 1    |

|                      | R/W High to DATA |                  | 12     | 50  | _   | _   | 1    |

| Hold Time            | SCK to DATA      | th               | 8      | 50  | _   | _   | ns   |

|                      | EN to R/W        |                  | 10     | 50  | _   | _   | 1    |

|                      | DATA to R/W      |                  | 14     | 50  | _   | _   | 1    |

|                      | R/W to DATA      |                  | 15     | 50  | _   | _   | 1    |

| Read Data Delay Time | EN to DATA       | t <sub>d</sub>   | 13     | _   | _   | 50  | ns   |

|                      | SCK to DATA      |                  | 17     | _   | _   | 50  | 1    |

Figure 1. Out-of-Band Energy

# NOTES:

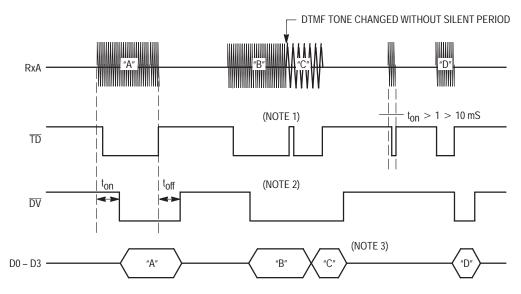

- The high-to-low and low-to-high transition on the TD pin will appear immediately after the valid DTMF tones are detected. The TD will also output a short H pulse when the device detects the DTMF tones being changed without a silent period.

- 2. The high-to-low and low-to-high transition on the  $\overline{\text{DV}}$  pin will appear after the programmed guard time determined by two bits of serial data (CD1, CD0).

- 3. The device recognizes the DTMF tones changed without a silent period, and the four bits of data can be read from the status register.

Figure 3. DTMF Frequency Detect Band Width

# CONTROL REGISTER

# STATUS REGISTER

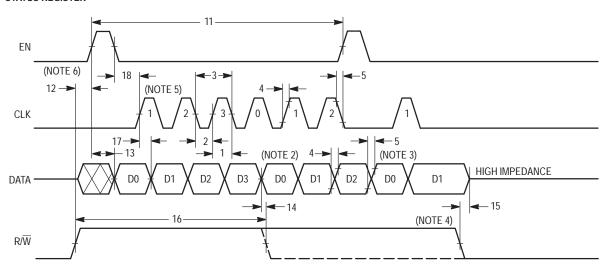

# NOTES:

- 1. The data in front of the EN signal will be latched.

- 2. The latched data will be repeated until there is an EN pulse.

- 3. The detected data will be updated with the next EN pulse.

- 4. After the  $R/\overline{W}$  pin becomes inactive, the data will be lost.

- 5. D1 corresponds to CLK1.

- 6. The EN and CLK signals need to be set at the logic low level when the  $R/\overline{W}$  signal changes.

- 7. The CLK signal must be held low when the EN signal is high.

Figure 4. Serial Interface Timing

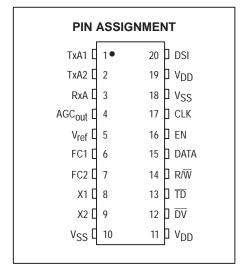

#### PIN DESCRIPTIONS

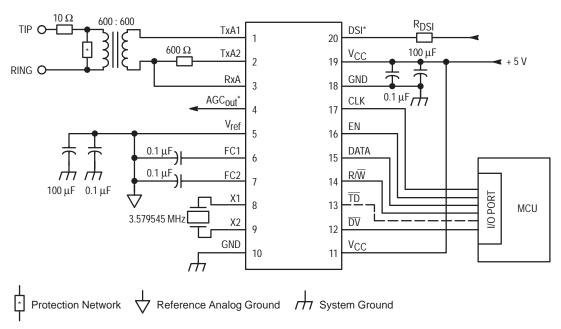

#### TxA1

#### Non-Inverting Analog Output (Pin 1)

This pin is the line driver non–inverting output. A +7 dBm (typ) differential output voltage can be obtained by connecting a 1.2 k $\Omega$  load resistor between TxA1 and TxA2. Note that the DSI input, if used, must be controlled for the output level not to exceed the above signal level.

#### TxA2

#### **Inverting Analog Output (Pin 2)**

This pin is the driver inverting output. Refer to TxA1.

#### **RxA**

#### **DTMF Receive Input (Pin 3)**

This pin is the DTMF signal input (AGC input).

# **AGC**out

# AGC Output (Pin 4)

This pin is the AGC amplifier output. The signal received from the RxA pin appears at this pin through the AGC amplifier so that any signal receivers can be connected on this pin to decode the non–DTMF signals. The AGC amplifier gain is software programmable as shown in Table 3.

#### Vref

# Reference Analog Ground (Pin 5)

This pin provides the analog ground voltage,  $V_{CC}/2$ , which is internally regulated from  $V_{CC}$ . This pin should be decoupled to GND with 0.1  $\mu$ F and 100  $\mu$ F capacitors.

# FTLC1, FTLC2

# Band-Pass Filter Test (Pins 6, 7)

These pins are high impedance filter outputs. They may be used for testing the DTMF receive high and low band–pass filter characteristics, and are reserved for manufacturer's use only. In normal operation, each pin is decoupled to  $V_{\text{ref}}$  with 0.1  $\mu$ F capacitors.

#### **X1**

# **Crystal Oscillator Output (Pin 8)**

A 3.579545 MHz  $\pm 0.1\%$  crystal oscillator is tied to this pin with the other end connected to X2.

#### X2

# **Crystal Oscillator Input (Pin 9)**

A 3.579545 MHz  $\pm 0.1\%$  crystal oscillator is tied to this pin with the other end connected to X1. X2 may be driven directly from an appropriate external clock source. In this case, X1 should be held open.

#### **GND**

#### **Ground (Pins 10, 18)**

Ground pins are connected to the system ground.

#### Vcc

# Power Supply (Pins 11, 19)

The digital supply pins are connected to the positive power supply (5 V).

#### DV

# **DTMF Data Valid (Pin 12)**

This pin goes low when valid DTMF tones are detected. The guard time of DTMF tone detection  $(t_{on})$  and release

(t<sub>Off</sub>) is programmed by two bits of serial data (CD1, CD0) as shown in Table 2. This feature improves the immunity to the short noise and momentary dropouts. See Figure 2 for the detailed timing diagram.

#### $\overline{\mathsf{TD}}$

# Tone Detect (Pin 13)

This pin goes low immediately after valid DTMF tones are detected, regardless of the guard time set by two bits of serial data. This pin also outputs the short high pulse when the device detects the change of DTMF tones without a silent period. For a detailed description, see Figure 2.

#### R/W

#### Read/Write Data Switch (Pin 14)

This pin is used for controlling the input/output direction of the DATA I/O pin.

#### **DATA**

#### Serial Data Input/Output (Pin 15)

When the  $R/\overline{W}$  pin is at logic low, the DATA pin works as the 14–bit control register input which determines the function mode, DTMF tones, transmit level (or receiver gain level), detect time, and transmit squelch. When the  $R/\overline{W}$  pin is at logic high, the DATA pin works as the 4–bit status register output which provides the hexadecimal codes corresponding to the detected digit.

#### FΝ

# **Enable Input (Pin 16)**

When the  $R/\overline{W}$  pin is held low, high level input to this pin transfers the 14 bits of control register data to the mode control logic, then the function mode is immediately changed. When this pin is at logic low, the control register and the mode control logic are isolated. Therefore, the 14 bits of data in the control register must not be changed while EN is at logic high level.

When the  $R/\overline{W}$  pin is held high, the rising edge of the EN pin loads the DTMF data from the DTMF decoder into the status register, and shifts out the first bit (LSB = D0) to the DATA pin.

#### **CLK**

# SPI Clock Input (Pin 17)

This pin is the SPI clock input for the 14–bit control register and the 4–bit status register. At the rising edge of CLK, the 14 bits of data are captured into the control register when  $R/\overline{W}$  is at logic low, and the 4 bits of data are shifted out from the status register when  $R/\overline{W}$  is at logic high.

#### DSI

#### **Driver Summing Input (Pin 20)**

This pin is the inverting input of the line driver. An external signal source may be connected to this pin through a series resistor R<sub>DSI</sub>, transmitting the signal from the TxA1 and TxA2. The differential gain G<sub>DSI</sub> =  $(V_{TxA1} - V_{TxA2})/V_{DSI}$  is determined by the following equation:

$$G_{DSI} = -2 R_F/R_{DSI}, R_F - 20 k\Omega$$

Note that the programmable transmit attenuator does not affect this case.

The DSI pin should be held open when not in use.

#### **SERIAL DATA INTERFACE**

#### REGISTER MAP DESCRIPTION

The timing diagram of the 14–bit control register input and the 4–bit status register output is shown in Figure 4. When the  $R/\overline{W}$  pin is at logic low (write is selected), the control register is enabled. The 14 bits of data are captured into the control register at the rising edge of SCK. The 14 bits of data in the control register are transferred to the mode control logic at logic high to the EN pin, and then the function mode is immediately changed.

When the  $R/\overline{W}$  pin is at logic high (read is selected), the status register is enabled to read out the decoded DTMF data. At the rising edge of EN, the four bits of data in the DTMF decoder are loaded into the status register, and the first bit (D0) is presented on the DATA pin. The next three bits are shifted out by following rising edges of CLK (see Figure 4).

# **FUNCTION MODE (M2 - M0)**

These three bits (M2 - M0) determine the function mode shown in Table 1.

**Table 1. Function Mode Truth Table**

| M2 | M1 | MO | Function Mode        |  |  |

|----|----|----|----------------------|--|--|

| 0  | 0  | 0  | DTMF Receive         |  |  |

| 0  | 0  | 1  | DTMF Transmit        |  |  |

| 0  | 1  | 0  | Single Tone Transmit |  |  |

| 0  | 1  | 1  | Power Down 1         |  |  |

| 1  | 0  | 0  | Power Down 2         |  |  |

| 1  | 0  | 1  | Analog Loopback      |  |  |

#### DTMF Receive Mode (M2 - M0 = 0, 0, 0)

The DTMF receiver is enabled. The transmitter is disabled.

# DTMF Transmit Mode (M2 – M0 = 0, 0, 1)

The DTMF tone generator is enabled. The receiver is disabled.

#### Single Tone Mode (M2 - M0 = 0, 1, 0)

The transmitter generates one of the eight frequencies of DTMF tones. The receiver is disabled.

# Power Down Mode 1 (M2 – M0 = 0, 1, 1)

All internal circuits except for the oscillator and Serial Interface are disabled, so all output pins except for the X1 are in high–impedance state. The device current is decreased to  $500 \,\mu\text{A}$  (max).

# Power Down Mode 2 (M2 – M0 = 1, 0, 0)

All internal circuits except for the Serial Interface are disabled, so all output pins are in high-impedance state. The device current is decreased to 1  $\mu$ A (max). The default condition that occurs after a power reset is Power Down Mode 2.

# Analog Loopback Mode (M2 - M0 = 1, 0, 1)

The transmitter output is internally connected to the receiver input.

# TRANSMIT SQUELCH (SQ)

When the SQ bit is 1, the DTMF and single tone transmission are disabled (squelch is selected). However, the transmit squelch does not affect the external signal input from DSI.

# DTMF TONE DETECT/REJECT TIME (CD1, CD0)

The CD1 and CD0 bits determine DTMF tones detect time  $(t_{On})$  and release time  $(t_{Off})$  of the  $\overline{DV}$  pin, as shown in Table 2. The timing diagram is shown in Figure 2.

**Table 2. DTMF Detect Time Truth Table**

| CD1 | CD0 | t <sub>on</sub> (ms) t <sub>off</sub> (ms) |       |

|-----|-----|--------------------------------------------|-------|

| 0   | 0   | Rese                                       | erved |

| 0   | 1   | 20                                         | 20    |

| 1   | 0   | 30                                         | 30    |

| 1   | 1   | 40                                         | 20    |

CONTROL REGISTER (R/W = "L")

FUNCTION MODE : 3 BITS M2 M1 M0

TRANSMIT SQUELCH : 1 BIT SQ

DTMF DETECT TIME : 2 BITS | CD1 | CD0

TRANSMIT ATTENUATOR/AGC GAIN : 4 BITS A3 A2 A1 A0

TRANSMIT FREQUENCY: 4 BITS T3 T2 T1 T0

STATUS REGISTER ( $R/\overline{W} = "H"$ )

RECEIVED TONE FREQUENCY : 4 BITS D3 D2 D1 D0

# TRANSMIT ATTENUATOR/AGC GAIN (A3 - A0)

The A3 – A0 bits determine the analog transmit level of DTMF tones. The transmit attenuator range is controlled from 0 to 15 dB in 1 dB steps as shown in Table 3. However, this attenuator does not affect the external signal source from DSI. These four bits also determine the AGC amplifier gain in DTMF receive mode. In normal operation, "automatic" may be selected so that the receiver's gain is automatically adjusted, corresponding to the input signal level.

# TRANSMIT TONE FREQUENCY (T3 - T0)

The T3-T0 bits determine DTMF tone frequencies transmitted from TxA1 and TxA2 in DTMF transmit and analog loopback mode, and determine the single tone frequency in single tone mode. Tone frequency assignments for the T3-T0 bits are shown in Table 4.

# **RECEIVED TONE FREQUENCY (D3 - D0)**

The D3 – D0 bits provide hexadecimal codes corresponding to detected DTMF tones. Tone frequency assignments for the D3 – D0 bits are shown in Table 4.

Table 3. Transmit Attenuator/AGC Gain Set Truth Table

| А3 | A2 | A1 | A0 | Tx Attenuation (dB) | Rx AGC Gain (dB) |

|----|----|----|----|---------------------|------------------|

| 0  | 0  | 0  | 0  | 0                   | - 5.0            |

| 0  | 0  | 0  | 1  | 1                   | <b>- 2.5</b>     |

| 0  | 0  | 1  | 0  | 2                   | 0.0              |

| 0  | 0  | 1  | 1  | 3                   | 2.5              |

| 0  | 1  | 0  | 0  | 4                   | 5.0              |

| 0  | 1  | 0  | 1  | 5                   | 7.5              |

| 0  | 1  | 1  | 0  | 6                   | 10.0             |

| 0  | 1  | 1  | 1  | 7                   | 12.5             |

| 1  | 0  | 0  | 0  | 8                   | 15.0             |

| 1  | 0  | 0  | 1  | 9                   | 17.5             |

| 1  | 0  | 1  | 0  | 10                  | 20.0             |

| 1  | 0  | 1  | 1  | 11                  | Clamp            |

| 1  | 1  | 0  | 0  | 12                  | Automatic        |

| 1  | 1  | 0  | 1  | 13                  | _                |

| 1  | 1  | 1  | 0  | 14                  | _                |

| 1  | 1  | 1  | 1  | 15                  | _                |

**Table 4. Tone Frequency Truth Table**

|       |       |       |       | Tone Frequency (Hz) |                           |                        |                     |  |

|-------|-------|-------|-------|---------------------|---------------------------|------------------------|---------------------|--|

|       |       |       |       | DTMF                | DTMF Tx/Rx Mode Frequency |                        |                     |  |

| T3/D3 | T2/D2 | T1/D1 | T0/D0 | High Group          | Low Group                 | Keyboard<br>Equivalent | Single Tone<br>Mode |  |

| 0     | 0     | 0     | 1     | 697                 | 1209                      | 1                      | 697                 |  |

| 0     | 0     | 1     | 0     | 697                 | 1336                      | 2                      | 697                 |  |

| 0     | 0     | 1     | 1     | 697                 | 1477                      | 3                      | 697                 |  |

| 0     | 1     | 0     | 0     | 770                 | 1209                      | 4                      | 770                 |  |

| 0     | 1     | 0     | 1     | 770                 | 1336                      | 5                      | 770                 |  |

| 0     | 1     | 1     | 0     | 770                 | 1477                      | 6                      | 770                 |  |

| 0     | 1     | 1     | 1     | 852                 | 1209                      | 7                      | 852                 |  |

| 1     | 0     | 0     | 0     | 852                 | 1336                      | 8                      | 1336                |  |

| 1     | 0     | 0     | 1     | 852                 | 1477                      | 9                      | 1477                |  |

| 1     | 0     | 1     | 0     | 941                 | 1336                      | 0                      | 1336                |  |

| 1     | 0     | 1     | 1     | 941                 | 1209                      | *                      | 1209                |  |

| 1     | 1     | 0     | 0     | 941                 | 1477                      | #                      | 1477                |  |

| 1     | 1     | 0     | 1     | 697                 | 1633                      | А                      | 1633                |  |

| 1     | 1     | 1     | 0     | 770                 | 1633                      | В                      | 1633                |  |

| 1     | 1     | 1     | 1     | 852                 | 1633                      | С                      | 1633                |  |

| 0     | 0     | 0     | 0     | 941                 | 1633                      | D                      | 941                 |  |

# **APPLICATION CIRCUIT**

<sup>\*</sup> The external devices (i.e., modem) may be connected on these pins, using the built-in line interface circuit.

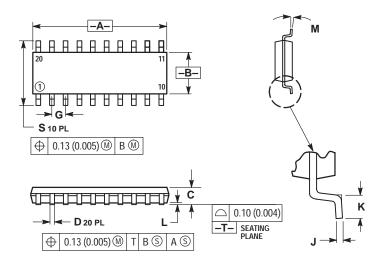

#### PACKAGE DIMENSIONS

#### **F SUFFIX** SOG (SMALL OUTLINE GULL-WING) PACKAGE CASE 751J-02

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.12 (0.006) PER SIDE.

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | METERS | INC       | HES   |  |

|-----|--------|--------|-----------|-------|--|

| DIM | MIN    | MAX    | MIN       | MAX   |  |

| Α   | 12.55  | 12.80  | 0.494     | 0.504 |  |

| В   | 5.10   | 5.40   | 0.201     | 0.213 |  |

| С   |        | 2.00   |           | 0.079 |  |

| D   | 0.35   | 0.45   | 0.014     | 0.018 |  |

| G   | 1.27   | BSC    | 0.050 BSC |       |  |

| J   | 0.18   | 0.23   | 0.007     | 0.009 |  |

| K   | 0.55   | 0.85   | 0.022     | 0.033 |  |

| L   | 0.05   | 0.20   | 0.002     | 0.008 |  |

| M   | 0 °    | 7 °    | 0 °       | 7 °   |  |

| S   | 7.40   | 8.20   | 0.291     | 0.323 |  |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and 祸 are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution: P.O. Box 5405, Denver, Colorado, 80217. 1-303-675-2140 or 1-800-441-2447

**TECHNICAL INFORMATION CENTER: 1-800-521-6274**

HOME PAGE: http://motorola.com/semiconductors/

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu. Minato-ku, Tokyo 106-8573 Japan. 81-3-3440-3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tao Po, N.T., Hong Kong. 852-26668334

MC145740/D