# MC145149

# **Dual PLL Frequency Synthesizer** Interfaces with Dual–Modulus Prescalers

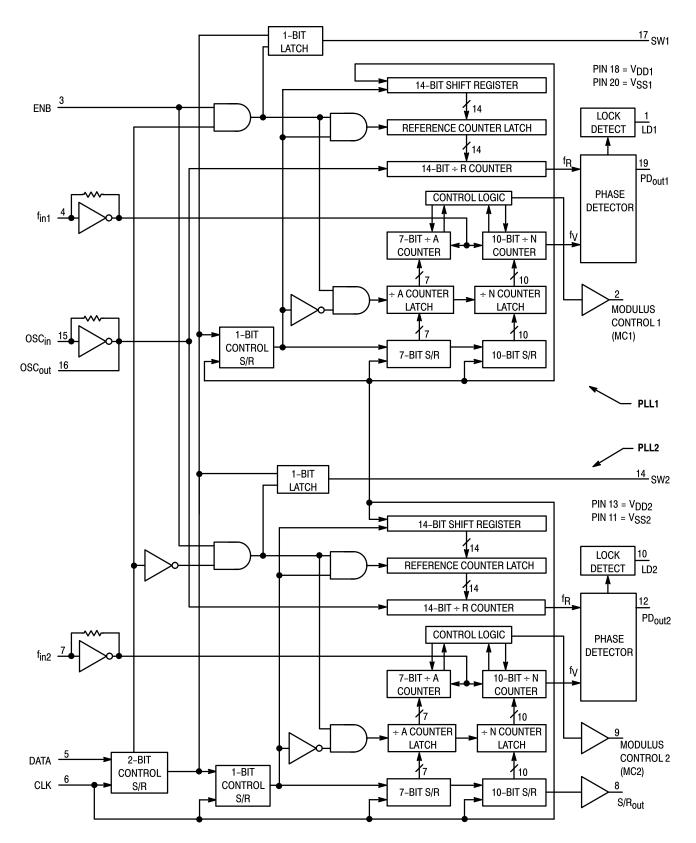

The MC145149 contains two PLL Frequency Synthesizers which share a common serial data port and common reference oscillator. The device contains two 14-stage R counters, two 10-stage N counters, and two 7-stage A counters. All six counters are fully programmable through a serial port. The divide ratios are latched into the appropriate counter latch according to the last data bits (control bits) entered.

When combined with external low-pass filters and voltage controlled oscillators (VCOs), the MC145149 can provide all the remaining functions for two PLL frequency synthesizers operating up to the device's frequency limit. For higher VCO frequency operation, a down mixer or dual-modulus prescaler can be used between the VCO and the synthesizer IC.

- Low Power Consumption Through Use of CMOS Technology

- Wide Operating Voltage Range: 3 to 9 V

- Operating Temperature Range: 40 to + 85°C

- ÷ R Range = 3 to 16,383

- $\div$  N Range = 3 to 1023

- $\div$  A Range = 0 to 127

- Two "Linearized" Three-State Digital Phase Detectors with No Dead Zone

- Two Lock Detect Signals (LD1 and LD2)

- Two Open–Drain Port Expander Outputs (SW1 and SW2)

- Compatible with the Serial Peripheral Interface (SPI) on CMOS MCUs

MC145149DW SOG Package

| PIN ASSIGNMENT       |    |        |                   |  |  |

|----------------------|----|--------|-------------------|--|--|

| LD1 [                | 1● | 20 🛛 V | SS1               |  |  |

| мс1 [                | 2  | 19 🛛 P | D <sub>out1</sub> |  |  |

| енв [                | 3  | 18 🛛 V | DD1               |  |  |

| fin1 🛛               | 4  | 17 🛛 S | W1                |  |  |

| DATA [               | 5  | 16 🛛 0 | SCout             |  |  |

| СГК [                | 6  | 15 🛛 0 | osc <sub>in</sub> |  |  |

| f <sub>in2</sub> [   | 7  | 14 🛛 S | W2                |  |  |

| S/R <sub>out</sub> [ | 8  | 13 🛛 V | DD2               |  |  |

| мс2 [                | 9  | 12 🛛 P | D <sub>out2</sub> |  |  |

| LD2 [                | 10 | 11 🛛 V | SS2               |  |  |

| -                    |    |        |                   |  |  |

#### MAXIMUM RATINGS\* (Voltages Referenced to VSS)

| Symbol                             | Rating                                                    | Value                          | Unit |

|------------------------------------|-----------------------------------------------------------|--------------------------------|------|

| V <sub>DD</sub>                    | DC Supply Voltage                                         | – 0.5 to + 10                  | V    |

| V <sub>in</sub> , V <sub>out</sub> | Input or Output Voltage (DC or Transient) except SW1, SW2 | – 0.5 to V <sub>DD</sub> + 0.5 | V    |

| Vout                               | Output Voltage (DC or Transient) — SW1,<br>SW2            | – 0.5 to 15                    | V    |

| l <sub>in</sub> , l <sub>out</sub> | Input or Output Current (DC or Transient),<br>per Pin     | ± 10                           | mA   |

| I <sub>DD</sub> , I <sub>SS</sub>  | Supply Current, $V_{DD}$ or $V_{SS}$ Pins                 | ± 30                           | mA   |

| PD                                 | Power Dissipation, per Package†                           | 500                            | mW   |

| T <sub>stg</sub>                   | Storage Temperature                                       | – 65 to + 150                  | °C   |

| ΤL                                 | Lead Temperature (8–Second Soldering)                     | 260                            | °C   |

This device contains circuitry to protect against damage due to high static voltages or electric fields, however, it is advised that normal precautions be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation, it is recommended that  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \leq (V_{in} \mbox{ or } V_{out}) \leq V_{DD}$  except SW1 and SW2 which may range up to 15 V.

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either  $V_{SS}$  or  $V_{DD}$ ). Unused outputs should be left floating.

\* Maximum Ratings are those values beyond which damage to the device may occur.

+Power Dissipation Temperature Derating:

Plastic DIP: - 12 mW/°C from 65 to 85°C

SOG Package: – 7 mW/°C from 65 to 85°C

ELECTRICAL CHARACTERISTICS (Voltages Referenced to VSS)

|                 |                                                                                                                                                                                                  |         | VDD         | - 4                        | 0°C                  | 25                         | °C                   | 85                         | °C                   |      |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|----------------------------|----------------------|----------------------------|----------------------|----------------------------|----------------------|------|

| Symbol          | Characteristic                                                                                                                                                                                   |         | V V         | Min                        | Max                  | Min                        | Max                  | Min                        | Max                  | Unit |

| V <sub>DD</sub> | Power Supply Voltage Range                                                                                                                                                                       |         | —           | 3                          | 9                    | 3                          | 9                    | 3                          | 9                    | V    |

| VOL             | Output Voltage<br>V <sub>in</sub> = 0 V or V <sub>DD</sub><br>I <sub>out</sub> = 0 μA                                                                                                            | 0 Level | 3<br>5<br>9 |                            | 0.05<br>0.05<br>0.05 |                            | 0.05<br>0.05<br>0.05 |                            | 0.05<br>0.05<br>0.05 | V    |

| VOH             |                                                                                                                                                                                                  | 1 Level | 3<br>5<br>9 | 2.95<br>4.95<br>8.95       |                      | 2.95<br>4.95<br>8.95       |                      | 2.95<br>4.95<br>8.95       |                      |      |

| VIL             | Input Voltage<br>V <sub>out</sub> = 0.5 V or V <sub>DD</sub> – 0.5 V<br>(All Outputs Except OSC <sub>out</sub> )                                                                                 | 0 Level | 3<br>5<br>9 |                            | 0.9<br>1.5<br>2.7    |                            | 0.9<br>1.5<br>2.7    |                            | 0.9<br>1.5<br>2.7    | V    |

| VIH             |                                                                                                                                                                                                  | 1 Level | 3<br>5<br>9 | 2.1<br>3.5<br>6.3          |                      | 2.1<br>3.5<br>6.3          | <br> <br>            | 2.1<br>3.5<br>6.3          | <br> <br>            |      |

| ЮН              | $\begin{array}{l} \text{Output Current} &\text{MC1, MC2} \\ \text{V}_{\text{out}} = 2.7 \text{ V} \\ \text{V}_{\text{out}} = 4.6 \text{ V} \\ \text{V}_{\text{out}} = 8.5 \text{ V} \end{array}$ | Source  | 3<br>5<br>9 | - 0.60<br>- 0.90<br>- 1.50 |                      | - 0.50<br>- 0.75<br>- 1.25 |                      | - 0.30<br>- 0.50<br>- 0.80 |                      | mA   |

| IOL             | V <sub>out</sub> = 0.3 V<br>V <sub>out</sub> = 0.4 V<br>V <sub>out</sub> = 0.5 V                                                                                                                 | Sink    | 3<br>5<br>9 | 1.30<br>1.90<br>3.80       |                      | 1.10<br>1.70<br>3.30       |                      | 0.66<br>1.08<br>2.10       |                      |      |

| IOL             | $\begin{array}{l} \text{Output Current} &\text{SW1, SW2} \\ \text{V}_{\text{out}} = 0.3 \text{ V} \\ \text{V}_{\text{out}} = 0.4 \text{ V} \\ \text{V}_{\text{out}} = 0.5 \text{ V} \end{array}$ | Sink    | 3<br>5<br>9 | 0.80<br>1.50<br>3.50       |                      | 0.48<br>0.90<br>2.10       |                      | 0.24<br>0.45<br>1.50       |                      | mA   |

| ЮН              | Output Current — Other Outputs<br>$V_{out} = 2.7 V$<br>$V_{out} = 4.6 V$<br>$V_{out} = 8.5 V$                                                                                                    | Source  | 3<br>5<br>9 | - 0.44<br>- 0.64<br>- 1.30 |                      | - 0.35<br>- 0.51<br>- 1.00 |                      | - 0.22<br>- 0.36<br>- 0.70 |                      | mA   |

| IOL             | V <sub>out</sub> = 0.3 V<br>V <sub>out</sub> = 0.4 V<br>V <sub>out</sub> = 0.5 V                                                                                                                 | Sink    | 3<br>5<br>9 | 0.44<br>0.64<br>1.30       |                      | 0.35<br>0.51<br>1.00       |                      | 0.22<br>0.36<br>0.70       |                      |      |

| l <sub>in</sub> | Input Current — DATA, CLK, ENB                                                                                                                                                                   |         | 9           | _                          | ± 0.3                |                            | ± 0.1                | _                          | ± 1.0                | μΑ   |

| l <sub>in</sub> | Input Current — f <sub>in</sub> , OSC <sub>in</sub>                                                                                                                                              |         | 9           | —                          | ± 50                 | —                          | ± 25                 | —                          | ± 22                 | μA   |

(continued)

# ELECTRICAL CHARACTERISTICS (continued)

|                 |                                                                                          | V <sub>DD</sub> | - 40 | 0°C                 | 25  | °C                  | 85  | °C                   |      |

|-----------------|------------------------------------------------------------------------------------------|-----------------|------|---------------------|-----|---------------------|-----|----------------------|------|

| Symbol          | Characteristic                                                                           | v               | Min  | Max                 | Min | Мах                 | Min | Max                  | Unit |

| C <sub>in</sub> | Input Capacitance                                                                        | —               | _    | 10                  |     | 10                  |     | 10                   | pF   |

| Cout            | Three-State Output Capacitance — PD <sub>out</sub>                                       | —               | _    | 10                  |     | 10                  | -   | 10                   | pF   |

| IDD             | Quiescent Current<br>V <sub>in</sub> = 0 V or V <sub>DD</sub><br>I <sub>out</sub> = 0 μA | 3<br>5<br>9     |      | 800<br>1200<br>1600 |     | 800<br>1200<br>1600 | _   | 1600<br>2400<br>3200 | μA   |

| loz             | Three–State Leakage Current — PD <sub>out</sub><br>V <sub>out</sub> = 0 V or 9 V         | 9               | _    | ±0.3                |     | ± 0.1               |     | ± 3.0                | μA   |

| loz             | Off–State Leakage Current — SW1, SW2<br>V <sub>out</sub> = 9 V                           | 9               | _    | 0.3                 |     | 0.1                 |     | 3.0                  | μA   |

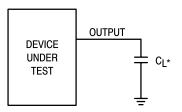

# SWITCHING CHARACTERISTICS (T<sub>A</sub> = 25°C, C<sub>L</sub> = 50 pF)

| Symbol                                            | Characteristic                            | Figure<br>No. | V <sub>DD</sub><br>V | Min            | Мах             | Unit |

|---------------------------------------------------|-------------------------------------------|---------------|----------------------|----------------|-----------------|------|

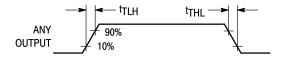

| <sup>t</sup> TLH                                  | Output Rise Time, MC1 and MC2             | 1, 6          | 3<br>5<br>9          |                | 115<br>60<br>40 | ns   |

| <sup>t</sup> THL                                  | Output Fall Time, MC1 and MC2             | 1, 6          | 3<br>5<br>9          |                | 60<br>34<br>30  | ns   |

| <sup>t</sup> TLH,<br><sup>t</sup> THL             | Output Rise and Fall Time, LD and S/Rout  | 1, 6          | 3<br>5<br>9          |                | 140<br>80<br>60 | ns   |

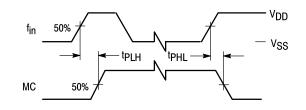

| <sup>t</sup> PLH <sup>,</sup><br><sup>t</sup> PHL | Propagation Delay Time, fin to MC1 or MC2 | 2, 6          | 3<br>5<br>9          |                | 125<br>80<br>50 | ns   |

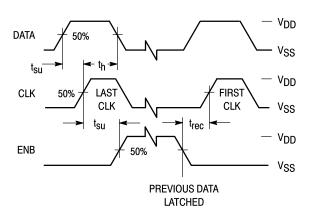

| t <sub>su</sub>                                   | Setup Time, DATA to CLK                   | 3             | 3<br>5<br>9          | 30<br>20<br>18 | <br><br>        | ns   |

| t <sub>su</sub>                                   | Setup Time, CLK to ENB                    | 3             | 3<br>5<br>9          | 70<br>32<br>25 | <br><br>        | ns   |

| th                                                | Hold Time, CLK to DATA                    | 3             | 3<br>5<br>9          | 12<br>12<br>15 |                 | ns   |

| trec                                              | Recovery Time, ENB to CLK                 | 3             | 3<br>5<br>9          | 5<br>10<br>20  |                 | ns   |

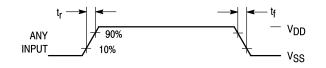

| t <sub>r</sub> , t <sub>f</sub>                   | Input Rise and Fall Times, Any Input      | 4             | 3<br>5<br>9          |                | 5<br>2<br>0.5   | μs   |

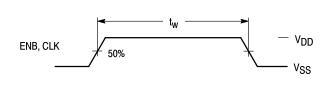

| t <sub>W</sub>                                    | Input Pulse Width, ENB and CLK            | 5             | 3<br>5<br>9          | 40<br>35<br>25 |                 | ns   |

# **FREQUENCY CHARACTERISTICS** (Voltages Referenced to $V_{SS}$ , $C_L = 50$ pF, Input $t_r = t_f = 10$ ns unless otherwise indicated)

|        |                                                           |                                                                                                                                                      | V <sub>DD</sub> | - 4 | 0°C           | 25  | °C            | 85  | °C            |      |

|--------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|---------------|-----|---------------|-----|---------------|------|

| Symbol | Parameter                                                 | Test Conditions                                                                                                                                      | V               | Min | Max           | Min | Max           | Min | Max           | Unit |

| fi     | Input Frequency<br>(f <sub>in</sub> , OSC <sub>in</sub> ) | $\label{eq:rescaled} \begin{array}{l} R \geq 8, \ A \geq 0, \ N \geq 8 \\ V_{in} = 500 \ mV \ p-p \\ ac \ coupled \ sine \ wave \end{array}$         | 3<br>5<br>9     |     | 6<br>15<br>15 |     | 6<br>15<br>15 |     | 6<br>15<br>15 | MHz  |

|        |                                                           | $\label{eq:rescaled} \begin{array}{l} R \geq 8, \ A \geq 0, \ N \geq 8 \\ V_{in} = V_{DD} \ to \ V_{SS} \\ dc \ coupled \ square \ wave \end{array}$ | 3<br>5<br>9     |     | 6<br>15<br>15 |     | 6<br>15<br>15 |     | 6<br>15<br>15 | MHz  |

# SWITCHING WAVEFORMS

Figure 1.

Figure 5.

Figure 2.

Figure 4.

\* Includes all probe and fixture capacitance.

Figure 6.

#### **INPUT PINS**

#### OSCin, OSCout Reference Oscillator Input/Output (Pins 15, 16)

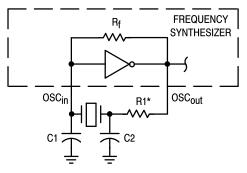

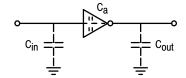

These pins form a reference oscillator when connected to terminals of an external parallel–resonant crystal. Frequency–setting capacitors of appropriate value must be connected from OSC<sub>in</sub> and OSC<sub>out</sub> to ground.

$OSC_{in}$  may also serve as input for an externally–generated reference signal. The signal is typically ac coupled to  $OSC_{in}$ , but for signals with CMOS logic levels, dc coupling may be used. When used with an external reference,  $OSC_{out}$  should be left open.

#### <sup>f</sup>in1, <sup>f</sup>in2 Frequency Inputs (Pins 4, 7)

Input frequency from an external VCO output. Each risingedge signal on  $f_{in1}$  decrements the N counter, and when appropriate, the A counter of PLL 1. Similarly,  $f_{in2}$  decrements the counters of PLL 2.

These inputs have inverters biased on the linear region which allows ac coupling for signals as low as 500 mV p–p. With square wave signals which swing from V<sub>SS</sub> to V<sub>DD</sub>, dc coupling may be used.

# DATA, CLK

# Data, Clock Inputs (Pins 5, 6)

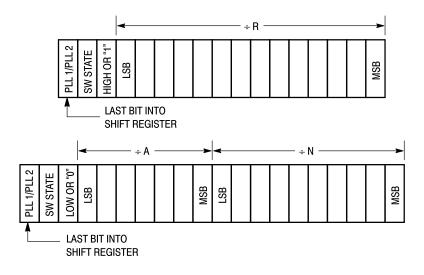

Shift register data and clock inputs. Each low-to-high transition on the clock pin shifts one bit of data into the onchip shift registers. Refer to Figure 7 for the following discussion.

The last bit entered is a steering bit that determines which set of latches are activated. A logic high selects the latches for PLL 1. A logic low selects PLL 2.

The second-to-last bit controls the appropriate port expander output, SW1 or SW2. A logic low forces the output low. A logic high forces the output to the high-impedance state.

The third–to–last bit determines which storage latch is activated. A logic low selects the  $\div$  A and  $\div$  N counter latches. A logic high selects the reference counter latch.

When writing to either set of  $\div$  A and  $\div$  N counter latches, 20 clock cycles are typically used. However, if a byte– oriented MCU is utilized, 24 clock cycles may be used with the first 4 bits being "Don't Care."

When writing to either reference counter latch, 17 clock cycles are typically used. However, if a byte–oriented MCU is utilized, 24 clock cycles may be used with the first 7 bits being "Don't Care".

# ENB

# Latch Enable Input (Pin 3)

A positive pulse on this input transfers data from the shift registers to the selected latches, as determined by the control and steering data bits. A logic low level on this pin allows the user to shift data into the shift registers without affecting the data in the latches or counters. Enable is normally held low and is pulsed high to transfer data into the latches.

### **OUTPUT PINS**

# PDout1, PDout2

#### Single–Ended Phase Detector Outputs (Pins 19, 12)

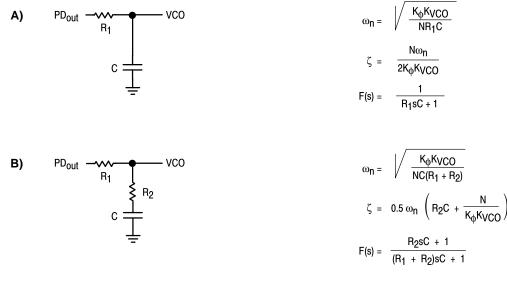

Each single–ended (three–state) phase detector output produces a loop error signal that is used with a loop filter to control a VCO (see Figure 8).

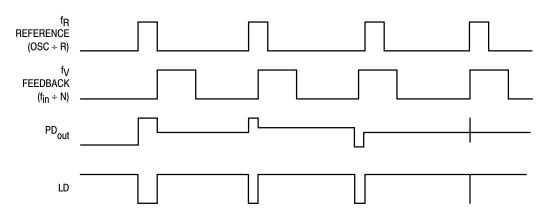

Frequency  $f_V > f_R$  or  $f_V$  Leading: Negative Pulses

Frequency  $f_V < f_R$  or  $f_V$  Lagging: Positive Pulses

Frequency  $f_V = f_R$  and Phase Coincidence: High–Impedance State

# S/Rout

### Shift Register Output (Pin 8)

This output can be connected to an external shift register to provide band switching or control information. S/R<sub>out</sub> may also be used to check the counter programming bit stream.

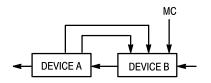

#### MC1, MC2

#### Modulus Control Outputs (Pins 2, 9)

Each output generates a signal by the on-chip control logic circuitry for controlling an external dual-modulus prescaler. The modulus control level is low at the beginning of a count cycle and remains low until the + A counter has counted down from its programmed value. At this time, modulus control goes high and remains high until the ÷ N counter has counted the rest of the way down from its programmed value (N-A additional counts since both ÷ N and + A are counting down during the first portion of the cycle). Modulus control is then set back low, the counters are preset to their respective programmed values, and the above sequence is repeated. This provides for a total programmable divide value  $(N_T) = N \bullet P + A$  where P and P + 1 represent the dual-modulus prescaler divide values respectively for high and low modulus control levels, N the number programmed into the + N counter, and A the number programmed into the ÷ A counter.

Note that when a prescaler is needed, the dual-modulus version offers a distinct advantage. The dual-modulus prescaler allows a higher reference frequency at the phase detector input, increasing system performance capability, and simplifying the loop filter design.

# LD1, LD2

# Lock Detect Signals (Pins 1, 10)

Each output is essentially at a high logic level when the corresponding loop is locked ( $f_R$  and  $f_V$  of the same phase and frequency). Each output pulses low when the corresponding loop is out of lock (see Figure 8).

# SW1, SW2

# Latched Open–Drain Switch Outputs (Pins 17, 14)

The state of each output is controlled by the "SW STATE" bit shown in Figure 7. If the bit is a logic high, the corresponding SW output assumes the high–impedance state. If the bit is low, the SW output goes low.

To control output SW1, steering bit PLL 1/PLL 2 shown in Figure 7 must be high. To control SW2, bit PLL 1/PLL 2 must be low.

These outputs have an output voltage range of  $\mathsf{V}_{\text{SS}}$  to 15 V.

#### V<sub>DD1</sub>, V<sub>DD2</sub> Positive Power Supply (Pins 18, 13)

The most positive power supply potentials. Both of these pins are connected to the substrate of the chip. Therefore, both must be tied to the same voltage potential. This potential may range from 3 to 9 V with respect to the  $V_{SS}$  pins.

For optimum performance, V<sub>DD1</sub> should be bypassed to V<sub>SS1</sub> and V<sub>DD2</sub> bypassed to V<sub>SS2</sub>. That is, two separate bypass capacitors should be utilized.

# VSS1, VSS2

# Negative Power Supply (Pins 20, 11)

The most negative power supply potentials. Both of these pins should be tied to ground.

# Figure 7. Bit Stream Formats

NOTE: The PD output state is equal to either V<sub>DD</sub> or V<sub>SS</sub> when active. When not active, the output is high impedance and the voltage at that pin is determined by the low–pass filter capacitor.

# Figure 8. Phase Detector/Lock Detector Output Waveforms

#### **DEFINITIONS:**

N = Total Division Ratio in Feedback Loop  $K_{\phi}$  (Phase Detector Gain) =  $V_{DD}/4\pi$  for PD<sub>out</sub>

$$K_{VCO}$$

(VCO Gain) =  $\frac{2\pi\Delta f_{VCO}}{\Delta V_{VCO}}$

for a typical design  $\omega_{\text{n}}$  (Natural Frequency)  $\approx \frac{2\pi fr}{10}$  (at phase detector input).

Damping Factor:  $\zeta \approx 1$

RECOMMENDED READING:

Gardner, Floyd M., Phaselock Techniques (second edition). New York, Wiley-Interscience, 1979.

Manassewitsch, Vadim, Frequency Synthesizers: Theory and Design (second edition). New York, Wiley-Interscience, 1980.

Blanchard, Alain, Phase–Locked Loops: Application to Coherent Receiver Design. New York, Wiley–Interscience, 1976.

Egan, William F., Frequency Synthesis by Phase Lock. New York, Wiley-Interscience, 1981.

Rohde, Ulrich L., Digital PLL Frequency Synthesizers Theory and Design. Englewood Cliffs, NJ, Prentice–Hall, 1983.

Berlin, Howard M., Design of Phase-Locked Loop Circuits, with Experiments. Indianapolis, Howard W. Sams and Co., 1978. Kinley, Harold, The PLL Synthesizer Cookbook. Blue Ridge Summit, PA, Tab Books, 1980.

AN535, Phase–Locked Loop Design Fundamentals, Motorola Semiconductor Products, Inc., 1970.

AR254, Phase–Locked Loop Design Articles, Motorola Semiconductor Products, Inc., Reprinted with permission from Electronic Design, 1987.

# Figure 9. Phase–Locked Loop Low–Pass Filter Design

# DESIGN CONSIDERATIONS

# **CRYSTAL OSCILLATOR CONSIDERATIONS**

The following options may be considered to provide a reference frequency to Motorola's CMOS frequency synthesizers.

#### Use of a Hybrid Crystal Oscillator

Commercially available temperature-compensate crystal oscillators (TCXOs) or crystal-controlled data clock oscillators provide very stable reference frequencies. An oscillator capable of sinking and sourcing 50  $\mu$ A at CMOS logic levels may be direct or dc coupled to OSCin. In general, the highest frequency capability is obtained utilizing a direct-coupled square wave having a rail-to-rail (VDD to VSS) voltage swing. If the oscillator does not have CMOS logic levels on the outputs, capacitive or ac coupling to OSCin may be used. OSCout, an unbuffered output, should be left floating.

For additional information about TCXOs and data clock oscillators, please consult the latest version of the eem Electronic Engineers Master Catalog, the Gold Book, or similar publications.

# **Design an Off–Chip Reference**

The user may design an off-chip crystal oscillator using ICs specifically developed for crystal oscillator applications, such as the MC12061 MECL device. The reference signal from the MECL device is ac coupled to OSCin. For large amplitude signals (standard CMOS logic levels), dc coupling is used. OSC<sub>OUt</sub>, an unbuffered output, should be left floating. In general, the highest frequency capability is obtained with a direct-coupled square wave having rail-to-rail voltage swing.

#### Use of the On-Chip Oscillator Circuitry

The on-chip amplifier (a digital inverter) along with an appropriate crystal may be used to provide a reference source frequency. A fundamental mode crystal, parallel resonant at the desired operating frequency, should be connected as shown in Figure 10.

For V<sub>DD</sub> = 5.0 V, the crystal should be specified for a loading capacitance, C<sub>L</sub>, which does not exceed 32 pF for frequencies to approximately 8 MHz, 20 pF for frequencies in the area of 8 to 15 MHz, and 10 pF for higher frequencies. These are guidelines that provide a reasonable compromise between IC capacitance, drive capability, swamping variations in stray and IC input/output capacitance, and realistic C<sub>L</sub> values. The shunt load capacitance, C<sub>L</sub>, presented across the crystal can be estimated to be:

$$C_{L} = \frac{C_{in}C_{out}}{C_{in} + C_{out}} + C_{a} + C_{O} + \frac{C1 \cdot C2}{C1 + C2}$$

where

C<sub>in</sub> = 5 pF (see Figure 11)

Cout = 6 pF (see Figure 11)

$C_a = 1 \text{ pF}$  (see Figure 11)

$C_{O}$ = the crystal's holder capacitance (see Figure 12) C1 and C2 = external capacitors (see Figure 10)

The oscillator can be "trimmed" on–frequency by making a portion or all of C1 variable. The crystal and associated components must be located as close as possible to the OSC<sub>in</sub> and OSC<sub>out</sub> pins to minimize distortion, stray capacitance, stray inductance, and startup stabilization time. In some cases, stray capacitance should be added to the value for C<sub>in</sub> and C<sub>out</sub>.

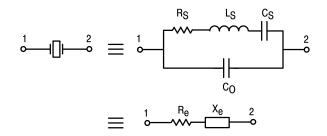

Power is dissipated in the effective series resistance of the crystal,  $R_e$ , in Figure 12. The drive level specified by the crystal manufacturer is the maximum stress that a crystal can withstand without damaging or excessive shift in frequency. R1 in Figure 10 limits the drive level. The use of R1 may not be necessary in some cases (i.e., R1 = 0  $\Omega$ ).

To verify that the maximum dc supply voltage does not overdrive the crystal, monitor the output frequency as a function of voltage at OSC<sub>out</sub>. (Care should be taken to minimize loading.) The frequency should increase very slightly as the dc supply voltage is increased. An overdriven crystal will decrease in frequency or become unstable with an increase in supply voltage. The operating supply voltage must be reduced or R1 must be increased in value if the overdriven condition exists. The user should note that the oscillator start–up time is proportional to the value of R1.

Through the process of supplying crystals for use with CMOS inverters, many crystal manufacturers have developed expertise in CMOS oscillator design with crystals. Discussions with such manufacturers can prove very helpful (see Table 1).

\* May be deleted in certain cases. See text.

Figure 10. Pierce Crystal Oscillator Circuit

Figure 11. Parasitic Capacitances of the Amplifier

NOTE: Values are supplied by crystal manufacturer (parallel resonant crystal).

#### Figure 12. Equivalent Crystal Networks

#### **RECOMMENDED READING**

Technical Note TN-24, Statek Corp.

Technical Note TN-7, Statek Corp.

E. Hafner, "The Piezoelectric Crystal Unit – Definitions and Method of Measurement", *Proc. IEEE*, Vol. 57, No. 2 Feb., 1969.

D. Kemper, L. Rosine, "Quartz Crystals for Frequency Control", *Electro–Technology*, June, 1969.

P. J. Ottowitz, "A Guide to Crystal Selection", *Electronic Design*, May, 1966.

Table 1. Partial List of Crystal Manufacturers

| Name                        | Address                               | Phone          |

|-----------------------------|---------------------------------------|----------------|

| United States Crystal Corp. | 3605 McCart Ave., Ft. Worth, TX 76110 | (817) 921–3013 |

| Crystek Crystal             | 2351 Crystal Dr., Ft. Myers, FL 33907 | (813) 936–2109 |

| Statek Corp.                | 512 N. Main St., Orange, CA 92668     | (714) 639–7810 |

NOTE: Motorola cannot recommend one supplier over another and in no way suggests that this is a complete listing of crystal manufacturers.

#### **DUAL-MODULUS PRESCALING**

#### **OVERVIEW**

The technique of dual-modulus prescaling is well established as a method of achieving high performance frequency synthesizer operation at high frequencies. Basically, the approach allows relatively low-frequency programmable counters to be used as high-frequency programmable counters with speed capability of several hundred MHz. This is possible without the sacrifice in system resolution and performance that results if a fixed (single-modulus) divider is used for the prescaler.

In dual–modulus prescaling, the lower speed counters must be uniquely configured. Special control logic is necessary to select the divide value P or P + 1 in the prescaler for the required amount of time (see modulus control definition). Motorola's dual–modulus frequency synthesizers contain this feature and can be used with a variety of dual–modulus prescalers to allow speed, complexity, and cost to be tailored to the system requirements. Prescalers having P, P + 1 divide values in the range of  $\div$  3/ $\div$  4 to  $\div$  128/ $\div$  129 can be controlled by most Motorola frequency synthesizers.

Several dual-modulus prescaler approaches suitable for use with the MC145149 are:

| MC12009  | ÷ 5/÷ 6              | 440 MHz |

|----------|----------------------|---------|

| MC12011  | ÷ 8/÷ 9              | 500 MHz |

| MC12013  | ÷ 10/÷ 11            | 500 MHz |

| MC12015  | ÷ 32/÷ 33            | 225 MHz |

| MC12016  | ÷ 40/÷ 41            | 225 MHz |

| MC12017  | ÷ 64/÷ 65            | 225 MHz |

| MC12018  | ÷ 128/÷ 129          | 520 MHz |

| MC12022A | ÷ 64/65 or ÷ 128/129 | 1.1 GHz |

| MC12032A | ÷ 64/65 or ÷ 128/129 | 2.0 GHz |

#### **DESIGN GUIDELINES**

The system total divide value,  $N_{total}\left(N_{T}\right)$  will be dictated by the application, i.e.,

$$NT = \frac{\text{frequency into the prescaler}}{\text{frequency into the phase detector}} = N \bullet P + A$$

N is the number programmed into the  $\div$  N counter, A is the number programmed into the  $\div$  A counter, P and P + 1 are the two selectable divide ratios available in the dual-modulus prescalers. To have a range of N<sub>T</sub> values in sequence, the  $\div$  A counter is programmed from 0 through P - 1 for a particular value N in the  $\div$  N counter. N is then incremented to N + 1 and the  $\div$  A is sequenced from 0 through P - 1 again.

There are minimum and maximum values that can be achieved for NT. These values are a function of P and the size of the  $\div$  N and  $\div$  A counters.

The constraint  $N \ge A$  always applies. If  $A_{max} = P - 1$ , then  $N_{min} \ge P - 1$ . Then  $N_{Tmin} = (P - 1) P + A$  or (P - 1) P since A is free to assume the value of 0.

#### $N_{Tmax} = N_{max} \bullet P + A_{max}$

To maximize system frequency capability, the dual-modulus prescaler output must go from low to high after each group of P or P + 1 input cycles. The prescaler should divide by P when its modulus control line is high and by P + 1 when its modulus control is low.

For the maximum frequency into the prescaler ( $f_{VCO}$  max), the value used for P must be large enough such that:

- f<sub>VCO</sub> max divided by P may not exceed the frequency capability of f<sub>in</sub> (input to the ÷ N and ÷ A counters).

- 2. The period of f<sub>VCO</sub> divided by P must be greater than the sum of the times:

- a. Propagation delay through the dual-modulus prescaler.

- b. Prescaler setup or release time relative to its modulus control signal.

- c. Propagation time from f<sub>in</sub> to the modulus control output for the frequency synthesizer device.

A sometimes useful simplification in the programming code can be achieved by choosing the values for P of 8, 16, 32, or 64. For these cases, the desired value of N<sub>T</sub> results when N<sub>T</sub> in binary is used as the program code to the  $\div$  N and  $\div$  A counters treated in the following manner:

- 1. Assume the  $\div$  A counter contains "a" bits where  $2^a \ge P$ .

- 2. Always program all higher order ÷ A counter bits above "a" to 0.

- 3. Assume the ÷ N counter and the ÷ A counter (with all the higher order bits above "a" ignored) combined into a single binary counter of n + a bits in length (n = number of divider stages in the ÷ N counter). The MSB of this "hypothetical" counter is to correspond to the MSB of ÷ N and the LSB is to correspond to the LSB of ÷ A. The system divide value, N<sub>T</sub>, now results when the value of N<sub>T</sub> in binary is used to program the "new" n + a bit counter.

By using the two devices, several dual-modulus values are achievable.

| DE1      | /ICE                         |                                |             |

|----------|------------------------------|--------------------------------|-------------|

|          | 3                            |                                |             |

| DEVICE A | MC12009                      | MC12011                        | MC12013     |

| MC10131  | ÷ 20/÷ 21                    | ÷ 32/÷ 33                      | ÷ 40/÷ 41   |

| MC10138  | ÷ 50/÷ 51                    | ÷ 80/÷ 81                      | ÷ 100/÷ 101 |

| MC10154  | ÷ 40/÷ 41<br>OR<br>÷ 80/÷ 81 | ÷ 64/÷ 65<br>OR<br>÷ 128/÷ 129 | ÷ 80/÷ 81   |

NOTE: MC12009, MC12011, and MC12013 are pin equivalent. MC12015, MC12016, and MC12017 are pin equivalent.

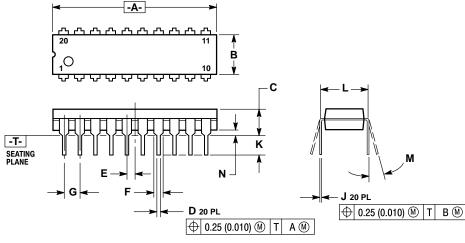

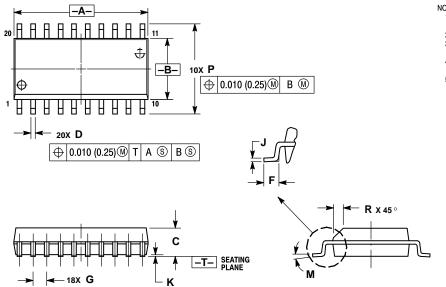

### PACKAGE DIMENSIONS

P SUFFIX PLASTIC DIP CASE 738-03

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: INCH. 2.

DIMENSION L TO CENTER OF LEAD WHEN FORMED PARALLEL. 3.

DIMENSION B DOES NOT INCLUDE MOLD 4.

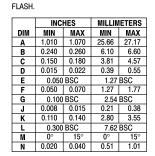

D SUFFIX SOG PACKAGE CASE 751D-04

NOTES: DIES:

DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.150

(0.006) PER SIDE. 5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN EXCESS OF D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS | INC       | HES   |  |

|-----|--------|--------|-----------|-------|--|

| DIM | MIN    | MAX    | MIN       | MAX   |  |

| Α   | 12.65  | 12.95  | 0.499     | 0.510 |  |

| В   | 7.40   | 7.60   | 0.292     | 0.299 |  |

| С   | 2.35   | 2.65   | 0.093     | 0.104 |  |

| D   | 0.35   | 0.49   | 0.014     | 0.019 |  |

| F   | 0.50   | 0.90   | 0.020     | 0.035 |  |

| G   | 1.27   | BSC    | 0.050 BSC |       |  |

| J   | 0.25   | 0.32   | 0.010     | 0.012 |  |

| Κ   | 0.10   | 0.25   | 0.004     | 0.009 |  |

| Μ   | 0 °    | 7 °    | 0 °       | 7°    |  |

| Р   | 10.05  | 10.55  | 0.395     | 0.415 |  |

| R   | 0.25   | 0.75   | 0.010     | 0.029 |  |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, Toshikatsu Otsuki, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–3521–8315

MFAX: RMFAX0@email.sps.mot.com - TOUCHTONE (602) 244–6609 INTERNET: http://Design-NET.com

0

HONG KONG: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298