###

### 300Msps, 12-Bit DAC with Complementary Voltage Outputs

### General Description

The MAX555 is an advanced, monolithic, 12-bit digitalto-analog converter (DAC) with complementary  $50\Omega$ outputs. Fabricated using an oxide-isolated bipolar process, the MAX555 is designed for signal-reconstruction applications at an output update rate of 300Msps. It incorporates an analog multiplying function with 10MHz useable input bandwidth. The voltage-output DAC uses precision laser trimming to achieve 12-bit accuracy with ±1/2LSB integral and differential linearity (±0.012% FS). Absolute gain error is a low 1% of full scale. Full-scale transitions occur in less than 0.5ns. Internal registers and a unique decoder reduce glitching and allow the MAX555 to achieve precise RF performance with over 73dBc of spurious-free dynamic range at 50Msps with four = 3.1MHz, or 62dBc at 300Msps with fOUT = 18.6MHz.

The MAX555 operates from a single -5.2V supply and dissipates 980mW (nominal). It comes in a 68-pin thermally enhanced PLCC package capable of accepting a heatsink.

#### \_Applications

Direct Digital Synthesis Arbitrary Waveform Generation HDTV/High-Resolution Graphics Instrumentation Communications Local Oscillators Automated Tester Applications

### \_\_\_\_\_Features

- **♦ 12-Bit Resolution**

- ♦ ±1/2LSB Integral and Differential Nonlinearity

- ♦ Capable of 300Msps Min Update Rate

- **♦** Complementary 50Ω Outputs

- **♦ Multiplying Reference Input**

- **♦ Low Glitch Energy (5.6pVs)**

- ♦ Single -5.2V Power Supply

- ♦ On-Chip Data Registers

- **♦ ECL-Compatible Inputs with Differential Clock**

### \_Ordering Information

| PART      | TEMP. RANGE  | PIN-PACKAGE                   |

|-----------|--------------|-------------------------------|

| MAX555CQK | 0°C to +70°C | 68 Thermally<br>Enhanced PLCC |

Pin Configuration appears at end of data sheet.

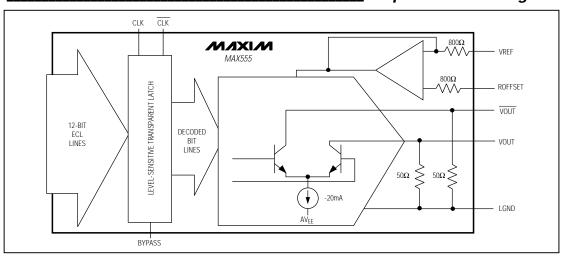

### Simplified Block Diagram

Maxim Integrated Products 1

Call toll free 1-800-998-8800 for literature.

### **ABSOLUTE MAXIMUM RATINGS**

| Analog Supply Voltage (AVEE)                  | 7V to +0.3V    |

|-----------------------------------------------|----------------|

| Digital Supply Voltage (DVEE)                 | 7V to +0.3V    |

| Digital Input Voltage (D0-D11)                | 5.5V to 0V     |

| Reference Input Voltage (VIN)                 | 0V to +1.25V   |

| Reference Input Current                       | 0mA to +1.56mA |

| Output Compliance Voltage (Voc)               |                |

| Output Common-Mode Voltage (V <sub>CM</sub> ) | 0.25V to +1.0V |

| Continuous Power Dissipation ( $T_A = +70$ °C) |               |

|------------------------------------------------|---------------|

| (without additional heatsink)                  | 1.3W          |

| Operating Temperature Range                    | 0°C to +70°C  |

| Junction Temperature Range (Note 1)            | 0°C to +150°C |

| Storage Temperature Range                      |               |

| Lead Temperature (soldering, 10sec)            | +300°C        |

|                                                |               |

Note 1: Typical thermal resistance, junction-to-case R<sub>BJC</sub> = 28°C/W. See *Package Information*.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(AV<sub>EE</sub> = DV<sub>EE</sub> = -5.2V, V<sub>REF</sub> = 1.000V,  $T_{MIN}$  to  $T_{MAX}$  = 0°C to +70°C, unless otherwise noted.) (Note 2.)

| PARAMETER                    | SYMBOL            | CONDITIONS                                                    |      | MIN        | TYP    | MAX   | UNITS            |

|------------------------------|-------------------|---------------------------------------------------------------|------|------------|--------|-------|------------------|

| DC ACCURACY                  |                   |                                                               |      |            |        |       |                  |

| Differential Linearity Error | DLE1              | V <sub>REF</sub> = 1.000V, current out, into                  | VOUT | -0.012     | ±0.003 | 0.012 | % Full<br>Scale  |

|                              | DLE2              | virtual ground, end-point linearity                           | VOUT | -0.05      | ±0.01  | 0.05  |                  |

| Integral Linearity Error     | ILE1              | V <sub>REF</sub> = 1.000V, current out, into                  | VOUT | -0.012     | ±0.006 | 0.012 | % Full           |

|                              | ILE2              | virtual ground, end-point linearity V                         | VOUT | -0.05      | ±0.01  | 0.05  | Scale            |

| Absolute Gain Error          | EG                | V <sub>REF</sub> = 1.000V, voltage out, VOUT/VIN (Note 3)     |      | -1.0       | ±0.2   | 1.0   | % Full<br>Scale  |

| 12-Bit Monotonicity          |                   |                                                               |      | Guaranteed |        |       |                  |

| Output Offset Current        | los               | D0-D11 = logic 1, V <sub>REF</sub> = 1.000V, measured at VOUT |      |            | 40     | 100   | μΑ               |

| Output Leakage Current       | ILEAK             | D0-D11 = logic 0, V <sub>REF</sub> = 0V,<br>measured at VOUT  |      |            | 3      | 50    | μΑ               |

| TIME-DOMAIN PERFORMANC       | E (Note 4)        |                                                               |      | •          |        |       | •                |

| Fall Time                    | t <sub>FALL</sub> | 90% to 10%, T <sub>A</sub> = +25°C                            |      | 510        |        | ps    |                  |

| Rise Time                    | t <sub>RISE</sub> | 10% to 90%, T <sub>A</sub> = +25°C                            |      | 450        |        | ps    |                  |

| Glitch Energy                |                   | Major carry, T <sub>A</sub> = +25°C                           |      | 5.6        |        | pVs   |                  |

| Settling Time                |                   | ±0.1% FSR                                                     |      | 4          |        | ns    |                  |

| 3                            |                   | ±0.024% FSR, 1LSB change                                      |      | 15         |        |       |                  |

| DYNAMIC PERFORMANCE (N       | otes 4, 5)        |                                                               |      |            |        |       | 1                |

|                              |                   | f <sub>OUT</sub> = 5MHz, f <sub>CLK</sub> = 50MHz             |      |            | 70     |       |                  |

| Spurious-Free Dynamic Range  |                   | f <sub>OUT</sub> = 10MHz, f <sub>CLK</sub> = 50MHz            |      | 70         |        |       | dBc              |

|                              |                   | f <sub>OUT</sub> = 20MHz, f <sub>CLK</sub> = 100MHz           |      | 65         |        |       |                  |

|                              |                   | f <sub>OUT</sub> = 30MHz, f <sub>CLK</sub> = 100MHz           |      | 60         |        |       |                  |

|                              |                   | f <sub>OUT</sub> = 30MHz, f <sub>CLK</sub> = 200MHz           |      | 56         |        |       |                  |

|                              |                   | f <sub>OUT</sub> = 40MHz, f <sub>CLK</sub> = 200MHz           |      | 53         |        |       |                  |

|                              |                   | fout = 40MHz, fclk = 250MHz                                   |      | 52         |        |       |                  |

|                              |                   | fout = 50MHz, fclk = 250MHz                                   |      | 51         |        |       |                  |

|                              |                   | fout = 40MHz, fclk = 300MHz                                   |      | 52         |        |       |                  |

|                              |                   | fout = 50MHz, fclk = 300MHz                                   |      |            | 51     |       |                  |

| Output Noise                 |                   | Bits 0–11 high, T <sub>A</sub> = +25°C                        |      |            | 10.6   |       | <u>nV</u><br>√Hz |

### **ELECTRICAL CHARACTERISTICS (continued)**

(AV<sub>EE</sub> = DV<sub>EE</sub> = -5.2V,  $V_{REF}$  = 1.000V,  $T_{MIN}$  to  $T_{MAX}$  = 0°C to +70°C, unless otherwise noted.) (Note 2.)

| PARAMETER                                          | SYMBOL           | CONDITIONS                                | MIN  | TYP   | MAX   | UNITS |

|----------------------------------------------------|------------------|-------------------------------------------|------|-------|-------|-------|

| DIGITAL INPUTS                                     | 1                |                                           |      |       |       |       |

| Input Current, Logic High                          | I <sub>IH</sub>  | V <sub>IH</sub> = -0.75V                  |      | 10    | 200   | μA    |

| Input Current, Logic Low                           | Iլլ              | V <sub>IL</sub> = -1.95V                  |      | 1     | 2     | μA    |

| Logic "1" Voltage                                  | VIH              |                                           | -1.1 | -0.75 | 0     | V     |

| Logic "0" Voltage                                  | VIL              |                                           | -2.0 | -1.95 | -1.48 | V     |

| DIGITAL TIMING                                     |                  |                                           | 1    |       |       |       |

| Data Update Rate                                   | fD               | Minimum data rate = DC (Note 6)           | 300  |       |       | MHz   |

| Data-to-Clock Setup Time                           | tsu              | Bypass = 0, clocked mode (Notes 4, 7)     |      | 1     |       | ps    |

| Data-to-Clock Hold Time                            | tHOLD            | Bypass = 0, clocked mode (Notes 4, 7)     |      | 1.8   |       | ns    |

| Clock-to-VOUT<br>Propagation Delay                 | t <sub>PD3</sub> | Bypass = 0, clocked mode (Notes 4, 7)     |      | 2.0   |       | ns    |

| LSBs Data-to-VOUT<br>Propagation Delay             | t <sub>PD2</sub> | Bypass = 1, transparent mode (Notes 4, 7) |      | 1.5   |       | ns    |

| MSBs Data-to-VOUT<br>Propagation Delay             | tPD1             | Bypass = 1, transparent mode (Notes 4, 7) |      | 2.1   |       | ns    |

| MSBs Decode Delay                                  | t <sub>DD</sub>  | Bypass = 1, transparent mode (Notes 4, 7) |      | 600   |       | ps    |

| CONTROL AMPLIFIER                                  |                  |                                           |      |       |       |       |

| Amplifier Input Resistance                         | RIN              | V <sub>REF</sub> = 1.000V                 | 775  | 800   | 825   | Ω     |

| Multiplying Input Bandwidth                        | BW               | -3dB                                      |      | 10    |       | MHz   |

| Open-Loop Gain                                     | AVOL             | $T_A = +25$ °C                            | 3    | 20    |       | kV/V  |

| Input Offset Voltage                               | Vos              | $T_A = +25$ °C                            | -250 | 0     | 250   | μV    |

| OUTPUT PERFORMANCE                                 |                  |                                           |      |       |       |       |

| Full-Scale Output Current                          | lout             | $V_{REF} = 1.000V$ , $R_L = 0\Omega$      | 19.0 | 20.0  | 21.0  | mA    |

| Output Resistance                                  | Rout             | VOUT, VOUT                                | 49.5 | 50.0  | 50.5  | Ω     |

| Output Capacitance                                 | Cout             | VOUT, VOUT                                |      | 15    |       | рF    |

| POWER SUPPLIES                                     | 1                |                                           |      |       |       | ı     |

| Analog Power-Supply Current                        | Alee             | AVEE = DVEE = -5.2V                       | 30   | 46    | 60    | mA    |

| Digital Power-Supply Current                       | DIEE             | AVEE = DVEE = -5.2V                       | 110  | 150   | 190   | mA    |

| Power Dissipation                                  | PD               |                                           |      | 0.98  | 1.3   | W     |

| Package Thermal Resistance,<br>Junction to Ambient | TJA              |                                           |      | 28    |       | °C/W  |

Note 2: All devices are 100% production tested at  $+25^{\circ}$ C and are guaranteed by design for T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub> as specified.

Note 3: The gain-error method of calculation is shown below:

Definition:  $EG \text{ Method:} \\ EG(\%) = \frac{[\text{VMEASURE(FS)} - \text{VIDEAL(FS)}] \times 100}{\text{VIDEAL(FS)}} \\ \text{where FS indicates full-scale measurements.} \\ EG \text{ Method:} \\ EG = [(4096 / 4095) \text{ VMEASURE} - 16(\text{VREF / RiN}) (\text{ROUT})] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [(4096 / 4095) \text{ VMEASURE} - 1] \times 100} \\ = [($

where:  $V_{REF} = 1.000V$ ,  $R_{IN} = 800\Omega$ ,  $R_{OUT} = 50\Omega$ ,  $V_{MEASURE} = \overline{VOUT}$  (FS).

- **Note 4:** Dynamic and timing specifications are obtained from device characterization and simulation testing and are not production tested. **Note 5:** Spurious-free dynamic range is measured from the fundamental frequency to any harmonic or non-harmonic spurs within

- Spurious-free dynamic range is measured from the fundamental frequency to any harmonic or non-narmonic spurs wit the bandwidth f<sub>CLK</sub>/2, unless otherwise specified.

- Note 6: Guaranteed by design.

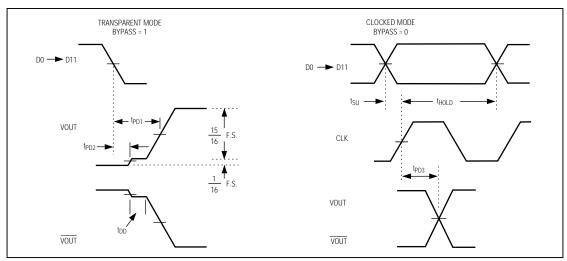

- Note 7: Timing definitions are detailed in Figure 2.

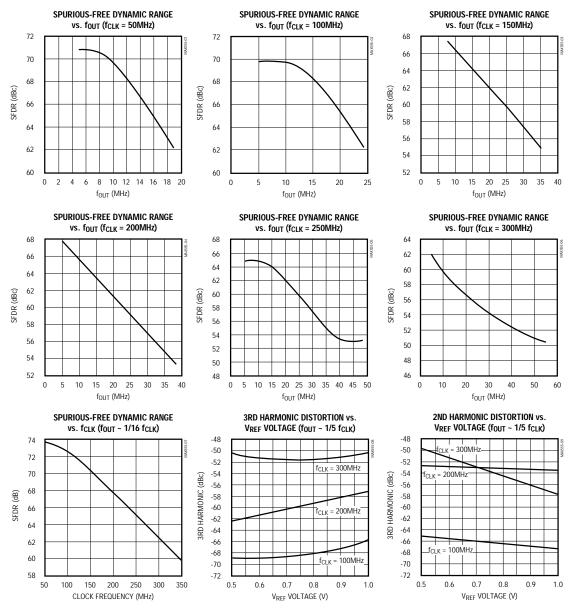

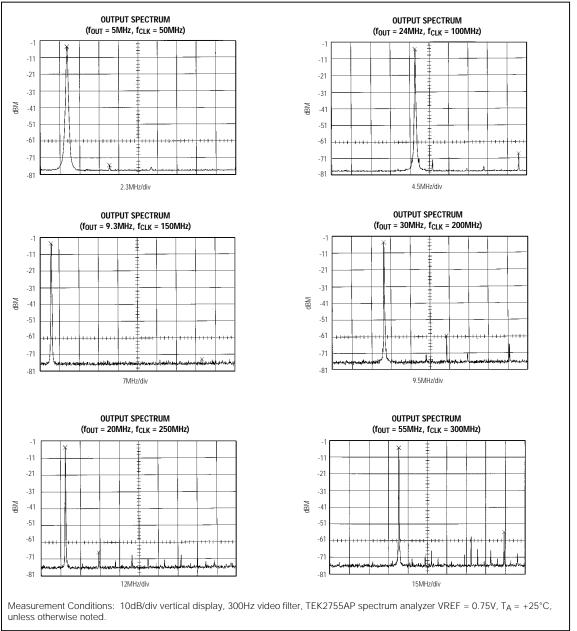

### Typical Operating Characteristics

(VREF = 0.75V,  $T_A = +25$ °C, unless otherwise noted.)

### Pin Description

| PIN                                                                   | NAME                 | FUNCTION                                                                                          |  |  |  |  |

|-----------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                                                                     | BYPASS               | Disables latching of data when high (ECL input)                                                   |  |  |  |  |

| 2                                                                     | CLK                  | Data Clock (ECL input)                                                                            |  |  |  |  |

| 3                                                                     | CLK                  | Data Clock Not (ECL input)                                                                        |  |  |  |  |

| 4, 56, 57,<br>63, 66                                                  | DGND                 | Digital Signal Grounds                                                                            |  |  |  |  |

| 5, 55                                                                 | DVEE                 | -5.2V Digital Power Supplies                                                                      |  |  |  |  |

| 10, 11, 12,<br>21–25, 27,<br>31, 36, 37,<br>40, 41, 43,<br>45, 46, 61 | N.C.                 | No Connection                                                                                     |  |  |  |  |

| 13, 14                                                                | VOUT                 | DAC Outputs                                                                                       |  |  |  |  |

| 15, 16                                                                | LGND                 | Ladder Grounds                                                                                    |  |  |  |  |

| 17, 18                                                                | VOUT                 | DAC Output Complements                                                                            |  |  |  |  |

| 19, 49, 51,<br>52, 53, 68                                             | TN                   | Test Node—internal test point, do not connect                                                     |  |  |  |  |

| 20, 29, 30,<br>48                                                     | AGND                 | Analog Signal Grounds                                                                             |  |  |  |  |

| 26, 44                                                                | HS                   | Heatspreader Connections—<br>bypass with 0.1µF to AV <sub>EE</sub>                                |  |  |  |  |

| 28                                                                    | ALTCOMPIB            | PTAT-IB Reference<br>Compensation Output (con-<br>nect bypass capacitor to<br>AVEE)               |  |  |  |  |

| 32                                                                    | LOOPCRNT             | Test node—must connect to AGND                                                                    |  |  |  |  |

| 33, 34                                                                | AVEE                 | -5.2V Analog Power Supplies                                                                       |  |  |  |  |

| 35                                                                    | VREF/2               | Analog Reference Voltage<br>Center-Tap Input                                                      |  |  |  |  |

| 38, 39                                                                | VREF                 | Analog Reference Voltage<br>Inputs (Kelvin connection)                                            |  |  |  |  |

| 42                                                                    | ROFFSET              | Offset Compensation Input                                                                         |  |  |  |  |

| 47                                                                    | ALTCOMPC             | Control-Amplifier PTAT<br>Reference Compensation<br>Input (connect bypass capaci-<br>tor to AVEE) |  |  |  |  |

| 50                                                                    | LBIAS                | Ladder-Bias Alternate<br>Compensation Output (con-<br>nect bypass capacitor to AVEE)              |  |  |  |  |

| 54, 58, 59,<br>60, 62, 64,<br>65, 67, 6,<br>7, 8, 9                   | D11(MSB)-<br>D0(LSB) | Data Words (ECL inputs)                                                                           |  |  |  |  |

#### \_Detailed Description

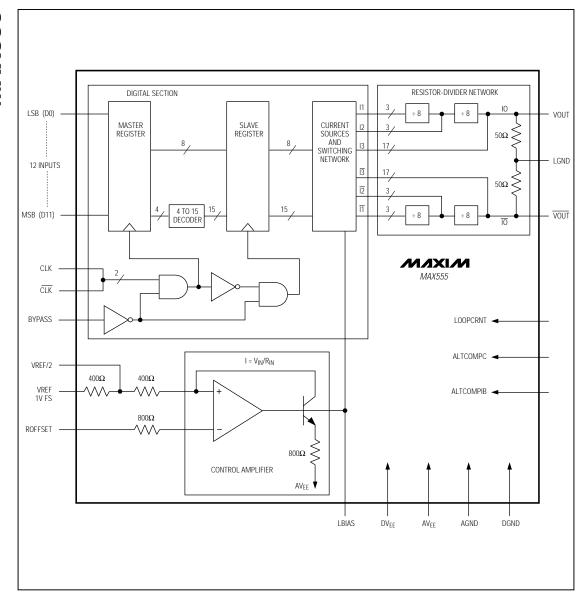

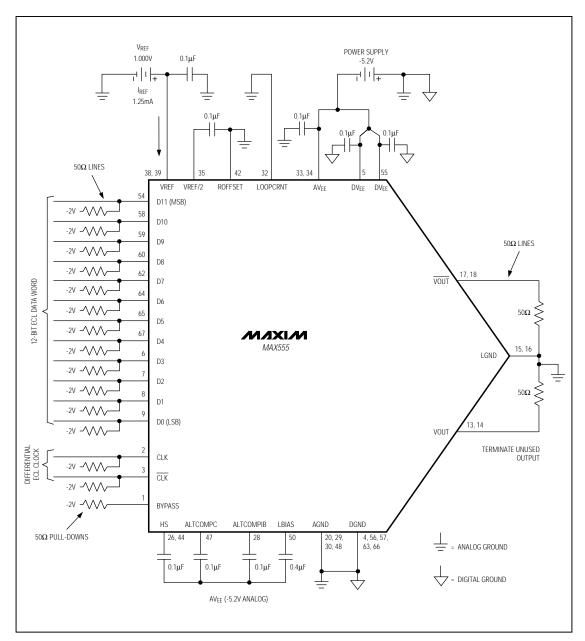

Figure 1's functional diagram shows the MAX555's three major divisions: a digital section, a control-amplifier section, and a resistor-divider network. The digital section consists of a master/slave register, decoding logic, and current switches. The control-amplifier section includes a control amplifier and an array of 23 current sources divided into three groups. The resistor divider scales the currents from these groups to achieve the correct binary weighting at the output. The output of the resistor-divider network is laser trimmed to  $50\Omega$ , a key feature for driving into controlled impedance transmission lines.

The first group of current sources comprises the six MSBs, D11–D6 (resulting in 15 identical, plus two binary weighted currents), which are applied directly to the output of the resistor-divider network. The second group, bits D5–D3 (three binary weighted currents), is applied to the middle of the divider network. The middle of the network divides the current seen at the output by 8. The third group, bits D2–D0 (three additional binary weighted current sources), is applied to the input of the resistive network, dividing the current seen at the output by 64.

Glitching is reduced by decoding the four MSBs into 15 identical current sources and synchronizing data with a master/slave register at every current switch. Data bits are transferred to the output on the positive-going edge of the clock, with the BYPASS input asserted low. In the asynchronous mode with the BYPASS input asserted high, the latches are transparent and data is transferred to the output regardless of the clock state. All digital inputs are ECL compatible. The clock input is differential.

The control amplifier forces a reference current, which is replicated in the current sources. This reference current is nominally 1.25mA. It can be supplied by an external current source, or by an external voltage source of 1.000V applied to the VREF input.

A reference input of  $V_{REF} = 1.000V$  will produce a full-scale output voltage of  $V_{FS} = -1.000V$ , where:

$V_{FS} = 4096 / 4095 \times \overline{VOUT}$  (code 0)

for the VOUT output. The output coding is summarized in Table 1.

The DAC's control amplifier has a typical open-loop voltage gain of 85dB, and its gain-magnitude bandwidth is flat up to 10MHz. When the control amplifier is not being used for high-speed multiplying applications, it is recommended that a 0.4µF capacitor be connected from LBIAS to AVEE to increase control-amplifier stability and reduce current-source noise.

Figure 1. Functional Diagram

6 \_\_\_\_\_\_\_M/1XI/M

**Table 1. Output Coding**

| DIGITAL CODE<br>(D11-D0) | VOUT<br>(V) | VOUT<br>(V) |  |  |

|--------------------------|-------------|-------------|--|--|

| 00000000000              | -0.999756   | 0           |  |  |

| 00000000001              | -0.999512   | -0.000244   |  |  |

| 011111111111             | -0.500000   | -0.499756   |  |  |

| 10000000000              | -0.499756   | -0.500000   |  |  |

| 111111111111             | 0           | -0.999756   |  |  |

#### **Timing Information**

The MAX555 features a differential ECL clock input with selective transparent operation (BYPASS = 1). It is possible to drive the MAX555 clock single-ended if desired by tying the  $\overline{\text{CLK}}$  input to an external voltage of -1.3V (ECL VBB). However, using a differential clock provides greater noise immunity and improved dynamic performance.

In the clocked mode (BYPASS = 0), when the clock line is low, the slave register is locked out and information on the digital inputs is permitted to enter the master register. The clock transition from low to high locks the master register in its present state and ignores further changes on the digital inputs. This transition simultaneously transfers the contents of the master register to the slave register, causing the DAC output to change.

Figure 2's timing diagram illustrates the importance of operating the MAX555 in the clocked mode. In the transparent mode (BYPASS = 1), both the master and slave registers are transparent, and changes in input data rip-

ple directly to the output. Because the four MSBs are decoded into 15 identical currents, there is a decode delay for these bits that is longer than for the eight LSBs. For the full-scale transition case shown, an intermediate output of 1/16 full-scale occurs until the four MSBs are properly decoded. This decode delay seriously degrades the device's spurious performance. In addition, skew in the timing of the input data also directly appears at the DAC output, further degrading high-speed performance.

MAX555 operation in the clocked mode (BYPASS = 0) with a differential clock precludes both of these potential problems and is required for high-speed operation. Since input data can only enter the master register when the clock is low (while the slave register is locked out), data-bus timing skew and the internal MSB decode delay will not appear at the DAC output. The DAC currents are switched only when the clock transitions from low to high, after the internal data stabilizes.

#### Layout and Power Supplies

The MAX555 has separate pins for analog and digital supplies. AVEE and DVEE are connected to each other through the substrate of the IC. These potentials should be derived from the same supply to minimize voltage mismatch, which would cause substrate current flow and possible latchup. Appropriate decoupling is needed to prevent digital-section current spikes from affecting the analog section (Figure 4).

It is recommended that a multilayer PC board be used, containing a solid ground and power planes. All analog

Figure 2. Timing Diagram

and digital ground pins must be connected directly to the analog ground plane at the MAX555, preferably with a "star connection" at the LGND pins (15 and 16).

High-speed ECL inputs, as well as the output from the MAX555, should employ good transmission-line techniques, with terminations close to the device pins. Separate power-supply buses for analog and digital power supplies are recommended as good general practice. Best results will be achieved by bypassing the device pins with high-quality ceramic chip capacitors connected physically close to the pins.

### \_Applications Information

#### Reference Input

The MAX555 uses an internal op-amp circuit to buffer the reference current. The input to the op amp may be driven with a 1.25mA external current source or a 1V external voltage reference. The reference input is the VREF pin. The input impedance to the op amp is  $800\Omega$ . As shown in Figure 1, VREF/2 is brought out externally with  $400\Omega$  of impedance to the op amp. These reference inputs can be used to vary the full-scale output for high-speed multiplying applications. ROFFSET must be connected to analog ground. In addition, a  $0.1\mu\text{F}$  capacitor should be connected from VREF/2 to analog ground to reduce reference current noise.

#### **Outputs**

The analog outputs are laser trimmed to  $50\Omega$ . They can be used either as a voltage drive with  $50\Omega$  impedance, or to drive into a virtual null using a transimpedance amplifier. Greater speed is achieved driving into  $50\Omega$  loads. The differential outputs of the MAX555 may be used to drive a balun for conversion to a single-ended output, while at the same time greatly reducing the second-harmonic content of the output.

#### **Dynamic Performance**

The Typical Operating Characteristics graphs show the MAX555's performance when used in direct digital synthesis (DDS) applications for generating RF sine waves. The first six graphs show the MAX555's spurious-free dynamic range (SFDR) for clock frequencies of 50MHz to 300MHz at various output frequencies. The seventh graph shows the SFDR for clock frequencies from 50MHz to 350MHz while producing an output frequency of about 1/16 the clock frequency.

The last two graphs show the MAX555's third and second harmonic distortion while producing an output frequency of about 1/5 fclk for clock frequencies from 100MHz to 300MHz as a function of the reference voltage. The third harmonic content of the output can be reduced at clock frequencies below about 200MHz by

reducing the reference voltage from its 1.000V nominal value. At clock frequencies above about 200MHz, the output's third harmonic content is dominated by coupling from the high-speed digital inputs to the output. Reducing the reference voltage at these high clock rates actually increases the third harmonic distortion in the output, since the carrier amplitude drops but the third harmonic level remains relatively constant.

The second harmonic distortion of the outputs is shown as a function of clock frequency and reference voltage. It is relatively constant for clock frequencies below about 200MHz at different  $V_{REF}$  values. As with the third harmonic distortion, however, the second harmonic distortion also increases at clock frequencies over 200MHz for lower  $V_{REF}$  values. Minimize these effects by bypassing the MAX555 heatspreader (pins 26 and 44) to  $V_{EE}$  with a good-quality RF chip capacitor. Reducing the swing of the input logic levels and/or decreasing the rise time of the digital signals can also improve the output's harmonic content. Combining these techniques achieves the best results. Some experimentation may be required to optimize the MAX555's performance for a particular application.

Figure 3 shows the spectrum analyzer plots of the MAX555 when used in DDS applications. These plots show the MAX555's output spectrum at clock frequencies from 50MHz to 300MHz while producing various output frequencies. Observing the output spectrum while adjusting the reference voltage or varying the logic levels is a sensitive method of optimizing MAX555 performance. The plots shown were obtained with a +0.75V reference voltage with 500mV ECL logic swings.

#### **Typical Application**

Figure 4 shows a typical connection. With  $\overline{VOUT}$  used to drive a  $50\Omega$  line, the unused complementary output, VOUT, should also be terminated to  $50\Omega$ . A 1V reference voltage at VREF gives a -0.5V full-scale voltage at  $\overline{VOUT}$  (when doubly terminated with  $50\Omega$  on the output). Because some loads may represent a complex impedance, be sure to match the output impedance with the load. Mismatching the impedances can cause reflections that will affect AC-performance parameters.

In all applications, the LOOPCRNT pin is always connected to AGND, and compensation capacitors are connected to pins ALTCOMPC, ALTCOMPIB, and LBIAS. The LBIAS compensation is recommended for non-multiplying applications. AC grounding the heat spreader on the package (with pins 26 and 44) reduces digital noise feedthrough and improves the MAX555's spurious performance at high data rates.

Figure 3. Spectrum Analyzer Plots

Figure 4. Typical Application

Pin Configuration TOP VIEW DO (LSB)

D1

D2

D2

D3

D3

DVEE

DGND

CIK

CIK

TN

TN

DGND

DGND

DGND

DGND

DGND

DS

NC. 9 8 7 6 5 4 3 2 1 68 67 66 65 64 63 62 61 N.C. 10 59 D9 58 D10 57 DGND N.C. 11 N.C. VOUT 13 57 DGND

56 DGND

55 DVEE

54 D11 (MSB)

53 TN

51 TN VOUT 14 LGND 15 LGND 16 VOUT 17 MIXIM VOUT 18 (TN) 19 51 TN

50 LBIAS

49 TN

48 AGND

47 ALTCOMPC

46 N.C.

45 N.C. AGND 20 N.C. 21 N.C. 22 23 N.C. N.C. 24 N.C. 25 HS 26 ALTOWNB AGNO TO AGNO T PLCC

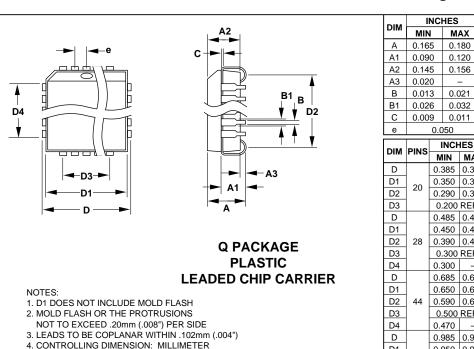

### Package Information

MILLIMETERS

MIN MAX

4.57

3.05

3.96

0.53

0.81

0.28

10.03

9.04

1.27

MILLIMETERS

7.37 8.38

5.08 REF

12.32 12.57

7.62 REF

12.70 REF

25.02 25.27

20.32 REF

7.62

11.94

15.87

4.19

2.29

3.68

0.51

0.33

0.66

0.23

MIN MAX MIN MAX

0.450 0.456 11.43 11.58

0.390 | 0.430 | 9.91 | 10.92

0.685 | 0.695 | 17.40 | 17.65

0.650 0.656 16.51 16.66

0.590 | 0.630 | 14.99 | 16.00

0.950 0.958 24.13 24.33

0.890 0.930 22.61 23.62

9.78

8.89

INCHES

0.180

0.120

0.156

0.021

0.032

INCHES

0.385 0.395

0.350 0.356

0.290 0.330

0.200 REF

0.300 REF

0.500 REF

0.985 0.995

0.800 REF

0.625

0.300

0.470

D1

D2

D3

D4

0.485 0.495

0.050

5. MEETS JEDEC MO047-XX AS SHOWN IN TABLE

7. D4 APPLIES TO THERMALLY ENHANCED

6. N = NUMBER OF PINS

PACKAGES ONLY.

12 NIXIN