#

# SOT23 Local Temperature Comparators with SMBus Serial Interface

### **General Description**

The MAX1755/MAX1756 are temperature monitors with ±3°C accuracy, each with a built-in comparator and SMBus<sup>™</sup>-controlled variable trip threshold. This DAC-programmable threshold allows specific thermal zones and system responses to overtemperature conditions to be adjusted under software control. The MAX1755/MAX1756 feature serial programmability, low cost, wide supply-voltage range, and a tiny package.

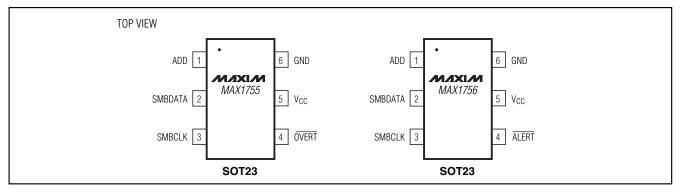

The MAX1755 has a self-clearing thermostat output (OVERT), and the MAX1756 has a latched interrupt output (ALERT). A variety of slave addresses allow for up to six devices per system (Table 3).

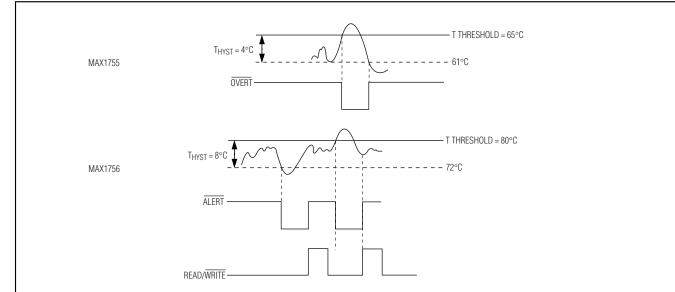

The MAX1755 has 4°C of built-in hysteresis. The MAX1756 detects both low-to-high and high-to-low temperature transitions within an 8°C temperature window. This arrangement supports "windowing" algorithms where the comparison threshold is reprogrammed "on-the-fly."

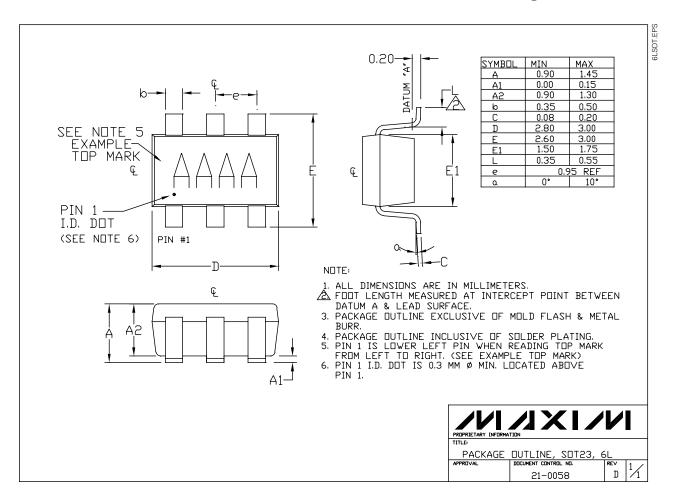

The MAX1755/MAX1756 are offered in the 6-pin SOT23 package and are specified over the -40°C to +125°C temperature range. For other temperature sensors with SMBus interfaces, refer to the MAX1617, MAX1618, MAX1668, and MAX1805 data sheets.

Local Temperature Monitoring Desktop Computers Notebook Computers

Servers

Workstations

Memory Modules

Multichip Modules

Industrial Control Systems

Automotive

Pin Configurations appear at end of data sheet.

SMBus is a trademark of Intel Corp.

#### Applications

Programmable Temperature Threshold

Features

- Built-In Hysteresis

- SMBus 2-Wire Serial Interface

- OVERT Thermostat Output (MAX1755)

- ◆ ALERT Interrupt Output (MAX1756)

- ◆ Threshold Accuracy ±3°C (+25°C to +100°C) ±5°C (-40°C to +125°C)

- ♦ 200µA (max) Supply Current

- +2.375V to +5.5V Supply Range

- Tiny 6-Pin SOT23 Package

### **Ordering Information**

| PART*       | TEMP. RANGE     | PIN-<br>PACKAGE | top<br>Mark |

|-------------|-----------------|-----------------|-------------|

| MAX1755AAUT | -40°C to +125°C | 6 SOT23-6       | AANM        |

| MAX1755BAUT | -40°C to +125°C | 6 SOT23-6       | AANL        |

| MAX1756AAUT | -40°C to +125°C | 6 SOT23-6       | AANO        |

| MAX1756BAUT | -40°C to +125°C | 6 SOT23-6       | AANL        |

\*A and B suffixes on these devices select different combinations of slave addresses. See Table 3 to determine the appropriate suffix.

**Note:** Requires a special solder temperature profile described in the Absolute Maximum Ratings section.

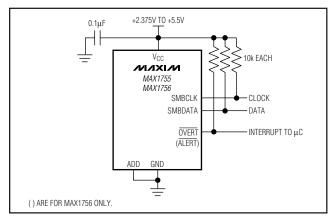

# **Typical Operating Circuit**

#

Maxim Integrated Products 1

For price, delivery, and to place orders, please contact Maxim Distribution at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

V<sub>CC</sub> to GND .....-0.3V to +6V ADD to GND .....-0.3V to (V<sub>CC</sub> +0.3V) SMBCLK, SMBDATA, ALERT, OVERT to GND .....-0.3V to +6V SMBDATA, ALERT, OVERT Current....-1mA to +50mA Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )

| 6-Pin SOT23 (derate 9.1mW/°C above +70°C)727mW       |  |

|------------------------------------------------------|--|

| Operating Temperature Range (extended)40°C to +125°C |  |

| Junction Temperature+150°C                           |  |

| Storage Temperature Range65°C to +150°C              |  |

Note 1: This device is constructed using a unique set of packaging techniques that impose a limit on the thermal profile to which the device can be exposed during board-level solder attach and rework. The limit permits the use of only the solder profiles recommended in the industry-standard specification, IPC/JEDEC J-STD-020A, paragraph 7.6, Table 3 for IR/VPR and Convection reflow. Preheating is required. Hand or wave soldering is not allowed.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = +3.3V, T<sub>A</sub> = 0°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                                  | CONDITIONS                                                              | MIN                   | ТҮР | МАХ  | UNITS |

|--------------------------------------------|-------------------------------------------------------------------------|-----------------------|-----|------|-------|

| TEMPERATURE COMPARATOR AND POW             | ER SUPPLY                                                               | •                     |     |      |       |

| DAC Resolution (Note 3)                    | Monotonicity guaranteed                                                 | 2                     |     |      | °C    |

| Tarra and an Oarra ania an Eman            | $T_A = +25^{\circ}C \text{ to } +100^{\circ}C$                          | -3                    |     | 3    | °C    |

| Temperature Comparison Error               | $T_A = 0^{\circ}C$ to $+125^{\circ}C$                                   | -5                    |     | 5    | Ĵ     |

| Temperature Hysteresis                     | With respect to temperature comparison value (MAX1755)                  | -4.5                  | -4  | -3.5 | °C    |

| Temperature Window                         | Lower threshold with respect to temperature comparison value (MAX1756)  | -9                    | -8  | -7   | Ĵ     |

| Sampling Frequency                         |                                                                         | 0.50                  | 1   | 2.00 | kHz   |

| Supply Voltage Range                       |                                                                         | 2.375                 |     | 5.5  | V     |

| Undervoltage Lockout Threshold             | V <sub>CC</sub> input, rising edge                                      | 2.05                  | 2.2 | 2.35 | V     |

| Undervoltage Lockout Hysteresis            |                                                                         |                       | 30  |      | mV    |

| Power-On Reset Threshold                   | V <sub>CC</sub> , falling edge                                          | 0.2                   | 1.5 | 2    | V     |

| Operating Supply Current                   | SMBus static, logic inputs forced to $V_{\mbox{\scriptsize CC}}$ or GND |                       | 85  | 200  | μA    |

| Standby Supply Current                     | SMBus static, logic inputs forced to $V_{\mbox{\scriptsize CC}}$ or GND |                       | 0.8 | 4    | μΑ    |

| ADD Input High Voltage                     |                                                                         | 0.8 x V <sub>C</sub>  | С   |      | V     |

| ADD Input Low Voltage                      |                                                                         | 0.2 × V <sub>CC</sub> |     | V    |       |

| SMBus INTERFACE                            |                                                                         |                       |     |      |       |

| Logic Input High Voltage                   | SMBCLK, SMBDATA; $V_{CC} = 2.7V$ to 5.5V                                | 2.1                   |     |      | V     |

| Logic Input Low Voltage                    | SMBCLK, SMBDATA; $V_{CC} = 2.7V$ to 5.5V                                |                       |     | 0.8  | V     |

| SMBus Output Low Sink Current              | SMBDATA forced to 0.4V; $V_{CC} = 2.7V$ to 5.5V                         | 6                     |     |      | mA    |

| ALERT, OVERT Output Low Sink Current       | Pin forced to 0.4V                                                      | 6                     |     |      | mA    |

| ALERT, OVERT Output High Leakage Current   | Pin forced to 5.5V                                                      |                       |     | 1    | μA    |

| Logic Input Current (ADD, SMBCLK, SMBDATA) | Inputs forced to V <sub>CC</sub> or GND                                 | -1                    |     | 1    | μA    |

| SMBus Input Capacitance                    | SMBCLK, SMBDATA                                                         |                       | 5   |      | pF    |

| SMBus Clock Frequency                      | (Note 4)                                                                | DC                    |     | 100  | kHz   |

| SMBCLK Clock Low Time                      | $t_{LOW}$ , 10% to 10% points, $V_{CC}$ = 2.7V to 5.5V                  | 4.7                   |     |      | μs    |

| SMBCLK Clock High Time                     | $t_{\text{HIGH}}$ , 90% to 90% points, $V_{\text{CC}}$ = 2.7V to 5.5V   | 4                     |     |      | μs    |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3.3V, T_A = 0^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                      | CONDITIONS                                                                               | MIN | TYP | MAX | UNITS |

|------------------------------------------------|------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| SMBus Rise Time                                | SMBCLK, SMBDATA; 10% to 90% points, $V_{CC} = 2.7V$ to 5.5V                              |     |     | 1   | μs    |

| SMBus Fall Time                                | SMBCLK, SMBDATA; 90% to 10% points, $V_{CC} = 2.7V$ to 5.5V                              |     |     | 300 | ns    |

| SMBus Start Condition Setup Time               | $V_{CC} = 2.7 V$ to 5.5 V                                                                | 4.7 |     |     | μs    |

| SMBus Repeated Start Condition Setup Time      | tsu:sta, 90% to 90% points, $V_{CC} = 2.7V$ to 5.5V                                      | 250 |     |     | ns    |

| SMBus Start Condition Hold Time                | t <sub>HD:STA</sub> , 10% of SMBDATA to 90% of<br>SMBCLK, V <sub>CC</sub> = 2.7V to 5.5V | 4   |     |     | μs    |

| SMBus Stop Condition Setup Time                | $t_{SU:STO}$ , 90% of SMBCLK to 10% of SMBDATA; V <sub>CC</sub> = 2.7V to 5.5V           | 4   |     |     | μs    |

| SMBus Data Valid to SMBCLK Rising-Edge<br>Time | $t_{\rm SU:DAT},10\%$ or 90% of SMBDATA to 10% of SMBCLK; $V_{\rm CC}$ = 2.7V to 5.5V    | 250 |     |     | ns    |

| SMBus Data-Hold Time (Master Transmitter)      | $t_{HD:DAT}$ , $V_{CC} = 2.7V$ to 5.5V                                                   | 0   |     |     | μs    |

| SMBus Data-Hold Time (Slave Transmitter)       | $t_{HD:DAT}$ , $V_{CC} = 2.7V$ to 5.5V                                                   | 300 |     |     | ns    |

### **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = +3.3V,  $T_A$  = -40°C to +125°C, unless otherwise noted.) (Note 2)

| PARAMETER                                | CONDITIONS                                                             | MIN   | TYP | MAX  | UNITS |  |

|------------------------------------------|------------------------------------------------------------------------|-------|-----|------|-------|--|

| TEMPERATURE COMPARATOR AND POW           | ER SUPPLY                                                              |       |     |      |       |  |

| DAC Resolution (Note 3)                  | Monotonicity guaranteed                                                | 2     |     |      | °C    |  |

| Temperature Comparison Error             |                                                                        | -5    |     | 5    | °C    |  |

| Temperature Hysteresis                   | With respect to temperature comparison value (MAX1755)                 | -4.5  |     | -3.5 | °C    |  |

| Temperature Window                       | Lower threshold with respect to temperature comparison value (MAX1756) | -9    |     | -7   |       |  |

| Supply Voltage Range                     |                                                                        | 2.375 |     | 5.5  | V     |  |

| Operating Supply Current                 | SMBus static, logic inputs forced to $V_{CC}$ or GND                   |       |     | 200  | μA    |  |

| SMBus INTERFACE                          |                                                                        |       |     |      |       |  |

| SMBus Output Low Sink Current            | SMBDATA forced to 0.4V; $V_{CC} = 2.7V$ to 5.5V                        | 6     |     |      | mA    |  |

| ALERT, OVERT Output Low Sink Current     | Pin forced to 0.4V                                                     | 6     |     |      | mA    |  |

| ALERT, OVERT Output High Leakage Current | Pin forced to 5.5V                                                     |       |     | 1    | μA    |  |

**Note 2:** Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over operating temperature are guaranteed by design. **Note 3:** Guaranteed, but not 100% tested.

**Note 4:** The SMBus logic block is a static design that works with clock frequencies down to DC. While slow operation is possible, it violates the 10kHz minimum clock frequency and SMBus specifications and may monopolize the bus.

(V<sub>CC</sub> = +3.3V,  $T_A$  = +25°C, unless otherwise noted.)

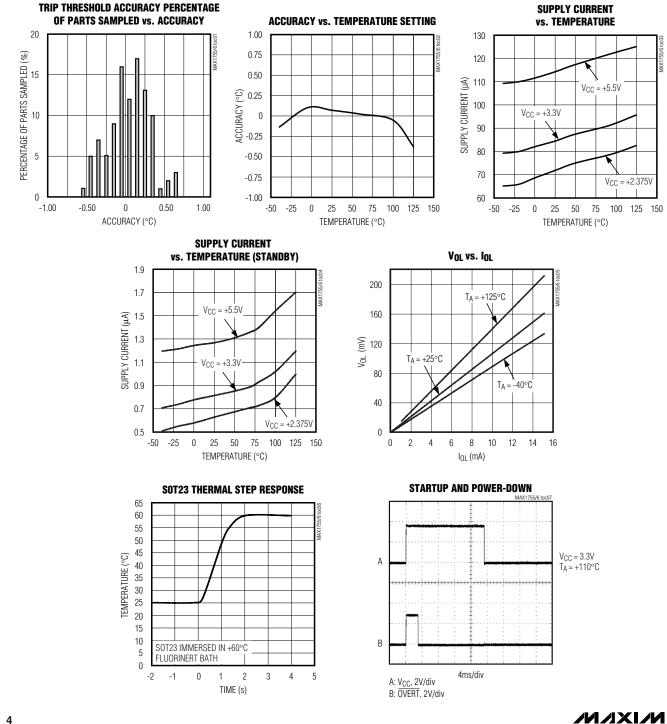

**Typical Operating Characteristics**

MAX1755/MAX1756

### **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                             |  |

|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | ADD             | SMBus Address Select Pin. See Table 3.                                                                                                                                               |  |

| 2   | SMBDATA         | SMBus Serial-Data Input/Output, Open Drain                                                                                                                                           |  |

| 3   | SMBCLK          | SMBus Serial-Clock Input                                                                                                                                                             |  |

| 4   | OVERT           | Open-Drain Thermostat Output (MAX1755 only)                                                                                                                                          |  |

| 4   | ALERT           | Open-Drain SMBus Alert (Interrupt) Output (MAX1756 only)                                                                                                                             |  |

| 5   | V <sub>CC</sub> | Supply Voltage Input, +2.375V to +5.5V. Bypass V <sub>CC</sub> to GND with a 0.1 $\mu$ F capacitor. If supply is noisy, insert 100 $\Omega$ resistor in series with this connection. |  |

| 6   | GND             | Ground                                                                                                                                                                               |  |

# **Detailed Description**

The MAX1755/MAX1756 are temperature comparators designed to work in conjunction with an external microcontroller ( $\mu$ C) or other digital intelligence through an SMBus interface. The  $\mu$ C is typically a power-management or keyboard controller, which generates SMBus serial commands from a GPIO port or through a dedicated SMBus interface block.

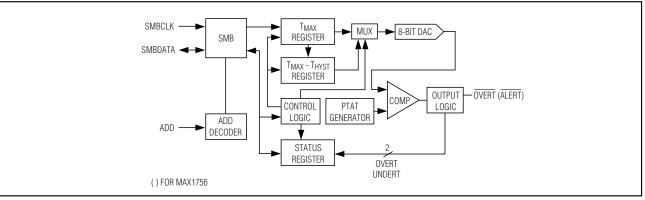

Figure 1 illustrates the circuit blocks in the MAX1755/ MAX1756. The output of an analog temperature-to-voltage converter signal is compared to the temperaturestable output of a serially programmed dual-output digital-to-analog converter (DAC). Great care is taken in the design to ensure that the thermal signal is proportional to absolute temperature or PTAT. A precision comparator with low-input offset voltage is used to compare the PTAT voltage to the DAC output.

The DAC provides two levels: one is set to the rising trip threshold, and the other is set to the falling threshold (hysteresis) level by a digital subtractor. This arrangement makes the hysteresis value very accurate with respect to the rising trip point. Each DAC level is alternately compared to the PTAT voltage through a sampling system that reuses the same comparator, thereby reducing errors due to comparator offset. The sampling rate is typically 1kHz.

A simplified SMBus interface enables the system to program the temperature thresholds and read the part's status register.

#### **SMBus Digital Interface**

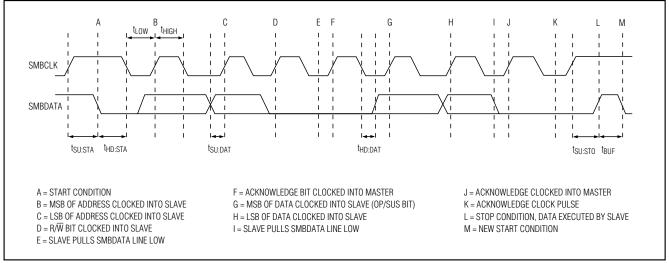

The SMBus block utilizes the read-byte/write-byte protocol. It only supports 8-bit reads and writes, has no command byte, and doesn't need to support the Alert Response feature. From a software perspective, the MAX1755/MAX1756 appear as write registers containing the DAC comparison value and as read registers containing the status byte. A standard SMBus 2-wire serial interface is used to program DAC values and read the status byte. Figure 2 shows the SMBus data protocols and Figure 3 details the SMBus timing.

#### Programming the TMAX Register

The T<sub>MAX</sub> register is programmed using a standard SMBus Send Byte operation. The temperature data format is 6 bits plus sign in two's complement form, with each data bit representing 2°C (Table 1). The MSB is transmitted first, LSB last. The MSB (B7) of the T<sub>MAX</sub> register is an embedded control bit, which can either invert the polarity of the OVERT output (MAX1755) or mask low-going (T<sub>HYST</sub>) interrupts (MAX1756). The B6 bit of the T<sub>MAX</sub> register is the sign bit for the remaining 6 bits that make up the binary-coded temperature threshold.

#### **Software Standby Mode**

If the DAC code is set to negative full scale, the device goes into software standby mode. In standby mode, supply current is reduced to  $0.8\mu$ A. At very low supply voltages (UVLO threshold), the supply current is higher due to address decoding. Typical supply current can be as high as 250 $\mu$ A, depending on the ADD setting, while the typical ADD input current can be as high as 40 $\mu$ A. Exiting standby mode causes the slave address to be checked again.

#### **OVERT** Thermostat Output (MAX1755)

The OVERT output is a self-clearing interrupt output that is activated when the current temperature equals or

Figure 1. MAX1755/MAX1756 Block Diagram

|   | te Format |            |       |        |       |   |

|---|-----------|------------|-------|--------|-------|---|

| S | ADDRESS   | READ/WRITE | ACK   | DATA   | ACK   | Р |

|   | 7 bits    | 1 bit      | 1 bit | 8 bits | 1 bit |   |

#### **Receive Byte Format**

| 11000110 | Dyte i offiat |            |       |        |       |   |

|----------|---------------|------------|-------|--------|-------|---|

| S        | ADDRESS       | READ/WRITE | ACK   | DATA   | ///   | Ρ |

|          | 7 bits        | 1 bit      | 1 bit | 8 bits | 1 bit |   |

S = START CONDITION

P = STOP CONDITION

SHADED = SLAVE TRANSMISSION /// = NOT ACKNOWLEDGED (NACK)

Figure 2. SMBus Protocols

Figure 3. SMBus Write Timing Diagram

| MASK/POLARITY |                     | DAC REGIS      | NOMINAL TEMPERATURE |     |                  |

|---------------|---------------------|----------------|---------------------|-----|------------------|

| BIT POR STATE | MASK OR<br>POLARITY | SIGN           | MSB                 | LSB | THRESHOLD (°C)   |

| 1/0           | Х                   | 0              | 111111              |     | +126             |

| 1/0           | Х                   | 0              | 111110              |     | +124             |

| 1/0           | Х                   | 0              | 110010              |     | +100 (POR State) |

| 1/0           | Х                   | 0              | 001100              |     | +24              |

| 1/0           | Х                   | 0              | 000001              |     | +2               |

| 1/0           | Х                   | 0              | 000000              |     | 0                |

| 1/0           | Х                   | 1              | 111111              |     | -2               |

| 1/0           | Х                   | 1              | 111110              |     | -4               |

| 1/0           | Х                   | 1              | 101100              |     | -40              |

| 1/0           | Х                   | 1              | 100101              |     | -54              |

| 1/0           | Bet                 | ween (X 1 1001 | 01) and (X 1 00000  | 1)  | -54              |

| 1/0           | Х                   | 1              | 000001              |     | -54              |

| 1/0           | Х                   | 1              | 000000              |     | Standby Mode     |

#### Table 1. TMAX Register Data Format (Two's Complement)

**POLARITY bit:**  $0 = \overline{OVERT}$  is active low;  $1 = \overline{OVERT}$  is active high (MAX1755). **MASK bit:** A logic 1 disables T<sub>HYST</sub> (negative-going) interrupts (MAX1756).

exceeds  $T_{MAX}$ .  $\overrightarrow{OVERT}$  normally goes low when active, but this polarity can be changed through the POLARITY bit in the  $T_{MAX}$  register. The latch is cleared when the current temperature reading is equal to or less than the current  $T_{MAX}$  value minus 4°C, which provides for 4°C of hysteresis (Figure 4).

#### **ALERT** Interrupt (MAX1756)

The ALERT interrupt output signal is latched and can only be cleared by reading the status register or writing a new T<sub>MAX</sub> value. Interrupts are generated when the device temperature goes above the current T<sub>MAX</sub> DAC setting or below the current DAC setting minus 8°C (T<sub>HYST</sub>). The POR state masks undertemperature interrupts (Figure 4).

#### **Status Register**

The bit functions for the status register are summarized in Table 2. The OVER bit (MSB) indicates when the T<sub>MAX</sub> threshold is crossed. The UNDER bit (B6) indicates when the T<sub>HYST</sub> threshold is crossed. For the MAX1755, the UNDER bit is not masked during POR; if the die temperature is less than 96°C, this bit will assert. For the MAX1756, the UNDER bit is masked to zero during POR. OVER and UNDER are cleared by any read or write operations. In the MAX1755, the OUT-

M/X/M

PUT bit (B5) mirrors the state of the OVERT signal. The OUTPUT bit is not used in the MAX1756 and returns zero. The DEFAULT bit (B1) indicates that the DAC is at the default value. This condition implies that the POR threshold was crossed. The DEFAULT bit is cleared using a Send Byte operation. The ERROR bit (LSB) indicates that the UVLO threshold was crossed, and therefore the conversion is inaccurate. Use a Send Byte operation, and make sure that V<sub>CC</sub> is in the valid operating range to clear this bit. The remaining bits in the status register (B4, B3, B2) are reserved for future use.

#### **Slave Addresses**

The MAX1755/MAX1756 appear to the SMBus as one address for both reads and writes. The device address can be set to one of three different values by pin strapping ADD, so that up to six ICs can reside on the same bus without address conflicts (Table 3). A test for the current state of the address pins is done at POR and when exiting standby mode. The results of this test are latched as the current address. This scheme allows for the use of three-way pin-strapping to set the address (V<sub>CC</sub>, GND, floating).

Figure 4. OVERT, ALERT Response

### **Table 2. Status Register Bit Assignments**

| BIT        | NAME                       | POR STATE   | FUNCTION                                                                                                                                                                    |  |  |  |

|------------|----------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7<br>(MSB) | OVER                       | 0           | This bit indicates that the $T_{\mbox{MAX}}$ threshold was crossed. Send a Send Byte or Receive Byte to clear this bit.                                                     |  |  |  |

| 6          | UNDER Not masked (MAX1755) |             | This bit indicates that the $T_{HYST}$ threshold was crossed. Send a Send Byte or                                                                                           |  |  |  |

| 0          | UNDER                      | 0 (MAX1756) | Receive Byte to clear this bit. See Table 1.                                                                                                                                |  |  |  |

| 5          | OUTPUT                     | Not latched | MAX1755: This bit exactly follows the current state of the $\overrightarrow{\text{OVERT}}$ pin (self-clearing). MAX1756: This bit is reserved for future use (returns 0).   |  |  |  |

| 4, 3, 2    | RFU                        | N/A         | Reserved for future use.                                                                                                                                                    |  |  |  |

| 1          | DEFAULT                    | 0           | This bit indicates that the DAC is at the default value; POR threshold was crossed. Send a Send Byte to clear this bit.                                                     |  |  |  |

| 0          | ERROR                      | 1           | This bit indicates that the conversion is inaccurate; UVLO threshold was crossed. Send a Send Byte and bring $V_{CC}$ back up to a valid operating range to clear this bit. |  |  |  |

#### **POR and UVLO**

The MAX1755/MAX1756 have volatile memory. To prevent power-supply conditions from corrupting the data in memory and causing erratic behavior, a POR voltage detector monitors V<sub>CC</sub> and clears the memory if V<sub>CC</sub> falls below 1.5V (typ, see *Electrical Characteristics*). When power is first applied and V<sub>CC</sub> rises above 1.5V (typ), the logic blocks begin operating, although the address decoder is not enabled until V<sub>CC</sub> > UVLO voltage. The UVLO comparator prevents the DAC and tem-

perature comparator from operating until there is sufficient headroom (V\_{CC}  $\ge$  2.2V typ).

#### **Power-Up Defaults:**

- T<sub>MAX</sub> register is set to +100°C.

- ALERT and OVERT are reset to High-Z state.

- OVERT polarity is set to active-low (MAX1755 only).

- ALERT low-going hysteresis interrupts are masked (MAX1756 only).

- Status byte is cleared.

| DEVICE   | ADD PIN TIED TO | ADDRESS  |

|----------|-----------------|----------|

| MAX1755A | V <sub>CC</sub> | 1001 000 |

| MAX1755A | GND             | 1001 001 |

| MAX1755A | Floating        | 0101 001 |

| MAX1755B | V <sub>CC</sub> | 0011 000 |

| MAX1755B | GND             | 0011 001 |

| MAX1755B | Floating        | 0101 000 |

| MAX1756A | V <sub>CC</sub> | 1001 010 |

| MAX1756A | GND             | 1001 011 |

| MAX1756A | Floating        | 0101 011 |

| MAX1756B | V <sub>CC</sub> | 0011 010 |

| MAX1756B | GND             | 0011 011 |

| MAX1756B | Floating        | 0101 010 |

#### Table 3. Slave Address Decoding (ADD Pin)

### **Applications Information**

#### **Thermal Considerations**

The MAX1755/MAX1756 supply current is typically 85µA. When used to drive high-impedance loads, the devices dissipate negligible power. Therefore, the die temperature is essentially the same as the package temperature. The key to accurate temperature monitoring is good thermal contact between the MAX1755/ MAX1756 package and the device being monitored. In some applications, the 6-pin SOT23 package may be small enough to fit underneath a socketed µP, allowing the device to monitor the µP's temperature directly. Accurate temperature monitoring depends on the thermal resistance between the device being monitored and the MAX1755/MAX1756 die. Heat flows in and out of plastic packages primarily through the leads. Short, wide copper traces leading to the temperature monitor ensure that heat transfers guickly and reliably. The rise in die temperature due to self-heating is given by the following formula:

#### $\Delta T_J = P_{DISSIPATION} \times \theta_{JA}$

where PDISSIPATION is the power dissipated by the MAX1755/MAX1756, and  $\theta_{JA}$  is the package's thermal resistance.

The typical thermal resistance is 110°C/W. To limit the effects of self-heating, minimize the output currents. For example, if the MAX1755 or MAX1756 sink 6mA, the output voltage is guaranteed to be less than 0.4V. Therefore, an additional 2.4mW of power is dissipated within the IC. This corresponds to a 0.26°C shift in the die temperature.

#### ALERT Software Model Example of Temperature Windowing

The MAX1756 ALERT interrupt output is designed so that effective clock-throttling and/or fan speed control can be done by the host firmware, while keeping the commands and registers of the MAX1756 very simple.

At initial power-up,  $T_{MAX}$  is set to +100°C. The user can modify this as needed using Send Byte. The POR state masks undertemperature interrupts. The initial temperature is assumed to be very low, below the  $T_{HYST}$  undertemperature threshold. No ALERT signal is issued, since  $T_{HYST}$  interrupts are masked.

If the system heats up sufficiently to exceed T<sub>MAX</sub>, this generates the first interrupt. The host reads the status byte, determining that the T<sub>MAX</sub> temperature was exceeded. The interrupt, although cleared, is immediately asserted again since the temperature still exceeds T<sub>MAX</sub>. The host now immediately writes a new value to the DAC register, approximately 4°C above the old D/A value. This hopefully places the (T<sub>MAX</sub> - T<sub>HYST</sub>) window centered around the current device temperature. This new DAC value also writes a zero to the MASK bit, enabling T<sub>HYST</sub> interrupts. Writing a new value clears the status byte and ALERT latch. The system then takes whatever corrective action is needed (clock throttling or fan control).

If the temperature continues to increase, another corrective action routine is done, similar to above. If the temperature decreases below  $T_{HYST}$ , an interrupt is generated and the host can remove the corrective action (if desired), set a new  $T_{MAX}$  value, and clear status, similar to the routine above.

If desired, the host can now mask undertemperature interrupts to avoid nuisance interrupts as the system cools.

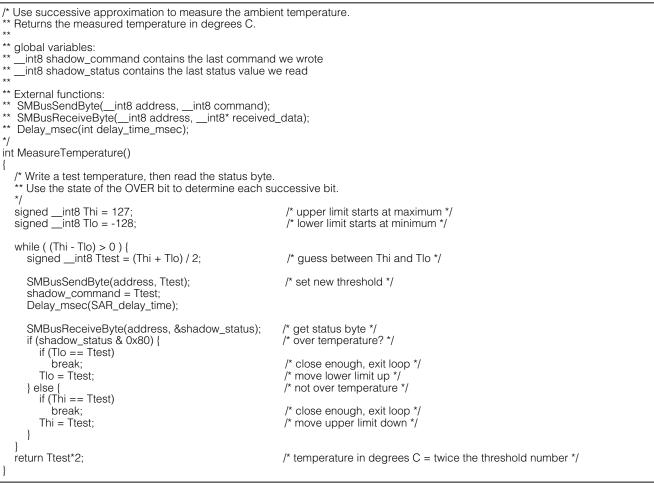

#### Temperature Measurement Using a Software SAR

A useful application of the MAX1755 is to determine the ambient temperature with a successive approximation algorithm to set the T<sub>MAX</sub> register. Like a successive approximation register (SAR) analog-to-digital converter, the C code routine provided in Listing 1 tests 1 bit at a time in the T<sub>MAX</sub> register form MSB to LSB. Based on the response of the OVERT signal, the bit is either set or cleared. This simple set and check algorithm repeats until all of the bits are set.

### Chip Information

TRANSISTOR COUNT: 2963

### Listing 1. Measuring Temperature by Successive Approximation

### Pin Configurations

### **Package Information**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2000 Maxim Integrated Products

Printed USA

**MAXIM** is a registered trademark of Maxim Integrated Products.