19-1132; Rev 0; 10/96

Radar Receivers Professional Video

## 12-Bit, 10Msps, TTL-Output ADC

#### General Description

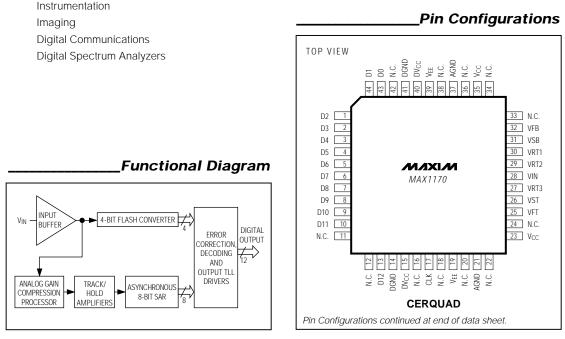

Applications

The MAX1170 analog-to-digital converter (ADC) is a 12-bit monolithic ADC capable of sample rates greater than 10Msps. An on-board input buffer and track/hold function ensure excellent dynamic performance without the need for external components. A 5pF input capacitance minimizes development problems.

Logic inputs and outputs are TTL compatible. An overrange output signal is provided to indicate overflow conditions. Output data format is straight binary. Power dissipation is a very low 1.1W with power-supply voltages of +5.0V and -5.2V. The MAX1170 also provides a wide input voltage range of  $\pm 2.0V$ .

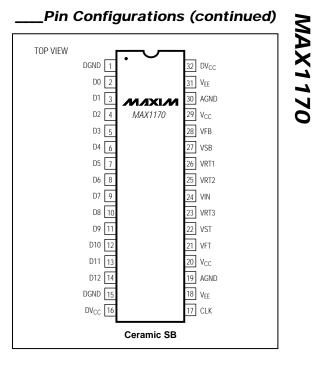

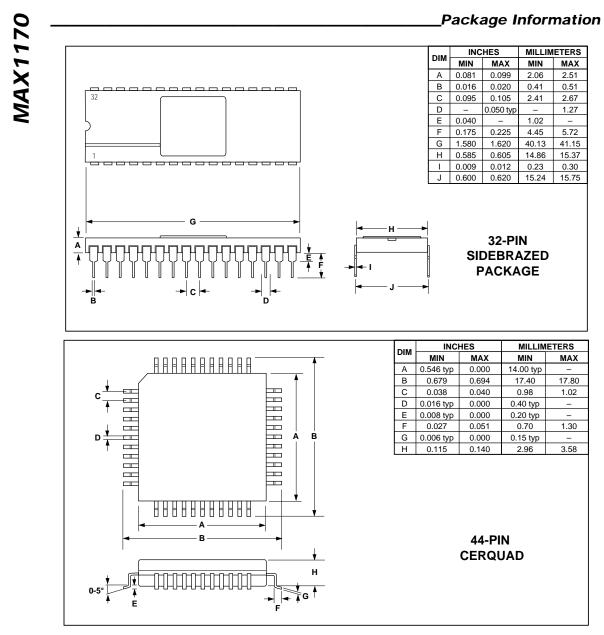

The MAX1170 is available in a 32-lead ceramic sidebrazed package and a 44-lead surface-mount CERQUAD package.

#### \_\_Features

- Monolithic, 12-Bit, 10Msps Converter

- On-Chip Track/Hold

- ±2.0V Analog Input Range

- High Input Impedance

- 66dB SNR at 1MHz Input

- Low Power: 1.1W

- 5pF Input Capacitance

- + TTL-Compatible Outputs

#### **Ordering Information**

| PART       | TEMP. RANGE  | PIN-PACKAGE   |

|------------|--------------|---------------|

| MAX1170CDJ | 0°C to +70°C | 32 Ceramic SB |

| MAX1170CBH | 0°C to +70°C | 44 CERQUAD    |

M/XI/M

Maxim Integrated Products 1

For the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800

# **MAX1170**

## ABSOLUTE MAXIMUM RATINGS

| V <sub>CC</sub>          | +6V                                    |

|--------------------------|----------------------------------------|

| VEE                      | 6V                                     |

| Analog Input             | $\dots$ $V_{FB} \le V_{IN} \le V_{FT}$ |

| VFB, VFT                 | 3.0V, +3.0V                            |

| Reference Ladder Current | 12mA                                   |

| CLK IN                   | V <sub>CC</sub>                        |

| Digital Outputs                     | 0mA to -30mA   |

|-------------------------------------|----------------|

| Operating Temperature Range         | 0°C to +70°C   |

| Junction Temperature (Tj)           | +175°C         |

| Storage Temperature Range           | 65°C to +150°C |

| Lead Temperature (soldering, 10sec) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +5.0V, \ V_{EE} = -5.2V, \ DV_{CC} = +5.0V, \ V_{IN} = \pm 2.0V, \ V_{SB} = -2.0V, \ V_{ST} = +2.0V, \ f_{CLK} = 10 MHz, \ 50\% \ clock \ duty \ cycle, \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted.)$

| PARAMETER                                   | CONDITIONS                        | TEST<br>LEVEL | MIN | ТҮР        | МАХ | UNITS          |

|---------------------------------------------|-----------------------------------|---------------|-----|------------|-----|----------------|

| Resolution                                  |                                   |               | 12  |            |     | Bits           |

| <b>DC ACCURACY</b> ( $T_A = +25^{\circ}C$ ) |                                   |               |     |            |     |                |

| Integral Nonlinearity                       | ± full scale                      | IV            |     | ±2.0       |     | LSB            |

| Differential Nonlinearity                   | 250kHz sample rate                | IV            |     | ±0.8       |     | LSB            |

| No Missing Codes                            |                                   | I             |     | Guaranteed |     |                |

| ANALOG INPUT                                |                                   |               |     |            |     |                |

| Input Voltage Range                         |                                   | VI            |     | ±2.0       |     | V              |

| Input Bias Current                          | $T_A = +25^{\circ}C$              | I             |     | 30         | 60  | μA             |

| Input Resistance                            | $V_{IN} = 0V, T_A = +25^{\circ}C$ | I             | 100 | 300        |     | kΩ             |

| Input Capacitance                           |                                   | V             |     | 5          |     | pF             |

| Input Bandwidth                             | 3dB small signal                  | V             |     | 120        |     | MHz            |

| Positive Full-Scale Error                   |                                   | V             |     | ±5.0       |     | LSB            |

| Negative Full-Scale Error                   |                                   | V             |     | ±5.0       |     | LSB            |

| REFERENCE INPUT                             | L.                                |               |     |            |     |                |

| Reference Ladder Resistance                 |                                   | VI            | 500 | 800        |     | Ω              |

| Reference Ladder Tempco                     |                                   | V             |     | 0.8        |     | Ω/°C           |

| TIMING CHARACTERISTICS                      |                                   |               |     |            |     |                |

| Maximum Conversion Rate                     |                                   | VI            | 10  |            |     | MHz            |

| Overvoltage Recovery Time                   |                                   | V             |     | 20         |     | ns             |

| Pipeline Delay (Latency)                    |                                   | VI            |     |            | 1   | Clock<br>Cycle |

| Output Delay                                | $T_A = +25^{\circ}C$              | V             |     | 14         | 18  | ns             |

| Aperture Delay Time                         | $T_A = +25^{\circ}C$              | V             |     | 1          |     | ns             |

| Aperture Jitter Time                        | $T_A = +25^{\circ}C$              | V             |     | 5          |     | ps-RMS         |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>CC</sub> = +5.0V, V<sub>EE</sub> = -5.2V, DV<sub>CC</sub> = +5.0V, V<sub>IN</sub> =  $\pm 2.0V$ , V<sub>SB</sub> = -2.0V, V<sub>ST</sub> = +2.0V, f<sub>CLK</sub> = 10MHz, 50% clock duty cycle, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| PARAMETER                      | CONDITIONS                                           |                              | TEST<br>LEVEL | MIN | ТҮР  | MAX | UNITS  |

|--------------------------------|------------------------------------------------------|------------------------------|---------------|-----|------|-----|--------|

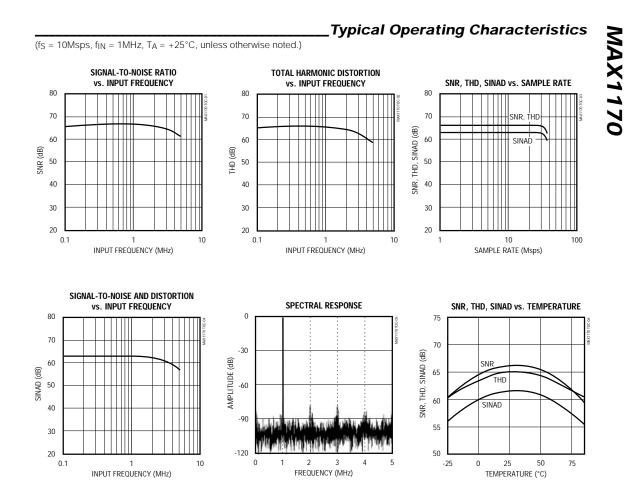

| DYNAMIC PERFORMANCE            |                                                      |                              | 1             |     |      |     | 1      |

|                                | $f_{IN} = 500 \text{kHz}$<br>$f_{IN} = 1 \text{MHz}$ |                              |               |     | 10.2 |     |        |

| Effective Number of Bits       |                                                      |                              |               |     | 10.0 |     | Bits   |

|                                | $f_{IN} = 3.58MHz$                                   |                              |               |     | 9.5  |     | 1      |

|                                | $f_{IN} = 500 \text{kHz}$                            | $T_A = +25^{\circ}C$         | I             | 64  | 67   |     |        |

|                                | IIN = SOOKHZ                                         | $T_A = T_{MIN}$ to $T_{MAX}$ | IV            | 58  | 61   |     | 1      |

| Signal-to-Noise Ratio          | f <sub>IN</sub> = 1MHz                               | $T_A = +25^{\circ}C$         | I             | 64  | 66   |     | dB     |

| (without Harmonics)            | IIN = IIVITZ                                         | $T_A = T_{MIN}$ to $T_{MAX}$ | IV            | 58  | 60   |     |        |

|                                | $f_{IN} = 3.58MHz$                                   | $T_A = +25^{\circ}C$         | I             | 62  | 64   |     | 1      |

|                                | IIN = 3.30IVITZ                                      | TA = TMIN to TMAX            | IV            | 58  | 60   |     | 1      |

|                                | for EOOkU IT                                         | $T_A = +25^{\circ}C$         | I             | 63  | 66   |     |        |

|                                | $f_{IN} = 500 kHz$                                   | $T_A = T_{MIN}$ to $T_{MAX}$ | IV            | 59  | 62   |     | 1      |

|                                | 6 4141                                               | $T_A = +25^{\circ}C$         | I             | 63  | 65   |     |        |

| Harmonic Distortion            | f <sub>IN</sub> = 1MHz                               | TA = TMIN to TMAX            | IV            | 59  | 61   |     | dB     |

|                                | £ 2.50MU                                             | $T_A = +25^{\circ}C$         | I             | 59  | 61   |     | 1      |

|                                | $f_{IN} = 3.58MHz$                                   | $T_A = T_{MIN}$ to $T_{MAX}$ | IV            | 57  | 59   |     | 1      |

|                                | 6 500111                                             | $T_A = +25^{\circ}C$         | I             | 60  | 63   |     |        |

|                                | $f_{IN} = 500 kHz$                                   | TA = TMIN to TMAX            | IV            | 55  | 58   |     | dB     |

|                                | f., 114117                                           | $T_A = +25^{\circ}C$         | I             | 60  | 62   |     |        |

| Signal-to-Noise and Distortion | f <sub>IN</sub> = 1MHz                               | $T_A = T_{MIN}$ to $T_{MAX}$ | IV            | 55  | 57   |     |        |

|                                | 6 0 501411                                           | $T_A = +25^{\circ}C$         | I             | 57  | 59   |     |        |

|                                | $f_{IN} = 3.58MHz$ T                                 | TA = TMIN to TMAX            | IV            | 54  | 56   |     |        |

| Spurious-Free Dynamic Range    | f <sub>IN</sub> = 1MHz, T <sub>A</sub> =             |                              | V             |     | 74   |     | dBc    |

| Differential Phase             | $f_{IN} = 3.58MHz and T_A = +25°C$                   | d 4.35MHz,                   | V             |     | 0.2  |     | Degree |

| Differential Gain              | $f_{IN} = 3.58MHz and T_A = +25°C$                   | d 4.35MHz,                   | V             |     | 0.7  |     | %      |

| DIGITAL INPUTS                 |                                                      |                              |               |     |      |     |        |

| Logic "1" Voltage              |                                                      |                              | V             | 2.4 |      | 4.0 | V      |

| Logic "0" Voltage              |                                                      |                              | V             |     |      | 0.8 | V      |

| Maximum Input Current Low      | $T_A = +25^{\circ}C$                                 |                              | Ι             | 0   | 5    | 20  | μΑ     |

| Maximum Input Current High     | $T_A = +25^{\circ}C$                                 |                              | I             | 0   | 5    | 20  | μΑ     |

| Pulse Width Low (CLK)          |                                                      |                              | IV            | 30  |      |     | ns     |

| Pulse Width High (CLK)         |                                                      |                              | IV            | 30  |      | 300 | ns     |

| DIGITAL OUTPUTS                | •                                                    |                              |               |     |      |     | •      |

| Logic "1" Voltage              | $T_A = +25^{\circ}C$                                 |                              | Ι             | 2.4 |      |     | V      |

| Logic "0" Voltage              | $T_A = +25^{\circ}C$                                 |                              | I             |     |      | 0.6 | V      |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +5.0V, V_{EE} = -5.2V, DV_{CC} = +5.0V, V_{IN} = \pm 2.0V, V_{SB} = -2.0V, V_{ST} = +2.0V, f_{CLK} = 10MHz, 50\% clock duty cycle, T_A = T_{MIN} to T_{MAX}, unless otherwise noted.)$

| PARAMETER              | CONDITIONS                      | TEST<br>LEVEL | MIN   | ТҮР  | MAX   | UNITS |

|------------------------|---------------------------------|---------------|-------|------|-------|-------|

| POWER-SUPPLY REQUIRE   | MENTS                           |               |       |      |       |       |

|                        | V <sub>CC</sub>                 | IV            | 4.75  | 5.0  | 5.25  |       |

| Voltages               | DVcc                            | IV            | 4.75  | 5.0  | 5.25  | V     |

|                        | -V <sub>EE</sub>                | IV            | -4.95 | -5.2 | -5.45 | 1     |

|                        | $I_{CC}, T_A = +25^{\circ}C$    | I             |       | 135  | 150   |       |

| Currents               | DICC, TA = TMIN to TMAX         | IV            |       | 40   | 55    | mA    |

|                        | $-I_{EE}, T_{A} = +25^{\circ}C$ | I             |       | 45   | 70    | 1     |

| Power Dissipation      |                                 | VI            |       | 1.1  | 1.3   | W     |

| Power-Supply Rejection | 5V ±0.25V, -5.2V ±0.25V         | V             |       | 1.0  |       | LSB   |

Note 1: Typical thermal impedances (unsoldered, in free air):

32 Ceramic SB:  $\theta j_A = 50^{\circ}$ C/W

44 CERQUAD:  $\theta j_A = 78^{\circ}$ C/W,  $\theta j_A$  at 1m/s airflow = 58°C/W,  $\theta j_C = 3.3^{\circ}$ C/W

Use forced-air cooling or heatsinking to maintain  $T_j \leq 150^{\circ}$ C.

| TEST LEVEL CODES                                                                               | TEST LEVEL | TEST PROCEDURE                                                                                      |

|------------------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------|

| All electrical characteristics are subject to the                                              | I          | 100% production tested at the specified temperature.                                                |

| following conditions:<br>All parameters having min/max specifications                          | П          | 100% production tested at $T_A = +25^{\circ}$ C, and sample tested at the specified temperatures.   |

| are guaranteed. The Test Level column indi-<br>cates the specific device testing actually per- |            | QA sample tested only at the specified temperatures.                                                |

| formed during production and Quality<br>Assurance inspection. Any blank section in the         | IV         | Parameter is guaranteed (but not tested) by design and charac-<br>terization data.                  |

| data column indicates that the specification is not tested at the specified condition.         | V          | Parameter is a typical value for information purposes only.                                         |

| Unless otherwise noted, all tests are pulsed; therefore, $T_j = T_C = T_A$ .                   | VI         | 100% production tested at $T_A = +25$ °C. Parameter is guaranteed over specified temperature range. |

**MAX1170**

| I          | PIN                                                  | NAME             | FUNCTION                             |

|------------|------------------------------------------------------|------------------|--------------------------------------|

| Ceramic SB | CERQUAD                                              | NAME             | FUNCTION                             |

| 1, 15      | 14, 41                                               | DGND             | Digital Ground                       |

| 2–13       | 43, 44, 1–10                                         | D0-D11           | TTL Outputs (D0 = LSB)               |

| 14         | 13                                                   | D12              | TTL Output Overrange Bit             |

| 16, 32     | 15, 40                                               | DV <sub>CC</sub> | Digital +5.0V Supply (TTL Outputs)   |

| 17         | 17                                                   | CLK              | TTL Clock Input                      |

| 18, 31     | 19, 39                                               | V <sub>EE</sub>  | -5.2V Supply                         |

| 19, 30     | 21, 37                                               | AGND             | Analog Ground                        |

| 20, 29     | 23, 35                                               | V <sub>CC</sub>  | +5.0V Supply                         |

| 21         | 25                                                   | VFT              | Force for Top of Reference Ladder    |

| 22         | 26                                                   | VST              | Sense for Top of Reference Ladder    |

| 23         | 27                                                   | VRT3             | Voltage Reference Tap 3              |

| 24         | 28                                                   | VIN              | Analog Input, ±2.0V typical          |

| 25         | 29                                                   | VRT2             | Voltage Reference Tap 2              |

| 26         | 30                                                   | VRT1             | Voltage Reference Tap 1              |

| 27         | 31                                                   | VSB              | Sense for Bottom of Reference Ladder |

| 28         | 32                                                   | VFB              | Force for Bottom of Reference Ladder |

| _          | 11, 12, 16, 18,<br>20, 22, 24, 33,<br>34, 36, 38, 42 | N.C.             | No Connection                        |

Pin Description

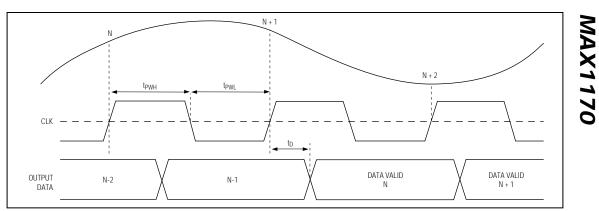

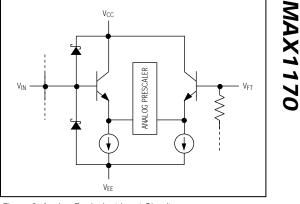

Figure 1a. Timing Diagram

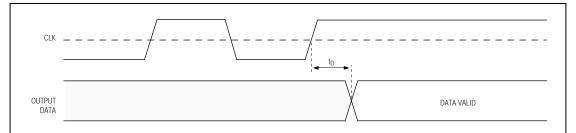

Figure 1b. Single-Event Clock

#### **Table 1. Timing Parameters**

| PARAMETER | DESCRIPTION                  | MIN | TYP | MAX | UNITS |

|-----------|------------------------------|-----|-----|-----|-------|

| tD        | CLK to Data Valid Prop Delay |     | 14  | 18  | ns    |

| tpwh      | CLK High Pulse Width         | 30  |     | 300 | ns    |

| tpwl      | CLK Low Pulse Width          | 30  |     |     | ns    |

#### \_Detailed Description

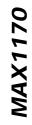

The MAX1170 requires few external components to achieve the stated operation and performance. Figure 2 shows the typical interface requirements when using the MAX1170 in normal circuit operation. The following section provides a description of the pin functions and outlines critical performance criteria for achieving the optimal device performance.

#### Power Supplies and Grounding

The MAX1170 requires -5.2V and +5V analog supply voltages. The +5V supply is common to analog V<sub>CC</sub> and digital DV<sub>CC</sub>. A ferrite bead in series with each supply line reduces the transient noise injected into the analog V<sub>CC</sub>. These beads should be connected as close to the device as possible. The connection between the beads and the MAX1170 should not be shared with any other device. Bypass each power-supply pin as close to the device as possible. Use 0.1µF for V<sub>CC</sub> and V<sub>CC</sub>, and 0.01µF for DV<sub>CC</sub> (chip capacitors are preferred).

Figure 2. Typical Interface Circuit

**M**/IXI/M

AGND and DGND are the two grounds available on the MAX1170. These two internal grounds are isolated on the device. The use of ground planes is recommended to achieve optimum device performance. DGND is needed for the  $DV_{CC}$  return path (40mA typical) and for the return path for all digital output logic interfaces. AGND and DGND should be separated from each other and connected together only at the device through a ferrite bead.

A Schottky or hot carrier diode connected between AGND and V<sub>EE</sub> is required. The use of separate power supplies between V<sub>CC</sub> and DV<sub>CC</sub> is not recommended due to potential power-supply sequencing latchup conditions. Use of the recommended interface circuit shown in Figure 2 will provide optimum device performance for the MAX1170.

#### Voltage Reference

The MAX1170 requires the use of two voltage references: V<sub>FT</sub> and V<sub>FB</sub>. V<sub>FT</sub> is the force for the top of the voltage reference ladder (+2.5V typical), V<sub>FB</sub> (-2.5V typical) is the force for the bottom of the voltage reference ladder. Both voltages are applied across an internal reference ladder resistance of 800 $\Omega$ . The +2.5V voltage source for reference V<sub>FT</sub> must be current limited to 20mA maximum if a different driving circuit is used in place of the recommended reference circuit shown in Figures 2 and 3.

In addition, there are five reference ladder taps (VST, VRT1, VRT2, VRT3, and VSB). VST is the sense for the top of the reference ladder (+2.0V), VRT2 is the midpoint of the ladder (0.0V typical), and VSB is the sense for the bottom of the reference ladder (-2.0V). VRT1 and VRT3 are guarter-point ladder taps (+1.0V and -1.0V typical, respectively). The voltages seen at VST and VSB are the true full-scale input voltages of the device when VFT and VFB are driven to the recommended voltages (+2.5V and -2.5V typical, respectively). VST and VSB can be used to monitor the actual full-scale input voltage of the device. VRT1, VRT2, and VRT3 should not be driven to the expected ideal values, as is commonly done with standard flash converters. A decoupling capacitor of 0.01µF connected to AGND from each tap is recommended to minimize high-frequency noise injection.

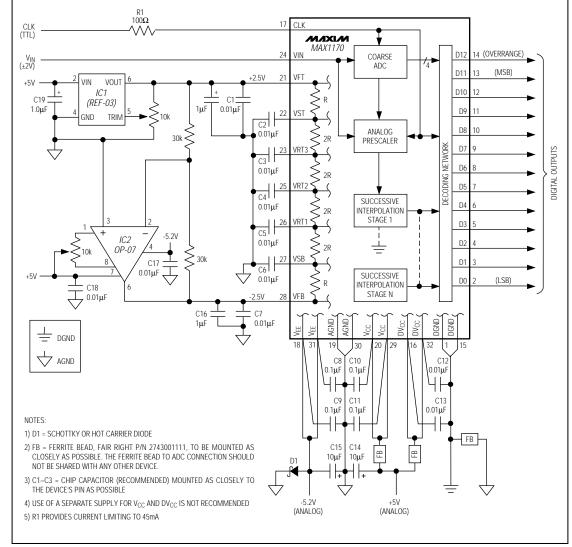

The analog input range will scale proportionally with respect to the reference voltage if a different input

Figure 3. Analog Equivalent Input Circuit

range is required. The maximum scaling factor for device operation is  $\pm 20\%$  of the recommended reference voltages of V<sub>FT</sub> and V<sub>FB</sub>. However, because the MAX1170 is laser trimmed to optimize performance with  $\pm 2.5V$  references, its accuracy will degrade if operated beyond a  $\pm 2\%$  range.

An example of a recommended reference driver circuit is shown in Figure 2. IC1 is REF-03, the +2.5V reference with a tolerance of 0.6% or  $\pm$ 0.015V. The 10k $\Omega$  potentiometer supports an adjustable range of 150mV. IC2 is recommended to be an OP-07 or equivalent device. R2 and R3 must be matched to within 0.1% with good TC tracking to maintain a 0.3LSB matching between V<sub>FT</sub> and V<sub>FB</sub>. If 0.1% matching is not met, then potentiometer R4 can be used to adjust the V<sub>FB</sub> voltage to the desired level. Adjust R1 and R4 such that V<sub>ST</sub> and V<sub>SB</sub> are exactly +2.0V and -2.0V, respectively.

The following errors are defined:

+FS error = top of ladder offset voltage

=

$$\Delta$$

(+FS - V<sub>ST</sub>)

FS error = bottom of ladder offset voltage

=

$$\Delta$$

(-FS - VsB)

Where the +FS (full scale) input voltage is defined as the output 1LSB above the transition of 1-10 and 1-11, and the -FS input voltage is defined as the output 1LSB below the transition of 0-00 and 0-01.

#### **MIXI/N**

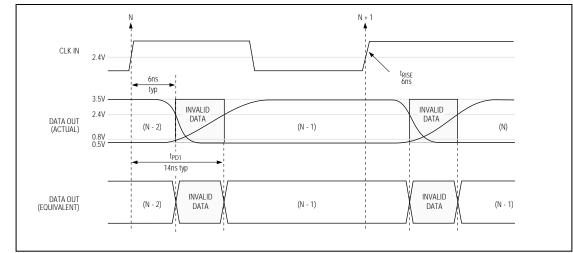

Figure 4. Digital Output Characteristics

#### Analog Input

$V_{IN}$  is the analog input. The full-scale input range will be 80% of the reference voltage or  $\pm 2V$  with  $V_{FB}$  = -2.5V and  $V_{FT}$  = +2.5V.

The drive requirements for the analog inputs are minimal compared to those of conventional flash converters, due to the MAX1170's extremely low 5pF input capacitance and high 300k $\Omega$  input impedance. For example, for an input signal of ±2Vp-p with an input frequency of 10MHz, the peak output current required for the driving circuit is only 628µA.

#### Clock Input

The MAX1170 is driven from a single-ended TTL input (CLK). For optimal noise performance, the clock input slew rate should be a minimum of 6ns. Because of this, the use of fast logic is recommended. The clock input duty cycle should be 50% where possible, but performance will not be degraded if kept within the range of 40% to 60%. However, in any case, the clock pulse width (tPWH) must be kept at 300ns maximum to ensure proper operation of the internal track/hold amplifier (Figure 1a). The analog input signal is latched on the rising edge of the CLK.

The clock input must be driven from fast TTL logic ( $V_{IH} \le 4.5V$ , t<sub>RISE</sub> < 6ns). In the event the clock is driven from a high current source, use a 100 $\Omega$  resistor (R1, Figure 2) in series to current limit to approximately 45mA.

#### Digital Outputs

The format of the output data (D0-D11) is straight binary (Table 2). The outputs are latched on the rising edge of CLK with a typical propagation delay of 14ns. There is a one clock cycle latency between CLK and the valid output data (Figure 1a).

The digital outputs' rise times and fall times are not symmetrical. The rise time's typical propagation delay is 14ns, and the typical fall time is 6ns (Figure 4). The nonsymmetrical rise and fall times create approximately 8ns of invalid data.

#### **Table 2. Output Data Information**

| ANALOG<br>INPUT  | OVERRANGE<br>D10 | OUTPUT CODE<br>D9–D0 |

|------------------|------------------|----------------------|

| > +2.0V + 1/2LSB | 1                | 11 1111 1111         |

| +2.0V - 1LSB     | 0                | 11 1111 111Ø         |

| 0.0V             | 0                | 00 0000 0000         |

| -2.0V + 1LSB     | 0                | 00 0000 000Ø         |

| < -2.0V          | 0                | 00 0000 0000         |

(Ø indicates the flickering bit between logic 0 and 1).

#### **Overrange Output**

The overrange output (D12) is an indication that the analog input signal has exceeded the full-scale input voltage by 1LSB. When this condition occurs, the outputs will switch to logic 1s. All other data outputs are unaffected by this operation. This feature makes it possible to include the MAX1170 in higher resolution systems.

#### **Evaluation Board**

The MAX1170 evaluation kit (EV kit) is available to aid designers in demonstrating the full performance of the MAX1172 (or of the MAX1170/MAX1171). This board includes a reference circuit, clock driver circuit, output data latches, and on-board reconstruction of the digital data. A separate EV kit manual describing the operation of this board is available. Contact the factory for price and availability.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 1996 Maxim Integrated Products

12

S Printed USA

**MAXIM** is a registered trademark of Maxim Integrated Products.