MAD 4868A

## Contents

| Page | Section  | Title                                                        |

|------|----------|--------------------------------------------------------------|

| 3    | 1.       | Introduction                                                 |

| 3    | 1.1.     | Features                                                     |

| 3    | 1.2.     | Interfaces                                                   |

| 3    | 1.3.     | Miscellaneous                                                |

| 5    | 2.       | Functional Description                                       |

| 5    | 2.1.     | Block Diagram                                                |

| 5    | 2.2.     | I <sup>2</sup> S Bus Interface                               |

| 6    | 2.2.1.   | Serial Mode - One Data Line                                  |

| 6    | 2.2.2.   | Parallel Mode - Four Data Lines                              |

| 7    | 2.3.     | Delay Line                                                   |

| 7    | 2.4.     | Word Width                                                   |

| 7    | 2.5.     | Output Data Mute                                             |

| 7    | 2.6.     | Reset                                                        |

| 7    | 2.7.     | RAM Clear                                                    |

| 8    | 3.       | Control Interface                                            |

| 8    | 3.1.     | I <sup>2</sup> C Bus Interface                               |

| 9    | 3.1.1.   | Protocol Description                                         |

| 9    | 3.1.2.   | Start-Up Sequence: Power-Up and I <sup>2</sup> C-Controlling |

| 9    | 3.2.     | Description of User Interface                                |

| 12   | 4.       | Specifications                                               |

| 12   | 4.1.     | Outline Dimensions                                           |

| 13   | 4.2.     | Pin Connections and Short Descriptions                       |

| 13   | 4.3.     | Pin Descriptions                                             |

| 14   | 4.4.     | Pin Configuration                                            |

| 14   | 4.5.     | Pin Circuits                                                 |

| 15   | 4.6.     | Electrical Characteristics                                   |

| 15   | 4.6.1.   | Absolute Maximum Ratings                                     |

| 16   | 4.6.2.   | Recommended Operating Conditions                             |

| 16   | 4.6.2.1. | General Recommended Operating Conditions                     |

| 17   | 4.6.3.   | Characteristics                                              |

| 17   | 4.6.3.1. | General Characteristics                                      |

| 17   | 4.6.3.2. | Digital Inputs, Digital Outputs                              |

| 17   | 4.6.3.3. | Reset Input and Power-Up                                     |

| 18   | 4.6.3.4. | I <sup>2</sup> C-Bus Characteristics                         |

| 19   | 4.6.3.5. | I <sup>2</sup> S-Bus Characteristics                         |

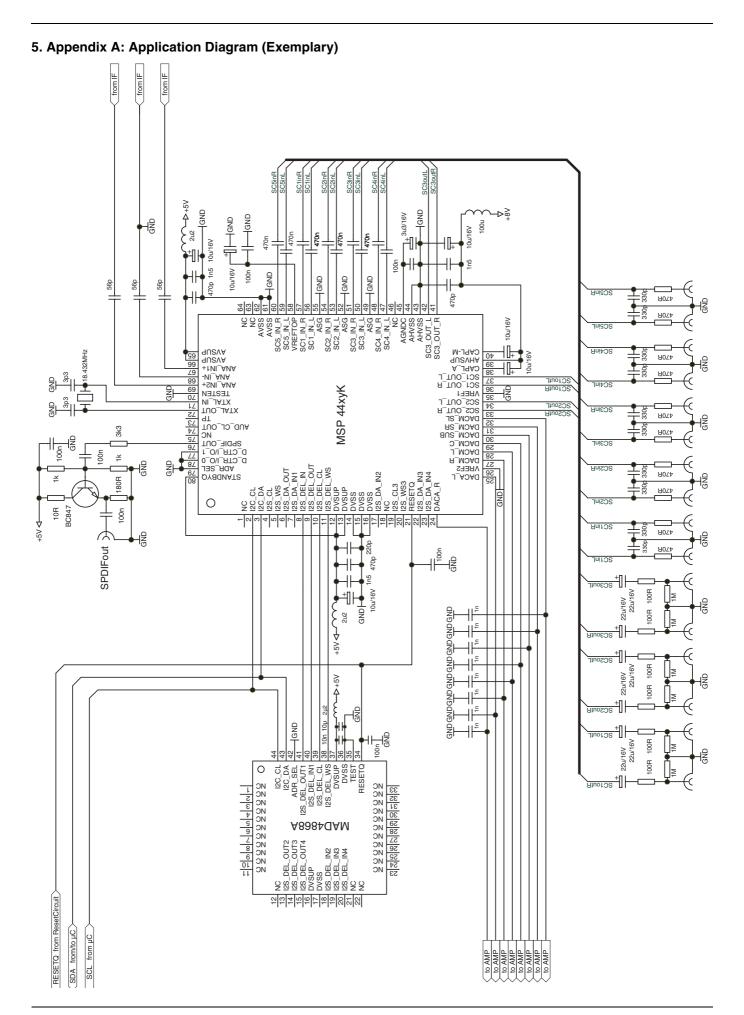

| 22   | 5.       | Appendix A: Application Diagram (Exemplary)                  |

| 24   | 6.       | Data Sheet History                                           |

MAD 4868A

#### **Micronas Audio Delay**

#### 1. Introduction

The Micronas Audio Delay IC MAD 4868A acts as a delay line for TV audio and consumer audio applications. The IC is designed for synchronizing audio and video signals ensuring "Lip Sync" by delaying the audio signal with the same amount of time as the video signal is delayed in a TV's video processing.

For TV designs, independent signals for loudspeakers, headphones, and line-out or S/PDIF out must be provided, resulting in the need to delay six independent audio channels.

Especially modern flat panel TVs (LCD- or plasma-TVs) require "Lip Sync" because of their video deinterlacing, processing, scaling, and pixel-oriented display.

In battery-operated "wireless TVs" using digital transmission, the compression/decompression also may delay video more than audio. Therefore, additional audio delay is necessary.

Consumer audio applications such as A/V-Receivers or HTiB can also use MAD 4868A to offer "Lip Sync" as an additional feature to delay audio according to the video delay appearing in the TV, beamer, or monitor used in a home cinema setup.

The MAD 4868A is equipped with all interfaces, as well as embedded RAM. This makes the IC easy to use and avoids RAM availability and pricing problems.

In its PMQFP44-1 package with 0.8 mm pitch, the MAD 4868A requires only little PCB space but is suitable for wave soldering and reflow soldering.

#### 1.1. Features

- 32 k audio samples RAM:

Total delay time of 680 ms at 48 kHz or

1020 ms at 32 kHz sampling rate

- 32/18-bit word width:

32-bit High-Resolution mode or

18-bit Standard mode

- Sampling rates from 32 kHz to 48 kHz for serial 8-channel mode are supported

- Sampling rates from 4 kHz to 192 kHz for parallel 2-channel mode are supported

- Memory allocation:

MAD 4868A's memory can be allocated for 1...8

audio channels. Delay time can be programmed for each channel individually.

#### 1.2. Interfaces

- 8-channel Micronas I<sup>2</sup>S input and output: In combination with Micronas ICs (serial mode) (e.g. MSP 44/46xyK, MAS 35xyH), eight audio channels can be routed through MAD 4868A by using four lines only.

- 4×2-channel standard I<sup>2</sup>S inputs and outputs (parallel mode) allow routing eight audio channels with sampling rates of 4...192 kHz through MAD 4868A

- I<sup>2</sup>C control for delay time programming

- Address select to set one out of two available I<sup>2</sup>C addresses

#### 1.3. Miscellaneous

- No crystal required:

The MAD 4868A derives all internal clocks from the I<sup>2</sup>S clock.

- Very few external components required

- 5 V or 3.3 V single supply voltage

- Very low power consumption

- 5 kHz to 192 kHz sampling rates

- Cascadable, extendable:

Two MAD 4868As can be cascaded to extend the delay time, either in 8-channel (serial) mode using one data line or in 2-channel (parallel) mode using up to four data lines.

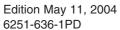

Fig. 1-1: Block diagram of the MAD 4868A

#### 2. Functional Description

#### 2.1. Block Diagram

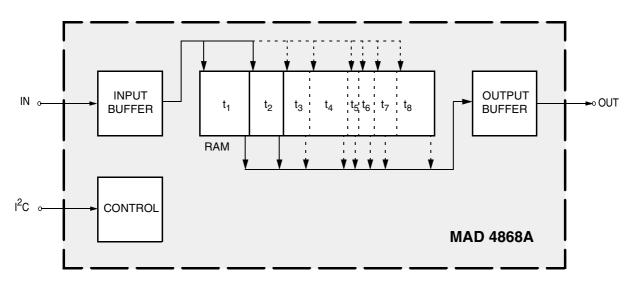

In Fig. 2–1, a simplified block diagram of the IC is given. Between 1 and 8 channels can be delayed individually by a programmable number of samples  $n_{\chi}$ . The delay RAM offers, depending on the accumulated adjusted delay, a word width of 32 or 18 bits.

The accumulated delay must not exceed 7FF0 $_{hex}$  (32752 $_{dec}$ ) samples (i.e. 682 ms @ 48 kHz F $_{s}$ ). As the bit clock (I2S\_DEL\_CL) is limited to 12.288 MHz and the used I<sup>2</sup>S bus format has a fixed word length of 32 bit, the maximum sample rate f $_{s}$  is 192 kHz in parallel mode (2-channels per data line) and 48 kHz in serial mode (8-channels on I2S DEL IN1/OUT1).

## 2.2. I<sup>2</sup>S Bus Interface

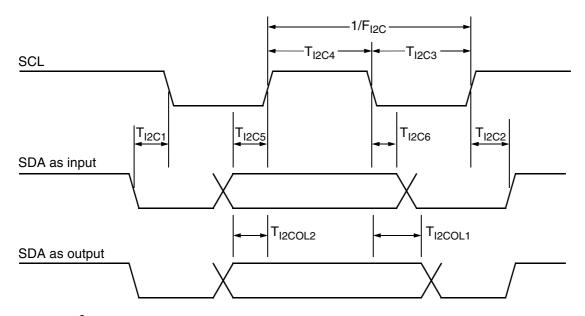

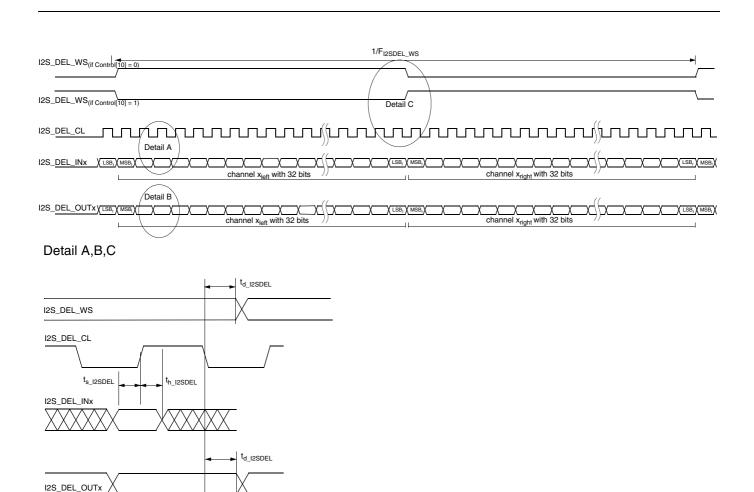

The MAD 4868A has four I<sup>2</sup>S data input lines and four I<sup>2</sup>S data output lines which together with I2S\_DEL\_WS and I2S\_DEL\_CL form one I<sup>2</sup>S bus interface for various sample rates in serial (8-channel) or parallel (2-channel) mode. The I2S\_DEL\_CL, I2S\_DEL\_WS, and I2S\_DEL\_IN1...4 are inputs to the MAD 4868A (tristate) while I2S\_DEL\_OUT1...4 are outputs. Bit[1:0] of the CONTROL register set the output driver active or tristate and its strength to weak or strong (see Table 3–3 on page 10). The interface works only in synchronous slave mode and with a fixed wordlength of each audio sample of 32 bits. Two different operational modes can be adjusted as described in the following sections.

Fig. 2-1: Simplified block diagram of the MAD 4868A

#### 2.2.1. Serial Mode - One Data Line

The MAD 4868A is capable of receiving signals with up to eight audio samples in a fixed 8-channel I<sup>2</sup>S format on one data line (serial mode). The interface consists of the pins:

- I2S\_DEL\_IN1:

I<sup>2</sup>S data input, with 8 audio channels per

I2S\_DEL\_WS cycle and 32 bit per audio sample

- I2S\_DEL\_OUT1:

I<sup>2</sup>S data output, with 8 audio channels per

I2S\_DEL\_WS cycle and 32 bit per audio sample

- I2S\_DEL\_CL:

I<sup>2</sup>S clock

- I2S\_DEL\_WS:

I<sup>2</sup>S word strobe signal defines the frame start at the sample rate.

As the bit clock must not exceed 12.288 MHz, the maximum sample rate is limited to 48 kHz when the MAD 4868A is operated in this mode. This mode is used for the connection to the Delay Line Interface of the MSP 44/46xyK. In serial mode, the number of audio channels must be even and less or equal eight. A timing diagram is shown in Fig. 4–8 on page 21. In this mode, it is possible to mute each output channel individually by means of the CONTROL register bit[2:9.]

Note: DVSUP2 drives the pins DA\_IN\_2...4 and DA\_OUT\_2...4. To avoid radiation from not connected pins, it is recommended not to connect DVSUP2 when MAD 4868A is to be used in Serial Mode.

#### 2.2.2. Parallel Mode - Four Data Lines

The MAD 4868A is capable of receiving stereo signals on up to four I<sup>2</sup>S data lines in Parallel Mode with a total of up to eight audio channels. The interface consists of the pins:

- I2S\_DEL\_IN1, I2S\_DEL\_IN2, I2S\_DEL\_IN3,

I2S\_DEL\_IN4:

I<sup>2</sup>S data input with 2 audio channels per

I2S\_DEL\_WS cycle and 32 bit per audio sample

- I2S\_DEL\_OUT1, I2S\_DEL\_OUT2,

I2S\_DEL\_OUT3, I2S\_DEL\_OUT4:

I<sup>2</sup>S data output with 2 audio channels per

I2S DEL WS cycle and 32 bit per audio sample

- I2S\_DEL\_CL:

I<sup>2</sup>S clock

- I2S\_DEL\_WS:

I<sup>2</sup>S word strobe signal defines the left and right sample at the sample rate.

As the bit clock must not exceed 12.288 MHz, the sample rate can be a maximum of 192 kHz when MAD 4868A is operated in this mode. This mode is used for connection to e.g. the I<sup>2</sup>S interface of the Micronas MSP 34/44xyG or any other audio DSP.

#### 2.3. Delay Line

The MAD 4868A has a delay line of 32k Words of RAM built in. The RAM can be split up into portions of different length to delay between 1 and 8 channels of audio. This makes the MAD 4868A very flexible. All channels can be delayed individually. The maximum amount of adjusted delay must not exceed 7FF0<sub>hex</sub> (32752<sub>dec</sub>) samples.

Equipped with a pointer unit and programmed with variable pointer offsets for the delay channels 1 to 8, the programming of the individual delay times is realized by means of its own control register for each delay channel (see Table 3–3 on page 10).

The delay time depends on the used sample frequency on the  $I^2S$ -bus. Since, not the delay time, but the number of delayed samples is programmed, the corresponding number of samples is calculated using the follwing formula:

$$n_r = (t_{ms}(x) \times f_s) - 1$$

$n_x$  = number of samples  $t_{ms}$  = time in milliseconds  $f_s$  = sample rate

In the pointer unit, the offsets are used as increments for the address pointer to receive the correct RAM address of the delayed sound samples.

Note: Reprogramming the delay length of a channel affects the output of the channels with higher numbers. Due to the "linked list" principle of the RAM organisation, the upper channels read from "wrong memory" until it is filled up with new audio samples. Therefore, it is recommended to mute the output of the delay line for the max programmed delay time of all channels.

#### 2.4. Word Width

The audio sample word width inside the RAM of the MAD 4868A depends on the adjusted number of samples for the delay. MAD 4868A automatically switches the word width to 32 bit if the total delay length is below 3FF8 $_{\rm hex}$  (16376 $_{\rm dec}$ ) i.e. half of the maximum length. Otherwise, the delay line is 18 bit wide. By means of bit[14] of the CONTROL register, a read out value is available in parallel mode which indicates the internally adjusted word width.

#### 2.5. Output Data Mute

The output data channel 1-8 can be muted by means of the CONTROL register bit[2:9]. In serial mode, each output data channel can be muted individually, while in parallel mode, all channels 1-8 have to be adjusted individually to the same value. It is recommended to mute the output data channels during the power-up sequence of the MAD 4868A, as well as during readjustment of the delay time during normal operation. To avoid any audible disturbances, the minimum mute time must be at least the maximum programmed delay time of all channels.

#### 2.6. Reset

The Reset is active low and resets the I<sup>2</sup>S and I<sup>2</sup>C-interfaces of the MAD 4868A. Since there is no RAM clear facility, the output of the MAD 4868A after reset is random, as long as no valid samples have been inserted and passed the delay line (e.g. after Reset, enable the I<sup>2</sup>S bus output but keep Mute active until the maximum programmed delay time is passed).

#### 2.7. RAM Clear

A RAM Clear can be performed manually. It is recommended to apply a manual RAM Clear after the power-up of the MAD 4868A. Mute the output data channel 1-8, apply a digital zero signal on all used channels. This can be achieved, for example, by selecting an I<sup>2</sup>S input with a prescaler setting to Mute in the MSP 44/46xyK for all used MAD 4868A input channels. The digital zero signal must be applied for at least the maximum programmed delay time of all channels.

#### 3. Control Interface

## 3.1. I<sup>2</sup>C Bus Interface

The MAD 4868A is controlled via its  $I^2C$  bus slave interface.

The IC is selected by transmitting an MAD 4868A device address. In order to allow two MAD 4868A ICs to be connected to a single bus, an address select pin (ADR\_SEL) has been implemented. With ADR\_SEL pulled to high or low, the MAD 4868A responds to different device addresses. A device address pair is defined as a write address and a read address.

**Writing** is done by sending the write device address, followed by the subaddress byte and the data bytes.

**Reading** is done by sending the write device address, followed by the subaddress byte. Without sending a stop condition, reading of the addressed data is completed by sending the device read address and reading two bytes of data.

See Table 3-1 for a list of available device addresses.

See Table 3-2 for a list of available subaddresses.

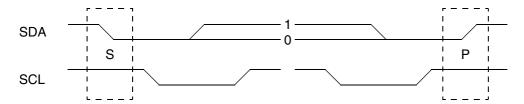

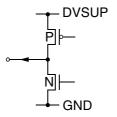

A general timing diagram of the  $I^2C$  bus is shown in Fig. 3–1 on page 9.

Table 3-1: I<sup>2</sup>C Bus Device Addresses

| ADR_SEL                  |                                                | ow<br>d to DVSS) | High<br>(connected to DVSUP) |                   |  |  |

|--------------------------|------------------------------------------------|------------------|------------------------------|-------------------|--|--|

| Mode                     | ode Write Read                                 |                  | Write                        | Read              |  |  |

| MAD 4868A device address | ce address 82 <sub>hex</sub> 83 <sub>hex</sub> |                  | 84 <sub>hex</sub>            | 85 <sub>hex</sub> |  |  |

Table 3–2: I<sup>2</sup>C Bus Subaddresses

| Name      | Binary Value | Hex Value | Mode         | Function                                 |

|-----------|--------------|-----------|--------------|------------------------------------------|

| CONTROL   | 0000 0000    | 00        | Read / Write | Write: Interface control<br>Read: Status |

| CH1_DELAY | 0000 0001    | 01        | Read / Write | delay channel 1                          |

| CH2_DELAY | 0000 0010    | 02        | Read / Write | delay channel 2                          |

| CH3_DELAY | 0000 0011    | 03        | Read / Write | delay channel 3                          |

| CH4_DELAY | 0000 0100    | 04        | Read / Write | delay channel 4                          |

| CH5_DELAY | 0000 0101    | 05        | Read / Write | delay channel 5                          |

| CH6_DELAY | 0000 0110    | 06        | Read / Write | delay channel 6                          |

| CH7_DELAY | 0000 0111    | 07        | Read / Write | delay channel 7                          |

| CH8_DELAY | 0000 1000    | 08        | Read / Write | delay channel 8                          |

#### 3.1.1. Protocol Description

# Write to CONTROL and CHX\_DELAY Registers

| S | write device | Wait | ACK | sub-addr | ACK | data-byte | ACK | data-byte | ACK | Р | Ì |

|---|--------------|------|-----|----------|-----|-----------|-----|-----------|-----|---|---|

|   | address      |      |     |          |     | high      |     | low       |     |   | l |

## Read from CONTROL or CHX\_DELAY Register

| Ī | S | write device | Wait | ACK | sub-addr | ACK | S | read device | Wait | ACK |      | ACK | data-byte | NAK | Р |

|---|---|--------------|------|-----|----------|-----|---|-------------|------|-----|------|-----|-----------|-----|---|

|   |   | address      |      |     |          |     |   | address     |      |     | high |     | low       |     |   |

**Note:**  $S = I^2C$ -Bus Start Condition from master

$P = I^2C$ -Bus Stop Condition from master

ACK = Acknowledge-Bit: LOW on SDA from slave (= MAD, light gray) or master (= controller, dark gray)

NAK = Not Acknowledge-Bit: HIGH on I2C\_DA from master (dark gray) to indicate 'End of Read'

or from MAD indicating internal error state

Wait =  $I^2C$ -Clock line is held low, while the MAD is processing the  $I^2C$  command.

This waiting time is max. 1 ms

Fig. 3–1: I<sup>2</sup>C bus protocol (MSB first; data must be stable while clock is high)

# 3.1.2. Start-Up Sequence: Power-Up and I<sup>2</sup>C-Controlling

After POWER-ON or RESET, the IC is in an inactive state. All registers are in their Reset position (see Table 3–3 on page 10), the Output Driver is set to tristate. The controller has to initialize the CONTROL and CHX\_DELAY registers.

## 3.2. Description of User Interface

Write and read registers are 16 bit wide, whereby the MSB is denoted bit[15]. Transmissions via  $I^2C$  bus have to take place in 16-bit words (two byte transfers, with the most significant byte transferred first). All registers are readable.

Unused parts of the 16-bit write registers must be zero. Addresses not given in this table must not be accessed.

Table 3-3: User Interface

| Sub -<br>Address<br>(hex) | Function                                                | Mode                                                                                                                                                                                                                                                                                                                                                                                          | Reset<br>Value<br>(hex) | Name    |

|---------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------|

| 00 <sub>hex</sub>         | Control                                                 |                                                                                                                                                                                                                                                                                                                                                                                               | 0000 <sub>hex</sub>     | CONTROL |

|                           | bit[15]                                                 | must be ignored                                                                                                                                                                                                                                                                                                                                                                               |                         |         |

|                           | bit[14] <sup>1)</sup>                                   | HighRes Flag (word width of delayed samples) 0 18 bit 1 32 bit (high resolution)                                                                                                                                                                                                                                                                                                              |                         |         |

|                           | bit[13:11]                                              | not used, must be set to 0                                                                                                                                                                                                                                                                                                                                                                    |                         |         |

|                           | bit[10]                                                 | WS_POL (word strobe polarity)  WS_POL = Low-High marks Framestart e.g. MSP 44/46xyK I <sup>2</sup> S-5 Interface, all MSPs 8-channel mode  WS_POL = High-Low marks Framestart e.g. MSP I2S_OUT (2-channel mode)                                                                                                                                                                               |                         |         |

|                           | bit[9] bit[8] bit[7] bit[6] bit[5] bit[4] bit[3] bit[2] | Output Data Mute channel 8 Output Data Mute channel 7 Output Data Mute channel 6 Output Data Mute channel 5 Output Data Mute channel 4 Output Data Mute channel 3 Output Data Mute channel 2 Output Data Mute channel 1 0 muted 1 0 dB Output Data Mute channel 1-8 can be set individually in serial mode, in parallel mode, Output Data Mute channel 1-8 must all be set to the same value. |                         |         |

|                           | bit[1]                                                  | Output Driver Active 0 tristate 1 active                                                                                                                                                                                                                                                                                                                                                      |                         |         |

|                           | bit[0]                                                  | Output Driver Strength 0 weak 1 strong                                                                                                                                                                                                                                                                                                                                                        |                         |         |

|                           | <sup>1)</sup> bit[14] is                                | s read only                                                                                                                                                                                                                                                                                                                                                                                   |                         |         |

Table 3-3: User Interface, continued

| Sub -<br>Address<br>(hex)              | Function                               |                                                                                                                                          |                                                                                                               |                                                                                                     | Mode                                                                                                     | Reset<br>Value<br>(hex) | Name                                                                            |

|----------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------|

| 01 <sub>hex</sub><br>08 <sub>hex</sub> | samples: n <sub>x</sub><br>min delay 0 | of samples:<br>x = 18; $nnumber ofx = 18f_s =32  kHz31 \mu\text{s}1.00  ms1.50  ms3.00  ms1.023  ms2  KWords of3  KWords of4  KWords of$ | = 032752<br>delayed satisfies $f_s$ = 48 kHz 21 $\mu$ s 0.66 ms 1.00 ms 2.00 ms 682 ms RAM acces in total a m | f <sub>s</sub> = $96 \text{ kHz}$ 10 $\mu$ s 0.33 ms 0.50 ms 1.00 ms 341 ms ssible, the Staximum de | f <sub>s</sub> = 192 kHz 5 µs 0.16 ms 0.25 ms 0.50 ms 170 ms SUM(n <sub>1</sub> :n <sub>8</sub> ) lay of | 0000 <sub>hex</sub>     | CH1_DELAY CH2_DELAY CH3_DELAY CH4_DELAY CH5_DELAY CH6_DELAY CH7_DELAY CH8_DELAY |

#### 4. Specifications

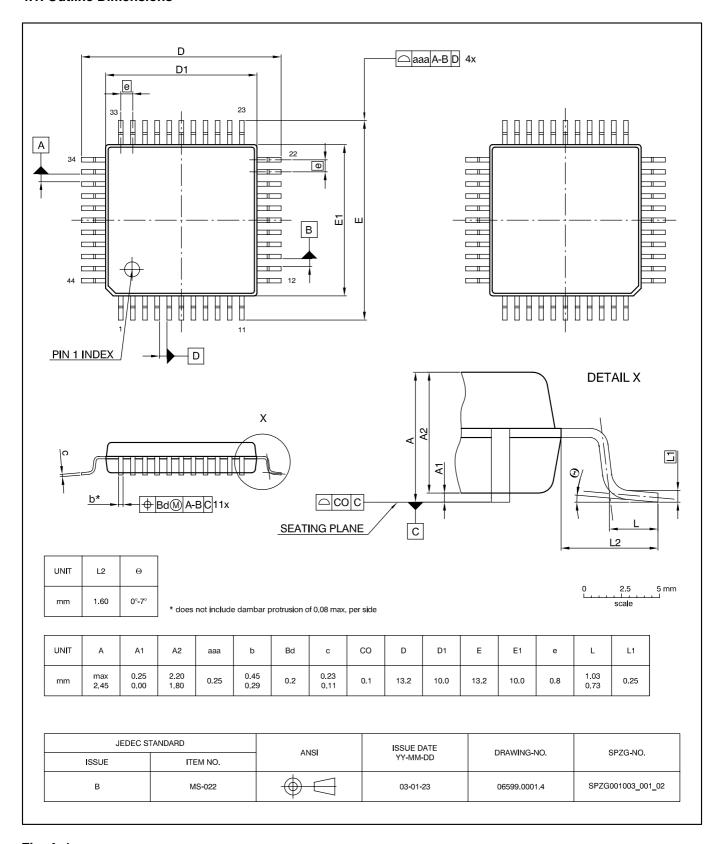

## 4.1. Outline Dimensions

Fig. 4–1:

PMQFP44-1: Plastic Metric Quad Flat Package, 44 leads,  $10 \times 10 \times 2 \text{ mm}^3$

Ordering code: QG

Weight approximately 0.5 g

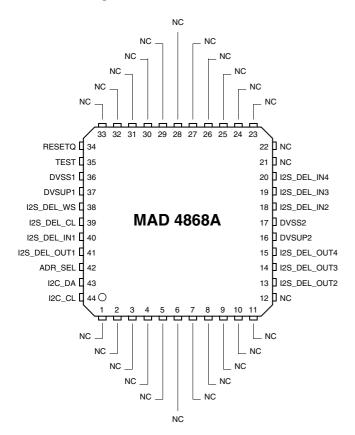

## 4.2. Pin Connections and Short Descriptions

NC = not connected; leave vacant

LV = if not used, leave vacant

OBL = obligatory; connect as described in circuit diagram

| Pin No.<br>PMQFP44-1 | Pin Name     | Туре   | Connection (If not used) | Short Description                                |

|----------------------|--------------|--------|--------------------------|--------------------------------------------------|

| 112                  | NC           |        | LV                       | Not Connected                                    |

| 13                   | I2S_DEL_OUT2 | OUT    | OBL                      | I <sup>2</sup> S data output channel 3 + 4       |

| 14                   | I2S_DEL_OUT3 | OUT    | OBL                      | I <sup>2</sup> S data output channel 5 + 6       |

| 15                   | I2S_DEL_OUT4 | OUT    | OBL                      | I <sup>2</sup> S data output channel 7 + 8       |

| 16                   | DVSUP2       | SUP    | DVSUP                    | Digital Power Supply                             |

| 17                   | DVSS2        | SUP    | DVSS                     | Digital Ground                                   |

| 18                   | I2S_DEL_IN2  | IN     | OBL                      | I <sup>2</sup> S data input channel 3 + 4        |

| 19                   | I2S_DEL_IN3  | IN     | OBL                      | I <sup>2</sup> S data input channel 5 + 6        |

| 20                   | I2S_DEL_IN4  | IN     | OBL                      | I <sup>2</sup> S data input channel 7 + 8        |

| 2133                 | NC           |        | LV                       | Not Connected                                    |

| 34                   | RESETQ       | IN     | OBL                      | Power-On Reset (active low)                      |

| 35                   | TEST         | IN     | DVSS                     | Test pin                                         |

| 36                   | DVSS1        | SUP    | DVSS                     | Digital Ground                                   |

| 37                   | DVSUP1       | SUP    | DVSUP                    | Digital Power Supply                             |

| 38                   | I2S_DEL_WS   | IN     | OBL                      | I <sup>2</sup> S word strobe input               |

| 39                   | I2S_DEL_CL   | IN     | OBL                      | I <sup>2</sup> S clock input                     |

| 40                   | I2S_DEL_IN1  | IN     | OBL                      | I <sup>2</sup> S data input channel 1 + 2 or 18  |

| 41                   | I2S_DEL_OUT1 | OUT    | OBL                      | I <sup>2</sup> S data output channel 1 + 2 or 18 |

| 42                   | ADR_SEL      | IN     | OBL                      | I <sup>2</sup> C bus address select              |

| 43                   | I2C_DA       | IN/OUT | OBL                      | I <sup>2</sup> C Data                            |

| 44                   | I2C_CL       | IN/OUT | OBL                      | I <sup>2</sup> C Clock                           |

## 4.3. Pin Descriptions

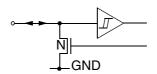

$I2C\_CL - I^2C$  Clock Input/Output (Fig. 4-3) Via this pin, the  $I^2C$ -bus clock signal has to be supplied.

$I2C_DA - I^2C$  Data Input/Output (Fig. 4–3) Via this pin, the  $I^2C$ -bus data is written to or read.

**I2S\_DEL\_WS** – Word Strobe Input (Fig. 4–4) Word strobe line for the I<sup>2</sup>S bus. An external word strobe has to be supplied.

**I2S\_DEL\_CL** – Clock Input (Fig. 4–4) Clock line for the I<sup>2</sup>S bus. An external clock has to be supplied. I2S\_DEL\_IN1, I2S\_DEL\_IN2, I2S\_DEL\_IN3, I2S\_DEL\_IN4 - Data Input (Fig. 4-4) Input of I<sup>2</sup>S data.

**I2S\_DEL\_OUT1, I2S\_DEL\_OUT2, I2S\_DEL\_OUT3, I2S\_DEL\_OUT4** – Data Output (Fig. 4–5) Output of I<sup>2</sup>S bus.

**DVSUP1**, **DVSUP2** – Digital Supply Voltage Power supply must be connected to +5 V or +3.3 V power supply.

**DVSS1**, **DVSS2** – Digital Ground Ground connection.

**TEST** – This pin enables factory test modes. For normal operation, it must be connected to DVSS

**RESETQ** – Reset Input (Fig. 4–4) In the steady state, high level is required. A low level

resets the interfaces of MAD 4868A.

**ADR\_SEL** – I<sup>2</sup>C Bus Address Select (Fig. 4–4) By means of this pin, one of two device addresses can be selected. The pin can be connected to DVSS (I<sup>2</sup>C device addresses 82/83<sub>hex</sub>) or to DVSUP (84/85<sub>hex</sub>).

NC - Pin not connected

#### 4.4. Pin Configuration

Fig. 4-2: PMQFP44-1 package

## 4.5. Pin Circuits

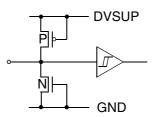

Fig. 4-3: Input/Output Pins: I2C\_CL, I2C\_DA

Fig. 4–4: Input Pins:I2S\_DEL\_CL, I2S\_DEL\_WS, I2S\_DEL\_IN1, I2S\_DEL\_IN2, I2S\_DEL\_IN3, I2S\_DEL\_IN4, ADR\_SEL, RESETQ

Fig. 4–5: Output Pins: I2S\_DEL\_OUT1, I2S\_DEL\_OUT2, I2S\_DEL\_OUT3, I2S\_DEL\_OUT4

Micronas

#### 4.6. Electrical Characteristics

#### **Abbreviations:**

tbd = to be defined vacant = not applicable positive current values mean current flowing into the chip

## 4.6.1. Absolute Maximum Ratings

Stresses beyond those listed in the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these conditions is not implied. Exposure to absolute maximum rating conditions for extended periods will affect device reliability.

This device contains circuitry to protect the inputs and outputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than absolute maximum-rated voltages to this high-impedance circuit.

All voltages listed are referenced to ground ( $V_{SS} = 0 \text{ V}$ ) except where noted.

All GND pins must be connected to a low-resistive ground plane close to the IC.

Table 4-1: Absolute Maximum Ratings

| Symbol                       | Parameter                         | Pin Name          | Limit Values |                        | Unit |

|------------------------------|-----------------------------------|-------------------|--------------|------------------------|------|

|                              |                                   |                   | Min.         | Max.                   |      |

| T <sub>A</sub> <sup>1)</sup> | Ambient Temperature               | _                 | -10          | 70                     | °C   |

| T <sub>C</sub>               | Case Temperature                  | _                 | -10          | 95                     | °C   |

| T <sub>S</sub>               | Storage Temperature               | _                 | -40          | 125                    | °C   |

| P <sub>MAX</sub>             | Maximum Power Dissipation         |                   |              | 860                    | mW   |

| V <sub>SUP</sub>             | Supply Voltage                    | DVSUP1,<br>DVSUP2 | -0.3         | 6.0                    | V    |

| V <sub>Idig</sub>            | Input Voltage, all Digital Inputs |                   | -0.3         | V <sub>SUP2</sub> +0.3 | V    |

| I <sub>Idig</sub>            | Input Current, all Digital Pins   | _                 | -20          | +20                    | mA   |

Measured on standard board according to JESD 51 Standard with maximum power consumption allowed for this package.

## 4.6.2. Recommended Operating Conditions

Functional operation of the device beyond those indicated in the "Recommended Operating Conditions/Characteristics" is not implied and may result in unpredictable behavior, reduce reliability and lifetime of the device.

All voltages listed are referenced to ground ( $V_{SS} = 0 \text{ V}$ ) except where noted.

All GND pins must be connected to a low-resistive ground plane close to the IC.

Do not insert the device into a live socket. Instead, apply power by switching on the external power supply. For power up/down sequences, see the instructions in Section 4.6.3.3. of this document.

## 4.6.2.1. General Recommended Operating Conditions

| Symbol           | Parameter                     | Pin Name          | Limit Values |      |      | Unit |

|------------------|-------------------------------|-------------------|--------------|------|------|------|

|                  |                               |                   | Min.         | Тур. | Max. |      |

| T <sub>A</sub>   | Ambient Operating Temperature | _                 | 0            |      | 70   | °C   |

| T <sub>C</sub>   | Case Operating Temperature    | _                 | 0            |      | 70   | °C   |

| P <sub>MAX</sub> | Maximum Power Dissipation     |                   |              |      | 50   | mW   |

| V <sub>SUP</sub> | Supply Voltage                | DVSUP1,<br>DVSUP2 | 3.0          |      | 5.25 | V    |

## 4.6.3. Characteristics

For Min./Max. values: at  $T_A = 0$  to 70 °C

at  $T_A$  = 0 to 70 °C  $V_{SUP}$  = 3.15 to 3.45 V if  $V_{SUP}$  = 3.3 V  $V_{SUP}$  = 4.75 to 5.25 V if  $V_{SUP}$  = 5 V

For typical values: at  $T_A = 60 \,^{\circ}\text{C}$

at  $T_A = 60$  °C  $V_{SUP} = 3.3$  V or  $V_{SUP} = 5$  V

#### 4.6.3.1. General Characteristics

| Symbol           | Parameter                                 | Pin Name          | Limit Values |                    |      | Unit           | Test Conditions                                                                                                    |

|------------------|-------------------------------------------|-------------------|--------------|--------------------|------|----------------|--------------------------------------------------------------------------------------------------------------------|

|                  |                                           |                   | Min.         | Тур.               | Max. |                |                                                                                                                    |

| Supply           |                                           |                   |              |                    |      |                |                                                                                                                    |

| I <sub>SUP</sub> | Supply Current (active)<br>(VSUP = 5 V)   | DVSUP1,<br>DVSUP2 |              | 2.4<br>2.9<br>0.8  |      | mA<br>mA<br>mA | Serial mode f <sub>s</sub> = 48 kHz<br>Parallel mode f <sub>s</sub> 192 kHz<br>Parallel mode f <sub>s</sub> 48 kHz |

|                  | Supply Current (active)<br>(VSUP = 3.3 V) |                   |              | 1.15<br>1.5<br>0.5 |      | mA<br>mA<br>mA | Serial mode $f_s = 48 \text{ kHz}$<br>Parallel mode $f_s$ 192 kHz<br>Parallel mode $f_s$ 48 kHz                    |

# 4.6.3.2. Digital Inputs, Digital Outputs

| Symbol               | Parameter                  | Pin Name | Limit Values |                |     | Unit             | Test Conditions |  |  |  |

|----------------------|----------------------------|----------|--------------|----------------|-----|------------------|-----------------|--|--|--|

|                      |                            |          | Min.         | Min. Typ. Max. |     |                  |                 |  |  |  |

| Digital Input Levels |                            |          |              |                |     |                  |                 |  |  |  |

| V <sub>DIGIL</sub>   | Digital Input Low Voltage  | ADR_SEL  |              |                | 0.2 | V <sub>SUP</sub> |                 |  |  |  |

| V <sub>DIGIH</sub>   | Digital Input High Voltage |          | 0.5          |                |     | V <sub>SUP</sub> |                 |  |  |  |

| Z <sub>DIGI</sub>    | Input Capacitance          |          |              |                | 5   | pF               |                 |  |  |  |

## 4.6.3.3. Reset Input and Power-Up

| Symbol              | Parameter                         | Pin Name | Limit Values |      |      | Unit             | Test Conditions |  |

|---------------------|-----------------------------------|----------|--------------|------|------|------------------|-----------------|--|

|                     |                                   |          | Min.         | Тур. | Max. |                  |                 |  |

| RESETQ Input Levels |                                   |          |              |      |      |                  |                 |  |

| V <sub>RHL</sub>    | Reset High-Low Transition Voltage | RESETQ   |              |      | 0.2  | V <sub>SUP</sub> |                 |  |

| V <sub>RLH</sub>    | Reset Low-High Transition Voltage |          | 0.5          |      |      | V <sub>SUP</sub> |                 |  |

| Z <sub>RES</sub>    | Input Capacitance                 |          |              |      | 5    | pF               |                 |  |

# 4.6.3.4. I<sup>2</sup>C-Bus Characteristics

| Symbol              | Parameter                                                              | Pin Name    | Limit Values |      |      | Unit             | Test Conditions           |

|---------------------|------------------------------------------------------------------------|-------------|--------------|------|------|------------------|---------------------------|

|                     |                                                                        |             | Min.         | Тур. | Max. |                  |                           |

| V <sub>I2CIL</sub>  | I <sup>2</sup> C-Bus Input Low Voltage                                 | SCL,<br>SDA |              |      | 0.3  | V <sub>SUP</sub> |                           |

| V <sub>I2CIH</sub>  | I <sup>2</sup> C-Bus Input High Voltage                                | - SDA       | 0.6          |      |      | V <sub>SUP</sub> |                           |

| t <sub>I2C1</sub>   | I <sup>2</sup> C Start Condition Setup Time                            |             | 120          |      |      | ns               |                           |

| t <sub>l2C2</sub>   | I <sup>2</sup> C Stop Condition Setup Time                             |             | 120          |      |      | ns               |                           |

| t <sub>I2C5</sub>   | I <sup>2</sup> C-Data Setup Time<br>before Rising Edge of Clock        |             | 55           |      |      | ns               |                           |

| t <sub>I2C6</sub>   | I <sup>2</sup> C-Data Hold Time<br>after Falling Edge of Clock         |             | 55           |      |      | ns               |                           |

| t <sub>I2C3</sub>   | I <sup>2</sup> C-Clock Low Pulse Time                                  | SCL         | 500          |      |      | ns               |                           |

| t <sub>I2C4</sub>   | I <sup>2</sup> C-Clock High Pulse Time                                 | 1           | 500          |      |      | ns               |                           |

| f <sub>I2C</sub>    | I <sup>2</sup> C-BUS Frequency                                         | 1           |              |      | 1.0  | MHz              |                           |

| V <sub>I2COL</sub>  | I <sup>2</sup> C-Data Output Low Voltage                               | SCL,        |              |      | 0.4  | V                | I <sub>I2COL</sub> = 3 mA |

| I <sub>I2COH</sub>  | I <sup>2</sup> C-Data Output<br>High Leakage Current                   | SDA         |              |      | 1.0  | μА               | V <sub>12COH</sub> = 5 V  |

| t <sub>I2COL1</sub> | I <sup>2</sup> C-Data Output Hold Time after Falling Edge of Clock     |             | 15           |      |      | ns               |                           |

| t <sub>I2COL2</sub> | I <sup>2</sup> C-Data Output Setup Time<br>before Rising Edge of Clock |             | 100          |      |      | ns               | f <sub>I2C</sub> = 1 MHz  |

Fig. 4–6: I<sup>2</sup>C bus timing diagram

# 4.6.3.5. I<sup>2</sup>S-Bus Characteristics

| Symbol                     | Parameter                                        | Pin Name                                                                                       | Min.                      | Тур. | Max.   | Unit             | Test Conditions                                                                         |

|----------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------|------|--------|------------------|-----------------------------------------------------------------------------------------|

| V <sub>IL</sub>            | Input Low Voltage                                | I2S_DEL_CL<br>  I2S_DEL_WS<br>  I2S_DEL_IN1<br>  I2S_DEL_IN2<br>  I2S_DEL_IN3<br>  I2S_DEL_IN4 |                           |      | 0.2    | V <sub>SUP</sub> |                                                                                         |

| V <sub>IH</sub>            | Input High Voltage                               |                                                                                                | 0.5                       |      |        | V <sub>SUP</sub> |                                                                                         |

| Z <sub>I</sub>             | Input Impedance                                  |                                                                                                |                           |      | 5      | pF               |                                                                                         |

| I <sub>LEAK</sub>          | Input Leakage Current                            |                                                                                                | -1                        |      | 1      | μА               | 0 V < U <sub>INPUT</sub> < DVSUP                                                        |

| V <sub>OL</sub>            | Output Low Voltage                               | I2S_DEL_OUT1,                                                                                  |                           |      | 0.4    | ٧                | I <sub>OL</sub> = 1 mA                                                                  |

| V <sub>OH</sub>            | Output High Voltage                              | 12S_DEL_OUT2,<br>12S_DEL_OUT3,<br>12S_DEL_OUT4                                                 | V <sub>SUP</sub> -<br>0.3 |      |        | ٧                | I <sub>OH</sub> = -1 mA                                                                 |

| I <sup>2</sup> S Interface | Parallel Mode 2-channel                          |                                                                                                |                           |      |        |                  |                                                                                         |

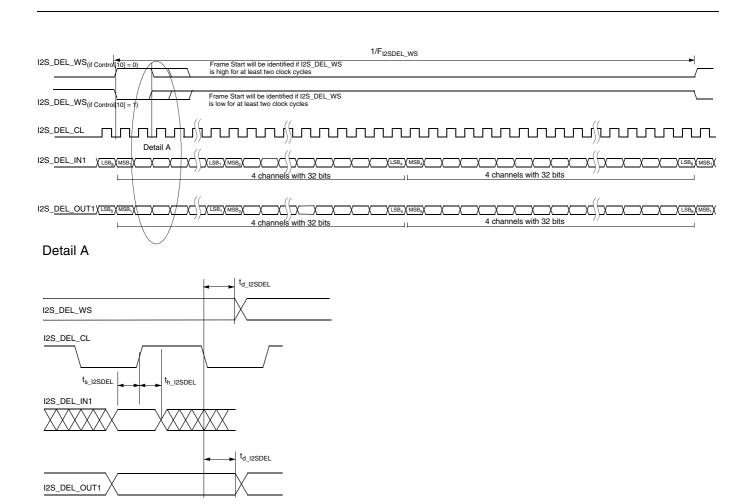

| t <sub>s_I2SDEL</sub>      | Input Setup Time<br>before Rising Edge of Clock  |                                                                                                | 7                         |      |        | ns               | for details see Fig. 4–8 "I <sup>2</sup> S bus timing diagram, serial mode (8-channel)" |

| t <sub>h_I2SDEL</sub>      | Input Hold Time<br>after Rising Edge of Clock    | - I2S_DEL_IN3,<br>I2S_DEL_IN4                                                                  | 10                        |      |        | ns               |                                                                                         |

| t <sub>d_I2SDEL</sub>      | Output Delay Time<br>after Falling Edge of Clock | I2S_DEL_OUT1,<br>I2S_DEL_OUT2,<br>I2S_DEL_OUT3,<br>I2S_DEL_OUT4                                |                           |      | 15     | ns               | C <sub>L</sub> =30 pF                                                                   |

| f <sub>I2SDEL_WS</sub>     | Word Strobe Input Frequency                      | ws                                                                                             | 4                         |      | 192    | kHz              | deviation = ±300 ppm                                                                    |

| f <sub>I2SDEL_CL</sub>     | Clock Input Frequency                            | CL                                                                                             | 0.256                     |      | 12.288 | MHz              | deviation = ±300 ppm                                                                    |

| R <sub>CL</sub>            | Clock Input Ratio                                |                                                                                                | 0.9                       |      | 1.1    |                  |                                                                                         |

| I <sup>2</sup> S Interface | Serial Mode 8-channel                            |                                                                                                |                           |      |        |                  |                                                                                         |

| t <sub>s_I2SDEL</sub>      | Input Setup Time<br>before Rising Edge of Clock  | I2S_DEL_CL<br>I2S_DEL_WS<br>I2S_DEL_IN1                                                        | 7                         |      |        | ns               | for details see Fig. 4–8 "I <sup>2</sup> S bus timing diagram, serial mode (8-channel)" |

| t <sub>h_I2SDEL</sub>      | Input Hold Time<br>after Rising Edge of Clock    |                                                                                                | 10                        |      |        | ns               |                                                                                         |

| t <sub>d_I2SDEL</sub>      | Output Delay Time<br>after Falling Edge of Clock | I2S_DEL_OUT1,                                                                                  |                           |      | 15     | ns               | C <sub>L</sub> =30 pF                                                                   |

| f <sub>I2SDEL_WS</sub>     | Word Strobe Input Frequency                      | I2S_DEL_WS                                                                                     | 4                         |      | 48     | kHz              |                                                                                         |

| f <sub>I2SDEL_CL</sub>     | Clock Input Frequency                            | I2S_DEL_CL                                                                                     | 1.024                     |      | 12.288 | MHz              |                                                                                         |

| R <sub>CL</sub>            | Clock Input Ratio                                |                                                                                                | 0.9                       |      | 1.1    |                  |                                                                                         |

Fig. 4–7: I<sup>2</sup>S bus timing diagram, parallel mode (2-channel)

Fig. 4–8: I<sup>2</sup>S bus timing diagram, serial mode (8-channel)

Micronas

#### 6. Data Sheet History

1. Preliminary Data Sheet: "MAD 4868A Micronas Audio Delay", May 11, 2004, 6251-636-1PD. First release of the preliminary data sheet.

Micronas GmbH Hans-Bunte-Strasse 19 D-79108 Freiburg (Germany) P.O. Box 840 D-79008 Freiburg (Germany) Tel. +49-761-517-0 Fax +49-761-517-2174 E-mail: docservice@micronas.com

Printed in Germany Order No. 6251-636-1PD

Internet: www.micronas.com

All information and data contained in this data sheet are without any commitment, are not to be considered as an offer for conclusion of a contract, nor shall they be construed as to create any liability. Any new issue of this data sheet invalidates previous issues. Product availability and delivery are exclusively subject to our respective order confirmation form; the same applies to orders based on development samples delivered. By this publication, Micronas GmbH does not assume responsibility for patent infringements or other rights of third parties which may result from its use.

Further, Micronas GmbH reserves the right to revise this publication and to make changes to its content, at any time, without obligation to notify any person or entity of such revisions or changes.

No part of this publication may be reproduced, photocopied, stored on a retrieval system, or transmitted without the express written consent of Micronas GmbH.