# IR2175(S)

### LINEAR CURRENT SENSING IC

#### **Features**

- Floating channel up to +600V

- · Monolithic integration

- Linear current feedback through shunt resistor

- Direct digital PWM output for easy interface

- Low IQBS allows the boot strap power supply

- Independent fast overcurrent trip signal

- High common mode noise immunity

- Input overvoltage protection for IGBT short circuit condition

- Open Drain outputs

#### **Description**

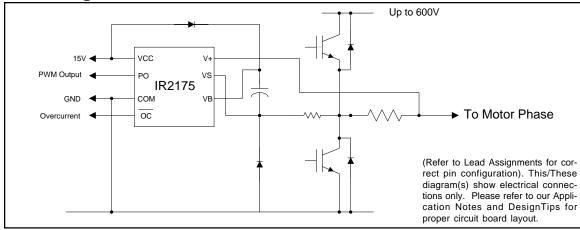

The IR2175 is a monolithic current sensing IC designed for motor drive applications. It senses the motor phase current through an external shunt resistor, converts from analog to digital signal, and transfers the signal to the low side. IR's proprietary high voltage isolation technology is implemented to enable the high bandwidth signal processing. The output format is discrete PWM to eliminate need for the A/D input interface for the IR2175. The dedicated overcurrent trip  $\overline{(OC)}$  signal facilitates IGBT short circuit protection. The open-drain outputs make easy for any interface from 3.3V to 15V. S

#### **Product Summary**

| Voffset                       | 600Vmax         |

|-------------------------------|-----------------|

| I <sub>QBS</sub>              | 2mA             |

| Vin                           | +/-260mVmax     |

| Gain temp.drift               | 20ppm/°C (typ.) |

| $f_{O}$                       | 130kHz (typ.)   |

| Overcurrent trip signal delay | 2μsec (typ)     |

| Overcurrent trip level        | +/-260mV (typ.) |

#### **Packages**

## **Block Diagram**

### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM, all currents are defined positive into any lead. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol            | Definition                                                        |             | Min.     | Max.     | Units |  |

|-------------------|-------------------------------------------------------------------|-------------|----------|----------|-------|--|

| Vs                | High side offset voltage                                          |             | -0.3     | 600      |       |  |

| V <sub>BS</sub>   | High side floating supply voltage                                 |             | -0.3     | 25       |       |  |

| Vcc               | Low side and logic fixed supply voltage                           |             | -0.3     | 25       |       |  |

| V <sub>IN</sub>   | Maximum input voltage between V <sub>IN+ and</sub> V <sub>3</sub> | 3           | -5       | 5        | V     |  |

| V <sub>PO</sub>   | Digital PWM output voltage                                        |             | COM -0.3 | VCC +0.3 |       |  |

| Voc               | Overcurrent output voltage                                        |             | COM -0.3 | VCC +0.3 |       |  |

| dV/dt             | Allowable offset voltage slew rate                                |             | _        | 50       | V/ns  |  |

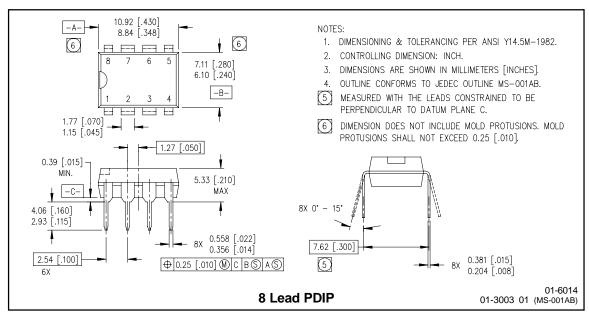

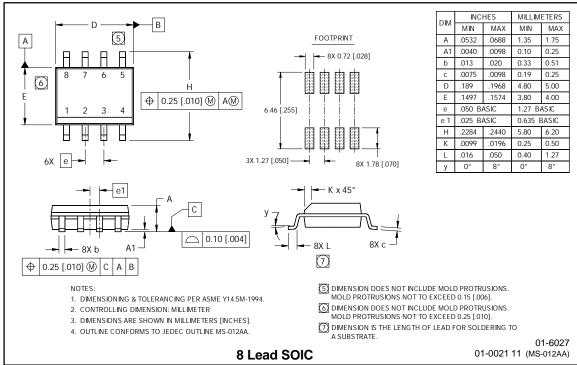

| PD                | Package power dissipation @ T <sub>A</sub> ≤ +25°C                | 8 lead SOIC | _        | .625     | w     |  |

|                   |                                                                   | 8 lead PDIP | _        | 1.0      | Į vv  |  |

| Rth <sub>JA</sub> | Thermal resistance, junction to ambient                           | 8 lead SOIC | _        | 200      |       |  |

|                   |                                                                   | 8 lead PDIP | _        | 125      | °C/W  |  |

| TJ                | Junction temperature                                              |             | _        | 150      |       |  |

| T <sub>S</sub>    | Storage temperature                                               |             | -55      | 150      | °C    |  |

| TL                | Lead temperature (soldering, 10 seconds)                          |             |          | 300      |       |  |

Note 1: Capacitors are required between VB and Vs when bootstrap power is used. The external power supply, when used, is required between VB and Vs pins.

## **Recommended Operating Conditions**

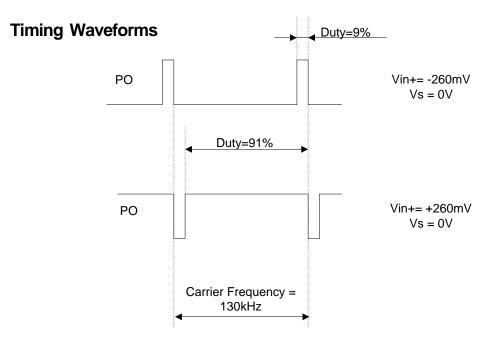

The output logic timing diagram is shown in figure 1. For proper operation the device should be used within the recommended conditions.

| Symbol          | Definition                                                | Min.                 | Max.               | Units |

|-----------------|-----------------------------------------------------------|----------------------|--------------------|-------|

| V <sub>B</sub>  | High side floating supply voltage                         | V <sub>S</sub> +13.0 | V <sub>S</sub> +20 |       |

| Vs              | High side floating supply offset voltage                  | 0.3                  | 600                |       |

| V <sub>PO</sub> | Digital PWM output voltage                                | СОМ                  | VCC                | V     |

| Voc             | Overcurrent output voltage                                | СОМ                  | VCC                |       |

| Vcc             | Low side and logic fixed supply voltage                   | 9.5                  | 20                 |       |

| V <sub>IN</sub> | Input voltage between V <sub>IN+</sub> and V <sub>S</sub> | -260                 | +260               | mV    |

| T <sub>A</sub>  | Ambient temperature                                       | -40                  | 125                | °C    |

#### **DC Electrical Characteristics**

$V_{CC} = V_{BS} = 15V$ , and  $T_A = 25^{\circ}$  unless otherwise specified.

| Symbol                       | Definition                                           | Min. | Тур. | Max. | Units  | Test Conditions                      |

|------------------------------|------------------------------------------------------|------|------|------|--------|--------------------------------------|

| V <sub>IN</sub>              | Nominal input voltage range before saturation        | -260 | _    | 260  |        |                                      |

|                              | V <sub>IN+</sub> -V <sub>S</sub>                     |      |      |      |        |                                      |

| V <sub>OC+</sub>             | Overcurrent trip positive input voltage              | _    | 260  | _    | mV     |                                      |

| V <sub>OC</sub> -            | Overcurrent trip negative input voltage              | _    | -260 | _    |        |                                      |

| Vos                          | Input offset voltage                                 | -10  | 0    | 10   |        | V <sub>IN</sub> = 0V (Note 1)        |

| $\Delta V_{OS}/\Delta T_{A}$ | Input offset voltage temperature drift               | _    | 25   | _    | μV/°C  |                                      |

| G                            | Gain (duty cycle % per V <sub>IN</sub> )             | 155  | 160  | 165  | %/V    | max gain error=5%                    |

|                              |                                                      |      |      |      |        | (Note 2)                             |

| ΔG/ΔΤΑ                       | Gain temperature drift                               | _    | 20   | _    | ppm/°C |                                      |

| I <sub>LK</sub>              | Offset supply leakage current                        | _    | _    | 50   | μA     | V <sub>B</sub> =V <sub>S</sub> =600V |

| I <sub>QBS</sub>             | Quiescent V <sub>BS</sub> supply current             | _    | 2    | _    | A      | V <sub>S</sub> = 0V                  |

| lacc                         | Quiescent V <sub>CC</sub> supply current             | _    | _    | 0.5  | mA     |                                      |

| LIN                          | Linearity (duty cycle deviation from ideal linearity | _    | 0.5  | 1    | %      |                                      |

|                              | curve)                                               |      |      |      |        |                                      |

| ΔV <sub>LIN</sub> /ΔΤΑ       | Linearity temperature drift                          | _    | .005 | _    | %/°C   |                                      |

| lopo                         | Digital PWM output sink current                      | 20   | _    | _    |        | V <sub>O</sub> = 1V                  |

|                              |                                                      | 2    | _    | _    | mA     | V <sub>O</sub> = 0.1V                |

| locc                         | OC output sink current                               | 10   | _    | _    | IIIA   | V <sub>O</sub> = 1V                  |

|                              |                                                      | 1    | _    |      |        | V <sub>O</sub> = 0.1V                |

Note 1:  $\pm 10$ mV offset represents  $\pm 1.5\%$  duty cycle fluctuation

Note 2: Gain = (full range of duty cycle in %) / (full input voltage range).

### **AC Electrical Characteristics**

$V_{CC} = V_{BS} = 15V$ , and  $T_A = 25^{\circ}$  unless otherwise specified.

| Symbol                  | Definition                             | Min. | Тур. | Max. | Units  | Test Conditions                 |

|-------------------------|----------------------------------------|------|------|------|--------|---------------------------------|

| Propaga                 | tion delay characteristics             |      |      |      |        |                                 |

| fo                      | Carrier frequency output               | 95   | 130  | 165  | kHz    | figure 1                        |

| $\Delta$ f/ $\Delta$ TA | Temperature drift of carrier frequency | _    | 500  | _    | ppm/°C | V <sub>IN</sub> = 0 & 5V        |

| Dmin                    | Minimum duty                           | _    | 9    | _    | %      | V <sub>IN</sub> +=-260mV,       |

| Dmax                    | Maximum duty                           | _    | 91   | _    | %      | V <sub>IN</sub> +=+260mV        |

| BW                      | fo bandwidth                           | _    | 15   | _    | kHz    | V <sub>IN</sub> + = 100mVpk -pk |

|                         |                                        |      |      |      |        | sine wave, gain=-3dB            |

| PHS                     | Phase shift at 1kHz                    | _    | -10  | _    | 0      | V <sub>IN</sub> + =100mVpk-pk   |

|                         |                                        |      |      |      |        | sine wave                       |

| tdoc                    | Propagation delay time of OC           | 1    | 2    |      | μsec   |                                 |

| twoc                    | Low true pulse width of OC             | _    | 1.5  | _    | μοσο   |                                 |

Figure 1 Output waveform

## **Application Hint:**

Temperature drift of the output carrier frequency can be cancelled by measuring both a PWM period and the on-time of PWM (Duty) at the same time. Since both periods vary in the same direction, computing the ratio between these values at each PWM period gives consistent measurement of the current feedback over the temperature drift.

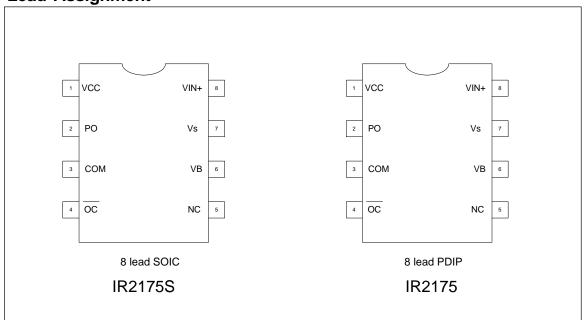

### **Lead Definitions**

| Symbol           | Description                         |

|------------------|-------------------------------------|

| Vcc              | Low side and logic supply voltage   |

| COM              | Low side logic ground               |

| V <sub>IN+</sub> | Positive sense input                |

| VB               | High side supply                    |

| Vs               | High side return                    |

| PO               | Digital PWM output                  |

| <u>oc</u>        | Overcurrent output (negative logic) |

| N.C.             | No connection                       |

# **Lead Assignment**

#### **Case Outlines**