Burr-Brown IC Data Book—Data Conversion Products

#### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage (Vpp)            | -0.3V to +7.0V |

|---------------------------------|----------------|

| Input Voltage (V <sub>N</sub> ) |                |

| Soldering Temperature           | +255°C         |

| Soldering Time                  |                |

| Storage Temperature             |                |

#### PACKAGE INFORMATION®

| PACKAGE         | NUMBER          |

|-----------------|-----------------|

| Pin Plastic DIP | 215<br>252      |

|                 | Pin Plastic DIP |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

# **DC SPECIFICATIONS**

#### ELECTRICAL

$V^{}_{\rm DD}$  = 4.5V to 5.5V,  $V^{}_{\rm SS}$  = 0V,  $T^{}_{\rm A}$  = –20°C to +80°C unless otherwise specified.

|                                             |         |                                      |                                                |                    | DF1750P/U | J                  |                  |

|---------------------------------------------|---------|--------------------------------------|------------------------------------------------|--------------------|-----------|--------------------|------------------|

| PARAMETER                                   | PIN     | SYMBOL                               | CONDITION                                      | MIN                | ТҮР       | MAX                | UNIT             |

| INPUTS                                      |         |                                      |                                                |                    |           | 1                  |                  |

| Logic Family                                | į –     |                                      |                                                |                    | CMOS      | i i                |                  |

| Logic Voltages                              | XTI     | ٧,,                                  | For Clock Input                                |                    |           | 0.3V <sub>00</sub> | ٧                |

|                                             | XTI     | V <sub>KL1</sub><br>V <sub>011</sub> | For Clock Input                                | 0.7V <sub>pp</sub> |           | 0.0                | ٧                |

|                                             | X⊤I     |                                      | For AC Coupling                                | 1.8                |           |                    | V <sub>p.p</sub> |

|                                             | (1).(2) | V <sub>II2</sub>                     | FSEN = H                                       |                    |           | 0.5                |                  |

|                                             | (1),(2) | V <sub>ite</sub>                     | FSEN = H                                       | 2.4                |           |                    | V                |

| Logic Currents                              | XTI     | 1. Ing -                             | V <sub>N</sub> = 0V                            | *                  | 5         | 10                 | μA               |

|                                             | XTI     | l <sub>int</sub>                     | $V_{iN} = V_{DO}$                              |                    | 5         | 10                 | μA               |

|                                             | (1).(2) | ha                                   | $V_{\rm N} = 0 \tilde{V}, FSEN = H$            |                    | 10        | 20                 | μA               |

| Input Leakage Current                       | (1).(2) | I <sub>LHI</sub>                     | V <sub>IN</sub> = V <sub>DO</sub> , FSEN = H   |                    |           | 1.0                | μA               |

| OUTPUTS                                     |         |                                      |                                                |                    |           |                    |                  |

| Logic Family                                | ł       |                                      |                                                |                    | CMOS      |                    |                  |

| Logic Voltages                              | (2),(3) | v                                    | l <sub>or</sub> = 1.6mA, FSEN = L              |                    | 0.000     | 0.4                | .v               |

|                                             | (2).(3) | V <sub>ol</sub><br>V <sub>oH</sub>   | $I_{OH} = -0.4$ mA, FSEN = L                   | 2.5                |           |                    |                  |

| POWER SUPPLY REQUIREMENTS<br>Supply Voltage | :       | V <sub>091</sub> , V <sub>002</sub>  |                                                |                    | +5        |                    | v                |

| Supply Current                              |         | 001 002                              | V <sub>10</sub> = 5V <sup>(4)</sup> , FSEN = H |                    | +3        | 30                 | mA               |

| Power Dissipation                           |         | • I <sub>D</sub>                     | Nominal V <sub>pp</sub>                        |                    |           | 250                | mW               |

| TEMPERATURE RANGE (AMBIENT, T,)             |         |                                      |                                                |                    |           |                    |                  |

| Specification                               |         |                                      |                                                | -20                |           | +80                | °C               |

| Operating                                   |         |                                      |                                                | -20                |           | +80                | °C               |

NOTES: (1) Refers to pins SCSL1, SCSL2, TEST, 2DS, IMOD, DINR, IBCK, DINL, 0W20, MUTE, OBPOL, LRPOL, FSEN, CKEN. (2) Refers to pins BCK, WDCK, LRCK. (3) Refers to pins CKO, CC, BBC, IBO, DOUT. (4) Test Condition; SCSL1 + H, SCSL2 + H, TEST + H, 2DS + H, IMOD = H, 0W20 = H, MUTE + H, OBPOL = H, FSEN = L, CKEN = L. T<sub>cv</sub> = 38ns (XTI Clock Period), C<sub>1</sub>= 0pF (Capacitive Load), DINL, DINR (Applicable Input Data).

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the users own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

8.3.160

Burr-Brown IC Data Book—Data Conversion Products

Electrostatic discharge can cause damage ranging from performance degradation to complete device failure. Burr-Brown Corporation recommends that all integrated circuits be handled and stored using appropriate ESD protection methods.

# Or, Call Customer Service at 1-800-548-6132 (USA Only)

# **AC SPECIFICATIONS**

### ELECTRICAL

$V_{op}$  = 4.5V to 5.5V,  $V_{ss}$  = 0V,  $T_{A}$  = -20°C to +80°C unless otherwise specified.

### XTI Clock

|                                    |                  | COND                | DITION             | SYS                                             | DF1750P/U            |     |                         |                          |                                                 |

|------------------------------------|------------------|---------------------|--------------------|-------------------------------------------------|----------------------|-----|-------------------------|--------------------------|-------------------------------------------------|

| PARAMETER                          | SYMBOL           | SCSL1               | SCSL2              | FREQ                                            | MIN                  | Түр | MAX                     | UNIT                     |                                                 |

| Crystal<br>Oscillator<br>Frequency | F <sub>oec</sub> | H<br>H<br>L         | H<br>L<br>H<br>L   | 512fs <sup>(1)</sup><br>256fs<br>768fs<br>384fs | 8<br>4<br>12<br>6    |     | 26<br>13<br>26<br>20    | MHz<br>MHz<br>MHz<br>MHz | XTI                                             |

| External Clock<br>Pulse Width      | t <sub>cw</sub>  | H <u></u><br>H<br>L | H .<br>L<br>H<br>L | 512fs<br>256fs<br>768fs<br>384fs                | 15<br>38<br>15<br>25 |     | 70<br>140<br>50<br>100  | ns<br>NS<br>NS<br>NS     | AC Coupling is required with an external clock. |

| External Clock<br>Pulse Period     | t <sub>ev</sub>  | H<br>H<br>L         | H<br>L<br>L        | 512ts<br>256ts<br>768ts<br>384ts                | 38<br>77<br>38<br>50 |     | 125<br>250<br>84<br>167 | ns<br>ns<br>ns<br>ns     |                                                 |

NOTE: (1) fs = Sampling frequency.

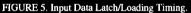

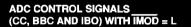

## ADC CONTROL SIGNAL TIMING (CC, BBC, AND IBO) WITH IMOD = H

| PARAMETER               |        |      |         |     |      |              |                        |

|-------------------------|--------|------|---------|-----|------|--------------|------------------------|

|                         | SYMBOL | MIN  | TYP     | MAX | UNIT |              |                        |

| 205 = H                 |        |      |         |     |      |              |                        |

| CC Pulse Width (H)      | T1     | 65   | 1/256fs |     | ns   |              |                        |

| S/H Acquisition Time    | T2     | 670  | 9/256fs |     | ns   |              |                        |

| CC-BBC Time             | Т3     | 285  | 4/256fs |     | ns   | cc1.5V       |                        |

| BBC Pulse Period        | T4     | 228  | 3/256fs | 1   | ns   |              |                        |

| BBC Pulse Width (H)     | T5     | 65   | 1/256fs |     | ns   |              | 0                      |

| BBC Pulse Width (L)     | T6     | 140  | 2/256fs |     | ns   | T2 T3 T5     | 9                      |

| BBC-IBO Time            | T7     | 140  | 2/256fs |     | ns   |              | Ň                      |

| IBO Pulse Period        | T8     | 228  | 3/256fs |     | ns   | BBC          |                        |

| IBO Pulse Width (H)     | T9     | 140  | 2/256fs |     | ns   |              | L ÚL -                 |

| IBO Pulse Width (L)     | T10    | 65   | 1/256fs |     | ПŜ   | 16           | DF1750                 |

| 2DS = L                 |        |      |         |     |      |              |                        |

| CC Pulse Width (H)      | T1     | 130  | 1/256fs |     | ns   | T9           |                        |

| S/H Acquisition Time    | T2     | 1350 | 9/256fs |     | ns   |              | 8.3                    |

| CC-BBC Time             | тз     | 570  | 4/256fs | 1   | ns   | во -/-\/-\\\ | 0.5                    |

| <b>BBC Pulse Period</b> | T4     | 456  | 3/256fs |     | ns   |              |                        |

| BBC Pulse Width (H)     |        | 130  | 1/256fs |     | ns   | T10          | L                      |

| BBC Pulse Width (L)     | Т6     | 280  | 2/256fs |     | ns   |              | ā                      |

| BBC-IBO Time            | 17     | 280  | 2/256fs |     | ns   |              |                        |

| IBO Pulse Period        | T8     | 456  | 3/256fs | ļ   | ns   |              |                        |

| IBO Pulse Width (H)     | Т9     | 280  | 2/256fs |     | ns   |              | CO I                   |

| IBO Pulse Width (L)     | T10    | 130  | 1/256fs |     | ns   |              | H                      |

|                         |        |      |         |     |      |              | DIGITAL AUDIO PRODUCTS |

BURR-BROWN® Burr-Brown IC Data Book—Data Conversion Products

|                                |                      |                            | DF1750P/U |     |      |                                           |

|--------------------------------|----------------------|----------------------------|-----------|-----|------|-------------------------------------------|

| PARAMETER SYMBOL               | SYMBOL               | MIN                        | TYP       | MAX | UNIT |                                           |

| 2DS = H                        |                      |                            |           |     |      |                                           |

| <b>IBCK Pulse Width</b>        | t <sub>ew</sub>      | 50                         | 1/256fs   |     | ns   |                                           |

| IBCK Pulse Period              | t <sub>iBY</sub>     | 3/12.928MHz <sup>(1)</sup> | 3/256fs   |     | ΠS   | CC                                        |

| Data Word Latch                | t <sub>sL</sub>      | 50                         |           |     | ns   |                                           |

| Set-up Time                    |                      |                            |           |     |      | t <sub>HL</sub> 🛌 <sup>t</sup> sl 🖛       |

| Data Word Latch                | t <sub>ne</sub>      | 50                         |           |     | ns   |                                           |

| Hold Time                      |                      |                            |           |     |      |                                           |

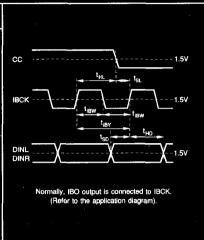

| DINL, DINR                     | t <sub>so</sub>      | 25                         |           |     | ns   | BCK                                       |

| Set-up Time                    |                      |                            |           |     |      |                                           |

| DINL, DINR                     | t <sub>HD</sub>      | 25                         |           |     | ns   | t <sub>IBY</sub>                          |

| Hold Time                      |                      |                            |           |     |      | t <sub>HD</sub>                           |

| 2DS = L                        |                      |                            |           |     |      |                                           |

|                                |                      |                            |           |     |      | DINL                                      |

| IBCK Pulse Width               | LIEW                 | 50                         | 1/128fs   |     | ns   |                                           |

| BCK Pulse Period               | LIBY                 | 3/12.928MHz(1)             | 3/1281s   |     | ns   |                                           |

| Data Word Latch<br>Set-up Time | t <sub>si</sub>      | 50                         |           |     | ns   | Normally, IBO output is connected to IBCK |

| Data Word Latch                |                      | 50                         |           |     | ns   | (Refer to the applications diagram).      |

| Hold Time                      | t <sub>HL</sub>      | 50                         |           |     | 15   |                                           |

| DINL, DINR                     | t <sub>so</sub>      | 25                         |           |     | ns   |                                           |

| Set-up Time                    | 50                   |                            |           |     | 13   |                                           |

| DINL, DINR                     | t<br>t <sub>HO</sub> | 25                         |           |     | ns   |                                           |

| Hold Time                      | 140                  |                            |           |     | 115  |                                           |

NOTE: (1) 12.928MHz = 256 x 50.5kHz (max sampling frequency).

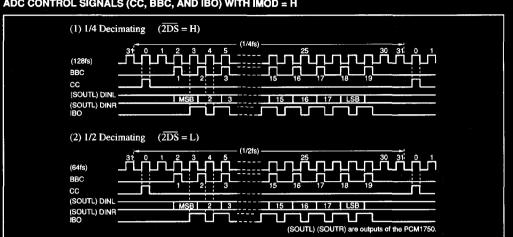

## ADC CONTROL SIGNAL TIMING (CC, BBC, AND IBO) WITH IMOD = L

|                                     |                                        |     | DF1750P/U         |     |          |

|-------------------------------------|----------------------------------------|-----|-------------------|-----|----------|

| PARAMETER                           | SYMBOL                                 | MIN | түр               | MAX | UNIT     |

| 2DS = H                             |                                        |     |                   |     |          |

| CC Pulse Width (H)                  | t <sub>cow</sub>                       |     | 1/8fs             |     | ns       |

| BBC Pulse Width                     | t <sub>eew</sub>                       | 130 | 1/128fs           |     | ns       |

| BBC Pulse Period                    | L <sup>BBA</sup>                       | 100 | 1/64fs            |     | ns       |

| IBO Pulse Width<br>IBO Pulse Period | t <sub>BOW</sub>                       | 130 | 1/128fs<br>1/64fs |     | ns<br>Ns |

| CC-BBC Time                         | t <sub>BOY</sub>                       | -5  | 0                 | 20  | ns       |

| CC-IBO Time                         | t <sub>ccso</sub>                      | 130 | 1/128fs           |     | ns       |

| BBC-IBO Time                        | teseo                                  | 130 | 1/128fs           |     | ns       |

| 2DS = L                             |                                        |     |                   |     |          |

| CC Pulse Width (H)                  | t <sub>cow</sub>                       |     | 1/4fs             |     | ns       |

| BBC Pulse Width                     | teew                                   | 280 | 1/64fs            |     | ns       |

| BBC Pulse Period                    | t <sub>BBY</sub>                       |     | 1/32fs            |     | ns       |

| IBO Pulse Width<br>IBO Pulse Period | Bow                                    | 280 | 1/64fs<br>1/32fs  |     | ns       |

| CC-BBC Time                         | teor                                   | -5  | 0                 | 20  | ns<br>ns |

| CC-IBO Time                         | <sup>1</sup> ссвв<br>t <sub>ссво</sub> | 280 | 1/64 <b>1</b> s   |     | ns       |

| BBC-IBOTime                         | t <sub>BBBO</sub>                      | 280 | 1/64fs            |     | пѕ       |

8.3.162

Burr-Brown IC Data Book—Data Conversion Products

# Or, Call Customer Service at 1-800-548-6132 (USA Only)

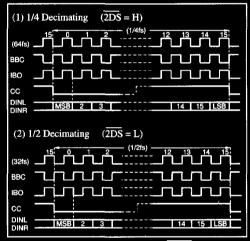

## SERIAL INPUT TIMING (IBCK, DINL, DINR) WITH IMOD = L

|                                |                  |                           | DF1750P/U |     |      |

|--------------------------------|------------------|---------------------------|-----------|-----|------|

| PARAMETER                      | SYMBOL           | MIN                       | ТҮР       | MAX | UNIT |

| 2DS = H                        |                  |                           |           |     |      |

| IBCK Pulse Width               | Lew              | 100                       | 1/128fs   |     | ns   |

| IBCK Pulse Period              | t <sub>iBY</sub> | 1/3.232MHz <sup>(1)</sup> | 1/64fs    |     | ns   |

| Data Word Latch<br>Set-up Time | t <sub>si</sub>  | 50                        |           |     | ns   |

| Data Word Latch<br>Hold Time   | t <sub>HL</sub>  | 50                        |           |     | ns   |

| DINL, DINR<br>Set-up Time      | t <sub>sp</sub>  | 25                        |           |     | ns   |

| DINL, DINR                     | t <sub>uo</sub>  | 25                        |           |     | ns   |

| Hold Time                      |                  |                           |           |     |      |

| 2DS = L                        |                  |                           |           |     |      |

| IBCK Pulse Width               | t <sub>iew</sub> | 100                       | 1/64fs    |     | ns   |

| IBCK Pulse Period              |                  | 1/3.232MHz <sup>(1)</sup> | 1/32fs    |     | ns   |

| Data Word Latch<br>Set-up Time | t <sub>st</sub>  | 50                        |           |     | ns   |

| Data Word Latch<br>Hold Time   | t <sub>ni</sub>  | 50                        |           |     | ns   |

| DINL, DINR<br>Set-up Time      | t <sub>s0</sub>  | 25                        |           |     | ns   |

| DINL, DINR<br>Hold Time        | t <sub>HD</sub>  | 25                        |           |     | ns   |

NOTE: (1) 3.232MHz = 64 x 50.5kHz (max sampling frequency).

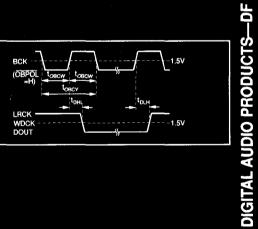

#### SERIAL OUTPUT TIMING WITH FSEN = H

|                                      |                                      |                           | F1750P/         | U   |          |                      | · · · · · · · · · · · · · · · · · · · |     |

|--------------------------------------|--------------------------------------|---------------------------|-----------------|-----|----------|----------------------|---------------------------------------|-----|

| PARAMETER                            | SYMBOL                               | MIN                       | TYP             | MAX | UNIT     | REMARKS              | LRCK 1.5V                             |     |

| BCK Pulse Width                      | t <sub>ecw</sub>                     | 100                       | 1/128fs         |     | ns       | :                    |                                       |     |

| BCK Pulse Period<br>LRCK Pulse Width | t <sub>ecv</sub><br>t <sub>icw</sub> | 1/3.232MHz <sup>(1)</sup> | 1/64ts<br>1/2fs |     | ns<br>µs | Duty = 50%           |                                       | 0   |

| LRCK Pulse Period                    | LCW                                  | 1/50.5kHz                 | 1/fs            |     | μs       |                      | вск 1.5V                              | 75  |

| LRCK Set-up Time<br>LRCK Hold Time   | t <sub>a</sub>                       | 50<br>50                  |                 | •   | ns       |                      |                                       |     |

| Output Data                          | t <sub>e</sub>                       | 0                         |                 |     | ns       | C <sub>L</sub> = 0pF | (OBPOL = H) t <sub>BCY</sub>          | l d |

| Hold Time<br>Output Data             | t,                                   |                           |                 | 100 | ns       | C, = 15pF            |                                       |     |

| Delay Time                           |                                      |                           |                 |     |          |                      | DOUT X X 1.5V                         |     |

|                                      |                                      |                           |                 |     |          |                      | /////                                 | 8.3 |

NOTE: (1) 3.232MHz = 64 x 50.5kHz (max sampling frequency)

#### SERIAL OUTPUT TIMING WITH FSEN = L

|                                                                                                                                                   |                                                                                              |            | DF1750P/L                                            | )        |                                        |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------|------------------------------------------------------|----------|----------------------------------------|------|

| PARAMETER                                                                                                                                         | SYMBOL                                                                                       | MIN        | ТҮР                                                  | MAX      | UNIT                                   | BCK  |

| BCK Pulse Width<br>BCK Pulse Period<br>WDCK Pulse Width<br>WDCK Pulse Width<br>LRCK Pulse Vidth<br>LRCK Pulse Period<br>Output Data<br>Delay Time | tовсм<br>tовсу<br>twocw<br>twocv<br>tuncw<br>tuncw<br>tuncw<br>tuncy<br>tonu<br>tonu<br>tonu | -10<br>-10 | 1/128fs<br>1/64fs<br>1/4fs<br>1/2fs<br>1/2fs<br>1/fs | 30<br>30 | ns<br>ns<br>µs<br>µs<br>µs<br>ns<br>ns | (ÖBF |

BURR-BROWNS Burr-Brown IC Data Book—Data Conversion Products

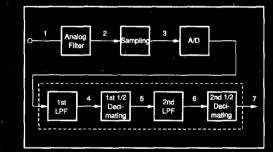

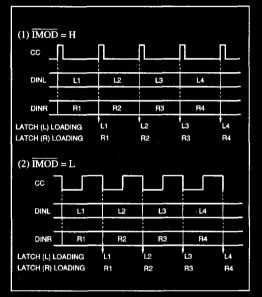

## THEORY

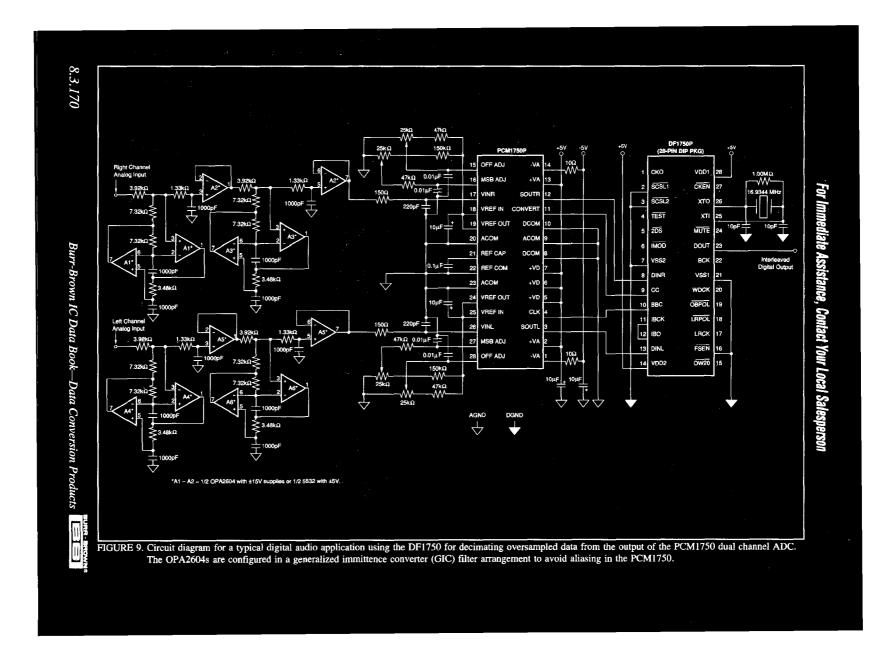

According to the Nyquist Theorem, digital audio recordings sampled at a rate of 44.1kHz (CD) or 48kHz (DAT) should accurately reproduce the full 20kHz audio bandwidth. Unfortunately, if frequencies higher than 1/2 the sample rate are seen at the input of an analog-to-digital converter, aliasing back into the baseband will occur. At these sample frequencies, the way to assure that aliasing does not occur is to use complicated high order filters at the input of the ADC. These filters can be expensive and they can also have undesirable phase characteristics. These problems can be avoided by using an oversampling ADC (such as the PCM1750) with a decimating filter, where a high order filter can be replaced with a low order filter which has very little phase distortion (Figure 1).

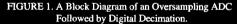

With the oversampling-decimating technique, the input signal (Figure 2a) is band limited by a low order analog low-pass filter as shown in Figure 2b. This signal is 4-times oversampled, with its spectra and foldover noise shown in Figure 2c. The DF1750 first rejects the high frequency components of the 4fs ADC output (Figure 2d). A 1/2 decimating filter then processes this data into a 2fs data stream. This output spectra is shown in Figure 2e. The high frequency components of the 2fs data are then removed, producing the output spectra shown in Figure 2f. A second 1/2 decimating filter processes the 2fs data to a final fs data stream and the original signal is restored without distortion (Figure 2g). Note, when operating in the 1/2 decimating mode the DF1750 processes data through the first LPF and a single 1/2 decimating filter only.

Signal (a) 2.0 4.0 x fs 1.0 3.0 Band limited by the analog filter. (b) 1.0 2.0 3.0 4.0 x fs Foldover Nolse (C) 2.0 3.0 4.0 x ts 1.0 Foldover Noise (d) Sia 2.0 4.0 x fs 1.0 3.0 Foldover Noise Foldove 2.0 1.0 3.0 4.0 x fs Foldover Noise Foldove Noise í n 2.0 3.0 4.0 x fs F/N F/N F/N F/N (q) 2.0 4.0 x fs 10 3.0 FIGURE 2. The Associated Spectra of the Oversampling-

8,3.164

Burr-Brown IC Data Book—Data Conversion Products

## **FUNCTIONAL DESCRIPTION**

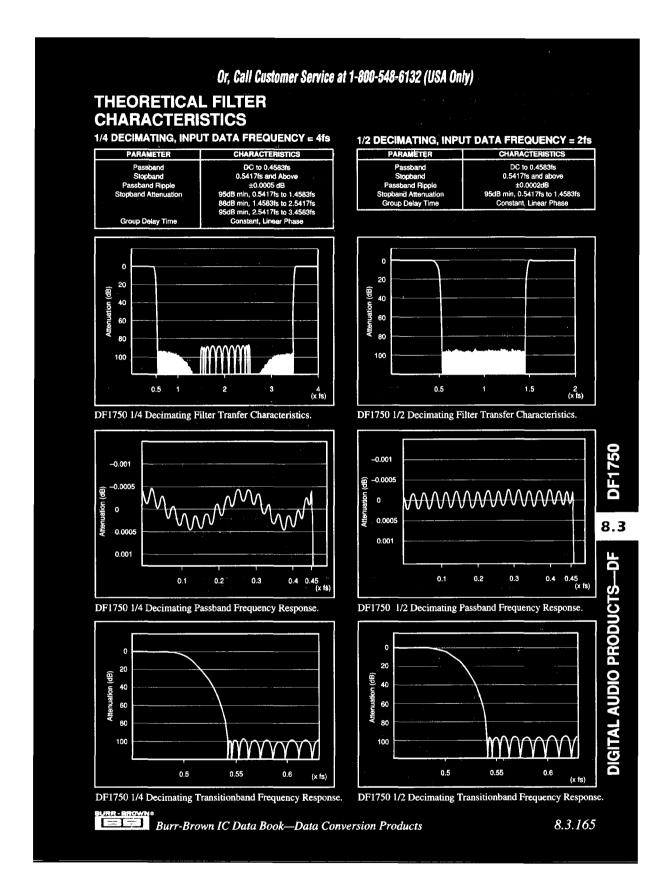

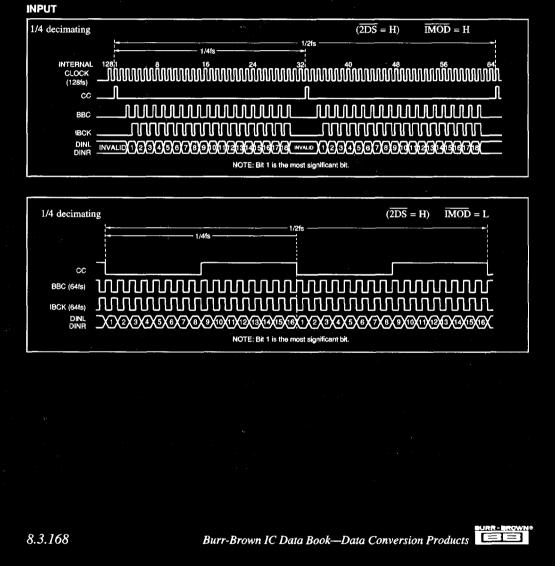

#### 1/4 AND 1/2 DECIMATING FUNCTIONS

1/4 or 1/2 decimating filtering converts 4fs or 2fs oversampled data back to a sampling rate of fs data by a digital filtering algorithm.  $\overline{2DS}$  is used to select 1/4 or 1/2 decimating.

$2\overline{DS}$  = H; 1/4 decimating (0.5417fs ~ 3.4583fs) 2DS = L; 1/2 decimating (0.5417fs ~ 1.4583fs)

The filter arithmetic block consists of two 1/2 decimating finite impulse response (FIR) filters as shown in Figure 3.

FIGURE 3. Filter Arithmetic Structure

#### SYSTEM CLOCK

The system clock frequency can be 256fs, 364fs, 512fs, or 768fs selectable with  $\overline{SCSL1}$  and  $\overline{SCSL2}$  as indicated in Table I. An external clock (applied to Pin XTI) or crystal oscillator (Pins XTI and XTO) can be employed. AC coupling is required for an external clock.

The XTI input clock is available as an output at pin CKO, when  $\overrightarrow{CKEN} = L$ . CKO stays low when  $\overrightarrow{CKEN} = H$ .

| SCSL1                                 |                  |       | н     |                          | L     |  |  |

|---------------------------------------|------------------|-------|-------|--------------------------|-------|--|--|

| SCSL2                                 |                  | н     | L     | Н                        | L     |  |  |

| XTI Glock<br>Frequency                | F <sub>xi</sub>  | 512fs | 256ts | 768fs                    | 384fs |  |  |

| Clock<br>Input                        |                  |       |       | l Clock or<br>Oscillator | = -   |  |  |

| Internal System<br>Clock<br>Frequency | F <sub>sys</sub> |       | 25    | 6fs                      |       |  |  |

TABLE I. System Clock and Internal Clock Frequency Selection.

#### SERIAL DATA INPUT

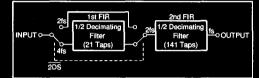

The DF1750 is programmed for accepting the correct number of input data bits per word by the  $\overline{IMOD}$  pin. A 16-bit input word is selected with  $\overline{IMOD} = L$  and an 18-bit input word is selected with  $\overline{IMOD} = H$ . Set  $\overline{IMOD} = H$  for use with the PCM1750. The serial input data format is two's complement and MSB first. Both the left and right channel data are loaded into the DF1750 simutaneously.

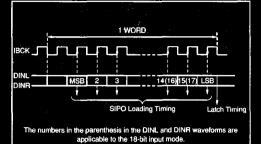

Each bit of the data is loaded to each channel's SIPO (Serial/ parallel conversion register) by the rising edge of the Input Bit Clock, IBCK (Figure 4). After the serial input data is loaded, the data is latched into a parallel register by the rising edge of CC for  $\overline{IMOD} = H$  and the falling edge of CC for  $\overline{IMOD} = L$  (Figure 5).

8.3.166

Burr-Brown IC Data Book—Data Conversion Products

FIGURE 4. SIPO Input Data Loading Timing.

### Or, Call Customer Service at 1-800-548-6132 (USA Only)

ADC CONTROL SIGNALS (CC, BBC, AND IBO) WITH IMOD = H

FIGURE 7. ADC Control Signals with  $\overline{\text{IMOD}} = L$ .

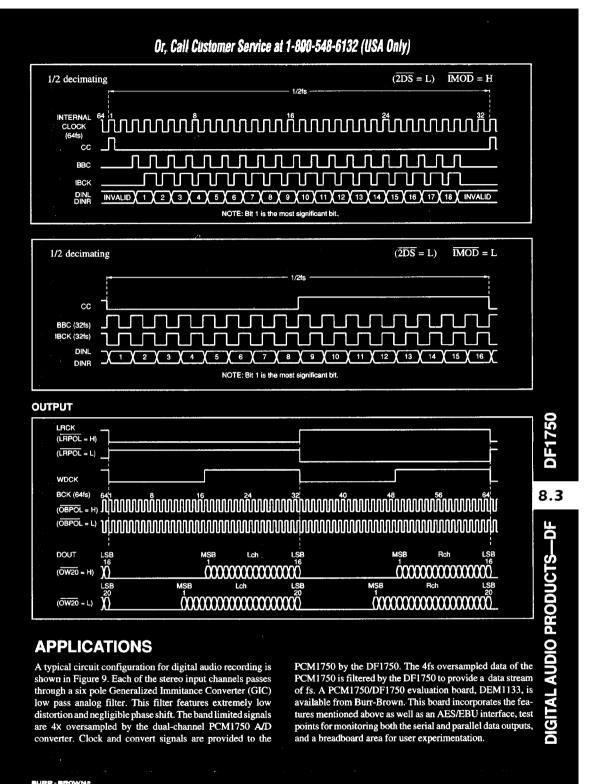

#### **OUTPUT INTERFACE**

(BCK, WDCK, LRCK, OBPOL, LRPOL, FSEN) The output of the DF1750 can be interfaced to many different devices by programming the output interface pins. These pins provide the following functions:

a. Output control clocks, BCK, WDCK, LRCK I/O selection (FSEN).

FSEN = H; BCK WDCK, LRCK = Input FSEN = L; BCK WDCK, LRCK = Output

- b. Sampling rate clock (LRCK) When FSEN = H, apply a 50% duty cycle sampling frequency (fs) to pin LRCK. When FSEN = L, a fs clock generated from the system clock is available at pin LRCK.

- F1750 c. Word Clock (WDCK) When FSEN = L, WDCK provides a 2fs clock that is derived from the system clock.

- d. Output bit clock When FSEN = H, apply a 64fs clock to pin BCK. When FSEN = L, a 64fs clock generated from the system 8.3 clock is available at pin BCK.

- e. LRCK polarity selection ( $\overline{LRPDL}$ )  $\overline{LRPOL} = H$ ; Lch/Rch = Low/High  $\overline{LRPOL} = L$ ; Lch/Rch = High/Low (Regardless of LRCK's I/O mode).

f. BCK polarity selection (OBPOL)  $\overline{OBPOL} = H$ ; DOUT changes state at rising edge of BCK.  $\overline{OBPOL} = L$ ; DOUT changes state at falling edge of BCK.

(Regardless of BCK's I/O mode).

g. Timing relation between XTI and BCK, WDCK, LRCK clocks.

When  $\overline{\text{FSEN}}$  = H, clocks to BCK and LRCK must be synchronized to XTI. However, there is no limit on their phase differences (between XTI and BCK, LRCK clocks).

BURR-BROWN® Burr-Brown IC Data Book—Data Conversion Products

8.3.167

PRODUCTS-DF

DIO

AUD

DIGITAL

#### SERIAL DATA OUTPUT

The number of bits per output data word is selected with the  $\overrightarrow{OW20}$  pin. With  $\overrightarrow{OW20}$  = H a 16-bit output is selected and with  $\overrightarrow{OW20}$  = L a 20-bit output is selected.

The serial output data format is two's complement and MSB first. The left and right channel outputs are alternated, with the left channel preceeding the right channel. Each data word is allocated in each pulse of LRCK and the LSB is located at the end of the LRCK pulse as shown in Figure 8. The output of the DF1750 can be muted by the use of the MUTE pin. When MUTE = L, the output stays low (muted). Under normal operation MUTE = H.

| LRCK   | -  |   |          | ſ |          | } |

|--------|----|---|----------|---|----------|---|

| (LRPOL | н) |   |          |   |          |   |

|        |    |   | Lch WORD |   | Rch WORD |   |

| DOUT   |    | M | SB LSB   |   | MSBLSB   |   |

| 100 C  |    |   |          |   |          |   |

FIGURE 8. Output Timing.

# TIMING DIAGRAMS

Burr-Brown IC Data Book—Data Conversion Products