The BU97711 is a character display LCD controller/driver that has a key scan function and an LED display. The IC can display 10 characters in one or two lines. With a serial interface control circuit and an LCD drive power supply circuit, the IC allows configuration of a compact application.

#### Applications

Cellular phones, fax machines, printers, and audio systems

#### ●Features

- 1) 4-line serial interface control.

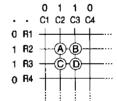

- 2)  $6 \times 6$  key matrix interface.

- 3) 3 bit LED driver.

- 4) Data of 240 characters installed.

- 5) 8 characters can be defined by the user.

- 6) Up to 50 segments can be displayed.

- 7) LCD drive power supply circuit.

- 8) Operation with low voltage and low power dissipation is possible.

# ●Absolute maximum ratings (Ta=25℃)

| Parameter              | Symbol | Limits               | Unit |  |

|------------------------|--------|----------------------|------|--|

| Power supply voltage 1 | Voo    | -0.3~+7.0            | ٧    |  |

| Power supply voltage 2 | VLCD   | -0.3~+7.0            | V    |  |

| D                      |        | 1000*1               |      |  |

| Power dissipation      | Pd -   | 1500*2               | mW   |  |

| Operating temperature  | Topr   | -20~ <del>+</del> 75 | °C   |  |

| Storage temperature    | Tstg   | -55~+125             | ా    |  |

<sup>\*1</sup> Data refers to independent IC; power dissipation drops by 10mW for every 1°C above 25°C.

# ●Recommended operating conditions (Ta=25°C, Vss=0V)

| Parameter                | Symbol | Min. | Тур. | Мах. | Unit |

|--------------------------|--------|------|------|------|------|

| Supply voltage 1         | VDD    | 2.7  | _    | 5.5  | ٧    |

| Supply voltage 2 *3      | VLCD   | 2.7  |      | 6.0  | ٧    |

| Oscillation frequency *4 | fosc   | 40   | 70   | 100  | kHz  |

| Key contact resistance   | Rkc    | 0    |      | 5    | kΩ   |

<sup>\*3</sup> Should satisfy  $V_{LCD} \ge V_C \ge V_1 \ge V_2 \ge V_3 \ge V_4 \ge V_{S9}$

# ●Model name list

| Model Number | Bullt-in font |

|--------------|---------------|

| BU97711-00   | ROM Ver.00    |

LCD drivers (Single chip controller drivers)

<sup>\*2</sup> When a 70mm x 70mm x 1.6mm board is mounted; power dissipation drops by 15mW for every 1°C above 25°C.

<sup>\*4</sup> Rf=2.2MΩ

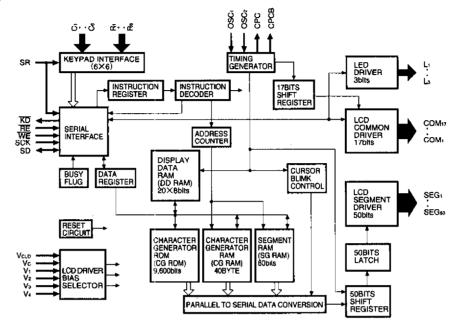

## Block diagram

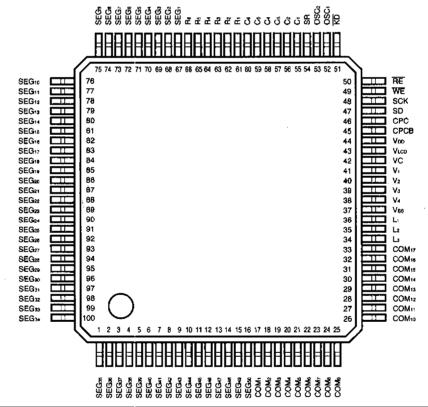

●Pin layout

# Pin descriptions

| Pin NO.                             | Pin name       | Туре | Function                                                                                                                                                                                                                                                                  |

|-------------------------------------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L1∼L3                               | 36~34          | 0    | Output pins for the LED drive; output FET is turned ON when "1" is written to the LED register, and the output FET and the LED are turned OFF when "0" is written to the LED register                                                                                     |

| COM <sub>17</sub> ~COM <sub>1</sub> | 33~17          | 0    | Output pins for the LCD drive; connected to the common terminal of the LCD panel; all the pins output at the $V_{\text{LCD}}$ level when the display is OFF                                                                                                               |

| SEG50~SEG1                          | 16~1<br>100~67 | 0    | Segment output pins for the LCD drive; connected to the segment terminal of the LCD panel; all the pins output at the $V_{\text{LCD}}$ level when the display is OFF                                                                                                      |

| R₁~R6<br>C1~C6                      | 61~66<br>55~60 | 1/0  | Keypad output pins; a keypad (up to 6 X 6) can be configured with single contact key switches                                                                                                                                                                             |

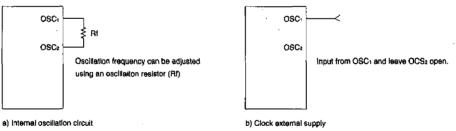

| OSC₁<br>OSC₂                        | 52<br>53       | -0   | Internal oscillator I/O pins; connect a resistor between the pins when the internal clock is operating; input from OSC <sub>1</sub> and leave OSC <sub>2</sub> open when the external clock is operating                                                                  |

| KD                                  | 51             | 0.   | Key press-down output pin; after a key is pressed down, the output is LOW level with the ON debounce effective; after a key is released, the output is ZERO (high impedance) with the OFF debounce effective                                                              |

| RE                                  | 50             | 1    | Read enable input pin; read mode at LOW level; data is read to the output serial register at the signal falling edge                                                                                                                                                      |

| WE                                  | 49             | l    | Light enable input pin; light mode at LOW level; data is read to the register at the signal rising edge when writing data to the LED port                                                                                                                                 |

| SCK                                 | 47             | ı    | Shift clock input pin for serial data; data is read bit-by-bit from the SD pin at the signal rising edge when RE is LOW level; data is written bit-by-bit from the SD pin at the signal falling edge when WE is LOW level                                                 |

| SD                                  | 48             | 1/0  | Serial data I/O pin; data format-related data is input and output; RE is LOW level and WE is HIGH level in the data output mode; "Z" (high impedance) if not in the output mode                                                                                           |

| SR                                  | 54             | 1 .  | Input pin for clearing the standby mode; input is possible even when RE and WE are both LOW level; the standby mode is released at LOW level; because the resistance is pulled up, the standby release key is configured by connecting a single contact key switch to Vss |

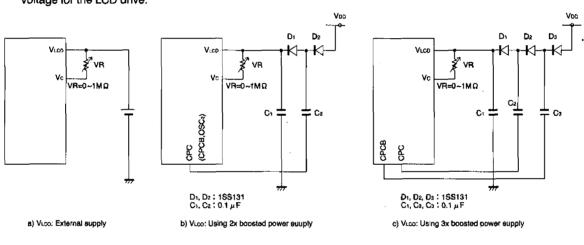

| CPC<br>CPCB                         | 46<br>45       | 0    | Output pin for booster circuit drive; booster power supply for V <sub>LCD</sub> an be configured with external diodes and capacitors                                                                                                                                      |

| VLCD<br>V1~V4                       | 43<br>41~38    |      | LCD power supply pin; should satisfy (High) V <sub>LCD</sub> ≧V <sub>C</sub> ≧V <sub>1</sub> ≧V <sub>2</sub> ≥V <sub>3</sub> ≧V <sub>4</sub> ≥V <sub>SS</sub> (Low)                                                                                                       |

| <b>V</b> c                          | 42             |      | Contrast adjustment pin                                                                                                                                                                                                                                                   |

| Voo                                 | 44             |      | V <sub>DD</sub> pin                                                                                                                                                                                                                                                       |

| Vss                                 | 37             |      | V <sub>SS</sub> pin                                                                                                                                                                                                                                                       |

# ●Input/output circuit

| Pin name          | 1/0        | Equivalent circuit | Pin name             | 1/0 | Equivalent circuit                      | Pin name                   | 1/0 | Equivalent circuit   |

|-------------------|------------|--------------------|----------------------|-----|-----------------------------------------|----------------------------|-----|----------------------|

| SCK,<br>SE,<br>RE | IN         | IN GND             | CPC,<br>CPCB         | OUT | VDD<br>OUT<br>GND                       | Vc<br>V1<br>V2<br>V3<br>V4 |     | V <sub>0</sub>       |

| SD                | IN/<br>OUT | VOD IN/OUT IN/OUT  | KD<br>L1<br>L2<br>L3 | IN  | OUT                                     |                            |     | V <sub>2</sub> → GND |

| SEGn<br>COMn      | OUT        | OUT VICE           | SR                   | IN  | VDD ★ ★ ★ ★ ★ ★ ★ ★ ★ ★ ★ ★ ★ ★ ★ ★ ★ ★ |                            |     | <i>777</i> G16       |

| Rn<br>Cn          | IN/<br>OUT | VDD IN/OUT         | OSC1<br>OSC2         |     | IN A GND                                |                            |     |                      |

| Parameter                   | Symbol           | Min.                | Тур. | Max.                | Unit | Conditions               | Pin.                      |  |

|-----------------------------|------------------|---------------------|------|---------------------|------|--------------------------|---------------------------|--|

| HIGH level input voltage    | Vıhı             | 0.8×V <sub>DD</sub> | _    | Von                 | ٧    |                          | OSC1,RE,WE,<br>SCK,SD,SR, |  |

| LOW level input voltage     | VIL1             | 0                   | _    | 0.2×VDD             | ٧    |                          | R₁∼R₅<br>C₁∼C₅            |  |

| COM driver ON resistance    | Ясом             | -                   | _    | 20                  | kΩ   | Id=±50 μ A               | COM1~17                   |  |

| SEG driver ON resistance    | Rseo             | _                   |      | 30                  | kΩ   | Id=±50 μ A               | SEG1~50                   |  |

| Input current               | liN1             | -1                  |      | 1                   | μΑ   | VIN=0~VDD                | RE,WE,SCK,SD              |  |

| HIGH level output voltage 1 | V <sub>OH1</sub> | 0.8×V <sub>DD</sub> | _    | <u> </u>            | V    | lон=−100 μ A             | SD                        |  |

| LOW level output voltage 1  | V <sub>OL1</sub> | _                   | _    | 0.2×V <sub>DD</sub> | V    | loc=100 μ A              | SD,KD                     |  |

| LOW I I I I I               | V                |                     | _    | 0.7                 | V    | VDD=5V, IOL=60mA         |                           |  |

| LOW level output voltage 2  | Volz             | _                   |      | 0.9                 | V    | VDD=3V, IoL=60mA         | - L1,L2                   |  |

|                             |                  |                     |      | 0.5                 | ٧    | Von=5V, loL=10mA         |                           |  |

| LOW level output voltage 3  | Vol3             |                     | _    | 0.7 V VDD=3V, IOL=1 |      | VDD=3V, IOL=10mA         | – L3                      |  |

|                             |                  | _                   | 35   | 60                  | μА   | fosc=70kHz, without load |                           |  |

| Current consumption         | IDD              |                     | _    | 2                   | μА   | Standby mode             | Voo                       |  |

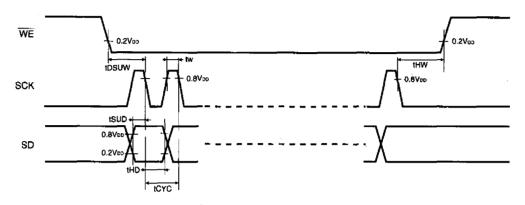

# AC characteristics (unless otherwise noted, V<sub>DD</sub>=2.7~5.5V, V<sub>SS</sub>=0V, and Ta=25°C)

| Parameter                   | Symbol            | Mln. | Тур.     | Max. | Unit | Conditions               |

|-----------------------------|-------------------|------|----------|------|------|--------------------------|

| Clock (fosc) characteristic | cs                |      |          |      |      | -                        |

| Operating frequency         | fin               | _    | T —      | 200  | kHz  | External clock operating |

| Clock duty ratio            | 1 <sub>Duty</sub> | 45   | 50       | 55   | %    | 1                        |

| Clock rise time             | tr                |      | _        | 100  | ns   |                          |

| Clock fall time             | tr                |      | <u> </u> | 100  | ns   |                          |

| Serial interface timing cha | aracteristics     |      |          |      |      |                          |

| SCK cycle time              | fovo              | 400  |          | _    | ns   |                          |

| SCK pulse width             | fw                | 100  | _        | _    | ns   |                          |

ROHM

LCD drivers (Single chip controller drivers)

Standard ICs BU97711

| Parameter                    | Symbol      | Min. | Тур.      | Max. | Unit | Conditions     |

|------------------------------|-------------|------|-----------|------|------|----------------|

| Setup time 1                 | tsuw        | 100  | _         |      | ns   | WE→SCK         |

| Setup time 2                 | tsuo        | 100  |           | _    | ns   | SD→SCK         |

| Setup time 3                 | tsun        | 100  | _         |      | ns   | RE→SCK         |

| Setup time 4                 | tsuk        | 100  | _         |      | ns   | KD→RE          |

| Hold time 1                  | thw         | 100  | _         | _    | ns   | SCK→WE         |

| Hold time 2                  | thb         | 100  |           |      | ns   | SCK→SD         |

| SD output delay time         | too         |      | -         | 150  | ns   | SCK→SD,CL=30pF |

| Key interface characteristic | :5          |      |           |      |      | -              |

|                              |             | T    | 1500/fosc | _    | s    | B1=1,B2=0,B3=0 |

| Key ON debounce time         | toen        |      | 800/fosc  | _    | s    | B1=0,B2=1,B3=0 |

|                              |             |      | 400/fosc  | _    | s    | B1=0,B2=0,B3=1 |

|                              |             |      | 2400/fosc | +    | s    | B1=1,B2=0,B3=0 |

| Key OFF debounce time        | toer        |      | 1400/fosc | _    | s    | B1=0,B2=1,B3=0 |

|                              |             |      | 650/fosc  | _    | s    | B1=0,B2=0,B3=1 |

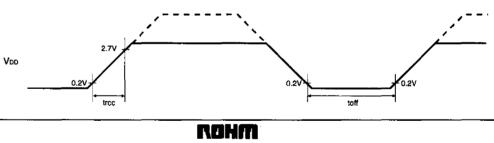

| Power supply characteristic  | s when rese | t    |           |      |      |                |

| Power supply rise time       | troc        | 0.05 | _         | 10   | ms   |                |

| Power supply fall time       | toff        | 1    | _         |      | ms   |                |

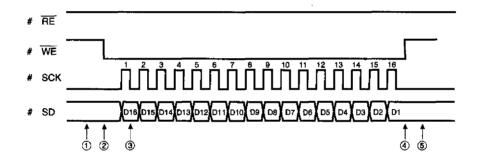

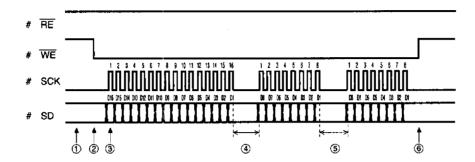

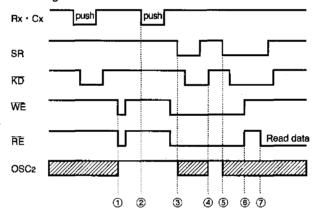

# Interface timing

# OSerial data input timing

# OSerial data output timing

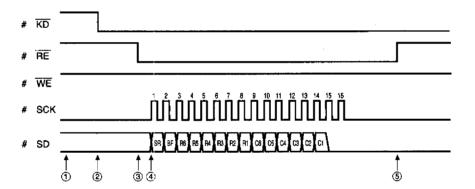

# Power supply characteristics

When initialization is carried out in the internal reset circuit at start-up, the power supply characteristics described below should be satisfied.

LCD drivers

LCD drivers (Single chip controller drivers)

Standard ICs BU97711

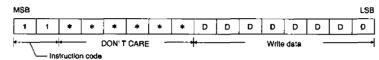

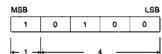

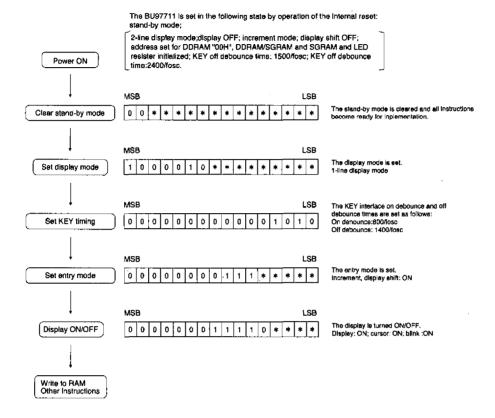

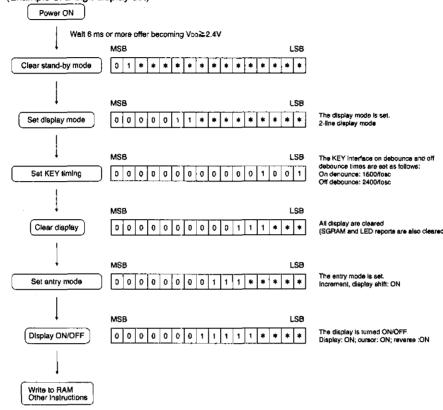

#### Data format

Serial data is transferred by a 4-line clock synchronous communication system. The I/O of serial data is synchronized with SCK. The following modes are selected according to the status of  $\overline{\text{RE}}$  and  $\overline{\text{WE}}$ . Either data input or output is carried out sequentially from MSB.

| RE | WE | Operating mode                                           |

|----|----|----------------------------------------------------------|

| Н  | н  | Normal (waiting for instruction)<br>Stop when SCK is LOW |

| н  | L  | Write mode                                               |

| L  | Н  | Read mode                                                |

| L  | L  | Standby mode                                             |

Serial data is input and output as 16-bit data. Execution of each instruction starts after the transfer of the final bit is confirmed. While an instruction is executed, no command can be executed except "SR/BF/key data read," "SR/BF/LED register read," and "LED register write." The busy flag is "1" (busy state) until the end of an instruction. Therefore, the MPU has to confirm that the busy flag is "0" (not busy) before sending an instruction to BU97711. If a next instruction is successively transferred without checking the busy flag, a transfer wait time longer than the instruction execution time is needed. A next instruction is ignored if the last bit of the instruction is received while a previous instruction is being executed.

Note: The RE and WE pins must be in the normal sate (RE=WE="H") and the SCK pin must be LOW before executing an instruction.

#### List of instructions

|                           |                                                   | Code                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                   |                                                    |                                                      |                      |        | Execution                                        |            |                                                 |                                               |                                                  |                                  |      |            |                                                                                                                 |                      |

|---------------------------|---------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------|----------------------|--------|--------------------------------------------------|------------|-------------------------------------------------|-----------------------------------------------|--------------------------------------------------|----------------------------------|------|------------|-----------------------------------------------------------------------------------------------------------------|----------------------|

| Instruction               | D16                                               | D15                                                               | D14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | D13                                                               | D12                                                | D11                                                  | D10                  | D9     | D8                                               | D7         | D6                                              | D5                                            | D4                                               | D3                               | D2   | D1         | Function                                                                                                        | time<br>(fosc=70kHz) |

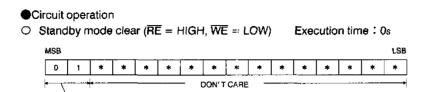

| Standby mode clear        | 0                                                 | 1                                                                 | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | *                                                                 | *                                                  | *                                                    | *                    | *      | *                                                | *          | *                                               | *                                             | *                                                | *                                | *    | *          | Clears the standby mode; oscillation starts and all instructions become executable                              | os                   |

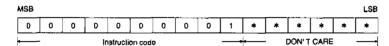

| KEY SCAN<br>timing set    | 0                                                 | 0                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                 | 0                                                  | 0                                                    | 0                    | 0      | 0                                                | 0          | 0                                               | 0.                                            | 1                                                | вз                               | B2   | <b>B</b> 1 | Sets ON and OFF debounce times when a key is pressed down                                                       | 143us                |

| Display clear             | Ó                                                 | 0                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                 | 0                                                  | 0                                                    | 0                    | 0      | 0                                                | 0          | 1                                               | L                                             | SG                                               | *                                | *    | *          | LCD is cleared and the DDRAM address 0 is set to the address counter                                            | 286us                |

| Return home               | 0                                                 | 0                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | o                                                                 | 0                                                  | 0                                                    | 0                    | 0      | 0                                                | 1          | *                                               | *                                             | *                                                | *                                | *    | *          | DDRAM address 0 is set to the address<br>counter, display shift is cleared, and<br>DDRAM contents are unchanged | 286us                |

| Entry mode set            | 0                                                 | 0                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                 | 0                                                  | 0                                                    | 0                    | 0      | 1                                                | I/D        | \$                                              | *                                             | *                                                | *                                | *    | *          | Sets the cursor direction and the display shift; carries out the operation designated during RAM data writing   | 143us                |

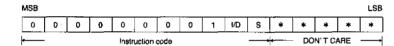

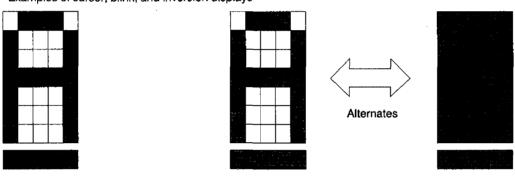

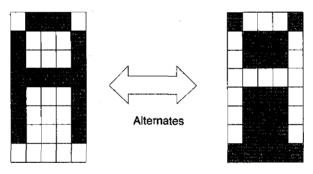

| Display ON/OFF            | 0                                                 | o                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                 | o                                                  | 0                                                    | o                    | 1      | D                                                | С          | в                                               | R                                             | *                                                | *                                | *    | *          | Sets LCD ON/OFF, cursor ON/OFF,<br>and blink/inversion of the cursor<br>position character                      | 143us                |

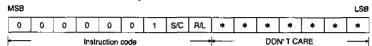

| Cursor/display<br>shift   | 0                                                 | 0                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                 | 0                                                  | 0                                                    | 1                    | S/C    | R/L                                              | *          | *                                               | *                                             | *                                                | *                                | *    | *          | Shifts the cursor movement and the display without changing the DDRAM contents                                  | 143us                |

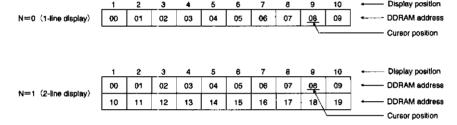

| Display mode set          | 0                                                 | 0                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                 | 0                                                  | 1                                                    | N                    | *      | *                                                | *          | *                                               | *                                             | *                                                | *                                | *    | *          | Sets one- or two-line display mode                                                                              | 143us                |

| SGRAM<br>address set      | 0                                                 | 0                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                 | 1                                                  |                                                      | ADD                  | RES    | s                                                | *          | *                                               | *                                             | *                                                | *                                | *    | *          | Sets the SGRAM address; the data to be followed is SGRAM data                                                   | 143us                |

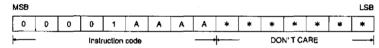

| DDRAM<br>address set      | 0                                                 | 0                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                 |                                                    | AC                                                   | DRE                  | \$\$   |                                                  | *          | *                                               | *                                             | *                                                | *                                | *    | *          | Sets the DDRAM address; the data to be followed is DDRAM data                                                   | 143us                |

| CGRAM<br>address set      | 0                                                 | 0                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                   | ,                                                  | ADD                                                  | RES                  | 5      |                                                  | *          | *                                               | *                                             | *                                                | *                                | *    | *          | Sets the CGRAM address; the data to be followed is CGRAM data                                                   | 143us                |

| SR/BF/<br>key data read   | SR                                                | BF                                                                | R6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R5                                                                | F14                                                | R3                                                   | R2                   | R1     | Св                                               | <b>C</b> 5 | C4                                              | СЗ                                            | C2                                               | C1                               | 0    | 0          | Reads SR pin status, BF status that indicates internal operation, and key data                                  | os                   |

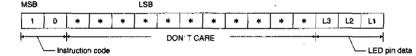

| LED register write        | 1                                                 | 0                                                                 | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | *                                                                 | *                                                  | *                                                    | *                    | *      | *                                                | *          | *                                               | *                                             | *                                                | L3                               | L2   | L1         | Controls LED port ON/OFF; ON when "1"                                                                           | os                   |

| CG/DD/SGRAM<br>data write | 1                                                 | 1                                                                 | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | *                                                                 | *                                                  | *                                                    | *                    | *      |                                                  |            | RAM                                             | WR                                            | ITE I                                            | DAT                              | 4    |            | Writes data to the CGRAM, DDRAM, or SGRAM                                                                       | 143us                |

|                           | Ke                                                | y inte                                                            | orface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | e tim                                                             | ing is                                             | tea                                                  | by B                 | 1, B2  | , and                                            | 1 B3       |                                                 |                                               |                                                  |                                  |      |            | 1                                                                                                               |                      |

|                           | В                                                 | 1 B                                                               | 2 E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 33                                                                | ON (                                               | odet                                                 | unce                 | time   | C                                                | FF d       | l <b>e</b> bot                                  | ınce                                          | time                                             |                                  |      |            |                                                                                                                 | }                    |

|                           | 1_1                                               | (                                                                 | ) (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | D                                                                 | 1                                                  | 1500.                                                | ∕tos                 | 0      |                                                  | 24         | 100/                                            | 1osc                                          |                                                  | _                                |      |            |                                                                                                                 |                      |

|                           | _0                                                | <u>'</u>                                                          | ' '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                 |                                                    | 800/                                                 | /fosc                | ;      | $\perp$                                          | 14         | 100/                                            | fosc                                          | ;                                                | _                                |      |            |                                                                                                                 |                      |

|                           | 0                                                 | <u> </u>                                                          | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                 |                                                    | 400/                                                 | ∕fosc                | ;      |                                                  | 6          | 50/                                             | fosc                                          |                                                  | _                                |      |            |                                                                                                                 |                      |