## High-Performance Programmable Audio Processing System

### Introduction

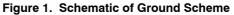

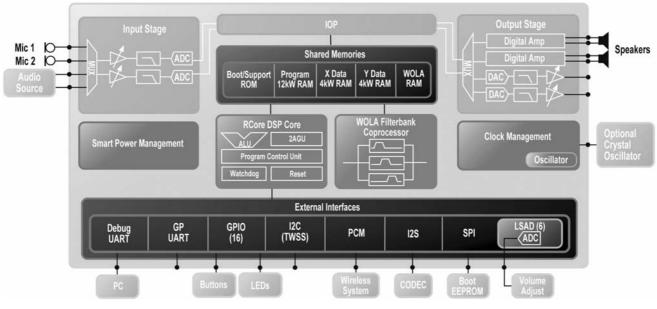

BELASIGNA<sup>®</sup> 250 is a complete programmable audio processing system, designed specifically for ultra-low-power embedded and portable digital audio systems. This high-performance chip builds on the architecture and design of BELASIGNA 200 to deliver exceptional sound quality along with unmatched flexibility.

BELASIGNA 250 incorporates a full audio signal chain, from stereo 16-bit A/D converters or digital interfaces to accept the signal, through the fully flexible digital processing architecture, to stereo analog line-level or direct digital power outputs that can connect directly to speakers.

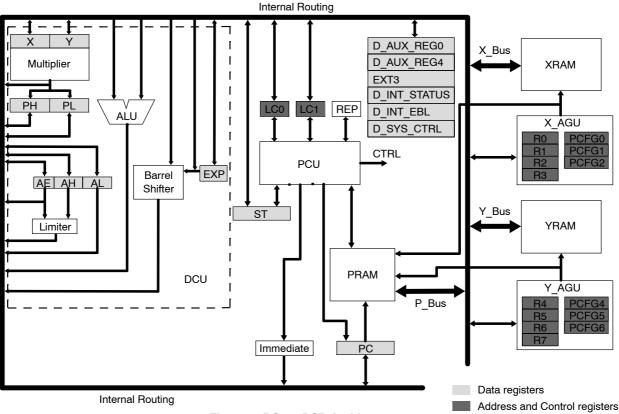

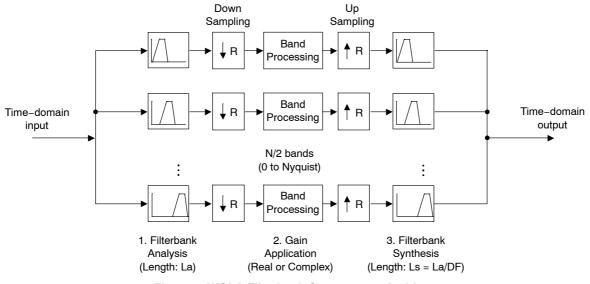

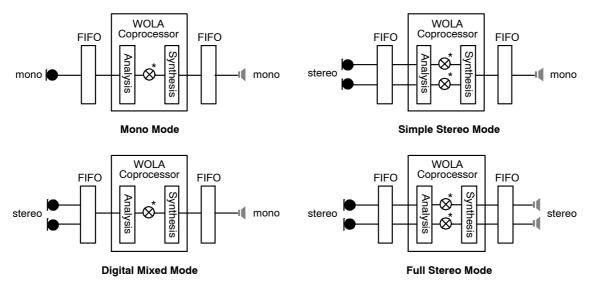

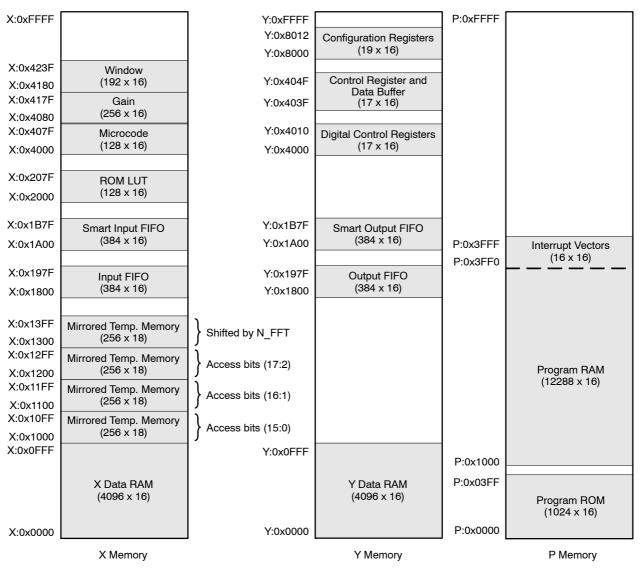

BELASIGNA 250 features flexible clocking options and smart power management features including a soft power-down mode. Two DSP subsystems operate concurrently: the RCore, which is a fully software programmable DSP core, and the weighted overlap-add (WOLA) filterbank coprocessor, which is a dedicated, configurable processor that executes time-frequency domain transforms and other vector- based computations. A full range of other hardware-assisted features, such as audio-targeted DMA complete the system.

A comprehensive and easy-to-use suite of development tools, hands-on training and full technical support are available to enable rapid development and introduction of highly differentiated products in record time.

### **Key Features**

- Unique Parallel-processing Architecture: A Complete DSP-based, Mixed-signal Audio System Consisting of a 16-bit Fully Programmable Dual-Harvard 16-bit DSP Core, a Patented, High-resolution Block Floating-point WOLA Filterbank Coprocessor, and an Input/Output Processor (IOP) along with Several Peripherals and Interfaces which Optimize the Architecture for Audio Processing

- Integrated Converters and Powered Output: Minimize Need for External Components

- Ultra-low Power Consumption: Under 5 mA at 20 MHz to Support Advanced Operations; 1.8 V Supply Voltage

- "Smart" Power Management: Including Low Current Standby Mode Requiring Only 0.05 mA

- Flexible Clocking Architecture: Supports Speeds up to 50 MHz

- Full Range of Configurable Interfaces: Including: I<sup>2</sup>S, PCM, UART, SPI, I<sup>2</sup>C, TWSS, GPIO

- Excellent Fidelity: 88 dB System Dynamic Range, Exceptionally Low System Noise and Low Group Delay

- **Support for IP Protection:** to Prevent Unauthorized Access to Algorithms and Data

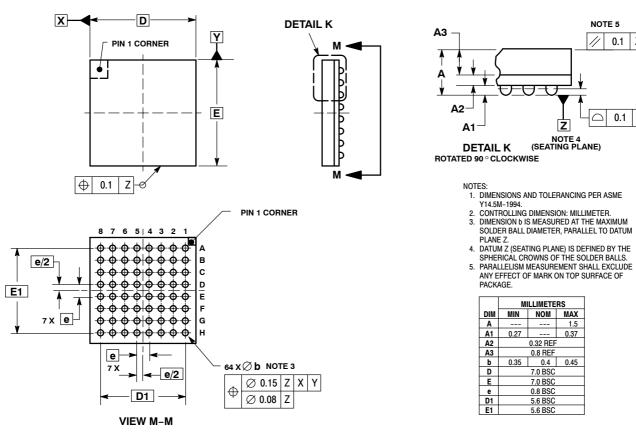

- Available in CABGA and LFBGA Package Options

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

### **ON Semiconductor®**

http://onsemi.com

### **ORDERING INFORMATION**

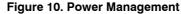

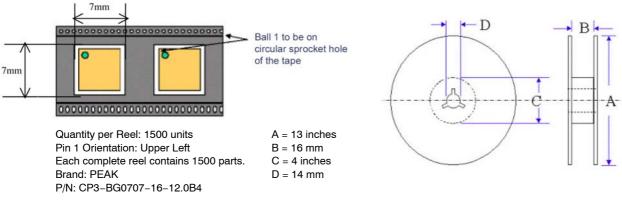

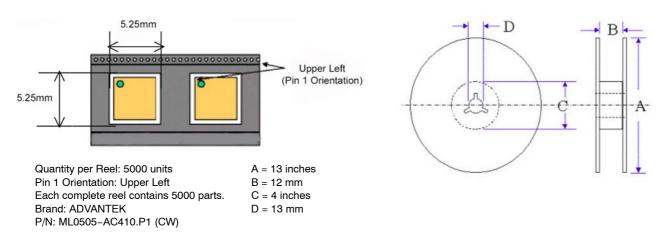

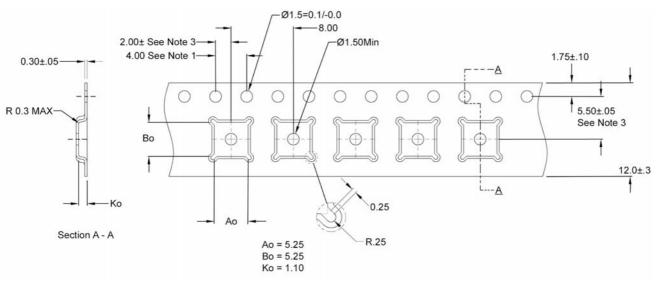

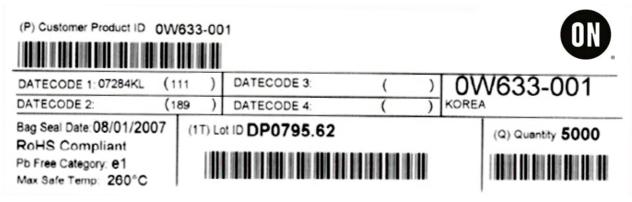

See detailed ordering and shipping information in the package dimensions section on page 28 of this data sheet.

### **Figures and Data**

### Table 1. ABSOLUTE MAXIMUM RATINGS

| Parameter                                                | Min  | Max | Unit |

|----------------------------------------------------------|------|-----|------|

| Voltage at any input pin                                 | -0.3 | 2.2 | V    |

| Operating supply voltage (Note 1)                        | 0.9  | 2.0 | V    |

| Operating temperature range (Note 2)                     | -40  | 85  | °C   |

| Storage temperature range                                | -40  | 125 | °C   |

| Caution: Class 2 ESD Sensitivity, JESD22-A114-B (2000 V) | •    | •   | •    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Below 1.05 V audio performance will be degraded.

Parameters may exceed listed tolerances when out of the temperature range 0 to 50°C.

### **Electrical Performance Specifications**

The parameters in Table 2 do not vary with WOLA filterbank configuration. The tests were performed at 20°C with a clean 1.8 V supply voltage. BELASIGNA 250 was running in high voltage mode (VDDC = 1.8 V). The system clock (SYS\_CLK) was set to 5.12 MHz and a sampling frequency of 16 kHz was used with MCLK was set to 1.28 MHz.

Parameters marked as screened are tested on each chip. Other parameters are qualified but not tested on every part.

### **Table 2. ELECTRICAL SPECIFICATIONS**

| Description                      | Symbol                   | Conditions                                  | Min             | Тур  | Max  | Units | Screened     |

|----------------------------------|--------------------------|---------------------------------------------|-----------------|------|------|-------|--------------|

| OVERALL                          | •                        |                                             |                 |      |      |       |              |

| Supply voltage                   | V <sub>BAT</sub>         |                                             | 0.9<br>(Note 3) | 1.8  | 2.0  | V     |              |

| Current consumption              | I <sub>BAT</sub>         | SYS_CLK = 1.28 MHz,<br>sample rate = 16 kHz | -               | 650  | -    | μΑ    |              |

|                                  |                          | 5.12 MHz, 16 kHz                            | -               | 1    | -    | mA    |              |

|                                  |                          | 19.2 MHz, 16 kHz                            | -               | 5    | -    | mA    |              |

|                                  |                          | 49.152 MHz, 16 kHz                          | -               | 10   | -    | mA    |              |

|                                  |                          | 49.152 MHz, 48 kHz                          | -               | 13   | -    | mA    |              |

| VREG (1 µF External Capacitor)   |                          |                                             |                 |      |      |       |              |

| Regulated voltage output         | V <sub>REG</sub>         |                                             | 0.95            | 1.00 | 1.05 | V     | $\checkmark$ |

| Regulator PSRR                   | V <sub>REG_PSRR</sub>    | 1 kHz                                       | 50              | 55   |      | dB    |              |

| Load current                     | I <sub>LOAD</sub>        |                                             | -               | -    | 2    | mA    |              |

| Load regulation                  | LOAD <sub>REG</sub>      |                                             | -               | 11   | 20   | mV/mA |              |

| Line regulation                  | LINE <sub>REG</sub>      |                                             | -               | 2    | 5    | mV/V  |              |

| VDBL (1 µF External Capacitor)   | -                        |                                             |                 |      | -    | -     |              |

| Regulated doubled voltage output | VDBL                     |                                             | 1.9             | 2.0  | 2.1  | V     | $\checkmark$ |

| Regulator PSRR                   | VDBL <sub>PSRR</sub>     | 1 kHz                                       | 45              | 50   |      | dB    |              |

| Load current                     | I <sub>LOAD</sub>        |                                             | -               | -    | 2    | mA    |              |

| Load regulation                  | LOAD <sub>REG</sub>      |                                             | -               | 120  | 200  | mV/mA | $\checkmark$ |

| Line regulation                  | LINE <sub>REG</sub>      |                                             | -               | 5    | 10   | mV/V  |              |

| VDDC (1 µF External Capacitor)   |                          |                                             |                 |      |      |       |              |

| Digital supply voltage output    | VDDC                     | LV mode (VREG)                              | 0.9             | 1.0  | 1.1  | V     | $\checkmark$ |

|                                  |                          | DV mode (VDBL)                              | 1.8             | 2.0  | 2.2  | V     | $\checkmark$ |

| Regulator PSRR                   | VDDC <sub>PSRR</sub>     | LV mode; 1 kHz                              | 20              | 28   | -    | dB    |              |

|                                  |                          | DV mode; 1 kHz                              | 40              | 48   | -    | dB    |              |

| Load current                     | I <sub>LOAD</sub>        | All modes                                   | -               | -    | 3.5  | mA    |              |

| VDDC (1 µF External Capacitor)   |                          |                                             |                 |      |      |       |              |

| Load regulation                  | LOAD <sub>REG</sub>      | LV mode                                     | -               | 5    | 10   | mV/mA | $\checkmark$ |

|                                  |                          | DV mode                                     | -               | 150  | 250  | mV/mA | $\checkmark$ |

| Line regulation                  | LINE <sub>REG</sub>      | LV mode                                     | -               | 1.5  | 10   | mV/V  |              |

|                                  |                          | DV mode                                     | -               | 5    | 10   | mV/V  |              |

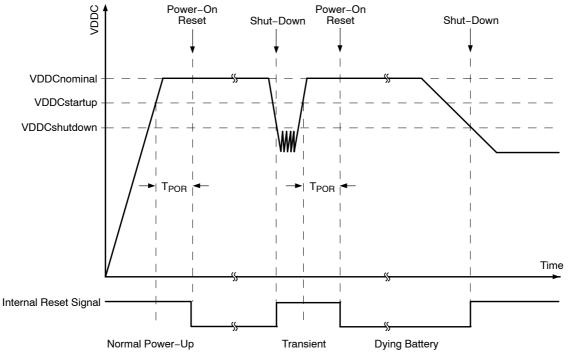

| POWER-ON-RESET (POR)             |                          |                                             | -               |      |      |       |              |

| POR startup voltage              | VDDC <sub>STARTUP</sub>  |                                             | 0.78            | 0.83 | 0.88 | V     |              |

| POR shutdown voltage             | VDDC <sub>SHUTDOWN</sub> | ١                                           | 0.76            | 0.81 | 0.86 | V     |              |

3. Audio performance will be degraded below 1.05 V.

4. Measured with a = 12 dB input signal.

Input stage delay is inversely proportional to sampling frequency.

Max voltage should be limited to 2.2 V peak regardless of VDDC. Protection diodes will be enabled above this voltage.

### Table 2. ELECTRICAL SPECIFICATIONS (continued)

| Description          | Symbol                    | Conditions | Min | Тур | Max | Units | Screened |

|----------------------|---------------------------|------------|-----|-----|-----|-------|----------|

| POWER-ON-RESET (POR) |                           |            |     |     |     |       |          |

| POR hysteresis       | POR <sub>HYSTERESIS</sub> |            | 10  | 16  | 22  | mV    |          |

| POR duration         | T <sub>POR</sub>          |            | 5   | 10  | 15  | ms    |          |

|                      |                           |            |     |     |     |       |          |

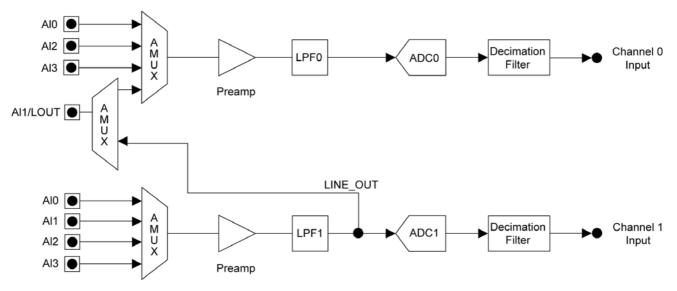

#### INPUT STAGE

| Analog input voltage                           | V <sub>IN</sub>    |                                                           | 0    | -   | 2   | V     |              |

|------------------------------------------------|--------------------|-----------------------------------------------------------|------|-----|-----|-------|--------------|

| Preamplifier gain tolerance                    | PAG                | 1 kHz                                                     | -1.5 | -   | 1.5 | dB    | $\checkmark$ |

| Preamplifier gain mismatch<br>between channels |                    | 1 kHz                                                     | -1   | _   | 1   | dB    |              |

| Input impedance                                | R <sub>IN</sub>    | 0 dB preamplifer gain                                     | -    | 250 | -   | kΩ    |              |

|                                                |                    | Non-zero preamplifier gains                               | 400  | 550 | 700 | kΩ    | $\checkmark$ |

| nput referred noise                            | IN <sub>IRN</sub>  | Unweighted,<br>20 Hz to 8 kHz BW<br>Preamplifier setting: |      |     |     | μVrms |              |

|                                                |                    | 0 dB                                                      | -    | 40  | 55  |       |              |

|                                                |                    | 12 dB                                                     | -    | 12  | 14  |       |              |

|                                                |                    | 15 dB                                                     | -    | 8   | 11  |       |              |

|                                                |                    | 18 dB                                                     | -    | 6   | 8   |       |              |

|                                                |                    | 21 dB                                                     | -    | 4.5 | 5.5 |       |              |

|                                                |                    | 24 dB                                                     | -    | 4   | 5   |       |              |

|                                                |                    | 27 dB                                                     | -    | 3.5 | 4.5 |       |              |

|                                                |                    | 30 dB                                                     | -    | 3   | 4   |       |              |

| Input dynamic range                            | IN <sub>DR</sub>   | 1 kHz, 20 Hz to 8 kHz BW<br>Preamplifier setting:         |      |     |     | dB    |              |

|                                                |                    | 0 dB                                                      | 85   | 88  | -   |       |              |

|                                                |                    | 12 dB                                                     | 84   | 87  | -   |       |              |

|                                                |                    | 15 dB                                                     | 84   | 87  | -   |       |              |

|                                                |                    | 18 dB                                                     | 83   | 86  | -   |       |              |

|                                                |                    | 21 dB                                                     | 82   | 85  | -   |       |              |

|                                                |                    | 24 dB                                                     | 81   | 84  | -   |       |              |

|                                                |                    | 27 dB                                                     | 80   | 83  | -   |       |              |

|                                                |                    | 30 dB                                                     | 78   | 81  | -   |       |              |

| Input peak THD+N (Note 4)                      | IN <sub>THDN</sub> | Any valid preamplifier gain,<br>1 kHz                     | _    | -63 | -60 | dB    | $\checkmark$ |

| Input stage delay (Note 5)                     | 1                  | Ì                                                         | -    | 200 | -   | μs    |              |

#### DIRECT DIGITAL OUTPUT

| I <sub>DO</sub>    | Normal mode                              | -                                                                                                                                | -                                                                                                                                                                                                                       | 13                                                                                                                                                                                           | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | High power mode                          | -                                                                                                                                | -                                                                                                                                                                                                                       | 25                                                                                                                                                                                           | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| R <sub>DO</sub>    | Normal mode                              | -                                                                                                                                | 9                                                                                                                                                                                                                       | 11                                                                                                                                                                                           | Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | High power mode                          | -                                                                                                                                | 5                                                                                                                                                                                                                       | 6                                                                                                                                                                                            | Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DO <sub>DR</sub>   | Unweighted, 100 Hz to<br>8 kHz BW, mono  | 90                                                                                                                               | 93                                                                                                                                                                                                                      | -                                                                                                                                                                                            | dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DO <sub>THDN</sub> | Unweighted, 100 Hz to<br>22 kHz BW, mono |                                                                                                                                  | -79                                                                                                                                                                                                                     | -76                                                                                                                                                                                          | dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DO <sub>VOUT</sub> |                                          | -Vbat                                                                                                                            |                                                                                                                                                                                                                         | Vbat                                                                                                                                                                                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -                  | DO <sub>DR</sub>                         | High power mode   RDO Normal mode   High power mode   DODR Unweighted, 100 Hz to   DOTHDN Unweighted, 100 Hz to   2 kHz BW, mono | High power mode -   R <sub>DO</sub> Normal mode -   High power mode -   High power mode -   DO <sub>DR</sub> Unweighted, 100 Hz to<br>8 kHz BW, mono 90   DO <sub>THDN</sub> Unweighted, 100 Hz to<br>22 kHz BW, mono - | High power mode -   RDO Normal mode -   High power mode - 9   High power mode - 5   DODR Unweighted, 100 Hz to<br>8 kHz BW, mono 90 93   DOTHDN Unweighted, 100 Hz to<br>22 kHz BW, mono -79 | $\frac{1}{1} \frac{1}{1} \frac{1}$ | $\frac{1}{1} \frac{1}{1} \frac{1}$ |

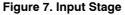

### ANALOG OUTPUT STAGE

| Analog output voltage | V <sub>OUT</sub> | 0 | - | 2 | V |  |

|-----------------------|------------------|---|---|---|---|--|

|                       |                  |   |   |   |   |  |

Audio performance will be degraded below 1.05 V.

Measured with a = 12 dB input signal.

Input stage delay is inversely proportional to sampling frequency.

Max voltage should be limited to 2.2 V peak regardless of VDDC. Protection diodes will be enabled above this voltage.

### Table 2. ELECTRICAL SPECIFICATIONS (continued)

| Description                                       | Symbol               | Conditions                                                                                  | Min                                  | Тур                                    | Max                                     | Units | Screened     |

|---------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------|-----------------------------------------|-------|--------------|

| ANALOG OUTPUT STAGE                               |                      |                                                                                             |                                      |                                        |                                         |       |              |

| Attenuator gain tolerance                         | ATG                  | Input is –6 dB re: full scale @<br>1 kHz (all preamplifier gains)                           | -1                                   | -                                      | 1                                       | dB    | $\checkmark$ |

| Output impedance                                  | R <sub>OUT</sub>     | Attenuator settings:<br>0 dB<br>12 dB<br>15 dB<br>18 dB<br>21 dB<br>24 dB<br>27 dB<br>30 dB | 1<br>9<br>7<br>4<br>3<br>2<br>1<br>1 | 2<br>13<br>10<br>8<br>6<br>4<br>3<br>2 | 5<br>17<br>14<br>12<br>9<br>7<br>6<br>5 | kΩ    | V            |

| Output noise                                      | OUT <sub>N</sub>     | 0 dB attenuation                                                                            | -                                    | 33                                     | 40                                      | μV    |              |

| Output dynamic range                              | OUT <sub>DR</sub>    | Unweighted, 100 Hz to<br>8 kHz BW, mono                                                     | 85                                   | 87                                     | -                                       | dB    |              |

| Output THD+N                                      | OUT <sub>THDN</sub>  | Unweighted, 100 Hz to<br>22 kHz BW, mono                                                    | -                                    | -70                                    | -67                                     | dB    |              |

| ANTI-ALIASING FILTERS (Input a                    | nd Output)           |                                                                                             |                                      |                                        |                                         |       |              |

| Preamplifier filter cut-off frequency             |                      | Preamp not bypassed                                                                         | -                                    | 25                                     | -                                       | kHz   |              |

| Digital anti-aliasing filter cut-off<br>frequency |                      |                                                                                             | -                                    | f <sub>s</sub> /2                      | -                                       |       |              |

| Analog output cut-off frequency                   |                      | 25 kHz                                                                                      | 15                                   | 25                                     | 35                                      | kHz   |              |

|                                                   |                      | 12 kHz (only output filter)                                                                 | 9                                    | 12                                     | 15                                      | kHz   |              |

| Passband flatness                                 |                      |                                                                                             | -1                                   | -                                      | 1                                       | dB    |              |

| Stopband attenuation                              |                      | 60 kHz (12 kHz cut–off)                                                                     | -                                    | 60                                     | -                                       | dB    |              |

| LOW-SPEED A/D                                     |                      |                                                                                             |                                      |                                        |                                         |       |              |

| Input voltage                                     |                      | Peak input voltage                                                                          | 0                                    | -                                      | 2.0                                     | V     | $\checkmark$ |

| INL                                               |                      | From GND to 2*VREG                                                                          | -                                    | -                                      | 10                                      | LSB   |              |

| DNL                                               |                      | From GND to 2*VREG                                                                          | -                                    | -                                      | 2                                       | LSB   |              |

| Maximum variation over temperature (0°C to 50°C)  |                      |                                                                                             | _                                    | -                                      | 5                                       | LSB   |              |

| Sampling frequency                                |                      | All channels sequentially                                                                   | -                                    | 12.8                                   | -                                       | kHz   |              |

| Channel sampling frequency                        |                      | 8 channels                                                                                  | -                                    | 1.6                                    | -                                       | kHz   |              |

| DIGITAL PADS                                      |                      |                                                                                             |                                      |                                        |                                         |       |              |

| Voltage level for high input                      | V <sub>IH</sub>      |                                                                                             | VDDC<br>* 0.8                        | _                                      | VDDC<br>+ 0.5<br>(Note 6)               | V     |              |

| Voltage level for low input                       | V <sub>IL</sub>      |                                                                                             | -0.3                                 | -                                      | VDDC<br>* 0.2                           | V     |              |

| Input capacitance for digital pads                | C <sub>IN</sub>      |                                                                                             | -                                    | 2                                      | -                                       | pF    |              |