PRELIMINARY SPECIFICATION

### DESCRIPTION

The Bus Expander is specifically designed to increase the I/O capability of 8X300 systems previously limited by fanout considerations. The bus expander serves as a buffer between the 8X300 and blocks of I/O devices. Each bus expander can buffer a block of 16 I/O ports while only adding a single load to the 8X300.

# FEATURES

- 15ns max propagation delay

- Bidirectional

- Three-state outputs on both ports

- Pre-programmed address range

#### APPLICATIONS

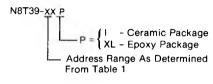

The 8T39 Bus Expander is designed to be used with the 8X300 microprocessor to allow increased I/O capability in those systems previously limited by fanout considerations. Figure 1 shows a typical arrangement of the bus expander in an 8X300 system. Each expander services I/O ports whose address is within the range of the expander. Other I/O ports or working storage may be directly connected to the bus as shown.

The bus expander is not limited to use with the 8X300, but may be applied in any system which uses a combined address/data bus.

### 8T39 ADDRESSING

During normal operation of the 8X300 when an I/O port address is being sent on the IV Bus (SC is high), the I/O port will examine all eight bits of the microprocessor bus for an address compare. Since the 8T39 is used to buffer blocks of I/O ports, only the four most significant bits are examined by the 8T39 for an address compare.

Note that redundant addresses are not programmed into separate devices. Rather, a discrete device (such as the 8T39-03) may be wired for any address requiring two 1 bits and two 0 bits in the address. The various address ranges for this same device are obtained by permuting the high order (DI0 and DO0 are MSB) data lines accordingly. Both input and output lines must be redefined in order to maintain data and address integrity on the extended bus. Table 1 summarizes the 8T39 addressing.

Address functions are specified with the convention that bit 0 is the MSB and bit 7 is the LSB. The DI microprocessor bus address decoding is active low.

#### FUNCTIONAL DESCRIPTION

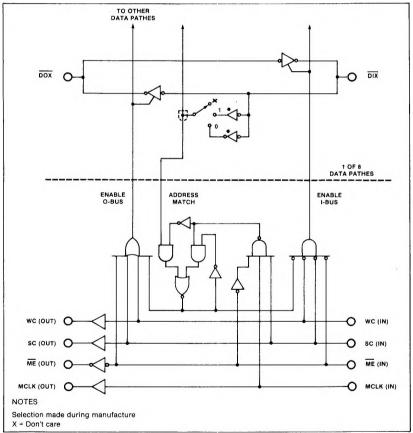

The Bus Expander contains eight sets of non-inverting bidirectional tri-state drivers for the bus data bits, four non-inverting

unidirectional drivers for I/O port control, and necessary control logic. The control logic is required to maintain the proper directional transfer of bus data as dictated by the states of the I/O port control signals and the currently enabled I/O port. Each bus expander is programmed during manufacturing to respond to a specific block of I/O port addresses. Only I/O ports with addresses in the range of a given bus expander may be connected to that expander. A bus expander may be used on either left bank or right bank. Multiple expanders on the same bank must have different address ranges; however, expanders with the same address range can be connected if they are on different banks. Systems may be configured with I/O ports connected directly to the 8X300, as well as I/O ports connected through a bus expander; however, no unbuffered I/O port may have an address within the span of a bus expander on the same bank.

Addition of bus expanders may impact system cycle time due to the added delay in the data path. For the purposes of calculating allowable cycle time as described in the 8X300 data sheet, the bus expander delays

#### **PIN CONFIGURATION**

may be considered additive to the I/O port delays so that a buffered I/O port simply appears as a slower I/O port.

| PIN NO.     | SYMBOL    | NAME AND FUNCTION       | ТҮРЕ                       |

|-------------|-----------|-------------------------|----------------------------|

| 2-7,9,10    | D00-D07   | I/O port data bus       | Active low,<br>three-state |

| 11          | WC(OUT)   | Write command output    | Active high                |

| 12          | SC(OUT)   | Select command output   | Active high                |

| 13          | MCLK(OUT) | Master clock output     | Acitve high                |

| 14          | ME(OUT)   | Master enable output    | Active low                 |

| 15          | ME(IN)    | Master enable input     | Active low                 |

| 16          | MCLK(IN)  | Master clock input      | Active high                |

| 17          | SC(IN)    | Select command output   | Active high                |

| 18          | WC(IN)    | Write command output    | Active high                |

| 19,20,22-27 | DI0-DI7   | Microprocessor data bus | Active low,<br>three-state |

| 1,8,21      | GND       | Ground                  |                            |

| 28          | Vcc       | +5 volt supply          | 0                          |

| ADDRESS PATTERN<br>PART TYPE MSB(0) LSB(7) |          | RN ADDRESS BLOCKS<br>Octal                         |  |  |

|--------------------------------------------|----------|----------------------------------------------------|--|--|

| 8T39-00                                    | 0000XXXX | 0-17                                               |  |  |

| 8T39-01                                    | 0001XXXX | 20-37, 40-57, 100-117, 200-217                     |  |  |

| 8T39-03                                    | 0011XXXX | 60-77, 120-137, 220-237, 140-157, 240-257, 300-317 |  |  |

| 8T39-07                                    | 0111XXXX | 160-177, 260-277, 320-337, 340-357                 |  |  |

| 8T39-17                                    | 1111XXXX | 360-377                                            |  |  |

Table 1 8T39 ADDRESSING SUMMARY

8T39

PRELIMINARY SPECIFICATION

### TRUTH TABLE

| ME | sc | wc | MCLK | SELECT<br>LATCH | DATA TRANSFER<br>DIRECTION | ADDRESS*<br>COMPARISON |

|----|----|----|------|-----------------|----------------------------|------------------------|

| L  | L  | L  | x    | Set             | DI Bus ← DO Bus            | No                     |

| L  | L  | L  | X    | Not set         | DI Bus → DO Bus            | No                     |

| L  | L  | н  | X    | x               | DI Bus → DO Bus            | No                     |

| L  | н  | x  | L    | x               | DI Bus → DO Bus            | No                     |

| L  | н  | X  | н    | х               | DI Bus → DO Bus            | Yes                    |

| н  | х  | ×  | X    | х               | DI Bus → DO Bus            | No                     |

NOTES

"When an address comparison is made, the select latch is set if the data on the DI Bus is within the manufactured address range of the IV Bus Expander. Otherwise, the select latch is cleared.

#### FUNCTIONAL BLOCK DIAGRAM

8T39-I,XL

8T39

PRELIMINARY SPECIFICATION

### **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

|                  | PARAMETER                   | RATING      | UNIT |

|------------------|-----------------------------|-------------|------|

| Vcc              | Power supply voltage        | +7          | Vdc  |

| VIN              | Input voltage               | +5.5        | Vdc  |

| ٧ <sub>0</sub>   | Off-state output voltage    | +5.5        | Vdc  |

| Τ <sub>Α</sub>   | Operating temperature range | 0 to +70    | °C   |

| <sup>⊤</sup> stg | Storage temperature range   | -65 to +150 | °C   |

#### **ORDERING INFORMATION**

The Bus Expander is ordered by specifying the following part number:

# DC ELECTRICAL CHARACTERISTICS $V_{CC} = 5V \pm 5\%$ , 0°C $\leq T_A \leq 70$ °C

| PARAMETER              |                                                | TEST CONDITIONS                                    |     | LIMITS | LIMITS      |          |  |

|------------------------|------------------------------------------------|----------------------------------------------------|-----|--------|-------------|----------|--|

|                        |                                                | TEST CONDITIONS                                    | Min | Тур    | Max         | UNIT     |  |

| VIL<br>VIH<br>VIC      | Input voltage<br>Low<br>High<br>Clamp          | -5mA at V <sub>CC</sub> min                        | 2.0 |        | .8<br>-1    | V        |  |

| V <sub>OL</sub><br>Voh | Output voltage<br>Low<br>High                  | VCC = 4.75V<br>IOL = 16mA<br>IOH = -3.2mA          | 2.4 |        | .55         | V        |  |

| LIL<br>LIH             | Input current<br>Low*<br>High*                 | V CC = 5.25V<br>V IL = .5V<br>V IH = 5.25V         |     | < 10   | -250<br>100 | uA       |  |

| los<br>lcc             | Short circuit output current<br>Supply current | V <sub>CC</sub> = 4.75V<br>V <sub>CC</sub> = 5.25V | -40 |        | 200         | mA<br>mA |  |

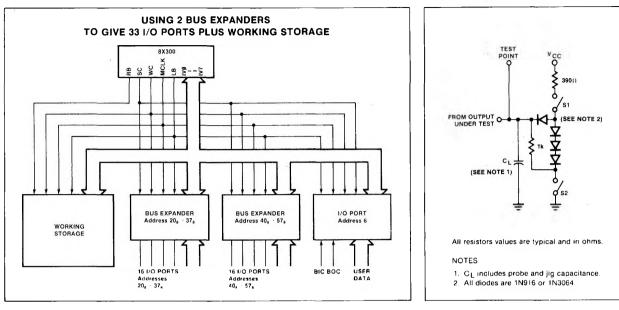

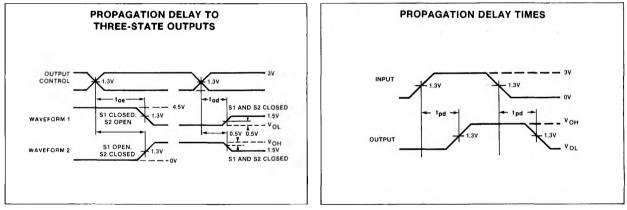

# AC ELECTRICAL CHARACTERISTICS $V_{CC} = 5V \pm 5\%, 0^{\circ}C \leqslant T_{A} \leqslant 70^{\circ}C, CL^{1} = 300pF^{2}$

|                    | PARAMETER                          | то                                             | FROM                                              | TEST CONDITIONS |     | LIMITS |     | UNIT |

|--------------------|------------------------------------|------------------------------------------------|---------------------------------------------------|-----------------|-----|--------|-----|------|

|                    |                                    | 10                                             |                                                   | TEST CONDITIONS | Min | Тур    | Max |      |

| tpd                | Propagation Delay<br>Data          | DOX<br>DIX                                     | DIX<br>DOX                                        | 10              |     |        | 15  | ns   |

| tpd                | Control<br>Propagation Delay       | ME (out)<br>MCLK (out)<br>SC (out)<br>WC (out) | ME (in)<br>MCLK (in)<br>SC (in)<br>WC (in)        |                 |     |        | 15  |      |

| toe                | Data<br>Output Enable              | DIX<br>DOX                                     | MĒ (in)<br>SC (in)<br>WC (in)                     |                 | 28  |        | 56  | ns   |

| tod                | Data<br>Output Disable             | DIX<br>DOX                                     | ME (in)<br>SC (in)<br>WC (in)                     |                 | 15  |        |     | ns   |

| <sup>t</sup> setup | Adverse<br>Setup Time <sup>3</sup> | DIX<br>DOX                                     | DIX<br>ME (in)<br>MCLK (in)<br>SC (in)<br>WC (in) |                 | 54  |        |     | ns   |

| t <sub>hold</sub>  | Address<br>Hold Time <sup>3</sup>  | DIX<br>DOX                                     | DIX<br>ME (in)<br>MCLK (in)<br>SC (in)<br>WC (in) |                 | 3   |        |     | ns   |

NOTES

1. Includes tri-state leakage.

2. Minimum clock width  $\approx$  50ns.

3. All set up and hold times are referenced to the trailing edge of the clocking input MCLK.

**8**T39

8T39-I,XL

PRELIMINARY SPECIFICATION

#### TYPICAL APPLICATIONS

**TEST LOAD CIRCUIT**

8T39

8T39-I.XL

## **VOLTAGE WAVEFORMS**

PRELIMINARY SPECIFICATION

Manufacturer reserves the right to make design changes and improvements.