## INTEGRATED CIRCUITS

Product specification IC20 Data Handbook 1996 Aug 16

Philips Semiconductors

#### 80C31/80C51/87C51

#### DESCRIPTION

The Philips 80C31/80C51/87C51 is a high-performance microcontroller fabricated with Philips high-density CMOS technology. The CMOS 8XC51 is functionally compatible with the NMOS 8031/8051 microcontrollers. The Philips CMOS technology combines the high speed and density characteristics of HMOS with the low power attributes of CMOS. Philips epitaxial substrate minimizes latch-up sensitivity.

The 8XC51 contains a 4k  $\times$  8 ROM (80C51) EPROM (87C51), a 128  $\times$  8 RAM, 32 I/O lines, two 16-bit counter/timers, a five-source, two-priority level nested interrupt structure, a serial I/O port for either multi-processor communications, I/O expansion or full duplex UART, and on-chip oscillator and clock circuits.

In addition, the device has two software selectable modes of power reduction—idle mode and power-down mode. The idle mode freezes the CPU while allowing the RAM, timers, serial port, and interrupt system to continue functioning. The power-down mode saves the RAM contents but freezes the oscillator, causing all other chip functions to be inoperative.

#### FEATURES

- 8031/8051 compatible

- 4k × 8 ROM (80C51)

- 4k × 8 EPROM (87C51)

- ROMless (80C31)

- 128 × 8 RAM

- Two 16-bit counter/timers

- Full duplex serial channel

- Boolean processor

- Memory addressing capability

64k ROM and 64k RAM

- Power control modes:

- Idle mode

- Power-down mode

- CMOS and TTL compatible

- Five speed ranges at V<sub>CC</sub> = 5V

- 12MHz

- 16MHz

- 24MHz

- 33MHz

- Five package styles

- Extended temperature ranges

- OTP package available

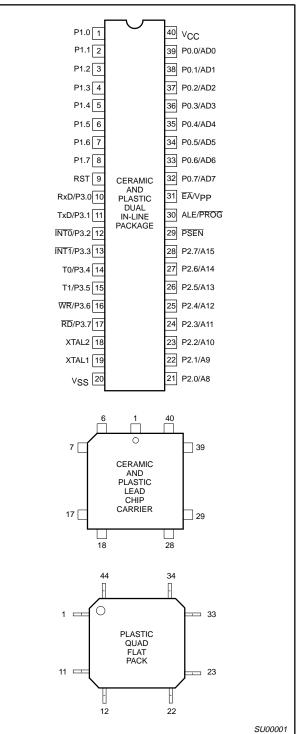

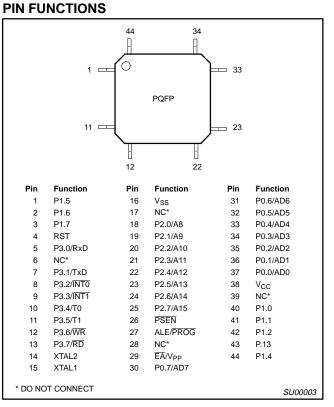

#### **PIN CONFIGURATIONS**

SEE PAGE 3 FOR QFP AND LCC PIN FUNCTIONS.

#### 80C31/80C51/87C51

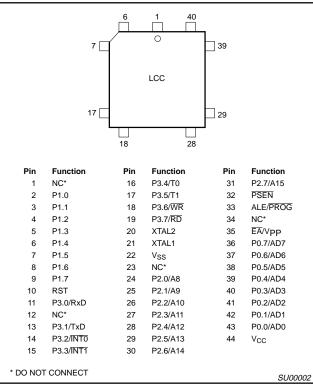

## CERAMIC AND PLASTIC LEADED CHIP CARRIER PIN FUNCTIONS

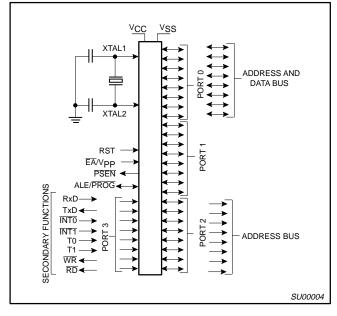

#### LOGIC SYMBOL

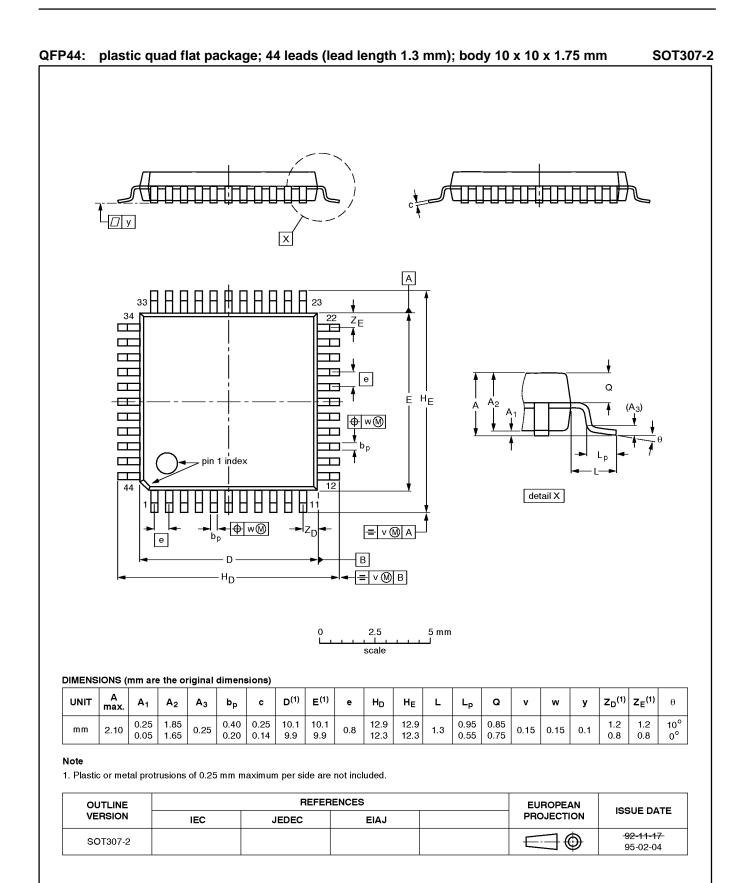

### PLASTIC QUAD FLAT PACK

1996 Aug 16

## **ORDERING INFORMATION**

|              |                   | PHILIPS NORTH AMERICA |               |                   |                                                  |             |  |  |  |  |

|--------------|-------------------|-----------------------|---------------|-------------------|--------------------------------------------------|-------------|--|--|--|--|

| EPROM        | DRAWING<br>NUMBER | ROMIess               | ROM           | DRAWING<br>NUMBER | TEMPERATURE RANGE °C<br>AND PACKAGE <sup>1</sup> | Freq<br>MHz |  |  |  |  |

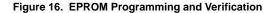

| SC87C51CCF40 | 0590B             |                       |               |                   | 0 to +70, Ceramic Dual In-line Package, UV       | 3.5 to 12   |  |  |  |  |

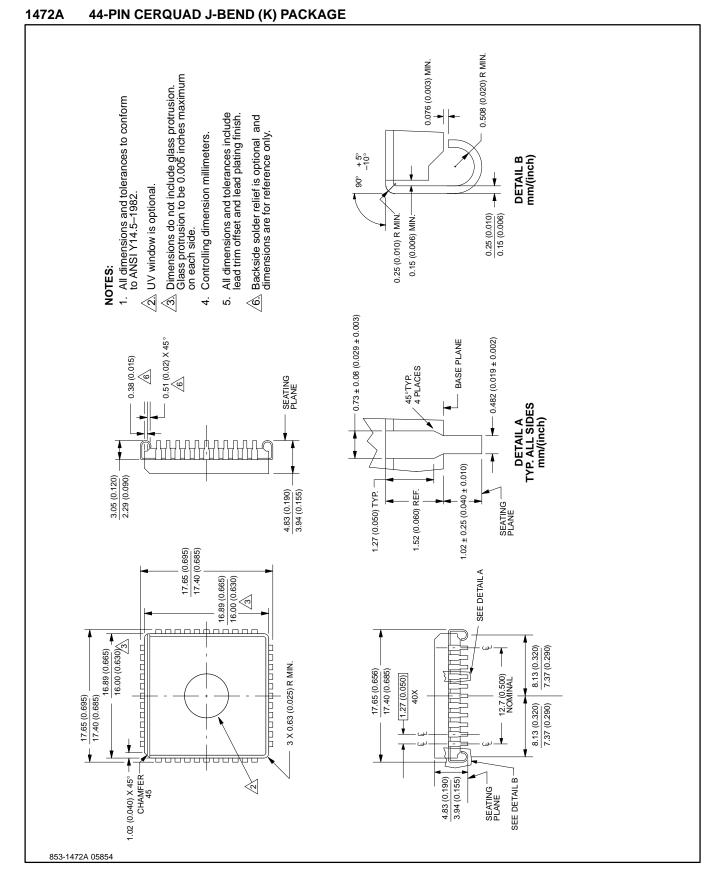

| SC87C51CCK44 | 1472A             |                       |               |                   | 0 to +70, Ceramic Leaded Chip Carrier, UV        | 3.5 to 12   |  |  |  |  |

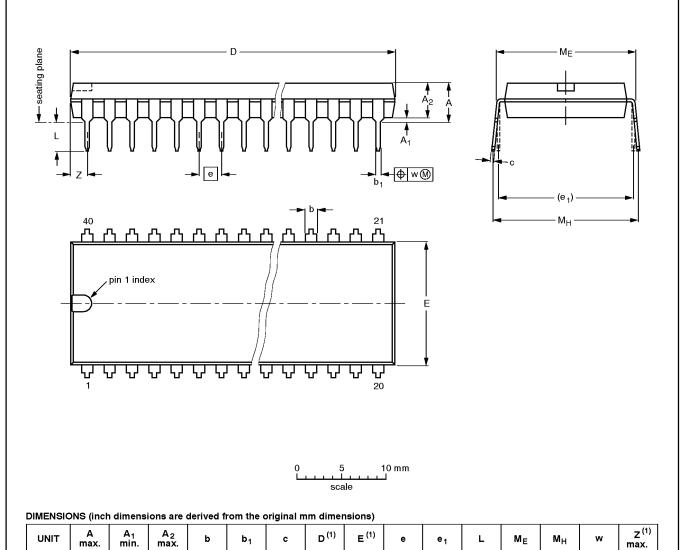

| SC87C51CCN40 | SOT129-1          | SC80C31BCCN40         | SC80C51BCCN40 | SOT129-1          | 0 to +70, Plastic Dual In-line Package, OTP      | 3.5 to 12   |  |  |  |  |

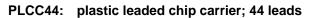

| SC87C51CCA44 | SOT187-2          | SC80C31BCCA44         | SC80C51BCCA44 | SOT187-2          | 0 to +70, Plastic Leaded Chip Carrier, OTP       | 3.5 to 12   |  |  |  |  |

| SC87C51CCB44 | SOT307-2          | SC80C31BCCB44         | SC80C51BCCB44 | SOT307-2          | 0 to +70, Plastic Quad Flat Pack, OTP            | 3.5 to 12   |  |  |  |  |

| SC87C51ACF40 | 0590B             |                       |               |                   | -40 to +85, Ceramic Dual In-line Package, UV     | 3.5 to 12   |  |  |  |  |

| SC87C51ACN40 | SOT129-1          | SC80C31BACN40         | SC80C51BACN40 | SOT129-1          | -40 to +85, Plastic Dual In-line Package, OTP    | 3.5 to 12   |  |  |  |  |

| SC87C51ACA44 | SOT187-2          | SC80C31BACA44         | SC80C51BACA44 | SOT187-2          | -40 to +85, Plastic Leaded Chip Carrier, OTP     | 3.5 to 12   |  |  |  |  |

| SC87C51ACB44 | SOT307-2          | SC80C31BACB44         | SC80C51BACB44 | SOT307-2          | -40 to +85, Plastic Quad Flat Pack, OTP          | 3.5 to 12   |  |  |  |  |

| SC87C51CGF40 | 0590B             |                       |               |                   | 0 to +70, Ceramic Dual In-line Package, UV       | 3.5 to 16   |  |  |  |  |

| SC87C51CGK44 | 1472A             |                       |               |                   | 0 to +70, Ceramic Leaded Chip Carrier, UV        | 3.5 to 16   |  |  |  |  |

| SC87C51CGN40 | SOT129-1          | SC80C31BCGN40         | SC80C51BCGN40 | SOT129-1          | 0 to +70, Plastic Dual In-line Package, OTP      | 3.5 to 16   |  |  |  |  |

| SC87C51CGA44 | SOT187-2          | SC80C31BCGA44         | SC80C51BCGA44 | SOT187-2          | 0 to +70, Plastic Leaded Chip Carrier, OTP       | 3.5 to 16   |  |  |  |  |

| SC87C51CGB44 | SOT307-2          | SC80C31BCGB44         | SC80C51BCGB44 | SOT307-2          | 0 to +70, Plastic Quad Flat Pack, OTP            | 3.5 to 16   |  |  |  |  |

| SC87C51AGF40 | 0590B             |                       |               |                   | -40 to +85, Ceramic Dual In-line Package, UV     | 3.5 to 16   |  |  |  |  |

| SC87C51AGN40 | SOT129-1          | SC80C31BAGN40         | SC80C51BAGN40 | SOT129-1          | -40 to +85, Plastic Dual In-line Package, OTP    | 3.5 to 16   |  |  |  |  |

| SC87C51AGA44 | SOT187-2          | SC80C31BAGA44         | SC80C51BAGA44 | SOT187-2          | -40 to +85, Plastic Leaded Chip Carrier, OTP     | 3.5 to 16   |  |  |  |  |

| SC87C51AGB44 | SOT307-2          | SC80C31BAGB44         | SC80C51BAGB44 | SOT307-2          | -40 to +85, Plastic Quad Flat Pack, OTP          | 3.5 to 16   |  |  |  |  |

|              |                   |                       |               |                   |                                                  |             |  |  |  |  |

| SC87C51CPF40 | 0590B             |                       |               |                   | 0 to +70, Ceramic Dual In-line Package, UV       | 3.5 to 24   |  |  |  |  |

| SC87C51CPK44 | 1472A             |                       |               |                   | 0 to +70, Ceramic Leaded Chip Carrier, UV        | 3.5 to 24   |  |  |  |  |

| SC87C51CPN40 | SOT129-1          | SC80C31BCPN40         | SC80C51BCPN40 | SOT129-1          | 0 to +70, Plastic Dual In-line Package, OTP      | 3.5 to 24   |  |  |  |  |

| SC87C51CPA44 | SOT187-2          | SC80C31BCPA44         | SC80C51BCPA44 | SOT187-2          | 0 to +70, Plastic Leaded Chip Carrier, OTP       | 3.5 to 24   |  |  |  |  |

| SC87C51APF40 | 0590B             |                       |               |                   | -40 to +85, Ceramic Dual In-line Package, UV     |             |  |  |  |  |

| SC87C51APN40 | SOT129-1          | SC80C31BAPN40         | SC80C51BAPN40 | SOT129-1          | -40 to +85, Plastic Dual In-line Package, OTP    | 3.5 to 24   |  |  |  |  |

| SC87C51APA44 | SOT187-2          | SC80C31BAPA44         | SC80C51BAPA44 | SOT187-2          | -40 to +85, Plastic Leaded Chip Carrier, OTP     | 3.5 to 24   |  |  |  |  |

|              |                   |                       |               |                   |                                                  |             |  |  |  |  |

| SC87C51CYF40 | 0590B             |                       |               |                   | 0 to +70, Ceramic Dual In-line Package, UV       | 3.5 to 33   |  |  |  |  |

| SC87C51CYK44 | 1472A             |                       |               |                   | 0 to +70, Ceramic Leaded Chip Carrier, UV        | 3.5 to 33   |  |  |  |  |

| SC87C51CYN40 | SOT129-1          | SC80C31BCYN40         | SC80C51BCYN40 | SOT129-1          | 0 to +70, Plastic Dual In-line Package, OTP      | 3.5 to 33   |  |  |  |  |

| SC87C51CYA44 | SOT187-2          | SC80C31BCYA44         | SC80C51BCYA44 | SOT187-2          | 0 to +70, Plastic Leaded Chip Carrier, OTP       | 3.5 to 33   |  |  |  |  |

|              | I                 | L                     |               | <u> </u>          | I                                                |             |  |  |  |  |

OTP = One Time Programmable EPROM. UV = UV Erasable EPROM

SOT311 replaced by SOT307-2.

#### **ORDERING INFORMATION** (Continued)

|                           |                             | F              | PHILIPS               |                                                  |             |

|---------------------------|-----------------------------|----------------|-----------------------|--------------------------------------------------|-------------|

| ROMIess<br>(ORDER NUMBER) | ROMIess<br>(MARKING NUMBER) | ROM            | DRAWING<br>NUMBER     | TEMPERATURE RANGE °C<br>AND PACKAGE <sup>1</sup> | Freq<br>MHz |

|                           |                             |                |                       |                                                  |             |

| PCB80C31-2 N              | PCB80C31BH2-12P             | PCB80C51BH-2P  | SOT129-1              | 0 to +70, Plastic Dual In-line Package, OTP      | 0.5 to 12   |

| PCB80C31-2 A              | PCB80C31BH2-12WP            | PCB80C51BH-2WP | SOT187-2              | 0 to +70, Plastic Leaded Chip Carrier, OTP       | 0.5 to 12   |

|                           | PCB80C31BH2-12H             | PCB80C51BH-2H  | SOT307-2 <sup>2</sup> | 0 to +70, Plastic Quad Flat Pack, OTP            | 0.5 to 12   |

|                           |                             |                |                       |                                                  |             |

|                           |                             |                |                       |                                                  |             |

| PCB80C31-3 N              | PCB80C31BH3-16P             | PCB80C51BH-3P  | SOT129-1              | 0 to +70, Plastic Dual In-line Package, OTP      | 1.2 to 16   |

| PCB80C31-3 A              | PCB80C31BH3-16WP            | PCB80C51BH-3WP | SOT187-2              | 0 to +70, Plastic Leaded Chip Carrier, OTP       | 1.2 to 16   |

|                           | PCB80C31BH3-16H             | PCB80C51BH-3H  | SOT307-2 <sup>2</sup> | 0 to +70, Plastic Quad Flat Pack, OTP            | 1.2 to 16   |

| PCF80C31-3 N              | PCF80C31BH3-16P             | PCF80C51BH-3P  | SOT129-1              | -40 to +85, Plastic Dual In-line Package, OTP    | 1.2 to 16   |

| PCF80C31-3 A              | PCF80C31BH3-16WP            | PCF80C51BH-3WP | SOT187-2              | -40 to +85, Plastic Leaded Chip Carrier, OTP     | 1.2 to 16   |

|                           | PCF80C31BH3-16H             | PCF80C51BH-3H  | SOT307-2 <sup>2</sup> | -40 to +85, Plastic Quad Flat Pack, OTP          | 1.2 to 16   |

|                           | PCA80C31BH3-16P             | PCA80C51BH-3P  | SOT129-1              | -40 to +125, Plastic Dual In-line Package        | 1.2 to 16   |

|                           | PCA80C31BH3-16WP            | PCA80C51BH-3WP | SOT187-2              | -40 to +125, Plastic Leaded Chip Carrier         | 1.2 to 16   |

|                           |                             |                |                       |                                                  |             |

| PCB80C31-4 N              | PCB80C31BH4-24P             | PCB80C51BH-4P  | SOT129-1              | 0 to +70, Plastic Dual In-line Package, OTP      | 1.2 to 24   |

| PCB80C31-4 A              | PCB80C31BH4-24WP            | PCB80C51BH-4WP | SOT187-2              | 0 to +70, Plastic Leaded Chip Carrier, OTP       | 1.2 to 24   |

|                           | PCB80C31BH4-24H             | PCB80C51BH-4H  | SOT307-2 <sup>2</sup> | 0 to +70, Plastic Quad Flat Pack, OTP            | 1.2 to 24   |

| PCF80C31-4 N              | PCF80C31BH4-24P             | PCF80C51BH-4P  | SOT129-1              | -40 to +85, Plastic Dual In-line Package, OTP    | 1.2 to 24   |

| PCF80C31-4 A              | PCF80C31BH4-24WP            | PCF80C51BH-4WP | SOT187-2              | -40 to +85, Plastic Leaded Chip Carrier, OTP     | 1.2 to 24   |

|                           | PCF80C31BH4-24H             | PCF80C51BH-4H  | SOT307-2 <sup>2</sup> | -40 to +85, Plastic Leaded Chip Carrier, OTP     | 1.2 to 24   |

|                           |                             |                |                       |                                                  |             |

|                           |                             |                |                       |                                                  |             |

| PCB80C31-5 N              | PCB80C31BH5-30P             | PCB80C51BH-5P  | SOT129-1              | 0 to +70, Plastic Dual In-line Package           | 1.2 to 33   |

| PCB80C31-5 A              | PCB80C31BH5-30WP            | PCB80C51BH-5WP | SOT187-2              | 0 to +70, Plastic Leaded Chip Carrier            | 1.2 to 33   |

| PCB80C31-5 B              | PCB80C31BH5-30H             | PCB80C51BH-5H  | SOT307-2 <sup>2</sup> | 0 to +70, Plastic Quad Flat Pack                 | 1.2 to 33   |

### 80C31/80C51/87C51

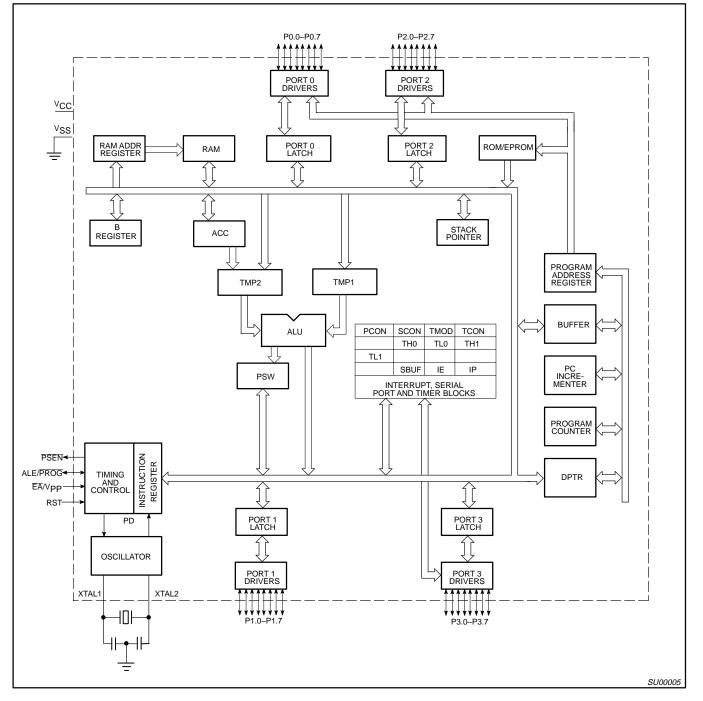

#### **BLOCK DIAGRAM**

### 80C31/80C51/87C51

#### **PIN DESCRIPTION**

|                    |          | PIN NO.      |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|----------|--------------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC           | DIP      | LCC          | QFP           | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>SS</sub>    | 20       | 22           | 16            | I    | Ground: 0V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>CC</sub>    | 40       | 44           | 38            | I    | <b>Power Supply:</b> This is the power supply voltage for normal, idle, and power-down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P0.0–0.7           | 39–32    | 43–36        | 37–30         | I/O  | <b>Port 0:</b> Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application, it uses strong internal pull-ups when emitting 1s. Port 0 also outputs the code bytes during program verification in the 87C51. External pull-ups are required during program verification.                                                                                                                                                                                                                                                                       |

| P1.0–P1.7          | 1–8      | 2–9          | 40-44,<br>1–3 | I/O  | <b>Port 1:</b> Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 1 pins that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ). Port 1 also receives the low-order address byte during program memory verification.                                                                                                                                                                                                                                                                                                               |

| P2.0–P2.7          | 21–28    | 24–31        | 18–25         | I/O  | <b>Port 2:</b> Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 2 pins that are externally being pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ). Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOV @Ri), port 2 emits the contents of the P2 special function register. |

| P3.0–P3.7          | 10–17    | 11,<br>13–19 | 5,<br>7–13    | I/O  | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins that are externally being pulled low will source current because of the pull-ups. (See DC Electrical Characteristics: $I_{IL}$ ). Port 3 also serves the special features of the 80C51 family, as listed below:                                                                                                                                                                                                                                                                                                                               |

|                    | 10       | 11           | 5             | I    | RxD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    | 11       | 13           | 7             | 0    | TxD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    | 12<br>13 | 14<br>15     | 8<br>9        |      | INT0 (P3.2): External interrupt<br>INT1 (P3.3): External interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                    | 14       | 16           | 10            |      | <b>T0 (P3.4):</b> Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                    | 15       | 17           | 11            | 1    | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | 16       | 18           | 12            | 0    | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | 17       | 19           | 13            | 0    | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RST                | 9        | 10           | 4             | I    | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

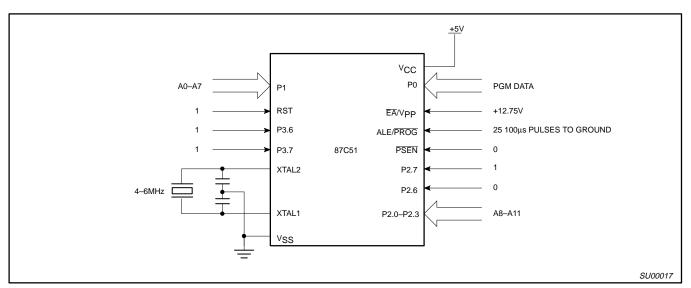

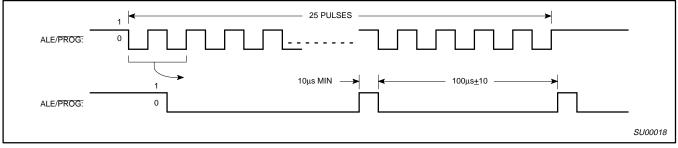

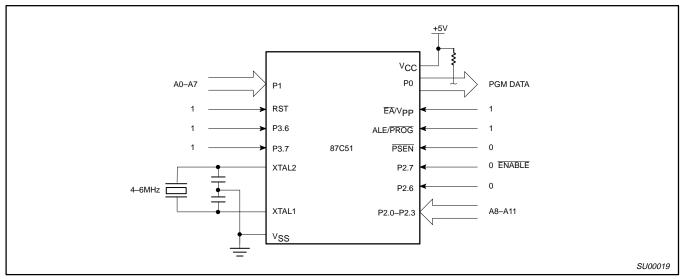

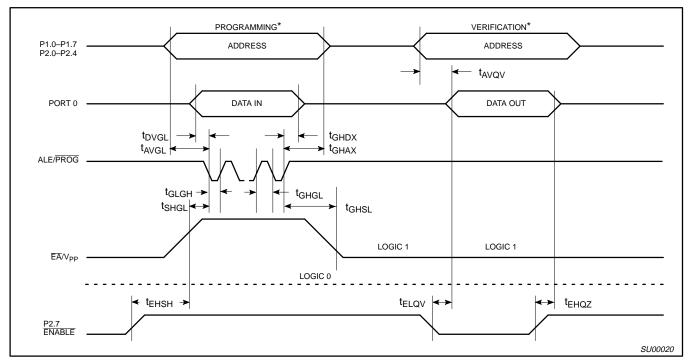

| ALE/PROG           | 30       | 33           | 27            | I/O  | Address Latch Enable/Program Pulse: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. This pin is also the program pulse input (PROG) during EPROM programming.                                                                                                                                                                                                                                                                                                                                   |

| PSEN               | 29       | 32           | 26            | 0    | <b>Program Store Enable:</b> The read strobe to external program memory. When the device is executing code from the external program memory, <u>PSEN</u> is activated twice each machine cycle, except that two <u>PSEN</u> activations are skipped during each access to external data memory. <u>PSEN</u> is not activated during fetches from internal program memory.                                                                                                                                                                                                                                                                                                                                                                                          |

| EA/V <sub>PP</sub> | 31       | 35           | 29            | I    | <b>External Access Enable/Programming Supply Voltage:</b> $\overline{EA}$ must be externally held low to enable the device to fetch code from external program memory locations 0000H to 0FFFH. If $\overline{EA}$ is held high, the device executes from internal program memory unless the program counter contains an address greater than 0FFFH. This pin also receives the 12.75V programming supply voltage (V <sub>PP</sub> ) during EPROM programming.                                                                                                                                                                                                                                                                                                     |

| XTAL1              | 19       | 21           | 15            | I    | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| XTAL2              | 18       | 20           | 14            | 0    | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### 80C31/80C51/87C51

#### Table 1. 80C52/80C54/80C58 Special Function Registers

| SYMBOL              | DESCRIPTION                                                     | DIRECT<br>ADDRESS | BIT A<br>MSB | DDRESS | , SYMBOI | , OR ALI | FERNATIV | E PORT | FUNCTIC | N<br>LSB | RESET<br>VALUE |

|---------------------|-----------------------------------------------------------------|-------------------|--------------|--------|----------|----------|----------|--------|---------|----------|----------------|

| ACC*                | Accumulator                                                     | E0H               | E7           | E6     | E5       | E4       | E3       | E2     | E1      | E0       | 00H            |

| AUXR#               | Auxiliary                                                       | 8EH               | -            | -      | -        | -        | -        | -      | -       | AO       | xxxxxxx0B      |

| AUXR1#              | Auxiliary 1 (Note 2)                                            | A2H               | -            | _      | -        | -        | WUPD     | 0      | -       | DPS      | xxxx00x0B      |

| B*                  | B register                                                      | F0H               | F7           | F6     | F5       | F4       | F3       | F2     | F1      | F0       | 00H            |

| DPTR:<br>DPH<br>DPL | Data Pointer (2 bytes)<br>Data Pointer High<br>Data Pointer Low | 83H<br>82H        |              |        |          |          |          |        |         |          | 00H<br>00H     |

|                     |                                                                 |                   | AF           | AE     | AD       | AC       | AB       | AA     | A9      | A8       |                |

| IE*                 | Interrupt Enable                                                | A8H               | EA           | EC     | ET2      | ES       | ET1      | EX1    | ET0     | EX0      | 00H            |

|                     |                                                                 |                   | BF           | BE     | BD       | BC       | BB       | BA     | B9      | B8       |                |

| IP*                 | Interrupt Priority                                              | B8H               | -            | -      | PT2      | PS       | PT1      | PX1    | PT0     | PX0      | x000000E       |

|                     |                                                                 |                   | B7           | B6     | B5       | B4       | B3       | B2     | B1      | B0       | 1              |

| IPH#                | Interrupt Priority High                                         | B7H               | -            | -      | PT2H     | PSH      | PT1H     | PX1H   | PT0H    | PX0H     | x0000000E      |

|                     |                                                                 |                   | 87           | 86     | 85       | 84       | 83       | 82     | 81      | 80       | 1              |

| P0*                 | Port 0                                                          | 80H               | AD7          | AD6    | AD5      | AD4      | AD3      | AD2    | AD1     | AD0      | FFH            |

|                     |                                                                 |                   | 97           | 96     | 95       | 94       | 93       | 92     | 91      | 90       | 1              |

| P1*                 | Port 1                                                          | 90H               | _            | _      | -        | _        | -        | _      | T2EX    | T2       | FFH            |

|                     |                                                                 |                   | A7           | A6     | A5       | A4       | A3       | A2     | A1      | A0       | 1              |

| P2*                 | Port 2                                                          | A0H               | AD15         | AD14   | AD13     | AD12     | AD11     | AD10   | AD9     | AD8      | FFH            |

|                     |                                                                 |                   | B7           | B6     | B5       | B4       | B3       | B2     | B1      | B0       | 1              |

| P3*                 | Port 3                                                          | B0H               | RD           | WR     | T1       | TO       | INT1     | INTO   | TxD     | RxD      | FFH            |

|                     |                                                                 |                   |              |        |          |          |          |        |         |          | 1              |

| PCON#1              | Power Control                                                   | 87H               | SMOD1        | SMOD0  | -        | -        | GF1      | GF0    | PD      | IDL      | 00xx0000E      |

|                     |                                                                 |                   | D7           | D6     | D5       | D4       | D3       | D2     | D1      | D0       | 1              |

| PSW*                | Program Status Word                                             | D0H               | CY           | AC     | F0       | RS1      | RS0      | OV     | -       | Р        | 00H            |

| SADDR#              | Slave Address                                                   | A9H               |              |        |          |          |          | •      |         |          | 00H            |

| SADEN#              | Slave Address Mask                                              | B9H               |              |        |          |          |          |        |         |          | 00H            |

| SBUF                | Serial Data Buffer                                              | 99H               |              |        |          |          |          |        |         |          | xxxxxxxB       |

|                     |                                                                 |                   | 9F           | 9E     | 9D       | 9C       | 9B       | 9A     | 99      | 98       |                |

| SCON*               | Serial Control                                                  | 98H               | SM0/FE       | SM1    | SM2      | REN      | TB8      | RB8    | TI      | RI       | 00H            |

| SP                  | Stack Pointer                                                   | 81H               | _            | _      | _        | _        | _        |        |         |          | 07H            |

|                     |                                                                 |                   | 8F           | 8E     | 8D       | 8C       | 8B       | 8A     | 89      | 88       |                |

| TCON*               | Timer Control                                                   | 88H               | TF1          | TR1    | TF0      | TR0      | IE1      | IT1    | IE0     | IT0      | 00H            |

|                     |                                                                 |                   | CF           | CE     | CD       | CC       | СВ       | CA     | C9      | C8       | 4              |

| T2MOD#              | Timer 2 Mode Control                                            | C9H               | -            | -      | -        | -        | -        | -      | T2OE    | DCEN     | xxxxxx00B      |

| TH0                 | Timer High 0                                                    | 8CH               |              |        |          |          |          |        |         |          | 00H            |

| TH1<br>TL0          | Timer High 1<br>Timer Low 0                                     | 8DH<br>8AH        |              |        |          |          |          |        |         |          | 00H<br>00H     |

| TL0<br>TL1          | Timer Low 0                                                     | 8BH               |              |        |          |          |          |        |         |          | 00H            |

| TMOD                | Timer Mode                                                      | 89H               | GATE         | C/T    | M1       | MO       | GATE     | C/T    | M1      | MO       | 00H            |

\*

SFRs are bit addressable. SFRs are modified from or added to the 80C51 SFRs. #

Reserved bits. \_

Reset value depends on reset source.

Available only on SC80C51.

#### 80C31/80C51/87C51

#### **OSCILLATOR CHARACTERISTICS**

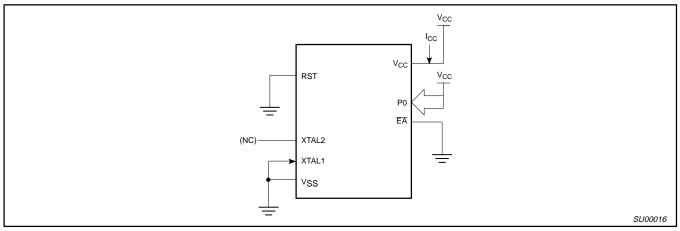

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier. The pins can be configured for use as an on-chip oscillator, as shown in the logic symbol.

To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected. There are no requirements on the duty cycle of the external clock signal, because the input to the internal clock circuitry is through a divide-by-two flip-flop. However, minimum and maximum high and low times specified in the data sheet must be observed.

#### RESET

A reset is accomplished by holding the RST pin high for at least two machine cycles (24 oscillator periods), while the oscillator is running. To insure a good power-up reset, the RST pin must be high long enough to allow the oscillator time to start up (normally a few milliseconds) plus two machine cycles.

#### IDLE MODE

In idle mode, the CPU puts itself to sleep while all of the on-chip peripherals stay active. The instruction to invoke the idle mode is the last instruction executed in the normal operating mode before the idle mode is activated. The CPU contents, the on-chip RAM, and all of the special function registers remain intact during this mode. The idle mode can be terminated either by any enabled interrupt (at which time the process is picked up at the interrupt service routine and continued), or by a hardware reset which starts the processor in the same manner as a power-on reset.

#### **POWER-DOWN MODE**

In the power-down mode, the oscillator is stopped and the instruction to invoke power-down is the last instruction executed. Only the contents of the on-chip RAM are preserved. A hardware reset is the only way to terminate the power-down mode. the control bits for the reduced power modes are in the special function register PCON.

Table 2 shows the state of I/O ports during low current operating modes.

#### Table 2. External Pin Status During Idle and Power-Down Modes

| MODE       | PROGRAM MEMORY | ALE | PSEN | PORT 0 | PORT 1 | PORT 2  | PORT 3 |

|------------|----------------|-----|------|--------|--------|---------|--------|

| Idle       | Internal       | 1   | 1    | Data   | Data   | Data    | Data   |

| Idle       | External       | 1   | 1    | Float  | Data   | Address | Data   |

| Power-down | Internal       | 0   | 0    | Data   | Data   | Data    | Data   |

| Power-down | External       | 0   | 0    | Float  | Data   | Data    | Data   |

#### ROM CODE SUBMISSION

When submitting ROM code for the 80C51, the following must be specified:

1. 4k byte user ROM data

- 2. 64 byte ROM encryption key (SC80C51 only)

- 3. ROM security bits (SC80C51 only).

| ADDRESS        | CONTENT | BIT(S) | COMMENT            |

|----------------|---------|--------|--------------------|

| 0000H to 0FFFH | DATA    | 7:0    | User ROM Data      |

| 1000H to 101FH | KEY     | 7:0    | ROM Encryption Key |

| 1020H          | SEC     | 0      | ROM Security Bit 1 |

| 1020H          | SEC     | 1      | ROM Security Bit 2 |

Security Bit 1: When programmed, this bit has two effects on masked ROM parts:

1. External MOVC is disabled, and

2. EA# is latched on Reset.

Security Bit 2: When programmed, this bit inhibits Verify User ROM.

#### 80C31/80C51/87C51

#### Electrical Deviations from Commercial Specifications for Extended Temperature Range (87C51)

DC and AC parameters not included here are the same as in the commercial temperature range table.

#### DC ELECTRICAL CHARACTERISTICS

$\begin{array}{l} T_{amb} = -40^{\circ}C \ to \ +85^{\circ}C, \ V_{CC} = 5V \ \pm 10\%, \ V_{SS} = 0V \ (Philips \ North \ America \ SC87C51); \\ For \ SC87C51 \ (33MHz \ only), \ T_{amb} = 0^{\circ}C \ to \ +70^{\circ}C, \ V_{CC} = 5V \ \pm 5\% \\ T_{amb} = -40^{\circ}C \ to \ +85^{\circ}C, \ V_{CC} = 5V \ \pm 10\%, \ V_{SS} = 0V \ (PCB80C31/51 \ and \ PCF80C31/51 \ Philips \ Parts \ Only) \end{array}$

|                  |                                                                                                                                                                                                                                                                                                                                                                                                     | TEST                       | LIN                     | IITS                             |                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------|----------------------------------|----------------------------|

| SYMBOL           | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                           | CONDITIONS                 | MIN                     | MAX                              | UNIT                       |

| V <sub>IL</sub>  | Input low voltage, except EA (Philips North America)                                                                                                                                                                                                                                                                                                                                                |                            | -0.5                    | 0.2V <sub>CC</sub> -0.15         | V                          |

| V <sub>IL</sub>  | Input low voltage, except EA (Philips)                                                                                                                                                                                                                                                                                                                                                              |                            | -0.5                    | 0.2V <sub>CC</sub> -0.25         | V                          |

| V <sub>IL1</sub> | Input low voltage to EA                                                                                                                                                                                                                                                                                                                                                                             |                            | -0.5                    | 0.2V <sub>CC</sub> -0.45         | V                          |

| V <sub>IH</sub>  | Input high voltage, except XTAL1, RST                                                                                                                                                                                                                                                                                                                                                               |                            | 0.2V <sub>CC</sub> +1   | V <sub>CC</sub> +0.5             | V                          |

| V <sub>IH1</sub> | Input high voltage to XTAL1, RST                                                                                                                                                                                                                                                                                                                                                                    |                            | 0.7V <sub>CC</sub> +0.1 | V <sub>CC</sub> +0.5             | V                          |

| IIL              | Logical 0 input current, ports 1, 2, 3                                                                                                                                                                                                                                                                                                                                                              | V <sub>IN</sub> = 0.45V    |                         | -75                              | μA                         |

| I <sub>TL</sub>  | Logical 1-to-0 transition current, ports 1, 2, 3                                                                                                                                                                                                                                                                                                                                                    | V <sub>IN</sub> = 2.0V     |                         | -750                             | μA                         |

| Icc              | Power supply current:<br>Active mode <sup>1</sup> @ 16MHz (Philips PCB80C31/51, PCF80C31/51)<br>Active mode @ 12MHz (Philips North America SC87C51)<br>Idle mode <sup>2</sup> @ 16MHz (Philips PCB80C31/51, PCF80C31/51)<br>Idle mode @ 12MHz (Philips North America SC87C51)<br>Power-down mode <sup>3</sup> (Philips PCB80C31/51, PCF80C31/51)<br>Power-down mode (Philips North America SC87C51) | V <sub>CC</sub> = 4.5–5.5V |                         | 25<br>20<br>6.5<br>5<br>75<br>50 | mA<br>mA<br>mA<br>μA<br>μA |

NOTES:

The operating supply current is measured with all output pins disconnected; XTAL1 driven with  $t_r = t_f = 10ns$ ;  $V_{IL} = V_{SS} + 0.5V$ ; 1.

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 not connected;  $\overline{EA} = RST = Port 0 = V_{CC}$ . The idle mode supply current is measured with all output pins disconnected; XTAL1 driven with  $t_r = t_f = 10ns$ ;  $V_{IL} = V_{SS} + 0.5V$ ; 2.  $V_{IH} = V_{CC} - 0.5V$ ; XTAL2 not connected;  $\overline{EA} = Port 0 = V_{CC}$ ; RST =  $V_{SS}$ . 3. The power-down current is measured with all output pins disconnected, XTAL2 not connected,  $\overline{EA} = Port 0 = V_{CC}$ ; RST =  $V_{SS}$ .

#### ABSOLUTE MAXIMUM RATINGS<sup>1, 2, 3</sup>

| PARAMETER                                                                                    | RATING                 | UNIT |

|----------------------------------------------------------------------------------------------|------------------------|------|

| Operating temperature under bias                                                             | 0 to +70 or -40 to +85 | °C   |

| Storage temperature range                                                                    | -65 to +150            | °C   |

| Voltage on $\overline{EA}/V_{PP}$ pin to $V_{SS}$                                            | 0 to +13.0             | V    |

| Voltage on any other pin to V <sub>SS</sub>                                                  | -0.5 to +6.5           | V    |

| Maximum I <sub>OL</sub> per I/O pin                                                          | 15                     | mA   |

| Power dissipation (based on package heat transfer limitations, not device power consumption) | 1.5                    | W    |

NOTES:

1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section of this specification is not implied.

2. This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maxima.

3. Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

### 80C31/80C51/87C51

#### DC ELECTRICAL CHARACTERISTICS

$T_{amb} = 0^{\circ}C \text{ to } +70^{\circ}C \text{ or } -40^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 5V \pm 20\%, V_{SS} = 0V \text{ (PCB80C31/51 and PCF80C31/51)} (12, 16, and 24MHz versions) \\ T_{amb} = 0^{\circ}C \text{ to } +70^{\circ}C \text{ or } -40^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 5V \pm 10\%, V_{SS} = 0V \text{ (87C51 12, 16, and 24MHz versions)} \text{ (PCB80C31/51 33MHz version)}; \\ T_{amb} = 0^{\circ}C \text{ to } +70^{\circ}C \text{ or } -40^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 5V \pm 10\%, V_{SS} = 0V \text{ (87C51 12, 16, and 24MHz versions)} \text{ (PCB80C31/51 33MHz version)}; \\ T_{amb} = 0^{\circ}C \text{ to } +70^{\circ}C \text{ or } -40^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 5V \pm 10\%, V_{SS} = 0V \text{ (87C51 12, 16, and 24MHz versions)} \text{ (PCB80C31/51 33MHz version)}; \\ T_{amb} = 0^{\circ}C \text{ to } +70^{\circ}C \text{ or } -40^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 5V \pm 10\%, V_{SS} = 0V \text{ (87C51 12, 16, and 24MHz versions)} \text{ (PCB80C31/51 33MHz version)}; \\ T_{amb} = 0^{\circ}C \text{ to } +70^{\circ}C \text{ or } -40^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 5V \pm 10\%, V_{SS} = 0V \text{ (87C51 12, 16, and 24MHz version)}; \\ T_{amb} = 0^{\circ}C \text{ to } +70^{\circ}C \text{ or } -40^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 5V \pm 10\%, V_{SS} = 0V \text{ (87C51 12, 16, and 24MHz version)}; \\ T_{amb} = 0^{\circ}C \text{ to } +70^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 5V \pm 10\%, V_{SS} = 0V \text{ (87C51 12, 16, and 24MHz version)}; \\ T_{amb} = 0^{\circ}C \text{ to } +70^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 5V \pm 10\%, V_{SS} = 0V \text{ (87C51 12, 16, and 24MHz version)}; \\ T_{amb} = 0^{\circ}C \text{ to } +10^{\circ}C \text{ to }$ For SC87C51 (33MHz only)  $T_{amb} = 0^{\circ}C$  to +70°C,  $V_{CC} = 5V \pm 5\%$

|                  |                                                                                                                                                                                                                                                                                                               | TEST                                                                             |                                                  | LIMITS               |                            |                      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------|----------------------|----------------------------|----------------------|

| SYMBOL           | PARAMETER                                                                                                                                                                                                                                                                                                     | CONDITIONS                                                                       | MIN                                              | TYPICAL <sup>1</sup> | МАХ                        | UNIT                 |

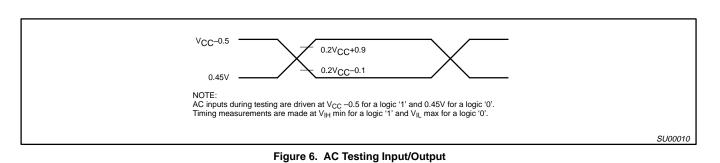

| V <sub>IL</sub>  | Input low voltage, except EA7                                                                                                                                                                                                                                                                                 |                                                                                  | -0.5                                             |                      | 0.2V <sub>CC</sub> -0.1    | V                    |

| V <sub>IL1</sub> | Input low voltage to EA <sup>7</sup>                                                                                                                                                                                                                                                                          |                                                                                  | 0                                                |                      | 0.2V <sub>CC</sub> -0.3    | V                    |

| V <sub>IH</sub>  | Input high voltage, except XTAL1, RST <sup>7</sup>                                                                                                                                                                                                                                                            |                                                                                  | 0.2V <sub>CC</sub> +0.9                          |                      | V <sub>CC</sub> +0.5       | V                    |

| V <sub>IH1</sub> | Input high voltage, XTAL1, RST <sup>7</sup>                                                                                                                                                                                                                                                                   |                                                                                  | 0.7V <sub>CC</sub>                               |                      | V <sub>CC</sub> +0.5       | V                    |

| V <sub>OL</sub>  | Output low voltage, ports 1, 2, 3 <sup>11</sup>                                                                                                                                                                                                                                                               | I <sub>OL</sub> = 1.6mA <sup>2</sup>                                             |                                                  |                      | 0.45                       | V                    |

| V <sub>OL1</sub> | Output low voltage, port 0, ALE, PSEN <sup>11</sup>                                                                                                                                                                                                                                                           | $I_{OL} = 3.2 \text{mA}^2$                                                       |                                                  |                      | 0.45                       | V                    |

| V <sub>OH</sub>  | Output high voltage, ports 1, 2, 3, ALE, PSEN <sup>3</sup>                                                                                                                                                                                                                                                    | $I_{OH} = -60\mu A,$<br>$I_{OH} = -25\mu A$<br>$I_{OH} = -10\mu A$               | 2.4<br>0.75V <sub>CC</sub><br>0.9V <sub>CC</sub> |                      |                            | V<br>V<br>V          |

| V <sub>OH1</sub> | Output high voltage (port 0 in external bus mode)                                                                                                                                                                                                                                                             | I <sub>OH</sub> = -800μA,<br>I <sub>OH</sub> = -300μA<br>I <sub>OH</sub> = -80μA | 2.4<br>0.75V <sub>CC</sub><br>0.9V <sub>CC</sub> |                      |                            | V<br>V<br>V          |

| IIL              | Logical 0 input current, ports 1, 2, 3 <sup>7</sup>                                                                                                                                                                                                                                                           | V <sub>IN</sub> = 0.45V                                                          |                                                  |                      | -50                        | μA                   |

| I <sub>TL</sub>  | Logical 1-to-0 transition current, ports 1, 2, 3 <sup>7</sup>                                                                                                                                                                                                                                                 | See note 4                                                                       |                                                  |                      | -650                       | μA                   |

| ILI              | Input leakage current, port 0                                                                                                                                                                                                                                                                                 | $V_{IN} = V_{IL} \text{ or } V_{IH}$                                             |                                                  |                      | ±10                        | μA                   |

| I <sub>CC</sub>  | Power supply current: <sup>7</sup><br>Active mode @ 12MHz <sup>8</sup> (Philips)<br>Active mode @ 12MHz <sup>5</sup> (Philips North America)<br>Idle mode @ 12MHz <sup>9</sup> (Philips)<br>Idle mode @ 12MHz (Philips North America)<br>Power-down mode <sup>10</sup> (Philips and<br>Philips North America) | See note 6                                                                       |                                                  | 11.5<br>1.3<br>3     | 18<br>19<br>4.4<br>4<br>50 | mA<br>mA<br>mA<br>μA |

| R <sub>RST</sub> | Internal reset pull-down resistor<br>(Philips North America)<br>(Philips)                                                                                                                                                                                                                                     |                                                                                  | 50<br>50                                         |                      | 300<br>150                 | kΩ<br>kΩ             |

| C <sub>IO</sub>  | Pin capacitance <sup>12</sup>                                                                                                                                                                                                                                                                                 |                                                                                  |                                                  |                      | 10                         | pF                   |

NOTES:

1. Typical ratings are not guaranteed. The values listed are at room temperature, 5V.

2. Capacitive loading on ports 0 and 2 may cause spurious noise to be superimposed on the Vols of ALE and ports 1 and 3. The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100pF), the noise pulse on the ALE pin may exceed 0.8V. In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input. IoL can exceed these conditions provided that no single output sinks more than 5mA and no more than two outputs exceed the test conditions.

Capacitive loading on ports 0 and 2 may cause the VOH on ALE and PSEN to momentarily fall below the 0.9V<sub>CC</sub> specification when the address bits are stabilizing.

4 Pins of ports 1, 2 and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when V<sub>IN</sub> is approximately 2V.

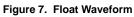

I<sub>CCMAX</sub> at other frequencies (for Philips North America parts) is given by: Active mode: I<sub>CCMAX</sub> = 1.43 X FREQ + 1.90;

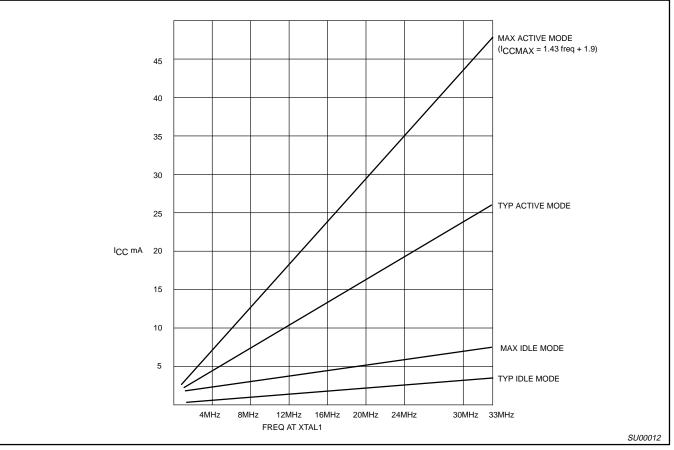

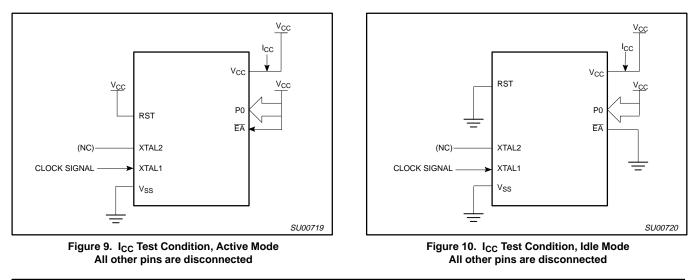

Idle mode: I<sub>CCMAX</sub> = 0.14 X FREQ +2.31, where FREQ is the external oscillator frequency in MHz. I<sub>CCMAX</sub> is given in mA. See Figure 8. See Figures 9 through 12 for I<sub>CC</sub> test conditions.

For Philips North America parts when  $T_{amb} = -40^{\circ}C$  to +85°C or Philips parts when  $T_{amb} = -40^{\circ}C$  to +125°C, see DC Electrical 7. Characteristics table on previous page.

The operating supply current is measured with all output pins disconnected; XTAL1 driven with  $t_r = t_f = 10ns$ ;  $V_{IL} = V_{SS} + 0.5V$ ;  $V_{IH} = V_{CC} - 0.5V$ ; XTAL2 not connected;  $\overline{EA} = RST = Port 0 = V_{CC}$ .

The idle mode supply current is measured with all output pins disconnected; XTAL1 driven with  $t_r = t_f = 10ns$ ;  $V_{IL} = V_{SS} + 0.5V$ ; 9.  $V_{IH} = V_{CC} - 0.5V$ ; XTAL2 not connected;  $\overline{EA} = Port 0 = V_{CC}$ ; RST =  $V_{SS}$ . 10. The power-down current is measured with all output pins disconnected, XTAL2 not connected,  $\overline{EA} = Port 0 = V_{CC}$ ; RST =  $V_{SS}$ .

11. Under steady state (non-transient) conditions, IOL must be externally limited as follows:

| Maximum I <sub>OL</sub> per port pin: | 15mA |

|---------------------------------------|------|

| Maximum IOL per 8-bit port:           | 26mA |

| Maximum IoL total for all outputs:    | 67mA |

If I<sub>OL</sub> exceeds the test condition, V<sub>OL</sub> may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

12. Pin capacitance for the ceramic DIP package is 15pF maximum.

#### 80C31/80C51/87C51

#### DC ELECTRICAL CHARACTERISTICS FOR PHILIPS NORTH AMERICA DEVICES (SC80C31 AND SC80C51)

$T_{amb} = 0^{\circ}C$  to +70°C or -40°C to +85°C,  $V_{CC} = 5V \pm 10\%$ ;  $V_{SS} = 0V$ LIMITS TEST SYMBOL PARAMETER UNIT CONDITIONS MIN TYP<sup>1</sup> MAX Input low voltage  $4.5V < V_{CC} < 5.5V$ -0.5 0.2V<sub>CC</sub>-0.1 V VIL Input high voltage (ports 0, 1, 2, 3, EA) V<sub>CC</sub>+0.5 V VIH 0.2V<sub>CC</sub>+0.9 0.7V<sub>CC</sub> V<sub>CC</sub>+0.5 Input high voltage, XTAL1, RST V V<sub>IH1</sub>  $V_{CC} = 4.5V$ Output low voltage, ports 1, 2, 38 VOL 0.4 V  $I_{OL} = 1.6 m A^2$  $V_{CC} = 4.5V$ Output low voltage, port 0, ALE, PSEN8, 7 V 0.4 V<sub>OL1</sub>  $I_{OL} = 3.2 \text{mA}^2$  $\begin{array}{l} V_{CC}=4.5V\\ I_{OH}=-30\mu A \end{array}$ VOH Output high voltage, ports 1, 2, 3<sup>3</sup>  $V_{CC} - 0.7$ V Output high voltage (port 0 in external bus mode),  $V_{CC} = 4.5V$ V<sub>OH1</sub> V<sub>CC</sub> – 0.7 V ALE<sup>9</sup>. PSEN<sup>3</sup>  $I_{OH} = -3.2 \text{mA}$ Logical 0 input current, ports 1, 2, 3  $V_{IN} = 0.4V$ -1 -50 μA Ι<sub>ΙL</sub>  $V_{IN} = 2.0V$ -650 Logical 1-to-0 transition current, ports 1, 2, 36  $I_{TL}$ μΑ See note 4 Input leakage current, port 0  $0.45 < V_{IN} < V_{CC} - 0.3$  $I_{LI}$ ±10 μΑ Icc Power supply current (see Figure 8): See note 5 Active mode @ 16MHz<sup>5</sup> 11.5 32 μΑ Idle mode @ 16MHz<sup>5</sup> 5 1.3 μΑ Power-down mode  $T_{amb} = 0$  to +70°C 50 3 μΑ  $T_{amb} = -40$  to  $+85^{\circ}C$ 75 μA Internal reset pull-down resistor 40 225 kΩ R<sub>RST</sub> CIO Pin capacitance<sup>10</sup> (except EA) 15 pF

NOTES:

1. Typical ratings are not guaranteed. The values listed are at room temperature, 5V.

Capacitive loading on ports 0 and 2 may cause spurious noise to be superimposed on the VoLs of ALE and ports 1 and 3. The noise is due 2. to external bus capacitance discharging into the port 0 and port 2 pins when these pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100pF), the noise pulse on the ALE pin may exceed 0.8V. In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input. IOL can exceed these conditions provided that no single output sinks more than 5mA and no more than two outputs exceed the test conditions.

3. Capacitive loading on ports 0 and 2 may cause the V<sub>OH</sub> on ALE and PSEN to momentarily fall below the (V<sub>CC</sub>-0.7) specification when the address bits are stabilizing.

4. Pins of ports 1, 2 and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when VIN is approximately 2V.

5. See Figures 9 through 12 for ICC test conditions.

$I_{CC} = 1.5 \times FREQ + 8.0;$ Active Mode:

$I_{CC} = 0.14 \times FREQ$  +2.31; See Figure 8. Idle Mode:

6. This value applies to  $T_{amb} = 0^{\circ}C$  to +70°C. For  $T_{amb} = -40^{\circ}C$  to +85°C,  $I_{TL} = -750\mu$ A. 7. Load capacitance for port 0, ALE, and PSEN = 100pF, load capacitance for all other outputs = 80pF.

Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 15mA (\*NOTE: This is 85°C specification.)

Maximum IOL per port pin: 26mA

Maximum IOI per 8-bit port: Maximum total IOL for all outputs:

71mA If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

ALE is tested to  $V_{OH1}$ , except when ALE is off then  $V_{OH}$  is the voltage specification.

10. Pin capacitance is characterized but not tested. Pin capacitance is less than 25pF. Pin capacitance of ceramic package is less than 15pF (except EA it is 25pF).

#### 80C31/80C51/87C51

#### AC ELECTRICAL CHARACTERISTICS FOR SC87C51 12–33MHz PHILIPS NORTH AMERICA DEVICES

$\label{eq:Tamb} \begin{array}{l} T_{amb} = 0^{\circ}C \ to \ +70^{\circ}C \ or \ -40^{\circ}C \ to \ +85^{\circ}C, \ V_{CC} = 5V \ \pm10\%, \ V_{SS} = 0V \ (SC87C51 \ 12, \ 16 \ and \ 24MHz \ versions); \\ For \ SC87C51 \ (33MHz \ only) \ T_{amb} = = 0^{\circ}C \ to \ +70^{\circ}C, \ V_{CC} = 5V \ \pm5\% \end{array}$

|                     | VARIABLE CLOCK <sup>3</sup> |                                                                  |                                 |                         |                          |  |

|---------------------|-----------------------------|------------------------------------------------------------------|---------------------------------|-------------------------|--------------------------|--|

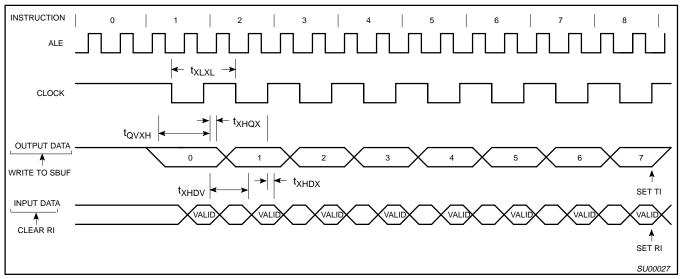

| SYMBOL              | FIGURE                      | PARAMETER                                                        | MIN                             | MAX                     | UNIT                     |  |

| 1/t <sub>CLCL</sub> |                             | Oscillator frequency: Speed Versions<br>SC87C51 C<br>G<br>P<br>Y | 3.5<br>3.5<br>3.5<br>3.5<br>3.5 | 12<br>16<br>24<br>33    | MHz<br>MHz<br>MHz<br>MHz |  |

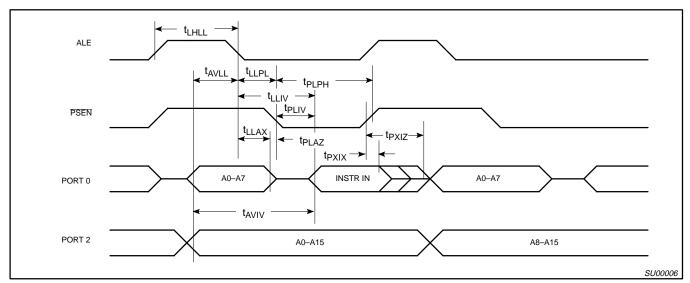

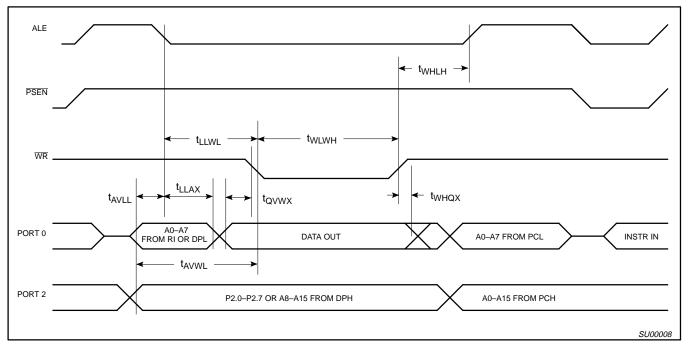

| t <sub>LHLL</sub>   | 1                           | ALE pulse width                                                  | 2t <sub>CLCL</sub> -40          |                         | ns                       |  |

| t <sub>AVLL</sub>   | 1                           | Address valid to ALE low                                         | t <sub>CLCL</sub> -13           |                         | ns                       |  |

| t <sub>LLAX</sub>   | 1                           | Address hold after ALE low                                       | t <sub>CLCL</sub> -20           |                         | ns                       |  |

| t <sub>LLIV</sub>   | 1                           | ALE low to valid instruction in                                  |                                 | 4t <sub>CLCL</sub> -65  | ns                       |  |

| t <sub>LLPL</sub>   | 1                           | ALE low to PSEN low                                              | t <sub>CLCL</sub> -13           |                         | ns                       |  |

| t <sub>PLPH</sub>   | 1                           | PSEN pulse width                                                 | 3t <sub>CLCL</sub> –20          |                         | ns                       |  |

| t <sub>PLIV</sub>   | 1                           | PSEN low to valid instruction in                                 |                                 | 3t <sub>CLCL</sub> -45  | ns                       |  |

| t <sub>PXIX</sub>   | 1                           | Input instruction hold after PSEN                                | 0                               |                         | ns                       |  |

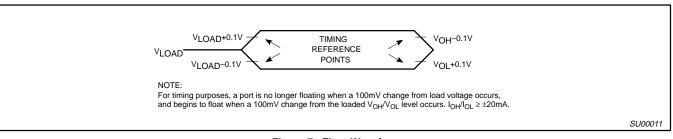

| t <sub>PXIZ</sub>   | 1                           | Input instruction float after PSEN                               |                                 | t <sub>CLCL</sub> -10   | ns                       |  |

| t <sub>AVIV</sub>   | 1                           | Address to valid instruction in                                  |                                 | 5t <sub>CLCL</sub> -55  | ns                       |  |

| t <sub>PLAZ</sub>   | 1                           | PSEN low to address float                                        |                                 | 10                      | ns                       |  |

| Data Memo           | ry                          |                                                                  |                                 |                         |                          |  |

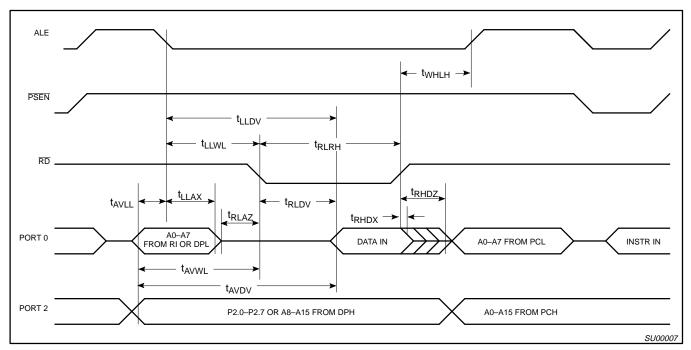

| t <sub>RLRH</sub>   | 2, 3                        | RD pulse width                                                   | 6t <sub>CLCL</sub> -100         |                         | ns                       |  |

| t <sub>WLWH</sub>   | 2, 3                        | WR pulse width                                                   | 6t <sub>CLCL</sub> -100         |                         | ns                       |  |

| t <sub>RLDV</sub>   | 2, 3                        | RD low to valid data in                                          |                                 | 5t <sub>CLCL</sub> –90  | ns                       |  |

| t <sub>RHDX</sub>   | 2, 3                        | Data hold after RD                                               | 0                               |                         | ns                       |  |

| t <sub>RHDZ</sub>   | 2, 3                        | Data float after RD                                              |                                 | 2t <sub>CLCL</sub> -28  | ns                       |  |

| t <sub>LLDV</sub>   | 2, 3                        | ALE low to valid data in                                         |                                 | 8t <sub>CLCL</sub> -150 | ns                       |  |

| t <sub>AVDV</sub>   | 2, 3                        | Address to valid data in                                         |                                 | 9t <sub>CLCL</sub> -165 | ns                       |  |

| t <sub>LLWL</sub>   | 2, 3                        | ALE low to RD or WR low                                          | 3t <sub>CLCL</sub> -50          | 3t <sub>CLCL</sub> +50  | ns                       |  |

| t <sub>AVWL</sub>   | 2, 3                        | Address valid to WR low or RD low                                | 4t <sub>CLCL</sub> -75          |                         | ns                       |  |

| t <sub>QVWX</sub>   | 2, 3                        | Data valid to WR transition                                      | t <sub>CLCL</sub> -20           |                         | ns                       |  |

| t <sub>WHQX</sub>   | 2, 3                        | Data hold after WR                                               | t <sub>CLCL</sub> -20           |                         | ns                       |  |

| t <sub>RLAZ</sub>   | 2, 3                        | RD low to address float                                          |                                 | 0                       | ns                       |  |

| t <sub>WHLH</sub>   | 2, 3                        | RD or WR high to ALE high                                        | t <sub>CLCL</sub> -20           | t <sub>CLCL</sub> +25   | ns                       |  |

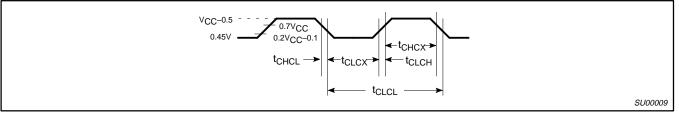

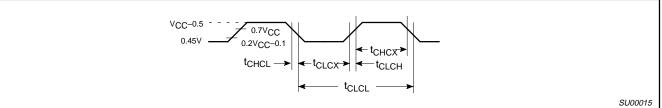

| External Cl         | ock                         | •                                                                | •                               |                         |                          |  |

| t <sub>CHCX</sub>   | 5                           | High time                                                        | 12                              |                         | ns                       |  |

| t <sub>CLCX</sub>   | 5                           | Low time                                                         | 12                              |                         | ns                       |  |

| t <sub>CLCH</sub>   | 5                           | Rise time                                                        |                                 | 20                      | ns                       |  |

| t <sub>CHCL</sub>   | 5                           | Fall time                                                        | 1                               | 20                      | ns                       |  |

NOTES:

Parameters are valid over operating temperature range unless otherwise specified.

Load capacitance for port 0, ALE, and PSEN = 100pF, load capacitance for all other outputs = 80pF.

3. For all Philips North America speed versions only.

4. Interfacing the 87C51 to devices with float times up to 50ns is permitted. This limited bus contention will not cause damage to port 0 drivers.

### 80C31/80C51/87C51

## AC ELECTRICAL CHARACTERISTICS FOR PHILIPS DEVICES T<sub>amb</sub> = 0°C to +70°C, V<sub>CC</sub> = 5V $\pm$ 20%, V<sub>SS</sub> = 0V (PCB80C31/51, PCF80C31/51)<sup>1, 2, 4, 5</sup>

|                     |        |                                                                                                                                                                     | VARIABLI                 | VARIABLE CLOCK <sup>3</sup> |                          |  |  |