# BINARY HEXADECIMAL AND BCD DECADE, SYNCHRONOUS UP/DOWN COUNTERS

8284 8285

REFER TO PAGE 17 FOR A, F AND Q PACKAGE PIN CONFIGURATIONS.

## DIGITAL 8000 SERIES TTL/MSI

### **DESCRIPTION**

The Up/Down Counter is a monolithic MSI circuit containing gates and binaries interconnected to provide a bidirectional divide-by-ten (decade) or divide-by-sixteen (hexadecimal) result as a function of the clock input.

The output code of the decade up/down counter is the commonly used BCD (8421) code, and the output sequence generated is the binary equivalent of the decimal numbers 0 through 9.

The hexadecimal up/down counter provides the output sequence 0 through 15 which is presented in a weighted binary code (8421).

Set and Reset on the binary elements provide asynchronous entry with respect to the clock line, causing a count of "0" or "15" (8284) or of "0" or "9" (8285), and also inhibit propagation of count enable data.

Entry and propagation of data is performed in a synchronous manner with the clock line, which is active on its negative going excursion. The input from a previous stage or other source is channeled through "Carry In" and its propagation can be inhibited by the "Count Enable" line. "Carry In" and "Count Enable" input duality gives added flexibility in multiple package cascading applications.

Direction of the counter is steered from a single line  $(Up/\overline{Down})$ , where a "0" level will cause a "down" count and a "1" level will accomplish an "up" count.

All Q outputs of the four binaries are brought to the outside world, together with the  $\overline{Q}$  output of the most significant binary (Q4) and the Carry Out.

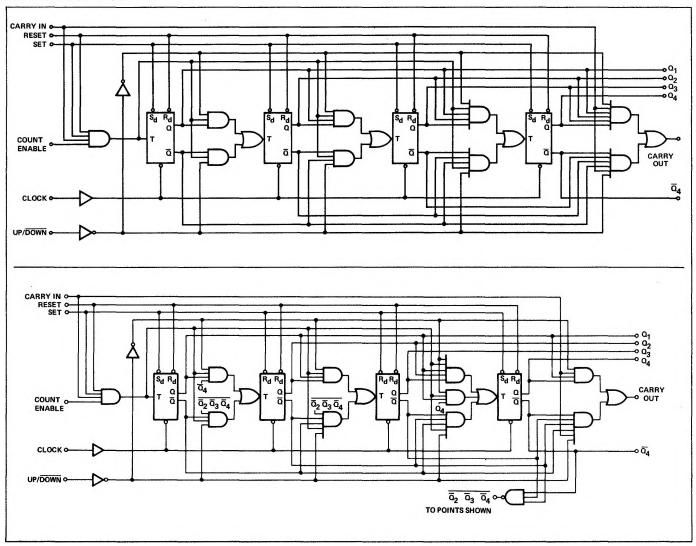

#### LOGIC DIAGRAM

## **ELECTRICAL CHARACTERISTICS** (Over Recommended Operating Temperature And Voltage)

| CHARACTERISTICS                             |      | LIN  | AITS |       | TEST CONDITIONS |       |         |       |       |           |         |       |

|---------------------------------------------|------|------|------|-------|-----------------|-------|---------|-------|-------|-----------|---------|-------|

|                                             | MIN. | TYP. | MAX. | UNITS | SET             | RESET | UP/DOWN | COUNT | CLOCK | CARRY     | OUTPUTS | NOTES |

| "1" Output Voltage                          |      |      |      |       |                 |       |         |       |       |           |         |       |

| Q <sub>1</sub> , Q <sub>4</sub> , Carry Out | 2.6  | 1    | İ    | v     | 0.8∨            | 2.0V  | 2.0∨    |       |       | 2.0V      | –800μA  |       |

| Q <sub>2</sub> , Q <sub>3</sub> , (8284)    |      | 1    | 1    |       | - 7             |       |         |       |       |           |         |       |

| Q <sub>2</sub> , Q <sub>3</sub> (8285)      | 2.6  |      | l    | l v l | Pulse           |       | 0.8V    |       |       |           | -800μA  |       |

| Q4                                          | 2.6  |      | }    | l v l | 2.0V            | 0.8V  | 1,01    |       |       |           | -800µA  |       |

| '0'' Output Voltage                         | 2.0  |      |      |       |                 |       |         |       |       |           | ·       |       |

| $Q_1, Q_2, Q_3, Q_4$ and                    |      | i    |      |       |                 |       | ,       |       | - V   |           |         |       |

| Carry Out                                   |      |      | 0.4  | l v l | 2.0V            | 0.8V  |         |       |       | 0.87      | 9.6mA   |       |

| $\overline{Q}_4$                            |      |      | 0.4  | l v l | 0.8V            | 2.0V  |         |       |       |           | 9.6mA   |       |

| '1" Input Current                           |      |      | 0.4  | •     | 0.01            |       |         |       |       |           |         |       |

| Carry In                                    |      |      | 120  | μΑ    | Pulse           |       | 5.0V    |       |       | 4.5V      |         |       |

| Set                                         |      |      | 200  | μA    | 4.5V            | Pulse |         |       |       |           |         |       |

| Reset                                       |      |      | 40   | μΑ    | Pulse           | 4.5V  |         |       |       |           |         |       |

| Count Enable                                |      |      | 40   | μA    |                 | 7.01  |         | 4.5V  | 71    |           |         |       |

| Clock and Up/Down                           |      |      | 40   | μΑ    |                 |       | 4.5V    | v v   | 4.5V  |           |         |       |

| '0' Input Current                           |      |      | 70   | ^^    |                 |       | 4.51    |       | 1.51  |           |         |       |

| Carry In                                    |      |      | 3.2  | mΑ    | Pulse           |       | ov      |       |       | 0.4V      |         |       |

| Set                                         |      |      | 6.4  | mA    | 0.4V            |       | _       | •     |       |           | 1       |       |

| Reset                                       |      |      | 6.4  | mA    |                 | 0.4V  |         |       |       |           |         |       |

| Count Enable                                |      |      | 1.6  | mA    |                 |       |         | 0.4V  |       |           |         |       |

| Clock                                       |      |      | 1.6  | mA    |                 |       |         |       | 0.4V  |           |         |       |

| Up/Down                                     |      |      | 1.6  | mA    |                 |       | 0.4V    |       |       |           |         |       |

| nput Latch Voltage                          |      |      | 1    | •     |                 |       |         |       |       |           |         |       |

| Carry in                                    | 5.5  |      |      | V     |                 | 0V    | 5.0V    | 0V    |       | 10mA      |         |       |

| Reset                                       | 5.5  |      |      | V     |                 | 10mA  |         | 0V    |       | <b>0V</b> |         |       |

| Set                                         | 5.5  |      |      | V     | 10mA            |       |         | 0V    |       | 0∨        |         |       |

| Count Enable                                | 5.5  |      | 1    | V     | 0V              |       |         | 10mA  |       | 0V        |         |       |

| Up/Down                                     | 5.5  |      |      | V     |                 |       | 10mA    |       |       |           |         |       |

| Output Short Circuit                        |      |      |      |       |                 |       |         |       |       |           | ov      |       |

| Current                                     | -20  |      | -70  | mA    |                 |       |         |       |       |           | ]       |       |

$T_{\mbox{\scriptsize A}}$  = 25° C and  $V_{\mbox{\scriptsize CC}}$  = 5.0V

| CHARACTERISTICS                         | LIMITS |      |      |       | TEST CONDITIONS |       |         |                 |       |       |         |       |

|-----------------------------------------|--------|------|------|-------|-----------------|-------|---------|-----------------|-------|-------|---------|-------|

|                                         | MIN.   | TYP. | MAX. | UNITS | SET             | RESET | UP/DOWN | COUNT<br>ENABLE | CLOCK | CARRY | OUTPUTS | NOTES |

| Power Consumption                       |        | 315  | 420  | mW    |                 |       |         |                 |       |       |         | 12    |

| Propagation Delay                       |        |      |      |       |                 |       |         |                 | ļ     |       |         |       |

| ton Clock to Q4 & Q4                    |        | 32   | 45   | ns    |                 |       |         |                 |       |       |         | 7     |

| $t_{on}$ Clock to $Q_1, Q_2, Q_3$       |        | 28   | 40   | ns    |                 |       |         |                 | 2.    |       |         | 7     |

| t off Clock to Qn, Qn                   |        | 25   | 35   | ns    |                 |       |         |                 |       |       |         | 7     |

| t <sub>on</sub> Reset to Q <sub>n</sub> |        | 24   | 35   | ns    |                 |       |         |                 |       |       |         | 7     |

| toff Set to Qn                          |        | 15   | 25   | ns    |                 |       |         |                 |       |       |         | 7     |

| ton Reset to Qn                         |        | 32   | 45   | ns    |                 |       |         |                 |       |       |         | 7     |

| ton Carry In to Carry Out               |        | 15   | 25   | ns    |                 |       |         |                 |       |       |         | 7     |

| toff Carry In to Carry Out              |        | 20   | 30   | ns    |                 |       |         |                 |       |       |         | 7     |

| Clock Min. "1" Interval                 | 20     | 15   |      | ns    |                 |       |         |                 |       |       |         | 7     |

| Count Rate                              | 20     | 30   |      | MHz   |                 |       | 1       |                 |       |       |         |       |

| Carry In, Count Enable,                 |        |      |      |       |                 |       |         |                 |       |       |         |       |

| & Up/Down Set-Up Time                   |        | 15   | 25   | ns    |                 |       |         |                 |       |       |         |       |

| Carry In, Count Enable                  |        |      |      |       |                 |       |         |                 |       |       |         |       |

| & Up/Down Hold Time                     |        | 0    | 2    | ns    |                 |       |         |                 |       |       |         |       |

| Set/Reset Pulse Width                   |        | 20   | 25   | ns    |                 |       |         |                 |       |       |         |       |

#### NOTES:

- All voltage measurements are referenced to the ground terminal. Terminals not specifically referenced are left electrically open.

- 2. All measurements are taken with ground pin tied to zero volts.

- 3. Positive current is defined as into the terminal referenced.

- 4. Positive NAND Logic Definition:

"UP" Level = "1", "DOWN" Level = "0".

- Output source current is supplied through a resistor to ground.

- 6. Output sink current is supplied through a resistor to V<sub>CC</sub>.

- 7. Refer to AC Test Figure.

- This test guarantees operation free of input latch-up over the specified operating supply voltage range.

- Manufacturer reserves the right to make design and process changes and improvements.

- 10. Connect  $\mathbf{Q_4}$  to count enable, set the counter (1001), and count down. The counter will halt at BCD-7 (0111).

- Pulse is normally at +4.0 volts, falling to 0 volts for at least 100 nsec,

- 12.  $V_{CC} = 5.25$  volts.

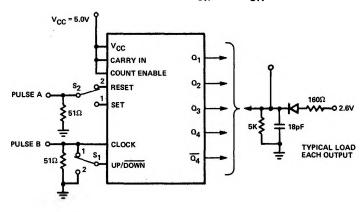

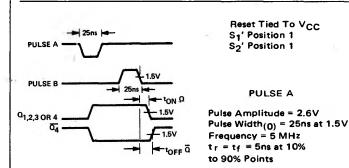

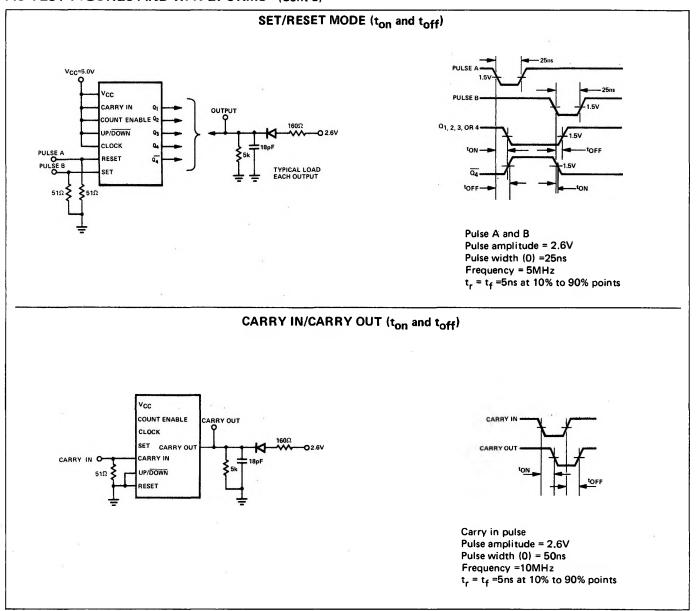

#### AC TEST FIGURES AND WAVEFORMS

#### **MODE OF OPERATION**

8284 Binary Synchronous Up/Down Counter 8285 BCD Synchronous Up/Down Counter

|                 | SET | RESET | CARRY IN | COUNT<br>ENABLE | UP/DOWN | FUNCTION       |

|-----------------|-----|-------|----------|-----------------|---------|----------------|

| A. Asynchronous |     |       |          |                 |         |                |

|                 | 1   | 0     | X        | X               | X       | (0000)         |

| 8284 Only       | 0   | 1     | X        | ( x             | X       | "15" (1 1 1 1) |

| 8285 Only       | 0   | 1     | X        | ×               | х       | "9" (1001)     |

| B. Synchronous  |     |       |          |                 |         |                |

| (1)             | 1   | 1     | 0        | X               | X       | Hold *         |

|                 | 1   | 1     | X        | lo              | ×       | Hold *         |

|                 | 1   | 1     | 1        | 1               | 0       | "Down" Count * |

|                 | 1   | 1     | 1        | 1               | 1       | "Up" Count *   |

<sup>\*</sup>Function is synchronous with NEGATIVE going transition of the Clock pin. X = don't care.

#### **CARRY OUT**

Carry Out<sub>8284</sub> = Carry In  $(Q_1Q_2Q_3Q_4 UP + \overline{Q}_1\overline{Q}_2\overline{Q}_3\overline{Q}_4 \overline{DOWN}$

Carry Out8285 = Carry In (Q1Q4 UP + Q1Q2Q3Q4 DOWN

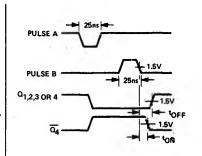

#### CLOCK MODE (ton AND toff)

Set Tied To V<sub>CC</sub> S<sub>1</sub>' Position 2 S<sub>2</sub>' Position 2

**PULSE B**

Pulse Amplitude = 2.6VPulse Width = 25ns at 1.5VFrequency = 5 MHz  $t_{T}$  =  $t_{f}$  = 5ns at 10%to 90% Points

## AC TEST FIGURES AND WAVEFORMS (Cont'd)

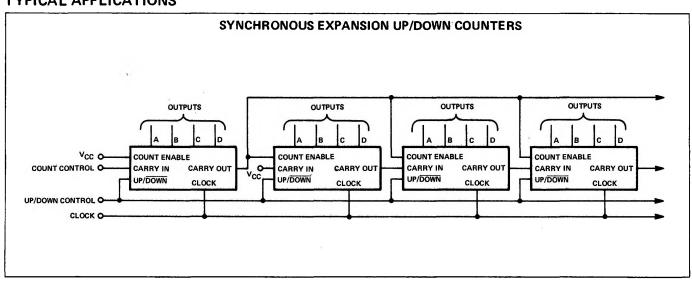

## TYPICAL APPLICATIONS