REFER TO PAGE 16 FOR B, E AND R PACKAGE PIN CONFIGURATIONS.

# DIGITAL 8000 SERIES TTL/MSI

### **DESCRIPTION**

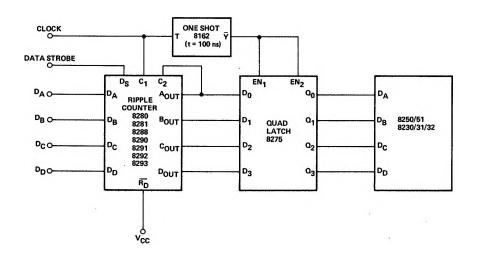

The 8275 is a QUAD LATCH circuit designed to provide temporary storage of four bits of information. A common application is as a holding register between a counter and a display driver (such as the 8280 and 8T01.) Separate enable lines to latches 1-2 and 3-4 allow individual control of each

pair of latches. Initially, data is transferred on the rising edge of the enable pulse. While the enable is high, output Q follows the data input. When the enable falls, the input data present at fall time is retained at the Q output. Both Q and  $\overline{Q}$  are accessible.

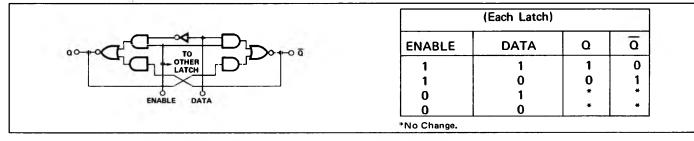

#### LOGIC DIAGRAM AND TRUTH TABLE

# **ELECTRICAL CHARACTERISTICS** (Over Recommended Operating Temperature And Voltage)

| CHARACTERISTICS                      |      | LIMITS |      |       |               | TEST CONDITIONS |         |       |

|--------------------------------------|------|--------|------|-------|---------------|-----------------|---------|-------|

|                                      | MIN. | TYP.   | MAX. | UNITS | DATA<br>INPUT | ENABLE<br>INPUT | OUTPUTS | NOTES |

| "1" Output Voltage (Q, \overline{Q}) | 2.6  | 3.5    |      | V     |               | -               | -800μA  | 6, 11 |

| "0" Output Voltage (Q, Q)            |      |        | 0.4  | V     |               |                 | 16mA    | 7, 11 |

| "0" Input Current (Data)             | -0.1 | l      | -3.2 | mA    | 0.4V          | 5.25V           |         |       |

| "0" Input Current (Enable)           | -0.1 | l      | -6.4 | m A   | 5.25V         | 0.4V            |         | 1     |

| "1" Input Current (Data)             |      |        | 80   | μΑ    | 4.5V          | 0.0∨            |         |       |

| "1" Input Current (Enable)           |      |        | 160  | μΑ    | 0.0∨          | 4.5V            |         | ł     |

# $T_{\Delta} = 25^{\circ} \text{ C}$ and $V_{CC} = 5.0 \text{ V}$

| CHARACTERISTICS                   | LIMITS |        |        |       | TEST CONDITIONS |                 |         |       |

|-----------------------------------|--------|--------|--------|-------|-----------------|-----------------|---------|-------|

|                                   | MIN.   | TYP.   | MAX.   | UNITS | DATA<br>INPUT   | ENABLE<br>INPUT | OUTPUTS | NOTES |

| setup (1) at D input              |        | 12     | 20     | ns    |                 |                 |         | 8, 12 |

| <sup>t</sup> setup (0) at D input |        | 14     | 20     | ns    |                 |                 |         | 8, 12 |

| <sup>t</sup> hold (1) at D input  | 0      | 15     |        | ns    |                 | ļ               |         | 8, 13 |

| <sup>t</sup> hold (0) at D input  | 0      | 6      |        | ns    |                 |                 |         | 8, 13 |

| <sup>t</sup> pd (1) D to Q        |        | 16     | 30     | ns    |                 |                 |         | 8     |

| pd (0) D to Q                     |        | 14     | 25     | ns    |                 | i               |         | 8     |

| <sup>1</sup> pd (1) D to 0̄       |        | 24     | 40     | ns    |                 |                 |         | 8     |

| pd (0) D to Q                     |        | 7      | 15     | ns    |                 |                 |         | 8     |

| <sup>t</sup> pd (1) E to Q        |        | 16     | 30     | ns    |                 |                 |         | 8     |

| tpd (0) E to Q                    |        | 12     | 20     | ns    |                 | 1               |         | 8     |

| <sup>t</sup> pd (1) E to          |        | 16     | 30     | ns    |                 |                 |         | 8     |

| <sup>t</sup> pd (0) E to          | - 3    | 12     | 20     | ns    |                 |                 |         | 8     |

| Power Consumption/Supply Current  |        | 205/39 | 265/50 | mW/mA |                 |                 |         | 14    |

| Input Voltage Rating (Data)       | 5.5    |        |        | V     | 10mA            | 0.0∨            |         | 12    |

| Input Voltage Rating (Enable)     | 5.5    |        |        | V     | 0.0V            | 10mA            |         | 12    |

| Output Short Circuit Current      | -20    |        | -70    | mA    | 0.0∨            |                 | 0.0∨    |       |

#### NOTES:

- All voltage measurements are referenced to the ground terminal. Terminals not specifically referenced are left electrically open.

- All measurements are taken with ground pin tied to zero volts.

- 3. Positive current flow is defined as into the terminal referenced.

- Positive NAND Logic Definition:

- "UP" Level = "1", "DOWN" Level = "0".

- Precautionary measures should be taken to ensure current limiting in accordance with Absolute Maximum Ratings should the isolation diodes become forward biased.

- Output source current is supplied through a resistor to ground.

- Output sink current is supplied through a resistor to  $V_{CC}$ ,

- Refer to AC Test Figure. 8.

- Manufacturer reserves the right to make design and process changes and improvements.

- 10. Inputs for output voltage test is per TRUTH TABLE with threshold levels of 0.8V for logical "0" and 2.0V for logical "1".

- This test guarantees operation free of input latch-up over the 11. specified operating power supply voltage range.

- $t_{\text{setup}}$  is defined as the time prior to the fall of the clock. thold is defined as the time after the fall of the clock.  $V_{\text{CC}} = 5.25 \text{ volts}.$ 12.

- 13,

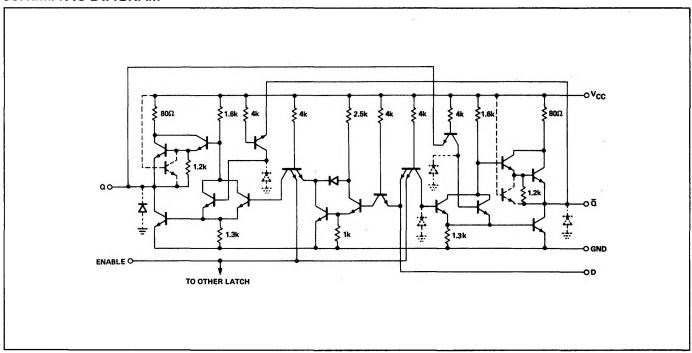

### **SCHEMATIC DIAGRAM**

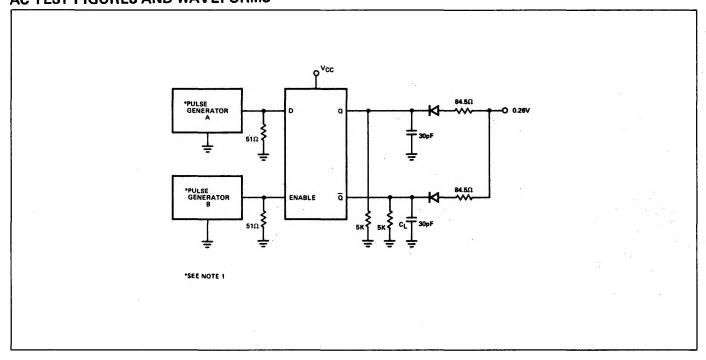

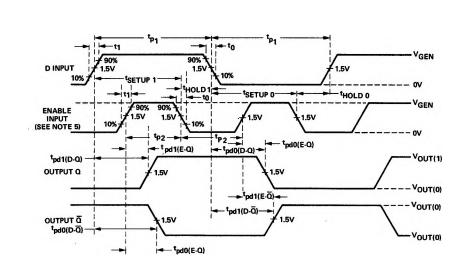

# **AC TEST FIGURES AND WAVEFORMS**

#### AC TEST FIGURES AND WAVEFORMS (Cont'd)

#### NOTES:

- The pulse generators have the following characteristics: V<sub>gen</sub> = 3V, t<sub>1</sub> = t<sub>0</sub>≤10ns, and Z<sub>out</sub> ≈50Ω. For pulse generator A tp 1 = 1µs and PRR = 500kHz. For pulse generator B, tp2 = 500ns and Prr = 1MHz. Positions of D-input and enable input pulses are varied with respect to each other to verify setup and hold times.

- 2. Each latch is tested separately.

- 3. C<sub>L</sub> includes probe and jig capacitance.

- 4. All diodes are 1N916.

- When measuring  $t_{pd}$ 1 (D-Q),  $t_{pd}$ 0 (D-Q),  $t_{pd}$ 0 (D-Q), and  $t_{pd}$ 1 (D-Q), enable input must be held at logical 1.

### TYPICAL APPLICATION

# **OUTPUT STROBING OF RIPPLE COUNTER TO ACHIEVE SYNCHRONOUS OUTPUT CHANGES**