# 10-BIT SERIAL-IN, PARALLEL-OUT | SHIFT REGISTER

8273

B,F,W PACKAGES

# DIGITAL 8000 SERIES TTL/MSI

#### **DESCRIPTION**

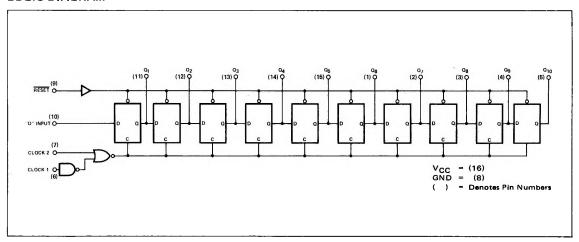

The 8273, 10-Bit Shift Register is an array of binary elements interconnected to perform the serial-in, parallel-out shift function. This device utilizes a common buffered reset and operates from either a positive or negative edge clock pulse. Clock 1 is triggered by a negative going clock pulse and Clock 2 is triggered by a positive going clock pulse. The unused clock input performs the inhibit function. The circuit configuration is arranged as a single serial input register with ten true parallel outputs.

#### **TRUTH TABLE**

| INPUT | RESET | CLOCK 1 | CLOCK 2 | Q <sub>n</sub> + 1 |

|-------|-------|---------|---------|--------------------|

| 1     | 1     | Pulse   | 0       | 1                  |

| 0     | 1     | Pulse   | 0       | 0                  |

| 1     | 1     | 1       | Pulse   | 1                  |

| 0     | 1     | 1       | Pulse   | 0                  |

| 1     | 1     | Pulse   | 1       | a                  |

| 1 0   | 1     | Pulse   | 1       | O                  |

| 1     | 1     | 0       | Pulse   | α                  |

| 1 0   | 1     | o       | Pulse   | ایتا               |

NOTE: The unused clock input performs the INHIBIT function.

RESET = 0 > Q = 0

#### LOGIC DIAGRAM

## ELECTRICAL CHARACTERISTICS (Over Recommended Operating Temperature And Voltage)

|                                   | LIMITS   |      |      |       | TEST CO   |         |         |       |               |       |

|-----------------------------------|----------|------|------|-------|-----------|---------|---------|-------|---------------|-------|

| CHARACTERISTICS                   | MIN. TYP | TYP. | MAX. | UNITS | "D" INPUT | CLOCK 1 | CLOCK 2 | RESET | OUTPUTS       | NOTES |

| "1" Output Voltage                | 2.6      | 3.4  |      | v     | 2.0V      | Pulse   | 0.8V    |       | -500µA        | 6     |

| "0" Output Voltage                |          | 0.2  | 0.4  | v     | 0.8V      | Pulse   | 0.8V    |       | 9.6m <b>A</b> | 7     |

| "O" Input Current                 |          |      |      |       |           |         | İ       |       | ĺ             |       |

| "D" Input                         | -0.1     |      | -1.6 | mA    | 0.4V      |         | ŀ       |       |               |       |

| Clock 1                           | -0.1     |      | -1.6 | mA    |           | 0.4V    |         |       |               |       |

| Clock 2                           | -0.1     |      | -1.6 | mA    |           |         | 0.4V    |       |               |       |

| Reset                             | -0.1     |      | -1.6 | mA    |           |         |         | 0.4V  |               |       |

| "1" Input Current                 |          |      |      |       |           |         |         |       |               |       |

| "D" Input                         |          |      | 40   | μА    | 4.5V      |         |         |       |               |       |

| Clock 1                           |          |      | 40   | μА    |           | 4.5V    |         |       |               |       |

| Clock 2                           |          |      | 40   | μА    |           |         | 4.5V    |       |               |       |

| Reset                             |          |      | 40   | μА    |           |         |         | 4.5V  |               |       |

| Input Voltage Rating (All Inputs) | 5.5      |      |      | V     | 10mA      | 10mA    | 10mA    | 10mA  |               |       |

$T_A = 25^{\circ} C$  and  $V_{CC} = 5.0 V$

| OUADA CTEDIOTION                   | LIMITS  |      |             | TEST CONDITIONS |           |         |         |       |         |       |

|------------------------------------|---------|------|-------------|-----------------|-----------|---------|---------|-------|---------|-------|

| CHARACTERISTICS                    | MIN. TY | TYP. | MAX.        | UNITS           | "D" INPUT | CLOCK 1 | CLOCK 2 | RESET | OUTPUTS | NOTES |

| Max. Data Transfer Rate            | 25      | 35   |             | MHz             | -2        |         |         |       |         |       |

| Turn-On Delay ton                  |         |      |             |                 |           |         |         |       |         |       |

| Clock 1 to Output                  |         | 32   | 40          | ns              | *         |         | 0.0∨    | 4.5V  |         | 10    |

| Clock 2 to Output                  |         | 28   | 40          | ns              |           |         |         | 4.5V  |         | 10    |

| Reset to Output                    |         | 35   | 50          | ns              |           | 4.5V    |         |       |         | 10    |

| Turn-Off Delay toff                | l       |      | l           |                 | 1 1       |         |         | 1     | l       |       |

| Clock 1 to Output                  |         | 25   | 40          | ns              |           |         | 0.0∨    |       |         | 10    |

| Clock 2 to Output                  |         | 19   | 40          | ns              | 1         | 4.5V    |         |       | !       | 10    |

| Clock Pulse Width                  | l       | }    | 100         |                 | ] ]       |         |         |       |         | i     |

| Clock 1                            |         | 16   | 25          | ns              |           |         | 0.0∨    |       |         | 10    |

| Clock 2                            |         | 12   | 20          | ns              | 1         | 4.5V    |         |       |         | 10    |

| Set-Up Time (t <sub>set-up</sub> ) |         | }    |             |                 | ]         |         |         |       |         |       |

| Clock 1                            |         |      | 15          | ns              |           |         | 0.0∨    |       | 1       | 10    |

| Clock 2                            | -       |      | 10          | ns              | 1 1       | 4.5V    |         |       |         | 10    |

| Hold Time (t <sub>hold</sub> )     |         | 1    |             |                 |           |         |         |       |         | 1     |

| Clock 1                            |         |      | 15          | ns              | 1 1       |         | 0.0∨    |       | (       | 10    |

| Clock 2                            |         |      | 10          | ns              |           | 4.5V    |         |       |         | 10    |

| Power Consumption/Supply Current   |         | 341/ | 540/<br>103 | mW              |           |         |         |       |         | 8     |

| Short Circuit Output Current       | -20     | 65   | -70         | mA              |           |         |         |       | 1       | 8,9   |

| Input Voltage Rating               |         |      |             |                 |           |         |         |       |         |       |

| (All Inputs)                       | 5.5     |      |             | l v             | 10mA      | 10mA    | 10mA    | 10mA  | }       |       |

#### NOTES:

- All voitage and capacitance measurements are referenced to the ground terminal. Terminals not specifically referenced are left electrically open.

- 2. All measurements are taken with ground pin tied to zero

- 3. Positive current flow is defined as into the terminal referenced.

- Positive logic definition: "UP" Level = "1", "DOWN" Level = "0".

- 5. Precautionary measures should be taken to ensure current

- limiting in accordance with Absolute Maximum Ratings should the isolation diodes become forward biased.

- Output source current is supplied through a resistor to ground.

- 7. Output sink current is supplied through a resistor to V<sub>CC</sub>.

- 8. V<sub>CC</sub> = 5.25V.

- 9. Not more than one output should be shorted at one time.

- 10. See AC Test Figure.

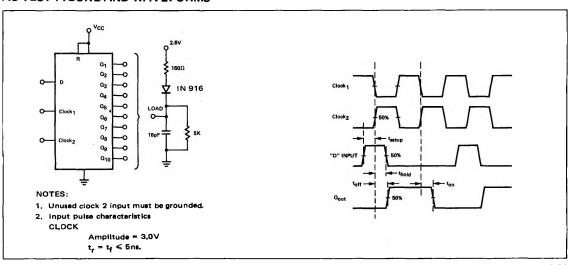

### AC TEST FIGURE AND WAVEFORMS